#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.8 PCON Register

The Power Control (PCON) Register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT), and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | —   | —   | —   |     | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

**BOR**: Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

NOTES:

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

|         | U-0                                                      | U-0                          | R/W-0           | R/W-0          | R/W-0             | R/W-0       | R/W-0         | R/W-0  |  |  |  |

|---------|----------------------------------------------------------|------------------------------|-----------------|----------------|-------------------|-------------|---------------|--------|--|--|--|

|         | _                                                        | _                            | T1CKPS1         | T1CKPS0        | T1OSCEN           | T1SYNC      | TMR1CS        | TMR10N |  |  |  |

|         | bit 7                                                    |                              |                 |                |                   |             |               | bit 0  |  |  |  |

|         |                                                          |                              |                 |                |                   |             |               |        |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                               |                              |                 |                |                   |             |               |        |  |  |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits |                              |                 |                |                   |             |               |        |  |  |  |

|         |                                                          | rescale valu                 |                 |                |                   |             |               |        |  |  |  |

|         |                                                          | rescale valu<br>rescale valu |                 |                |                   |             |               |        |  |  |  |

|         | • = • • • • •                                            | rescale valu                 |                 |                |                   |             |               |        |  |  |  |

| bit 3   | T1OSCEN                                                  | : Timer1 Os                  | cillator Enal   | ble Control b  | it                |             |               |        |  |  |  |

|         | 1 = Oscillat                                             | tor is enable                | ed              |                |                   |             |               |        |  |  |  |

|         | 0 = Oscillat                                             | tor is shut-c                | off (the oscill | ator inverter  | is turned off to  | eliminate p | ower drain    | )      |  |  |  |

| bit 2   | T1SYNC: 7                                                | Timer1 Exte                  | rnal Clock Ir   | nput Synchro   | onization Contr   | ol bit      |               |        |  |  |  |

|         | When TMF                                                 |                              |                 |                |                   |             |               |        |  |  |  |

|         |                                                          | •                            | e external cl   |                |                   |             |               |        |  |  |  |

|         | When TMR                                                 |                              | nal clock inp   | Jul            |                   |             |               |        |  |  |  |

|         |                                                          |                              | ner1 uses th    | e internal clo | ock when TMR      | 1CS = 0.    |               |        |  |  |  |

| bit 1   | TMR1CS:                                                  | -<br>Timer1 Cloo             | k Source So     | elect bit      |                   |             |               |        |  |  |  |

|         |                                                          |                              | •               | 10SO/T1Ck      | (I (on the rising | edge)       |               |        |  |  |  |

|         | 0 = Interna                                              | I clock (Fos                 | sc/4)           |                |                   |             |               |        |  |  |  |

| bit 0   | TMR10N:                                                  |                              | bit             |                |                   |             |               |        |  |  |  |

|         | 1 = Enable                                               |                              |                 |                |                   |             |               |        |  |  |  |

|         | 0 = Stops 7                                              | imer1                        |                 |                |                   |             |               |        |  |  |  |

|         | · · ·                                                    |                              |                 |                |                   |             |               |        |  |  |  |

|         | Legend:                                                  |                              |                 |                |                   |             |               |        |  |  |  |

|         | R = Reada                                                |                              |                 | Vritable bit   | U = Unimpl        |             |               |        |  |  |  |

|         | - n = Value                                              | at POR                       | '1' = E         | Bit is set     | '0' = Bit is c    | leared      | x = Bit is ur | nknown |  |  |  |

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                                                                  | Freq.          | C1           | C2        |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                        | 32 kHz         | 33 pF        | 33 pF     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 100 kHz        | 15 pF        | 15 pF     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 200 kHz        | 15 pF        |           |  |  |  |  |

| These va                                                                                                                                                                                                                                                                                                                                                  | lues are for o | design guida | nce only. |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                                                                          |                |              |           |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                                                                | Epson C-00     | 1R32.768K-A  | ± 20 PPM  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                                                                   | Epson C-2      | 100.00 KC-P  | ± 20 PPM  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                                                                   | STD XTL        | 200.000 kHz  | ± 20 PPM  |  |  |  |  |

| <ul> <li>200 kHz STD XTL 200.000 kHz ± 20 PPM</li> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                |              |           |  |  |  |  |

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

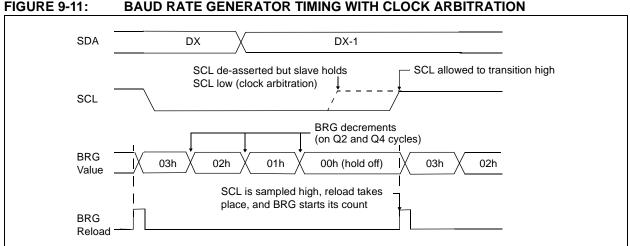

### BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

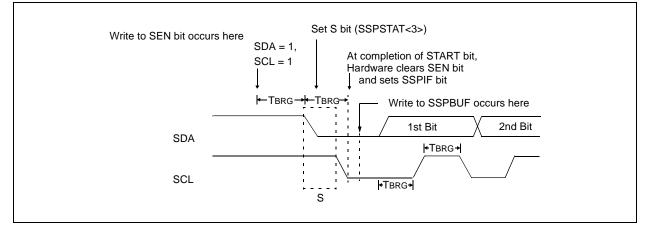

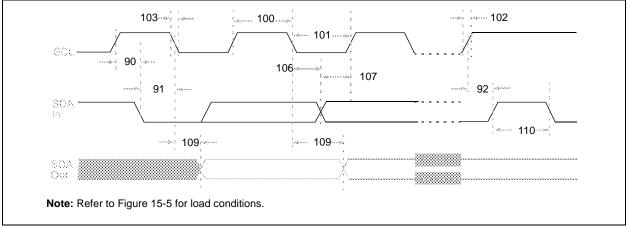

#### 9.2.9 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the START condition, and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware. The baud rate generator is suspended, leaving the SDA line held low, and the START condition is complete.

Note: If, at the beginning of START condition, the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

#### 9.2.9.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

#### **FIGURE 9-12:** FIRST START BIT TIMING

### TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG                                  | USART Tr             | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

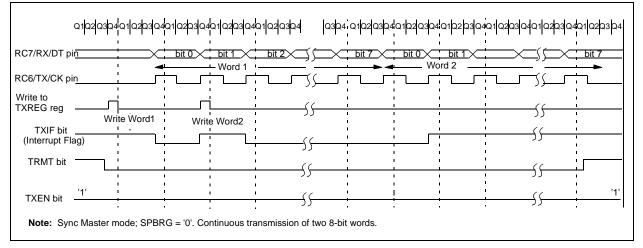

### FIGURE 10-9: SYNCHRONOUS TRANSMISSION

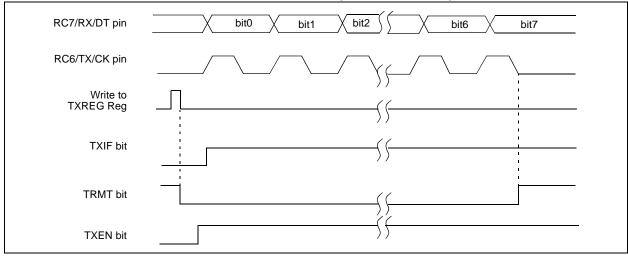

### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

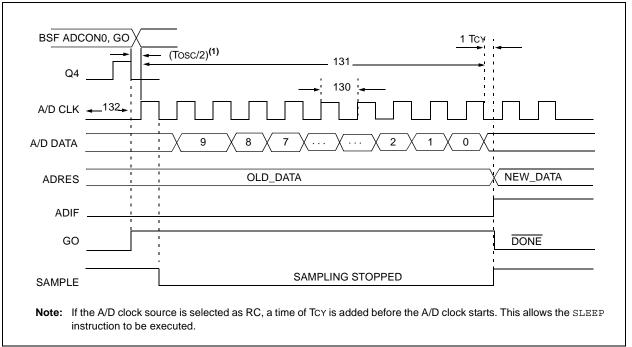

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the other devices.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, VSS, RA2, or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

## REGISTER 11-1: ADCON0 REGISTER (ADDRESS: 1Fh)

|         | R/W-0                                                                                                                                                                                                                                                                                                                              | R/W-0         | R/W-0                          | R/W-0           | R/W-0 | R/W-0                       | U-0         | R/W-0  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------|-----------------|-------|-----------------------------|-------------|--------|--|--|--|

|         | ADCS1                                                                                                                                                                                                                                                                                                                              | ADCS0         | CHS2                           | CHS1            | CHS0  | GO/DONE                     | _           | ADON   |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                              |               |                                |                 |       |                             |             | bit 0  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                    |               |                                |                 |       |                             |             |        |  |  |  |

| bit 7-6 | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from the internal A/D module RC oscillator)                                                                                                                                                                 |               |                                |                 |       |                             |             |        |  |  |  |

| bit 5-3 | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)<br>101 = channel 5, (RE0/AN5) <sup>(1)</sup><br>110 = channel 6, (RE1/AN6) <sup>(1)</sup><br>111 = channel 7, (RE2/AN7) <sup>(1)</sup> |               |                                |                 |       |                             |             |        |  |  |  |

| bit 2   | $\frac{\text{If ADON} = 1}{1 = A/D \text{ cor}}$ $0 = A/D \text{ cor}$                                                                                                                                                                                                                                                             | version in pr | ogress (setti<br>n progress (t | ng this bit sta |       | onversion)<br>ared by hardv | vare when t | he A/D |  |  |  |

| bit 1   | Unimpleme                                                                                                                                                                                                                                                                                                                          | ented: Read a | as '0'                         |                 |       |                             |             |        |  |  |  |

| bit 0   | ADON: A/D On bit<br>1 = A/D converter module is operating                                                                                                                                                                                                                                                                          |               |                                |                 |       |                             |             |        |  |  |  |

|         | <ul> <li>0 = A/D converter module is shut-off and consumes no operating current</li> <li>Note 1: These channels are not available on PIC16F873/876 devices.</li> </ul>                                                                                                                                                             |               |                                |                 |       |                             |             |        |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC16F87X

### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

### bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | Α          | А          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

# 12.0 SPECIAL FEATURES OF THE CPU

All PIC16F87X devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87X devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

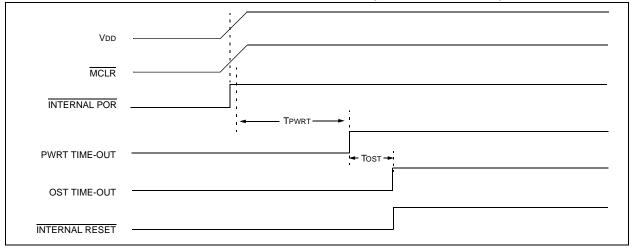

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the  $PIC^{\mathbb{R}}$  MCU Mid-Range Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

|          |     |     |      |     |                                    | •                         | ,                               |

|----------|-----|-----|------|-----|------------------------------------|---------------------------|---------------------------------|

| Register |     | Dev | ices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| PIE2     | 873 | 874 | 876  | 877 | -r-0 00                            | -r-0 00                   | -r-u uu                         |

| PCON     | 873 | 874 | 876  | 877 | dd                                 | uu                        | uu                              |

| PR2      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | 1111 1111                       |

| SSPADD   | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| SSPSTAT  | 873 | 874 | 876  | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |

| TXSTA    | 873 | 874 | 876  | 877 | 0000 -010                          | 0000 -010                 | uuuu -uuu                       |

| SPBRG    | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| ADRESL   | 873 | 874 | 876  | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| ADCON1   | 873 | 874 | 876  | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| EEDATA   | 873 | 874 | 876  | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| EEADR    | 873 | 874 | 876  | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EEDATH   | 873 | 874 | 876  | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EEADRH   | 873 | 874 | 876  | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EECON1   | 873 | 874 | 876  | 877 | x x000                             | u u000                    | u uuuu                          |

| EECON2   | 873 | 874 | 876  | 877 |                                    |                           |                                 |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

# PIC16F87X

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                       |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# PIC16F87X

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                       |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [ label ] NOP |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |

|------------------|--------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                              |

| Status Affected: | None                                                                                             |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |

| RETFIE           | Return from Interrupt                         |

|------------------|-----------------------------------------------|

| Syntax:          | [label] RETFIE                                |

| Operands:        | None                                          |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$ |

| Status Affected: | None                                          |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |

| Operands:        | $0 \leq f \leq 127$                        |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |  |

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHARACTERISTICS |       |                                         |                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |       |                                                             |  |  |  |

|--------------------|-------|-----------------------------------------|-------------------|------------------------------------------------------|---------|-------|-------------------------------------------------------------|--|--|--|

| Param<br>No. Sym   |       | Characteristic                          | Min               | Тур†                                                 | Max     | Units | Conditions                                                  |  |  |  |

|                    | VIL   | Input Low Voltage                       |                   |                                                      |         |       |                                                             |  |  |  |

|                    |       | I/O ports                               |                   |                                                      |         |       |                                                             |  |  |  |

| D030               |       | with TTL buffer                         | Vss               | —                                                    | 0.15Vdd | V     | For entire VDD range                                        |  |  |  |

| D030A              |       |                                         | Vss               | —                                                    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                     |  |  |  |

| D031               |       | with Schmitt Trigger buffer             | Vss               | —                                                    | 0.2Vdd  | V     |                                                             |  |  |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss               | —                                                    | 0.2Vdd  | V     |                                                             |  |  |  |

| D033               |       | OSC1 (in XT, HS and LP)                 | Vss               | —                                                    | 0.3Vdd  | V     | (Note 1)                                                    |  |  |  |

|                    |       | Ports RC3 and RC4                       |                   | —                                                    |         |       |                                                             |  |  |  |

| D034               |       | with Schmitt Trigger buffer             | Vss               | —                                                    | 0.3Vdd  | V     | For entire VDD range                                        |  |  |  |

| D034A              |       | with SMBus                              | -0.5              | —                                                    | 0.6     | V     | for VDD = 4.5 to 5.5V                                       |  |  |  |

|                    | Vih   | Input High Voltage                      |                   |                                                      | r       | r     | 1                                                           |  |  |  |

|                    |       | I/O ports                               |                   | —                                                    |         |       |                                                             |  |  |  |

| D040               |       | with TTL buffer                         | 2.0               | —                                                    | Vdd     | -     | $4.5V \leq VDD \leq 5.5V$                                   |  |  |  |

| D040A              |       |                                         | 0.25VDD<br>+ 0.8V | _                                                    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8Vdd            | —                                                    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D042               |       | MCLR                                    | 0.8Vdd            | —                                                    | Vdd     | V     |                                                             |  |  |  |

| D042A              |       | OSC1 (XT, HS and LP)                    | 0.7Vdd            | —                                                    | Vdd     | V     | (Note 1)                                                    |  |  |  |

| D043               |       | OSC1 (in RC mode)<br>Ports RC3 and RC4  | 0.9Vdd            |                                                      | Vdd     | V     |                                                             |  |  |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7Vdd            | —                                                    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D044A              |       | with SMBus                              | 1.4               | —                                                    | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |  |  |  |

| D070               | IPURB | PORTB Weak Pull-up Current              | 50                | 250                                                  | 400     | μA    | VDD = 5V, VPIN = Vss,<br>-40°С то +85°С                     |  |  |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                   | •                                                    |         | •     |                                                             |  |  |  |

| D060               |       | I/O ports                               | —                 | —                                                    | ±1      | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at hi-impedance             |  |  |  |

| D061               |       | MCLR, RA4/T0CKI                         | _                 | _                                                    | ±5      | μA    | $Vss \leq VPIN \leq VDD$                                    |  |  |  |

| D063               |       | OSC1                                    | —                 | _                                                    | ±5      | •     | $Vss \le VPIN \le VDD$ , XT, HS<br>and LP osc configuration |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

### 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |                    |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |     |      |            |                                            |  |

|--------------------------------------------------------------------|--------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|------|------------|--------------------------------------------|--|

| Param<br>No.                                                       | Symbol             | ol Characteristic/ Min Typ† Max Units<br>Device                  |                                                                                                                          |     |      | Conditions |                                            |  |

|                                                                    | VDD Supply Voltage |                                                                  |                                                                                                                          |     |      |            |                                            |  |

| D001                                                               |                    |                                                                  | 4.0                                                                                                                      | —   | 5.5  | V          | LP, XT, RC osc configuration               |  |

| D001A                                                              |                    |                                                                  | 4.5                                                                                                                      |     | 5.5  | V          | HS osc configuration                       |  |

| D001A                                                              |                    |                                                                  | VBOR                                                                                                                     |     | 5.5  | V          | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |  |

| D002                                                               | Vdr                | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                                                                                        | 1.5 | _    | V          |                                            |  |

| D003                                                               | VPOR               | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                        | Vss | _    | V          | See section on Power-on Reset for details  |  |

| D004                                                               | Svdd               | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                     | —   | —    | V/ms       | See section on Power-on Reset for details  |  |

| D005                                                               | VBOR               | Brown-out Reset<br>Voltage                                       | 3.7                                                                                                                      | 4.0 | 4.35 | V          | BODEN bit in configuration word<br>enabled |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

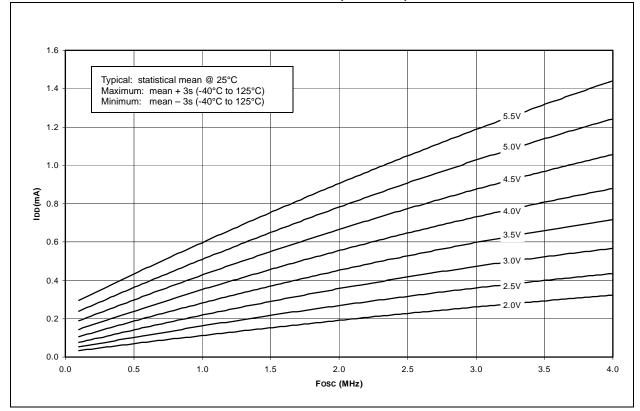

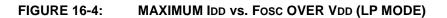

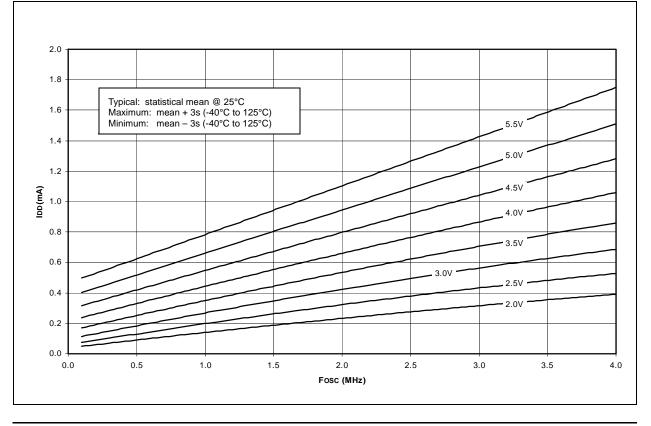

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

### 15.4 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| DC CHARACTERISTICS |       |                                         | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section 15.1) |     |         |       |                                                             |  |  |

|--------------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-------|-------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                          | Min Typ†                                                                                                                                                                                                   |     | Max     | Units | Conditions                                                  |  |  |

|                    | VIL   | Input Low Voltage                       |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

|                    |       | I/O ports                               |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

| D030               |       | with TTL buffer                         | Vss                                                                                                                                                                                                        | —   | 0.15Vdd |       | For entire VDD range                                        |  |  |

| D030A              |       |                                         | Vss                                                                                                                                                                                                        | —   | 0.8V    | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |

| D031               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                        | —   | 0.2Vdd  | V     |                                                             |  |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss                                                                                                                                                                                                        | —   | 0.2Vdd  | V     |                                                             |  |  |

| D033               |       | OSC1 (in XT, HS and LP)                 | Vss                                                                                                                                                                                                        | —   | 0.3Vdd  | V     | (Note 1)                                                    |  |  |

|                    |       | Ports RC3 and RC4                       |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

| D034               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                        | —   | 0.3Vdd  | V     | For entire VDD range                                        |  |  |

| D034A              |       | with SMBus                              | -0.5                                                                                                                                                                                                       | —   | 0.6     | V     | for $VDD = 4.5$ to $5.5V$                                   |  |  |

|                    | Vih   | Input High Voltage                      |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

|                    |       | I/O ports                               |                                                                                                                                                                                                            | —   |         |       |                                                             |  |  |

| D040               |       | with TTL buffer                         | 2.0                                                                                                                                                                                                        | —   | Vdd     | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |

| D040A              |       |                                         | 0.25VDD                                                                                                                                                                                                    | —   | Vdd     | V     | For entire VDD range                                        |  |  |

|                    |       |                                         | + 0.8V                                                                                                                                                                                                     |     |         |       |                                                             |  |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8Vdd                                                                                                                                                                                                     | —   | Vdd     | V     | For entire VDD range                                        |  |  |

| D042               |       | MCLR                                    | 0.8Vdd                                                                                                                                                                                                     | —   | Vdd     | V     |                                                             |  |  |

| D042A              |       | OSC1 (XT, HS and LP)                    | 0.7Vdd                                                                                                                                                                                                     | —   | Vdd     | V     | (Note 1)                                                    |  |  |

| D043               |       | OSC1 (in RC mode)                       | 0.9Vdd                                                                                                                                                                                                     | —   | Vdd     | V     |                                                             |  |  |

|                    |       | Ports RC3 and RC4                       |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7VDD                                                                                                                                                                                                     | —   | Vdd     | V     | For entire VDD range                                        |  |  |

| D044A              |       | with SMBus                              | 1.4                                                                                                                                                                                                        | —   | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |  |  |

| D070A              | IPURB |                                         | 50                                                                                                                                                                                                         | 250 | 400     | μA    | VDD = 5V, VPIN = VSS,                                       |  |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                                            |     |         |       |                                                             |  |  |

| D060               |       | I/O ports                               | -                                                                                                                                                                                                          | -   | ±1      | μA    | $Vss \le VPIN \le VDD,$                                     |  |  |

|                    |       |                                         |                                                                                                                                                                                                            |     |         |       | Pin at hi-impedance                                         |  |  |

| D061               |       | MCLR, RA4/T0CKI                         | -                                                                                                                                                                                                          | -   | ±5      | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |