Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-04i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

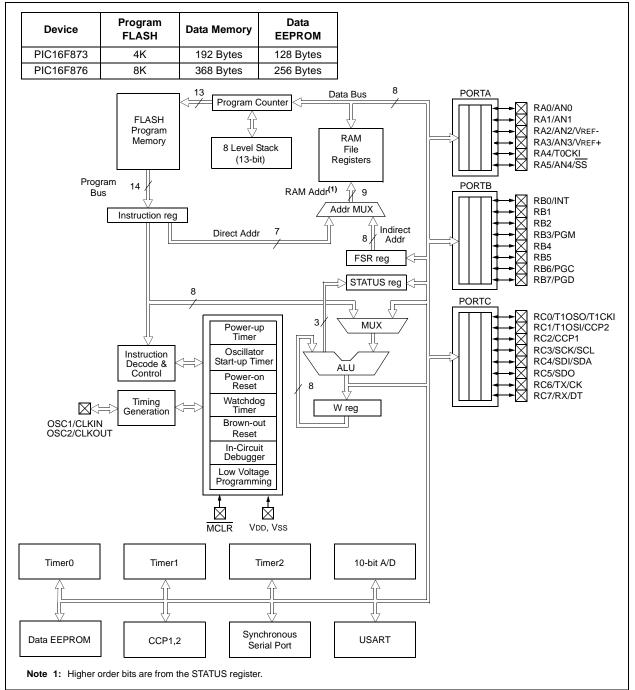

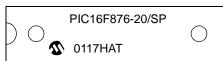

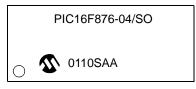

# 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | Pin Name DIP<br>Pin# |       | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|----------------------|-------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                    | 9     | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                   | 10    | 0             | _                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                    | 1     | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                      |       |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                    | 2     | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                    | 3     | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                    | 4     | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                    | 5     | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                    | 6     | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                    | 7     | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                      |       |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                   | 21    | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                   | 22    | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                   | 23    | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                   | 24    | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                   | 25    | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                   | 26    | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                   | 27    | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                   | 28    | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                      |       |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                   | 11    | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                   | 12    | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                   | 13    | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                   | 14    | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                   | 15    | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                   | 16    | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                   | 17    | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                   | 18    | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19                | 8, 19 | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                   | 20    | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not  |       |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin#     | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                         |  |  |  |  |

|-------------------|----------------|-------------------|-----------------|----------------------|------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

|                   |                |                   |                 |                      |                        | PORTC is a bi-directional I/O port.                                                                 |  |  |  |  |

| RC0/T1OSO/T1CKI   | 15             | 16                | 32              | I/O                  | ST                     | RC0 can also be the Timer1 oscillator output or<br>Timer1 clock input.                              |  |  |  |  |

| RC1/T1OSI/CCP2    | 16             | 18                | 35              | I/O                  | ST                     | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.       |  |  |  |  |

| RC2/CCP1          | 17             | 19                | 36              | I/O                  | ST                     | RC2 can also be the Capture1 input/Compare1<br>output/PWM1 output.                                  |  |  |  |  |

| RC3/SCK/SCL       | 18             | 20                | 37              | I/O                  | ST                     | RC3 can also be the synchronous serial clock inp<br>output for both SPI and I <sup>2</sup> C modes. |  |  |  |  |

| RC4/SDI/SDA       | 23             | 25                | 42              | I/O                  | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |  |  |  |  |

| RC5/SDO           | 24             | 26                | 43              | I/O                  | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                        |  |  |  |  |

| RC6/TX/CK         | 25             | 27                | 44              | I/O                  | ST                     | RC6 can also be the USART Asynchronous Transmi<br>or Synchronous Clock.                             |  |  |  |  |

| RC7/RX/DT         | 26             | 29                | 1               | I/O                  | ST                     | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                              |  |  |  |  |

|                   |                |                   |                 |                      |                        | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus. |  |  |  |  |

| RD0/PSP0          | 19             | 21                | 38              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD1/PSP1          | 20             | 22                | 39              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD2/PSP2          | 21             | 23                | 40              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD3/PSP3          | 22             | 24                | 41              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD4/PSP4          | 27             | 30                | 2               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD5/PSP5          | 28             | 31                | 3               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD6/PSP6          | 29             | 32                | 4               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

| RD7/PSP7          | 30             | 33                | 5               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                     |  |  |  |  |

|                   |                |                   |                 |                      |                        | PORTE is a bi-directional I/O port.                                                                 |  |  |  |  |

| RE0/RD/AN5        | 8              | 9                 | 25              | I/O                  | ST/TTL <sup>(3)</sup>  | RE0 can also be read control for the parallel slave port, or analog input5.                         |  |  |  |  |

| RE1/WR/AN6        | 9              | 10                | 26              | I/O                  | ST/TTL <sup>(3)</sup>  | RE1 can also be write control for the parallel slave port, or analog input6.                        |  |  |  |  |

| RE2/CS/AN7        | 10             | 11                | 27              | I/O                  | ST/TTL <sup>(3)</sup>  | RE2 can also be select control for the parallel slave port, or analog input7.                       |  |  |  |  |

| Vss               | 12,31          | 13,34             | 6,29            | Р                    | _                      | Ground reference for logic and I/O pins.                                                            |  |  |  |  |

| Vdd               | 11,32          | 12,35             | 7,28            | Р                    | _                      | Positive supply for logic and I/O pins.                                                             |  |  |  |  |

| NC                | -              | 1,17,28,<br>40    | 12,13,<br>33,34 |                      | —                      | These pins are not internally connected. These pins should be left unconnected.                     |  |  |  |  |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |                 | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                             |  |  |  |  |

#### TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

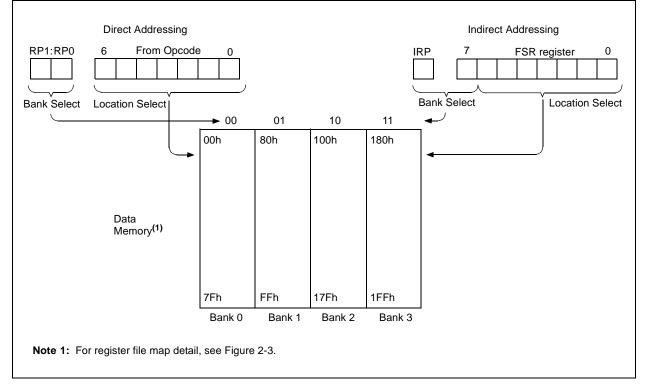

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

#### TABLE 3-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |  |  |  |  |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |  |  |  |  |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |  |  |  |  |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |  |  |  |  |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |  |  |  |  |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |  |  |  |  |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |  |  |  |  |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or Synchronous Clock.                          |  |  |  |  |

|                 |      | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |  |  |  |  |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|----------------------------------------|-------|-------|-------|-------|-----------|-----------|-------|-----------|--------------------------|---------------------------------|

| 07h     | PORTC                                  | RC7   | RC6   | RC5   | RC4   | xxxx xxxx | uuuu uuuu |       |           |                          |                                 |

| 87h     | 7h TRISC PORTC Data Direction Register |       |       |       |       |           |           |       | 1111 1111 | 1111 1111                |                                 |

Legend: x = unknown, u = unchanged

### 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

### 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**REGISTER 5-1: OPTION REG REGISTER**

DANA

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|                                                                                                                                                                                                                                                                                                 | R/W-1                                                                                                                                                     | R/W-1                                                       | R/W-1                                                                     | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|-------|-------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                 | RBPU                                                                                                                                                      | INTEDG                                                      | T0CS                                                                      | TOSE  | PSA   | PS2   | PS1   | PS0   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | bit 7                                                                                                                                                     |                                                             |                                                                           |       |       |       |       | bit 0 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                           | RBPU                                                                                                                                                      |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 6                                                                                                                                                                                                                                                                                           | INTEDG                                                                                                                                                    |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 5                                                                                                                                                                                                                                                                                           | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 4                                                                                                                                                                                                                                                                                           | <b>T0SE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 3                                                                                                                                                                                                                                                                                           | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>   |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| bit 2-0                                                                                                                                                                                                                                                                                         | PS2:PS0:                                                                                                                                                  | Prescaler Ra                                                | ite Select b                                                              | oits  |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | Bit Value                                                                                                                                                 | TMR0 Rate                                                   | WDT Rat                                                                   | e     |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                      | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 | -     |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | Legend:                                                                                                                                                   |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$                                                                                  |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 | - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                               |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                 |                                                                                                                                                           |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

| To avoid an unintended device RESET, the instruction sequence shown in the PIC <sup>®</sup> MCU Mid-Range Fam-<br>ily Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0<br>to the WDT. This sequence must be followed even if the WDT is disabled. |                                                                                                                                                           |                                                             |                                                                           |       |       |       |       |       |  |  |  |  |

Note:

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

|         | U-0                                                      | U-0                          | R/W-0           | R/W-0          | R/W-0             | R/W-0       | R/W-0         | R/W-0  |  |  |  |  |

|---------|----------------------------------------------------------|------------------------------|-----------------|----------------|-------------------|-------------|---------------|--------|--|--|--|--|

|         | _                                                        | _                            | T1CKPS1         | T1CKPS0        | T1OSCEN           | T1SYNC      | TMR1CS        | TMR10N |  |  |  |  |

|         | bit 7                                                    |                              |                 |                |                   |             |               | bit 0  |  |  |  |  |

|         |                                                          |                              |                 |                |                   |             |               |        |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                               |                              |                 |                |                   |             |               |        |  |  |  |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits |                              |                 |                |                   |             |               |        |  |  |  |  |

|         | 11 = 1:8 Prescale value                                  |                              |                 |                |                   |             |               |        |  |  |  |  |

|         |                                                          | rescale valu<br>rescale valu |                 |                |                   |             |               |        |  |  |  |  |

|         | • = • • • • •                                            | rescale valu                 |                 |                |                   |             |               |        |  |  |  |  |

| bit 3   | T1OSCEN                                                  | : Timer1 Os                  | cillator Enal   | ble Control b  | it                |             |               |        |  |  |  |  |

|         | 1 = Oscillat                                             | tor is enable                | ed              |                |                   |             |               |        |  |  |  |  |

|         | 0 = Oscillat                                             | tor is shut-c                | off (the oscill | ator inverter  | is turned off to  | eliminate p | ower drain    | )      |  |  |  |  |

| bit 2   | T1SYNC: 7                                                | Timer1 Exte                  | rnal Clock Ir   | nput Synchro   | onization Contr   | ol bit      |               |        |  |  |  |  |

|         | When TMF                                                 |                              |                 |                |                   |             |               |        |  |  |  |  |

|         |                                                          | •                            | e external cl   |                |                   |             |               |        |  |  |  |  |

|         | When TMR                                                 |                              | nal clock inp   | Jul            |                   |             |               |        |  |  |  |  |

|         |                                                          |                              | ner1 uses th    | e internal clo | ock when TMR      | 1CS = 0.    |               |        |  |  |  |  |

| bit 1   | TMR1CS:                                                  | -<br>Timer1 Cloo             | k Source So     | elect bit      |                   |             |               |        |  |  |  |  |

|         |                                                          |                              | •               | 10SO/T1Ck      | (I (on the rising | edge)       |               |        |  |  |  |  |

|         | 0 = Interna                                              | I clock (Fos                 | sc/4)           |                |                   |             |               |        |  |  |  |  |

| bit 0   | TMR10N:                                                  |                              | bit             |                |                   |             |               |        |  |  |  |  |

|         | 1 = Enables Timer1                                       |                              |                 |                |                   |             |               |        |  |  |  |  |

|         | 0 = Stops Timer1                                         |                              |                 |                |                   |             |               |        |  |  |  |  |

|         |                                                          |                              |                 |                |                   |             |               |        |  |  |  |  |

|         | Legend:                                                  |                              |                 |                |                   |             |               |        |  |  |  |  |

|         | R = Reada                                                |                              |                 | Vritable bit   | U = Unimpl        |             |               |        |  |  |  |  |

|         | - n = Value                                              | at POR                       | '1' = E         | Bit is set     | '0' = Bit is c    | leared      | x = Bit is ur | nknown |  |  |  |  |

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

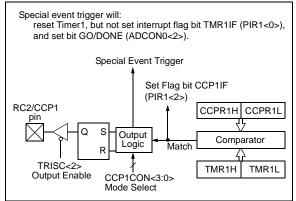

#### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

|       | R/W-0                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                 | R/W-0                       | R/W-0                      | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|-------------------------|---------------|---------------|-------------|--|

|       | GCEN                                                                                                                                                                                               | ACKSTAT                                                                                                                                                                                               | ACKDT                       | ACKEN                      | RCEN                    | PEN           | RSEN          | SEN         |  |

|       | bit 7                                                                                                                                                                                              |                                                                                                                                                                                                       |                             |                            |                         |               |               | bit 0       |  |

| bit 7 | 1 = Enable                                                                                                                                                                                         | <b>GCEN</b> : General Call Enable bit (In I <sup>2</sup> C Slave mode only)<br>1 = Enable interrupt when a general call address (0000h) is received in the SSPSR<br>0 = General call address disabled |                             |                            |                         |               |               |             |  |

| bit 6 | ACKSTAT                                                                                                                                                                                            | Acknowledg                                                                                                                                                                                            | e Status bit                | (In I <sup>2</sup> C Maste | er mode onl             | у)            |               |             |  |

|       | In Master Transmit mode:<br>1 = Acknowledge was not received from slave<br>0 = Acknowledge was received from slave                                                                                 |                                                                                                                                                                                                       |                             |                            |                         |               |               |             |  |

| bit 5 | ACKDT: A                                                                                                                                                                                           | cknowledge [                                                                                                                                                                                          | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m    | ode only)               |               |               |             |  |

|       | Value that end of a re                                                                                                                                                                             | knowledge                                                                                                                                                                                             |                             | the user initi             | ates an Ack             | nowledge s    | equence at    | the         |  |

| bit 4 | ACKEN: A                                                                                                                                                                                           | cknowledge \$                                                                                                                                                                                         | Sequence E                  | nable bit (In              | I <sup>2</sup> C Master | mode only)    |               |             |  |

|       | In Master Receive mode:<br>1 = Initiate Acknowledge sequence on SDA and SCL pins and transmit ACKDT data bit.<br>Automatically cleared by hardware.<br>0 = Acknowledge sequence idle               |                                                                                                                                                                                                       |                             |                            |                         |               | ta bit.       |             |  |

| bit 3 | RCEN: Re                                                                                                                                                                                           | ceive Enable<br>es Receive mo                                                                                                                                                                         | bit (In I <sup>2</sup> C M  | laster mode                | only)                   |               |               |             |  |

| bit 2 | PEN: STC                                                                                                                                                                                           | P Condition I                                                                                                                                                                                         | Enable bit (I               | n I <sup>2</sup> C Master  | r mode only             | )             |               |             |  |

|       | 1 = Initiate                                                                                                                                                                                       | ase Control:<br>STOP condit<br>condition idle                                                                                                                                                         |                             | and SCL pir                | ns. Automat             | ically cleare | d by hardwa   | are.        |  |

| bit 1 | 1 = Initiate                                                                                                                                                                                       | epeated STAR<br>Repeated ST/<br>ted START co                                                                                                                                                          | ART conditic                | on on SDA an               |                         |               |               | / hardware. |  |

| bit 0 | <b>SEN</b> : START Condition Enable bit (In I <sup>2</sup> C Master mode only)<br>1 = Initiate START condition on SDA and SCL pins. Automatically cleared by hardware.<br>0 = START condition idle |                                                                                                                                                                                                       |                             |                            |                         |               |               |             |  |

|       |                                                                                                                                                                                                    | For bits ACK<br>mode, this bit<br>writes to the \$                                                                                                                                                    | may not be                  | set (no spo                |                         |               |               |             |  |

|       | Logondi                                                                                                                                                                                            |                                                                                                                                                                                                       |                             |                            |                         |               |               |             |  |

|       | Legend:<br>R = Reada                                                                                                                                                                               | blo bit                                                                                                                                                                                               | ۱۸/ _ ۱۸/-                  | itable bit                 |                         | plemented k   | hit road as f | 0'          |  |

|       | K = Keaua                                                                                                                                                                                          |                                                                                                                                                                                                       | vv = vvi                    |                            | 0 = 0.000               |               | n, reau as    | 0           |  |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

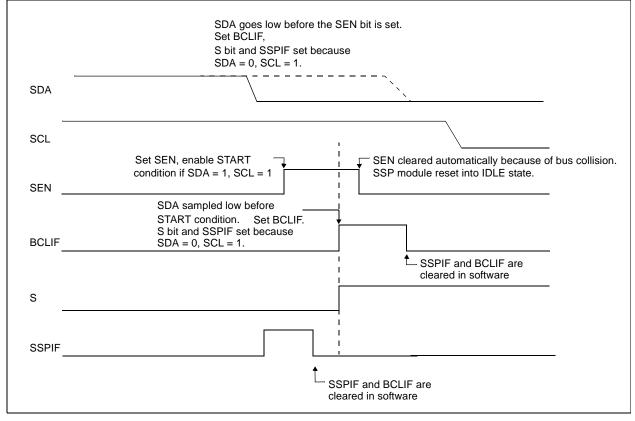

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth

receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-----------------------------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                        | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                        | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                         | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re                   | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                        | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                         | TXEN   | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | aud Rate Generator Register |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

NOTES:

#### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

#### bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 3.2).

#### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F873/874 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876/877 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

| MOVWF  | W TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|