Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-04i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|---------------------|--------------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                  | 10           | 0             | _                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                   | 1            | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                     |              |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                   | 2            | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                   | 3            | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                   | 4            | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                   | 5            | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                   | 6            | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                   | 7            | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                     |              |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                  | 22           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                  | 23           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                  | 24           | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                  | 25           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                  | 26           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                     |              |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                  | 11           | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                  | 12           | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                  | 13           | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                  | 14           | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                  | 15           | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                  | 16           | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                  | 17           | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                  | 18           | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19               | 8, 19        | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                  | 20           | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not |              |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

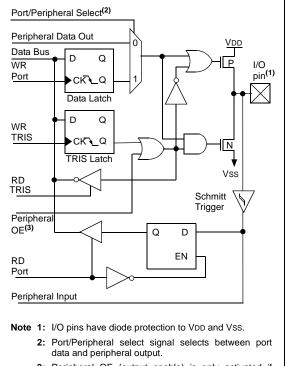

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

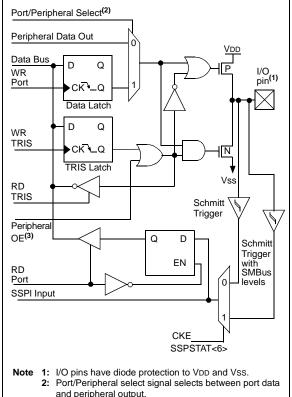

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

# FIGURE 3-6:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active. NOTES:

#### 4.4 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program the memory and insert value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

#### EXAMPLE 4-3: FLASH PROGRAM READ

| BSF   | STATUS, RP1   | ;                        |

|-------|---------------|--------------------------|

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | ADDRL, W      | ;Write the               |

| MOVWF | EEADR         | ;address bytes           |

| MOVF  | ADDRH,W       | ;for the desired         |

| MOVWF | EEADRH        | ;address to read         |

| BSF   | STATUS, RPO   | ;Bank 3                  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |

| BSF   | EECON1, RD    | ;Start read operation    |

| NOP   |               | ;Required two NOPs       |

| NOP   |               | ;                        |

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |

| MOVWF | DATAL         | ;                        |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |

| MOVWF | DATAH         | ;                        |

|       |               |                          |

# 4.5 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory, is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 4-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

# 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                    | e Freq. C1 C2 |                               |          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------|----------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                          | 32 kHz        | 33 pF                         | 33 pF    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 100 kHz       | 15 pF                         |          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 200 kHz       | 15 pF                         | 15 pF    |  |  |  |  |

| These values are for design guidance only.                                                                                                                                                                                                                                                                  |               |                               |          |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                            |               |                               |          |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                  | Epson C-00    | 1R32.768K-A                   | ± 20 PPM |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                     | Epson C-2     | pson C-2 100.00 KC-P ± 20 PPM |          |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                     | STD XTL       | 200.000 kHz                   | ± 20 PPM |  |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |               |                               |          |  |  |  |  |

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Figure 9-1 shows a block diagram for the SPI mode, while Figure 9-5 and Figure 9-9 show the block diagrams for the two different  $I^2C$  modes of operation.

The Application Note AN734, "Using the PIC<sup>®</sup> MCU SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication" describes the slave operation of the MSSP module on the PIC16F87X devices. AN735, "Using the PIC<sup>®</sup> MCU MSSP Module for I<sup>2</sup>C<sup>TM</sup> Communications" describes the master operation of the MSSP module on the PIC16F87X devices.

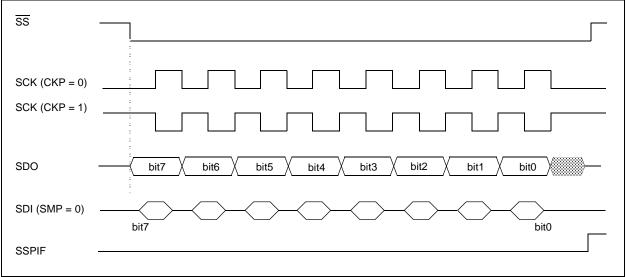

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

# FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

# 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware, to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

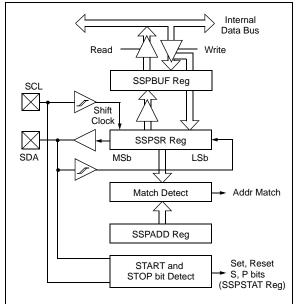

#### FIGURE 9-5:

I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C firmware modes (provided for compatibility to other mid-range products)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode. Pull-up resistors must be provided externally to the SCL and SDA pins for the proper operation of the  $I^2C$  module.

The CKE bit (SSPSTAT<6:7>) sets the levels of the SDA and SCL pins in either Master or Slave mode. When CKE = 1, the levels will conform to the SMBus specification. When CKE = 0, the levels will conform to the  $I^2C$  specification.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written to, or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

# 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

# 12.3 **RESET**

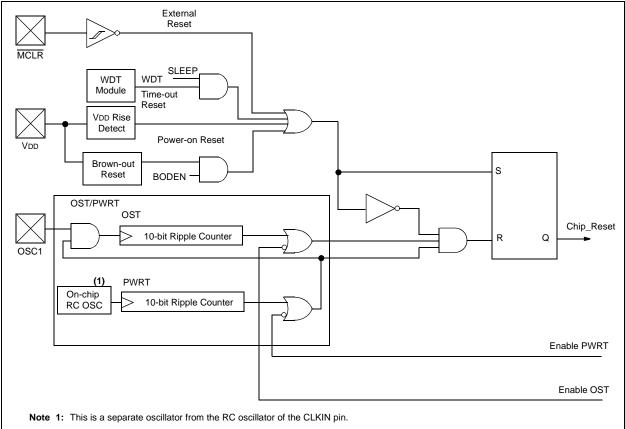

The PIC16F87X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different RESET situations as indicated in Table 12-4. These bits are used in software to determine the nature of the RESET. See Table 12-6 for a full description of RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

|          |         |     |     |     |                                    | •                         | ,                               |  |  |  |  |

|----------|---------|-----|-----|-----|------------------------------------|---------------------------|---------------------------------|--|--|--|--|

| Register | Devices |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |

| PIE2     | 873     | 874 | 876 | 877 | -r-0 00                            | -r-0 00                   | -r-u uu                         |  |  |  |  |

| PCON     | 873     | 874 | 876 | 877 | dd                                 | uu                        | uu                              |  |  |  |  |

| PR2      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | 1111 1111                       |  |  |  |  |

| SSPADD   | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| SSPSTAT  | 873     | 874 | 876 | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |  |  |  |  |

| TXSTA    | 873     | 874 | 876 | 877 | 0000 -010                          | 0000 -010                 | uuuu -uuu                       |  |  |  |  |

| SPBRG    | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |  |  |  |

| ADRESL   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| ADCON1   | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |  |  |  |  |

| EEDATA   | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |  |  |  |  |

| EEADR    | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| EEDATH   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| EEADRH   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |  |  |  |  |

| EECON1   | 873     | 874 | 876 | 877 | x x000                             | u u000                    | u uuuu                          |  |  |  |  |

| EECON2   | 873     | 874 | 876 | 877 |                                    |                           |                                 |  |  |  |  |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

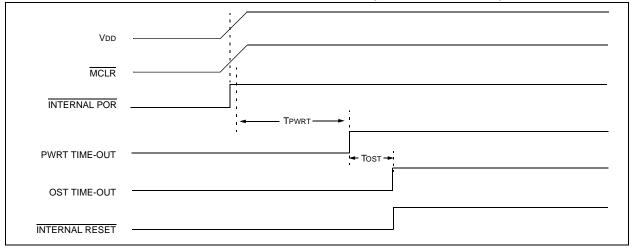

#### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

# PIC16F87X

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in the W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                           |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |  |  |

### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

# 14.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC MCU series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

## 14.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC MCU microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

# 14.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

# PIC16F87X

|                       | >                    | >                                |                                                                    |                                                                                            |                                          |                                | ``````````````````````````````````````               | *                                           |                                  |                                  |                                  |                                                 |                                   | >                                 | >                                  | >                         | >                                 | >                                                 | >                                                   |                             |

|-----------------------|----------------------|----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|------------------------------------------------------|---------------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------------------|-----------------------------------|-----------------------------------|------------------------------------|---------------------------|-----------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|

|                       | _                    | >                                | × × ×                                                              | ~                                                                                          |                                          |                                | >                                                    |                                             |                                  |                                  |                                  |                                                 |                                   | >                                 | >                                  |                           |                                   |                                                   |                                                     |                             |

|                       | _                    | >                                | <b>`</b>                                                           | ~                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       | _                    | >                                | >                                                                  | ~                                                                                          |                                          |                                | >                                                    |                                             |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       | _                    |                                  |                                                                    |                                                                                            |                                          |                                | L                                                    | >                                           |                                  | >                                |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     | <u> </u>                    |

|                       | >                    |                                  | >                                                                  | ~                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 | >                                 |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  |                                                                    |                                                                                            |                                          |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  | >                                |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          |                                          | >                              | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        | *                              | >                                                    | >                                           | <b>*</b> +                       | ,+                               |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | **/                                                                                        |                                          |                                | **/                                                  | **/                                         |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        | *                              | >                                                    | >                                           |                                  | ÷,                               |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  | `                                               |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | `                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

| MBLAB® C17 C Compiler | PLAB® C17 C Compiler | PLAB <sup>®</sup> C18 C Compiler | PASM <sup>TM</sup> Assembler/<br>PLINK <sup>TM</sup> Object Linker | MPLAB <sup>®</sup> ICE In-Circuit Emulator                                                 | ICEPIC <sup>TM</sup> In-Circuit Emulator | PLAB®ICD In-Circuit<br>ebugger | PICSTART® Plus Entry Level<br>Development Programmer | PRO MATE® II<br>Universal Device Programmer | PICDEM™ 1 Demonstration<br>Board | PICDEM™ 2 Demonstration<br>Board | PICDEM™ 3 Demonstration<br>Board | PICDEM <sup>TM</sup> 14A Demonstration<br>Board | PICDEM™ 17 Demonstration<br>Board | EELoo <sup>®</sup> Evaluation Kit | εεLoα <sup>®</sup> Transponder Kit | iicrolD™ Programmer's Kit | 25 kHz microlD™<br>eveloper's Kit | 125 kHz Anticollision microlD™<br>Developer's Kit | 13.56 MHz Anticollision<br>microlD™ Developer's Kit | MCP2510 CAN Developer's Kit |

|                       |                      |                                  |                                                                    | MPLAB® C17 C Compile<br>MPLAB® C18 C Compile<br>MPASM™ Assembler/<br>MPLINK™ Object Linker |                                          |                                |                                                      |                                             |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

| TABLE 14-1: | DEVELOPMENT TOOLS FROM MICROCHIP |

|-------------|----------------------------------|

|-------------|----------------------------------|

© 1998-2013 Microchip Technology Inc.

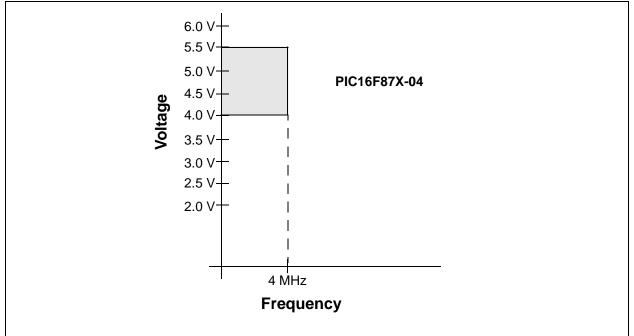

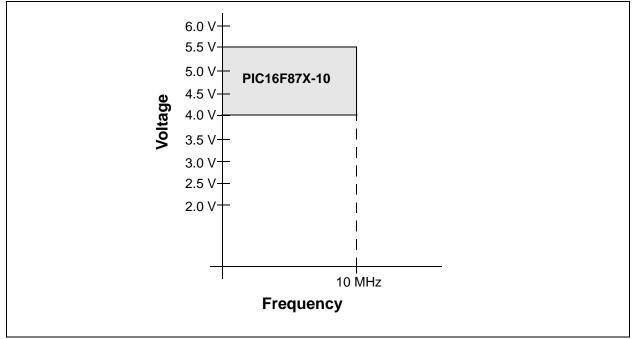

#### FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

# PIC16F87X

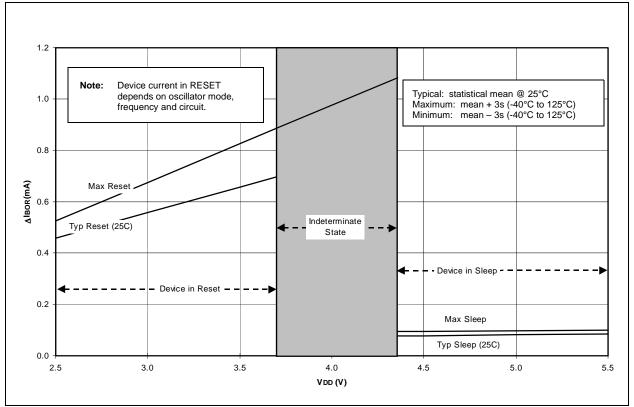

FIGURE 16-12: TYPICAL AND MAXIMUM △ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO 70°C, TIMER1 WITH OSCILLATOR, XTAL=32 kHZ, C1 AND C2=50 pF)

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|

| Pins              | 28/40                                               | 28/40                                                      |

| Timers            | 3                                                   | 3                                                          |

| Interrupts        | 11 or 12                                            | 13 or 14                                                   |

| Communication     | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Slave) | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Master/Slave) |

| Frequency         | 20 MHz                                              | 20 MHz                                                     |

| Voltage           | 2.5V - 5.5V                                         | 2.0V - 5.5V                                                |

| A/D               | 8-bit                                               | 10-bit                                                     |

| CCP               | 2                                                   | 2                                                          |

| Program<br>Memory | 4K, 8K<br>EPROM                                     | 4K, 8K<br>FLASH                                            |

| RAM               | 192, 368<br>bytes                                   | 192, 368<br>bytes                                          |

| EEPROM data       | None                                                | 128, 256<br>bytes                                          |

| Other             | _                                                   | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming      |

# INDEX

Α

| A/D                                        |

|--------------------------------------------|

| Acquisition Requirements                   |

| ADCON0 Register                            |

| ADCON1 Register                            |

| ADIF bit                                   |

| Analog Input Model Block Diagram           |

| Analog Port Pins                           |

| Associated Registers and Bits              |

| Block Diagram                              |

| Calculating Acquisition Time114            |

| Configuring Analog Port Pins               |

| Configuring the Interrupt                  |

| Configuring the Module113                  |

| Conversion Clock                           |

| Conversions                                |

| Delays                                     |

| Effects of a RESET117                      |

| GO/DONE bit                                |

| Internal Sampling Switch (Rss) Impedence   |

| Operation During SLEEP                     |

| Result Registers                           |

| Sampling Requirements                      |

| Source Impedence                           |

| Time Delays114                             |

| Absolute Maximum Ratings                   |

| ACK                                        |

| Acknowledge Data bit                       |

| Acknowledge Pulse                          |

| Acknowledge Sequence Enable bit            |

| Acknowledge Status bit                     |

| ADRES Register                             |

| Analog Port Pins. See A/D                  |

| Analog-to-Digital Converter. See A/D       |

| Application Notes                          |

| AN552 (Implementing Wake-up on Key Strokes |

| Using PIC16CXXX)                           |

| AN556 (Implementing a Table Read)          |

| AN578 (Use of the SSP Module in the I2C    |

| Multi-Master Environment)                  |

| Architecture                               |

| PIC16F873/PIC16F876 Block Diagram5         |

| PIC16F874/PIC16F877 Block Diagram          |

| Assembler                                  |

| MPASM Assembler143                         |

|                                            |

| В                                          |

| Banking, Data Memory 12, 18                |

| Baud Rate Generator                        |

| BCLIF                                      |

| BF                                         |

| Block Diagrams                             |

| A/D                                        |

| A/D Converter113                           |

Analog Input Model

114

Baud Rate Generator

79

Capture Mode

59

Compare Mode

60

I<sup>2</sup>C Master Mode

78

I<sup>2</sup>C Module

73

I<sup>2</sup>C Slave Mode

73

Interrupt Logic

129

PIC16F873/PIC16F876

5

| PIC16F874/PIC16F877                             | 6        |

|-------------------------------------------------|----------|

| PORTA                                           |          |

| RA3:RA0 and RA5 Pins                            |          |

| RA4/T0CKI Pin                                   | 29       |

| PORTB                                           |          |

| RB3:RB0 Port Pins                               |          |

| RB7:RB4 Port Pins                               | 31       |

| PORTC                                           |          |

| Peripheral Output Override (RC 0:2, 5:7)        |          |

| Peripheral Output Override (RC 3:4)             |          |

| PORTD                                           |          |

| PORTD and PORTE (Parallel Slave Port)           |          |

| PORTE                                           | 36       |

| PWM Mode                                        | 61       |

| RESET Circuit                                   | 123      |

| SSP (I <sup>2</sup> C Mode)                     | 73       |

| SSP (SPI Mode)                                  |          |

| Timer0/WDT Prescaler                            | 47       |

| Timer1                                          | 52       |

| Timer2                                          | 55       |

| USART Asynchronous Receive                      | 101      |

| USART Asynchronous Receive (9-bit Mode)         | 103      |

| USART Transmit                                  | 99       |

| Watchdog Timer                                  | 131      |

| BOR. See Brown-out Reset                        |          |

| BRG                                             | 79       |

| BRGH bit                                        |          |

| Brown-out Reset (BOR) 119, 123, 7               | 125, 126 |

| BOR Status (BOR Bit)                            | 25       |

| Buffer Full bit, BF                             | 74       |

| Bus Arbitration                                 | 89       |

| Bus Collision Section                           | 89       |

| Bus Collision During a Repeated START Condition | 92       |

| Bus Collision During a START Condition          |          |

| Bus Collision During a STOP Condition           | 93       |

| Bus Collision Interrupt Flag bit, BCLIF         | 24       |

|                                                 |          |

#### С

| Capture/Compare/PWM (CCP)              | 57   |

|----------------------------------------|------|

| Associated Registers                   |      |

| Capture, Compare and Timer1            | 62   |

| PWM and Timer2                         | 63   |

| Capture Mode                           | 59   |

| Block Diagram                          | 59   |

| CCP1CON Register                       | 58   |

| CCP1IF                                 | 59   |

| Prescaler                              | 59   |

| CCP Timer Resources                    | 57   |

| CCP1                                   |      |

| RC2/CCP1 Pin                           | 7, 9 |

| CCP2                                   |      |

| RC1/T1OSI/CCP2 Pin                     | 7, 9 |

| Compare                                |      |

| Special Trigger Output of CCP1         | 60   |

| Special Trigger Output of CCP2         | 60   |

| Compare Mode                           | 60   |

| Block Diagram                          | 60   |

| Software Interrupt Mode                |      |

| Special Event Trigger                  | 60   |

| Interaction of Two CCP Modules (table) | 57   |

|                                        |      |

# PIC16F87X