### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

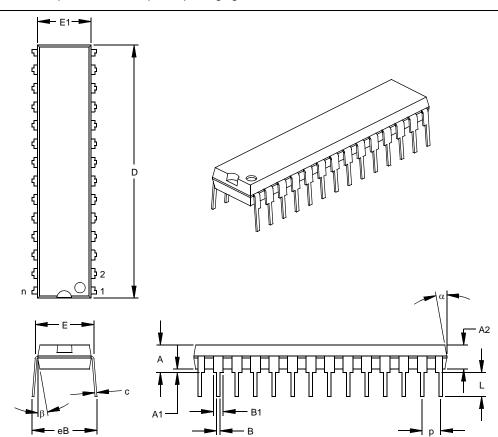

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-10e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                                                                                                                                                                                                                                                          | File<br>Address | A                              | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|--|--|

| Indirect addr. <sup>(*)</sup>                                                                                                                                                                                                                              | 00h             | Indirect addr.(*)              | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |  |  |

| TMR0                                                                                                                                                                                                                                                       | 01h             | OPTION_REG                     | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |  |  |

| PCL                                                                                                                                                                                                                                                        | 02h             | PCL                            | 82h            | PCL                 | 102h            | PCL                     | 182h           |  |  |

| STATUS                                                                                                                                                                                                                                                     | 03h             | STATUS                         | 83h            | STATUS              | 103h            | STATUS                  | 183h           |  |  |

| FSR                                                                                                                                                                                                                                                        | 04h             | FSR                            | 84h            | FSR                 | 104h            | FSR                     | 184h           |  |  |

| PORTA                                                                                                                                                                                                                                                      | 05h             | TRISA                          | 85h            |                     | 105h            |                         | 185h           |  |  |

| PORTB                                                                                                                                                                                                                                                      | 06h             | TRISB                          | 86h            | PORTB               | 106h            | TRISB                   | 186h           |  |  |

| PORTC                                                                                                                                                                                                                                                      | 07h             | TRISC                          | 87h            |                     | 107h            |                         | 187h           |  |  |

| PORTD <sup>(1)</sup>                                                                                                                                                                                                                                       | 08h             | TRISD <sup>(1)</sup>           | 88h            |                     | 108h            |                         | 188h           |  |  |

| PORTE <sup>(1)</sup>                                                                                                                                                                                                                                       | 09h             | TRISE <sup>(1)</sup>           | 89h            |                     | 109h            |                         | 189h           |  |  |

| PCLATH                                                                                                                                                                                                                                                     | 0Ah             | PCLATH                         | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |  |  |

| INTCON                                                                                                                                                                                                                                                     | 0Bh             | INTCON                         | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |  |  |

| PIR1                                                                                                                                                                                                                                                       | 0Ch             | PIE1                           | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |  |  |

| PIR2                                                                                                                                                                                                                                                       | 0Dh             | PIE2                           | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |  |  |

| TMR1L                                                                                                                                                                                                                                                      | 0Eh             | PCON                           | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |  |  |

| TMR1H                                                                                                                                                                                                                                                      | 0Fh             |                                | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |  |  |

| T1CON                                                                                                                                                                                                                                                      | 10h             |                                | 90h            |                     | 110h            |                         | 190h           |  |  |

| TMR2                                                                                                                                                                                                                                                       | 11h             | SSPCON2                        | 91h            |                     |                 |                         |                |  |  |

| T2CON                                                                                                                                                                                                                                                      | 12h             | PR2                            | 92h            |                     |                 |                         |                |  |  |

| SSPBUF                                                                                                                                                                                                                                                     | 13h             | SSPADD                         | 93h            |                     |                 |                         |                |  |  |

| SSPCON                                                                                                                                                                                                                                                     | 14h             | SSPSTAT                        | 94h            |                     |                 |                         |                |  |  |

| CCPR1L                                                                                                                                                                                                                                                     | 15h             |                                | 95h            |                     |                 |                         |                |  |  |

| CCPR1H                                                                                                                                                                                                                                                     | 16h             |                                | 96h            |                     |                 |                         |                |  |  |

| CCP1CON                                                                                                                                                                                                                                                    | 17h             |                                | 97h            |                     |                 |                         |                |  |  |

| RCSTA                                                                                                                                                                                                                                                      | 18h             | TXSTA                          | 98h            |                     |                 |                         |                |  |  |

| TXREG                                                                                                                                                                                                                                                      | 19h             | SPBRG                          | 99h            |                     |                 |                         |                |  |  |

| RCREG                                                                                                                                                                                                                                                      | 1Ah             |                                | 9Ah            |                     |                 |                         |                |  |  |

| CCPR2L                                                                                                                                                                                                                                                     | 1Bh             |                                | 9Bh            |                     |                 |                         |                |  |  |

| CCPR2H                                                                                                                                                                                                                                                     | 1Ch             |                                | 9Ch            |                     |                 |                         |                |  |  |

| CCP2CON                                                                                                                                                                                                                                                    | 1Dh             |                                | 9Dh            |                     |                 |                         |                |  |  |

| ADRESH                                                                                                                                                                                                                                                     | 1Eh             | ADRESL                         | 9Eh            |                     |                 |                         |                |  |  |

| ADCON0                                                                                                                                                                                                                                                     | 1Fh             | ADCON1                         | 9Fh            |                     | 1206            |                         | 1A0h           |  |  |

|                                                                                                                                                                                                                                                            | 20h             |                                | A0h            |                     | 120h            |                         |                |  |  |

| General<br>Purpose<br>Register                                                                                                                                                                                                                             |                 | General<br>Purpose<br>Register |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |  |  |

| 96 Bytes                                                                                                                                                                                                                                                   |                 | 96 Bytes                       |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |  |  |

|                                                                                                                                                                                                                                                            | 754             |                                |                |                     | 1756            |                         | 4              |  |  |

| Bank 0                                                                                                                                                                                                                                                     | J 7Fh           | Bank 1                         | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |  |  |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>* Not a physical register.</li> <li>Note 1: These registers are not implemented on the PIC16F873.</li> <li>2: These registers are reserved, maintain these registers clear.</li> </ul> |                 |                                |                |                     |                 |                         |                |  |  |

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, and the EEPROM write operation interrupt.

### REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

|         | U-0                                      | R/W-0                                         | U-0          | R/W-0        | R/W-0          | U-0       | U-0            | R/W-0  |  |  |  |  |  |

|---------|------------------------------------------|-----------------------------------------------|--------------|--------------|----------------|-----------|----------------|--------|--|--|--|--|--|

|         | —                                        | Reserved                                      | —            | EEIE         | BCLIE          | —         | —              | CCP2IE |  |  |  |  |  |

|         | bit 7                                    |                                               |              |              |                |           |                | bit 0  |  |  |  |  |  |

|         |                                          |                                               |              |              |                |           |                |        |  |  |  |  |  |

| bit 7   | Unimplem                                 | ented: Read                                   | as '0'       |              |                |           |                |        |  |  |  |  |  |

| bit 6   | Reserved: Always maintain this bit clear |                                               |              |              |                |           |                |        |  |  |  |  |  |

| bit 5   | Unimplemented: Read as '0'               |                                               |              |              |                |           |                |        |  |  |  |  |  |

| bit 4   | EEIE: EEP                                | EEIE: EEPROM Write Operation Interrupt Enable |              |              |                |           |                |        |  |  |  |  |  |

|         | 1 = Enable                               | EE Write Int                                  | errupt       |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                              | e EE Write In                                 | terrupt      |              |                |           |                |        |  |  |  |  |  |

| bit 3   | BCLIE: Bu                                | s Collision In                                | terrupt Ena  | able         |                |           |                |        |  |  |  |  |  |

|         | 1 = Enable                               | Bus Collisio                                  | n Interrupt  |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                              | e Bus Collisio                                | on Interrupt |              |                |           |                |        |  |  |  |  |  |

| bit 2-1 | Unimplem                                 | ented: Read                                   | as '0'       |              |                |           |                |        |  |  |  |  |  |

| bit 0   | CCP2IE: C                                | CP2 Interrup                                  | t Enable b   | it           |                |           |                |        |  |  |  |  |  |

|         | 1 = Enable                               | s the CCP2 i                                  | nterrupt     |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                              | es the CCP2                                   | interrupt    |              |                |           |                |        |  |  |  |  |  |

|         |                                          |                                               |              |              |                |           |                |        |  |  |  |  |  |

|         | Legend:                                  |                                               |              |              |                |           |                |        |  |  |  |  |  |

|         | R = Reada                                | ble bit                                       | VV = V       | Vritable bit | U = Unimpl     | emented b | oit, read as ' | 0'     |  |  |  |  |  |

|         | - n = Value                              | at POR                                        | '1' = E      | Bit is set   | '0' = Bit is c | leared    | x = Bit is u   | nknown |  |  |  |  |  |

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

|         | U-0           | U-0                                                | R/W-0           | R/W-0          | R/W-0             | R/W-0       | R/W-0         | R/W-0  |  |  |  |  |  |

|---------|---------------|----------------------------------------------------|-----------------|----------------|-------------------|-------------|---------------|--------|--|--|--|--|--|

|         | _             | _                                                  | T1CKPS1         | T1CKPS0        | T1OSCEN           | T1SYNC      | TMR1CS        | TMR10N |  |  |  |  |  |

|         | bit 7         |                                                    |                 |                |                   |             |               | bit 0  |  |  |  |  |  |

|         |               |                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

| bit 7-6 | Unimplem      | ented: Rea                                         | id as '0'       |                |                   |             |               |        |  |  |  |  |  |

| bit 5-4 | T1CKPS1:      | T1CKPS0:                                           | Timer1 Inpu     | t Clock Pres   | cale Select bit   | 5           |               |        |  |  |  |  |  |

|         |               | 1 = 1:8 Prescale value                             |                 |                |                   |             |               |        |  |  |  |  |  |

|         |               | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value |                 |                |                   |             |               |        |  |  |  |  |  |

|         | • = • • • • • | rescale valu                                       |                 |                |                   |             |               |        |  |  |  |  |  |

| bit 3   | T1OSCEN       | OSCEN: Timer1 Oscillator Enable Control bit        |                 |                |                   |             |               |        |  |  |  |  |  |

|         | 1 = Oscillat  | tor is enable                                      | ed              |                |                   |             |               |        |  |  |  |  |  |

|         | 0 = Oscillat  | tor is shut-c                                      | off (the oscill | ator inverter  | is turned off to  | eliminate p | ower drain    | )      |  |  |  |  |  |

| bit 2   | T1SYNC: 7     | Timer1 Exte                                        | rnal Clock Ir   | nput Synchro   | onization Contr   | ol bit      |               |        |  |  |  |  |  |

|         | When TMF      |                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

|         |               | •                                                  | e external cl   |                |                   |             |               |        |  |  |  |  |  |

|         | When TMR      |                                                    | nal clock inp   | Jul            |                   |             |               |        |  |  |  |  |  |

|         |               |                                                    | ner1 uses th    | e internal clo | ock when TMR      | 1CS = 0.    |               |        |  |  |  |  |  |

| bit 1   | TMR1CS:       | -<br>Timer1 Cloo                                   | k Source So     | elect bit      |                   |             |               |        |  |  |  |  |  |

|         |               |                                                    | •               | 10SO/T1Ck      | (I (on the rising | edge)       |               |        |  |  |  |  |  |

|         | 0 = Interna   | I clock (Fos                                       | sc/4)           |                |                   |             |               |        |  |  |  |  |  |

| bit 0   | TMR10N:       |                                                    | bit             |                |                   |             |               |        |  |  |  |  |  |

|         | 1 = Enable    |                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

|         | 0 = Stops 7   | imer1                                              |                 |                |                   |             |               |        |  |  |  |  |  |

|         | · · ·         |                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

|         | Legend:       |                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

|         | R = Reada     |                                                    |                 | Vritable bit   | U = Unimpl        |             |               |        |  |  |  |  |  |

|         | - n = Value   | at POR                                             | '1' = E         | Bit is set     | '0' = Bit is c    | leared      | x = Bit is ur | nknown |  |  |  |  |  |

### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                                                                  | Freq.      | C1                      | C2       |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------|----------|--|--|--|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                        | 32 kHz     | 33 pF                   | 33 pF    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 100 kHz    | 15 pF                   | 15 pF    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 200 kHz    | 15 pF                   | 15 pF    |  |  |  |  |  |  |  |

| These values are for design guidance only.                                                                                                                                                                                                                                                                                                                |            |                         |          |  |  |  |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                                                                          |            |                         |          |  |  |  |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                                                                | Epson C-00 | 1R32.768K-A             | ± 20 PPM |  |  |  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                                                                   | Epson C-2  | -2 100.00 KC-P ± 20 PPM |          |  |  |  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                                                                   | STD XTL    | 200.000 kHz             | ± 20 PPM |  |  |  |  |  |  |  |

| <ul> <li>200 kHz STD XTL 200.000 kHz ± 20 PPM</li> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |            |                         |          |  |  |  |  |  |  |  |

### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

|       | R/W-0                  | R/W-0                                                          | R/W-0                       | R/W-0                      | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |

|-------|------------------------|----------------------------------------------------------------|-----------------------------|----------------------------|-------------------------|---------------|---------------|-------------|

|       | GCEN                   | ACKSTAT                                                        | ACKDT                       | ACKEN                      | RCEN                    | PEN           | RSEN          | SEN         |

|       | bit 7                  |                                                                |                             |                            |                         |               |               | bit 0       |

| bit 7 | 1 = Enable             | eneral Call En<br>e interrupt whe                              | en a genera                 |                            |                         | received in   | the SSPSR     | 2           |

| bit 6 | ACKSTAT                | Acknowledg                                                     | e Status bit                | (In I <sup>2</sup> C Maste | er mode onl             | у)            |               |             |

|       | 1 = Acknow             | <u>Transmit mod</u><br>wledge was n<br>wledge was re           | ot received                 |                            |                         |               |               |             |

| bit 5 | ACKDT: A               | cknowledge [                                                   | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m    | ode only)               |               |               |             |

|       | Value that end of a re | knowledge                                                      |                             | the user initi             | ates an Ack             | nowledge s    | equence at    | the         |

| bit 4 | ACKEN: A               | cknowledge \$                                                  | Sequence E                  | nable bit (In              | I <sup>2</sup> C Master | mode only)    |               |             |

|       | 1 = Initiate<br>Autom  | Receive mode<br>Acknowledge<br>atically cleare<br>wledge seque | e sequence<br>ed by hardw   |                            | I SCL pins a            | and transmit  | ACKDT da      | ta bit.     |

| bit 3 | RCEN: Re               | ceive Enable<br>es Receive mo                                  | bit (In I <sup>2</sup> C M  | laster mode                | only)                   |               |               |             |

| bit 2 | PEN: STC               | P Condition I                                                  | Enable bit (I               | n I <sup>2</sup> C Master  | r mode only             | )             |               |             |

|       | 1 = Initiate           | ase Control:<br>STOP condit<br>condition idle                  |                             | and SCL pir                | ns. Automat             | ically cleare | d by hardwa   | are.        |

| bit 1 | 1 = Initiate           | epeated STAR<br>Repeated ST/<br>ted START co                   | ART conditic                | on on SDA an               |                         |               |               | / hardware. |

| bit 0 | 1 = Initiate           | RT Condition<br>START cond<br>condition idl                    | lition on SD/               |                            |                         |               | ed by hardv   | vare.       |

|       |                        | For bits ACK<br>mode, this bit<br>writes to the \$             | may not be                  | set (no spo                |                         |               |               |             |

|       | Logondi                |                                                                |                             |                            |                         |               |               |             |

|       | Legend:<br>R = Reada   | blo bit                                                        | ۱۸/ _ ۱۸/-                  | itable bit                 |                         | plemented k   | hit road as f | 0'          |

|       | K = Keaua              |                                                                | vv = vvi                    |                            | 0 = 0.000               |               | n, reau as    | 0           |

'1' = Bit is set

'0' = Bit is cleared

### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

### 9.1.2 SLAVE MODE

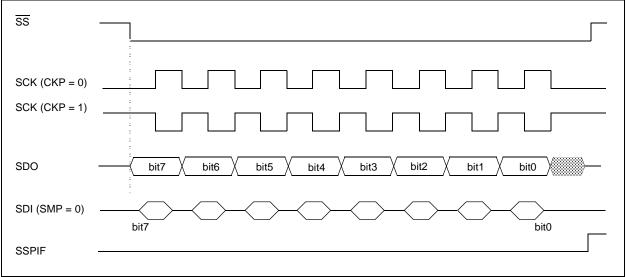

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

### FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

### TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|---------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ve Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р       | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                          | R/W-0         | R/W-0        | R/W-0          | U-0            | R/W-0     | R-1           | R/W-0      |

|-------|--------------------------------|---------------|--------------|----------------|----------------|-----------|---------------|------------|

|       | CSRC                           | TX9           | TXEN         | SYNC           | _              | BRGH      | TRMT          | TX9D       |

|       | bit 7                          |               |              |                |                |           |               | bit 0      |

|       |                                |               |              |                |                |           |               |            |

| bit 7 | CSRC: Cloc                     |               | lect bit     |                |                |           |               |            |

|       | Asynchronou<br>Don't care      | us mode:      |              |                |                |           |               |            |

|       | Synchronou                     | s mode:       |              |                |                |           |               |            |

|       | 1 = Master n                   |               | generated ir | nternally from | n BRG)         |           |               |            |

|       | 0 = Slave m                    | ode (clock fr | om external  | source)        |                |           |               |            |

| bit 6 | TX9: 9-bit Tr                  |               |              |                |                |           |               |            |

|       | 1 = Selects 9<br>0 = Selects 8 |               |              |                |                |           |               |            |

| bit 5 | TXEN: Tran                     | smit Enable   | bit          |                |                |           |               |            |

|       | 1 = Transmit                   |               |              |                |                |           |               |            |

|       | 0 = Transmit                   | tdisabled     |              |                |                |           |               |            |

|       | Note: SREN                     | I/CREN ovei   | rides TXEN   | in SYNC m      | ode.           |           |               |            |

| bit 4 |                                | RT Mode S     | elect bit    |                |                |           |               |            |

|       | 1 = Synchro<br>0 = Asynchro    |               |              |                |                |           |               |            |

| bit 3 | Unimpleme                      |               |              |                |                |           |               |            |

| bit 2 | BRGH: High                     |               |              |                |                |           |               |            |

|       | Asynchrono                     |               | 000000       |                |                |           |               |            |

|       | 1 = High spe                   | ed            |              |                |                |           |               |            |

|       | 0 = Low spe                    |               |              |                |                |           |               |            |

|       | Synchronous<br>Unused in th    |               |              |                |                |           |               |            |

| bit 1 | TRMT: Trans                    |               | aister Statu | s bit          |                |           |               |            |

|       | 1 = TSR em                     |               | 9            |                |                |           |               |            |

|       | 0 = TSR full                   |               |              |                |                |           |               |            |

| bit 0 | <b>TX9D:</b> 9th b             | it of Transmi | t Data, can  | be parity bit  |                |           |               |            |

|       | Logondi                        |               |              |                |                |           |               |            |

|       | Legend:<br>R = Readab          | la hit        | W = Wri      | tahla hit      | U = Unimple    | amonted b | it road as "  | <b>)</b> ' |

|       | - n = Value a                  |               | '1' = Bit    |                | '0' = Bit is c |           | x = Bit is ur |            |

|       |                                |               | i – Dil      | 10 301         |                |           |               | IN IOWIT   |

### TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| DAUD              | Fosc = 20 MHz |                             |       | F          | osc = 16 N                  | IHz   | F          | Fosc = 10 MHz               |     |  |  |

|-------------------|---------------|-----------------------------|-------|------------|-----------------------------|-------|------------|-----------------------------|-----|--|--|

| RATE<br>(K) KBAUD | %<br>ERROR    | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |     |  |  |

| 0.3               | -             | -                           | -     | -          | -                           | -     | -          | -                           | -   |  |  |

| 1.2               | 1.221         | 1.75                        | 255   | 1.202      | 0.17                        | 207   | 1.202      | 0.17                        | 129 |  |  |

| 2.4               | 2.404         | 0.17                        | 129   | 2.404      | 0.17                        | 103   | 2.404      | 0.17                        | 64  |  |  |

| 9.6               | 9.766         | 1.73                        | 31    | 9.615      | 0.16                        | 25    | 9.766      | 1.73                        | 15  |  |  |

| 19.2              | 19.531        | 1.72                        | 15    | 19.231     | 0.16                        | 12    | 19.531     | 1.72                        | 7   |  |  |

| 28.8              | 31.250        | 8.51                        | 9     | 27.778     | 3.55                        | 8     | 31.250     | 8.51                        | 4   |  |  |

| 33.6              | 34.722        | 3.34                        | 8     | 35.714     | 6.29                        | 6     | 31.250     | 6.99                        | 4   |  |  |

| 57.6              | 62.500        | 8.51                        | 4     | 62.500     | 8.51                        | 3     | 52.083     | 9.58                        | 2   |  |  |

| HIGH              | 1.221         | -                           | 255   | 0.977      | -                           | 255   | 0.610      | -                           | 255 |  |  |

| LOW               | 312.500       | -                           | 0     | 250.000    | -                           | 0     | 156.250    | -                           | 0   |  |  |

| DAUD                |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |

|---------------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |

| 1.2                 | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |

| 2.4                 | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |

| 9.6                 | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |

| 19.2                | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |

| 28.8                | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |

| 33.6                | -      | -          | -                           | -                 | -          | -                           |  |

| 57.6                | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |

| HIGH                | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |

| LOW                 | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |

### TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD              | Fosc = 20 MHz |                             | Hz    | F          | osc = 16 M                  | Hz    | Fosc = 10 MHz |                             |     |  |

|-------------------|---------------|-----------------------------|-------|------------|-----------------------------|-------|---------------|-----------------------------|-----|--|

| RATE<br>(K) KBAUD | %<br>ERROR    | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR    | SPBRG<br>value<br>(decimal) |     |  |

| 0.3               | -             | -                           | -     | -          | -                           | -     | -             | -                           | -   |  |

| 1.2               | -             | -                           | -     | -          | -                           | -     | -             | -                           | -   |  |

| 2.4               | -             | -                           | -     | -          | -                           | -     | 2.441         | 1.71                        | 255 |  |

| 9.6               | 9.615         | 0.16                        | 129   | 9.615      | 0.16                        | 103   | 9.615         | 0.16                        | 64  |  |

| 19.2              | 19.231        | 0.16                        | 64    | 19.231     | 0.16                        | 51    | 19.531        | 1.72                        | 31  |  |

| 28.8              | 29.070        | 0.94                        | 42    | 29.412     | 2.13                        | 33    | 28.409        | 1.36                        | 21  |  |

| 33.6              | 33.784        | 0.55                        | 36    | 33.333     | 0.79                        | 29    | 32.895        | 2.10                        | 18  |  |

| 57.6              | 59.524        | 3.34                        | 20    | 58.824     | 2.13                        | 16    | 56.818        | 1.36                        | 10  |  |

| HIGH              | 4.883         | -                           | 255   | 3.906      | -                           | 255   | 2.441         | -                           | 255 |  |

| LOW               | 1250.000      | -                           | 0     | 1000.000   |                             | 0     | 625.000       | -                           | 0   |  |

| BAUD        | F       | osc = 4 MH | łz                          | Fos   | c = 3.6864 | MHz                         |

|-------------|---------|------------|-----------------------------|-------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -     | -          | -                           |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2   | 0          | 191                         |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4   | 0          | 95                          |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6   | 0          | 23                          |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2  | 0          | 11                          |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8  | 0          | 7                           |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9  | 2.04       | 6                           |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6  | 0          | 3                           |

| HIGH        | 0.977   | -          | 255                         | 0.9   | -          | 255                         |

| LOW         | 250.000 | -          | 0                           | 230.4 | -          | 0                           |

### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                                | Name   | Bit 7                | Bit 6                  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|----------------------------------------|--------|----------------------|------------------------|-------|-------|-------|--------|-----------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE                   | TOIE  | INTE  | RBIE  | T0IF   | INTF      | R0IF      | 0000 000x                | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9                    | SREN  | CREN  | ADDEN | FERR   | OERR      | RX9D      | 0000 000x                | 0000 000x                       |

| 1Ah                                    | RCREG  | USART R              | JSART Receive Register |       |       |       |        |           |           | 0000 0000                | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9                    | TXEN  | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010                | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |                        |       |       |       |        | 0000 0000 | 0000 0000 |                          |                                 |

### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note** 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.

NOTES:

|          |         |     |                                    |                           |                                 | ,         |           |  |

|----------|---------|-----|------------------------------------|---------------------------|---------------------------------|-----------|-----------|--|

| Register | Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |           |           |  |

| PIE2     | 873     | 874 | 876                                | 877                       | -r-0 00                         | -r-0 00   | -r-u uu   |  |

| PCON     | 873     | 874 | 876                                | 877                       | dd                              | uu        | uu        |  |

| PR2      | 873     | 874 | 876                                | 877                       | 1111 1111                       | 1111 1111 | 1111 1111 |  |

| SSPADD   | 873     | 874 | 876                                | 877                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| SSPSTAT  | 873     | 874 | 876                                | 877                       | 00 0000                         | 00 0000   | uu uuuu   |  |

| TXSTA    | 873     | 874 | 876                                | 877                       | 0000 -010                       | 0000 -010 | uuuu -uuu |  |

| SPBRG    | 873     | 874 | 876                                | 877                       | 0000 0000                       | 0000 0000 | uuuu uuuu |  |

| ADRESL   | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |  |

| ADCON1   | 873     | 874 | 876                                | 877                       | 0 0000                          | 0 0000    | u uuuu    |  |

| EEDATA   | 873     | 874 | 876                                | 877                       | 0 0000                          | 0 0000    | u uuuu    |  |

| EEADR    | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |  |

| EEDATH   | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |  |

| EEADRH   | 873     | 874 | 876                                | 877                       | XXXX XXXX                       | սսսս սսսս | uuuu uuuu |  |

| EECON1   | 873     | 874 | 876                                | 877                       | x x000                          | u u000    | u uuuu    |  |

| EECON2   | 873     | 874 | 876                                | 877                       |                                 |           |           |  |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

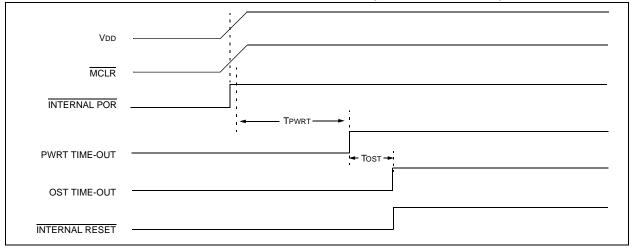

### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

### 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

### 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                       |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| PIC16LF8<br>(Comme             | 73/874/87<br>rcial, Indu |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |      |      |                                               |  |