Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-10e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin# | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|----------------|-------------------|-------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13             | 14                | 30          | I                    | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14             | 15                | 31          | 0                    | —                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1              | 2                 | 18          | I/P                  | ST                     | Master Clear (Reset) input or programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                        |

|                   |                |                   |             |                      |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2              | 3                 | 19          | I/O                  | TTL                    | RA0 can also be analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 3              | 4                 | 20          | I/O                  | TTL                    | RA1 can also be analog input1.                                                                                                                                                                                    |

| RA2/AN2/VREF-     | 4              | 5                 | 21          | I/O                  | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                               |

| RA3/AN3/VREF+     | 5              | 6                 | 22          | I/O                  | TTL                    | RA3 can also be analog input3 or positive<br>analog reference voltage.                                                                                                                                            |

| RA4/T0CKI         | 6              | 7                 | 23          | I/O                  | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                          |

| RA5/SS/AN4        | 7              | 8                 | 24          | I/O                  | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                                |

|                   |                |                   |             |                      |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33             | 36                | 8           | I/O                  | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1               | 34             | 37                | 9           | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB2               | 35             | 38                | 10          | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB3/PGM           | 36             | 39                | 11          | I/O                  | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                                |

| RB4               | 37             | 41                | 14          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB5               | 38             | 42                | 15          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB6/PGC           | 39             | 43                | 16          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                                  |

| RB7/PGD           | 40             | 44                | 17          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                                   |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |             | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

|         | U-0                        | U-0                                                      | R/W-0           | R/W-0          | R/W-0             | R/W-0       | R/W-0         | R/W-0  |  |  |  |  |  |

|---------|----------------------------|----------------------------------------------------------|-----------------|----------------|-------------------|-------------|---------------|--------|--|--|--|--|--|

|         | _                          | _                                                        | T1CKPS1         | T1CKPS0        | T1OSCEN           | T1SYNC      | TMR1CS        | TMR10N |  |  |  |  |  |

|         | bit 7                      |                                                          |                 |                |                   |             |               | bit 0  |  |  |  |  |  |

|         |                            |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0' |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

| bit 5-4 | T1CKPS1:                   | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits |                 |                |                   |             |               |        |  |  |  |  |  |

|         |                            | rescale valu                                             |                 |                |                   |             |               |        |  |  |  |  |  |

|         |                            | rescale valu                                             |                 |                |                   |             |               |        |  |  |  |  |  |

|         | • = • • • • •              | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value       |                 |                |                   |             |               |        |  |  |  |  |  |

| bit 3   | T1OSCEN                    | : Timer1 Os                                              | cillator Enal   | ble Control b  | it                |             |               |        |  |  |  |  |  |

|         | 1 = Oscillat               | tor is enable                                            | ed              |                |                   |             |               |        |  |  |  |  |  |

|         | 0 = Oscillat               | tor is shut-c                                            | off (the oscill | ator inverter  | is turned off to  | eliminate p | ower drain    | )      |  |  |  |  |  |

| bit 2   | T1SYNC: 7                  | Timer1 Exte                                              | rnal Clock Ir   | nput Synchro   | onization Contr   | ol bit      |               |        |  |  |  |  |  |

|         | When TMF                   |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

|         |                            | •                                                        | e external cl   |                |                   |             |               |        |  |  |  |  |  |

|         | When TMR                   |                                                          | nal clock inp   | Jul            |                   |             |               |        |  |  |  |  |  |

|         |                            |                                                          | ner1 uses th    | e internal clo | ock when TMR      | 1CS = 0.    |               |        |  |  |  |  |  |

| bit 1   | TMR1CS:                    | -<br>Timer1 Cloo                                         | k Source Se     | elect bit      |                   |             |               |        |  |  |  |  |  |

|         |                            |                                                          | •               | 10SO/T1Ck      | (I (on the rising | edge)       |               |        |  |  |  |  |  |

|         | 0 = Interna                | I clock (Fos                                             | sc/4)           |                |                   |             |               |        |  |  |  |  |  |

| bit 0   | TMR10N:                    |                                                          | bit             |                |                   |             |               |        |  |  |  |  |  |

|         | 1 = Enable                 |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

|         | 0 = Stops 7                | imer1                                                    |                 |                |                   |             |               |        |  |  |  |  |  |

|         | · · ·                      |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

|         | Legend:                    |                                                          |                 |                |                   |             |               |        |  |  |  |  |  |

|         | R = Reada                  |                                                          |                 | Vritable bit   | U = Unimpl        |             |               |        |  |  |  |  |  |

|         | - n = Value                | at POR                                                   | '1' = E         | Bit is set     | '0' = Bit is c    | leared      | x = Bit is ur | nknown |  |  |  |  |  |

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

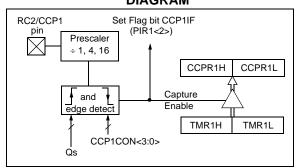

## 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### CCP1 Module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

#### CCP2 Module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

## TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                          |

|-----------|-----------|--------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)               |

| PWM       | Capture   | None                                                                                 |

| PWM       | Compare   | None                                                                                 |

## 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

The type of event is configured by control bits CCP1M3:CCP1M0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

#### 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in operating mode.

#### 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | •           |   |                        |

|-------|-------------|---|------------------------|

| CLRF  | CCP1CON     | ; | Turn CCP module off    |

| MOVLW | NEW_CAPT_PS | ; | Load the W reg with    |

|       |             | ; | the new prescaler      |

|       |             | ; | move value and CCP ON  |

| MOVWF | CCP1CON     | ; | Load CCP1CON with this |

|       |             | ; | value                  |

|       |             |   |                        |

| 1     |             |   |                        |

## 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Figure 9-1 shows a block diagram for the SPI mode, while Figure 9-5 and Figure 9-9 show the block diagrams for the two different  $I^2C$  modes of operation.

The Application Note AN734, "Using the PIC<sup>®</sup> MCU SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication" describes the slave operation of the MSSP module on the PIC16F87X devices. AN735, "Using the PIC<sup>®</sup> MCU MSSP Module for I<sup>2</sup>C<sup>TM</sup> Communications" describes the master operation of the MSSP module on the PIC16F87X devices.

### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined. It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name                                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|----------------------------------------|-------|-------|-------|-------|-------|-----------|-----------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA                                  | CSRC  | TX9   | TXEN  | SYNC  |       | BRGH      | TRMT      | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA                                  | SPEN  | RX9   | SREN  | CREN  | ADDEN | 0000 000x | 0000 000x |       |                          |                                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |       |       |       |       |       |           |           |       | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE      | INTE      | RBIE  | T0IF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R | egister   |           |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Genera | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note** 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.

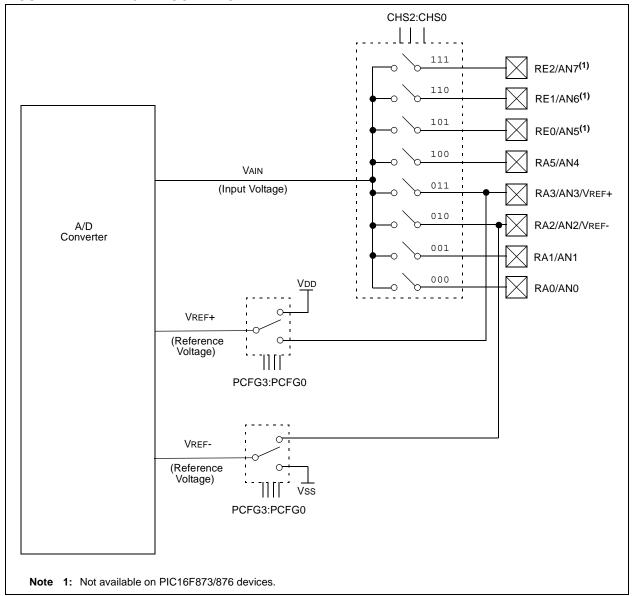

## PIC16F87X

#### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

#### bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | А          | А          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before the next acquisition starts.

#### FIGURE 11-1: A/D BLOCK DIAGRAM

### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock                | AD Clock Source (TAD) |          |  |  |

|-------------------------|-----------------------|----------|--|--|

| Operation               | ADCS1:ADCS0           | Max.     |  |  |

| 2Tosc                   | 0 0                   | 1.25 MHz |  |  |

| 8Tosc                   | 01                    | 5 MHz    |  |  |

| 32Tosc                  | 10                    | 20 MHz   |  |  |

| RC <sup>(1, 2, 3)</sup> | 11                    | (Note 1) |  |  |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s, but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 15.1 and 15.2).

## 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

| Note | 1: When reading the port register, any pin   |

|------|----------------------------------------------|

|      | configured as an analog input channel will   |

|      | read as cleared (a low level). Pins config-  |

|      | ured as digital inputs will convert an ana-  |

|      | log input. Analog levels on a digitally      |

|      | configured input will not affect the conver- |

|      | sion accuracy.                               |

2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

## TABLE 12-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                            |          |  |  |  |  |

|---------------|----------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A      | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz         | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1            | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1            | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C      | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-<br>C | ± 30 PPM |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the startup time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- R<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PIC<sup>®</sup> MCU devices, oscillator performance should be verified.

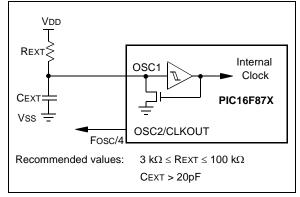

## 12.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F87X.

### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

## 14.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC MCU series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

## 14.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC MCU microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 14.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

# PIC16F87X

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| PIC16LF8<br>(Comme             | <b>73/874/87</b><br>ercial, Indu |                                           |     | ard Ope<br>ting tem                                                                                                                                                                        | -   | -40°  | ns (unless otherwise stated)<br>$C \leq TA \leq +85^{\circ}C$ for industrial<br>$C \leq TA \leq +70^{\circ}C$ for commercial |  |  |

|--------------------------------|----------------------------------|-------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F87<br>PIC16F87<br>(Comme |                                  | /877-20                                   |     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |     |       |                                                                                                                              |  |  |

| Param<br>No.                   | Symbol                           | Characteristic/<br>Device                 | Min | Тур†                                                                                                                                                                                       | Мах | Units | Conditions                                                                                                                   |  |  |

|                                | IPD                              | Power-down Current <sup>(3,5)</sup>       |     |                                                                                                                                                                                            |     |       |                                                                                                                              |  |  |

| D020                           |                                  | 16LF87X                                   | _   | 7.5                                                                                                                                                                                        | 30  | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C                                                                                   |  |  |

| D020                           |                                  | 16F87X                                    |     | 10.5                                                                                                                                                                                       | 42  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C                                                                                   |  |  |

| D021                           |                                  | 16LF87X                                   | _   | 0.9                                                                                                                                                                                        | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>0°C to +70°C                                                                                     |  |  |

| D021                           |                                  | 16F87X                                    | _   | 1.5                                                                                                                                                                                        | 16  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C                                                                                   |  |  |

| D021A                          |                                  | 16LF87X                                   |     | 0.9                                                                                                                                                                                        | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C                                                                                   |  |  |

| D021A                          |                                  | 16F87X                                    |     | 1.5                                                                                                                                                                                        | 19  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C                                                                                   |  |  |

| D023                           | ΔIBOR                            | Brown-out<br>Reset Current <sup>(6)</sup> | _   | 85                                                                                                                                                                                         | 200 | μΑ    | BOR enabled, VDD = 5.0V                                                                                                      |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

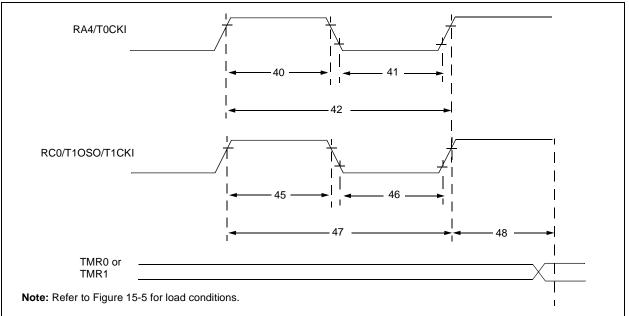

| TABLE 15-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Symbol    |                                             | Characteristic        |                | Min                   | Тур† | Max   | Units        | Conditions         |

|--------------|-----------|---------------------------------------------|-----------------------|----------------|-----------------------|------|-------|--------------|--------------------|

| 40*          | Tt0H      | T0CKI High Pulse                            | Width                 | No Prescaler   | 0.5TCY + 20           | _    | _     | ns           | Must also meet     |

|              |           | _                                           |                       | With Prescaler | 10                    | _    | _     | ns           | parameter 42       |

| 41*          | Tt0L      | T0CKI Low Pulse                             | T0CKI Low Pulse Width |                | 0.5Tcy + 20           | _    | _     | ns           | Must also meet     |

|              |           | N                                           |                       | With Prescaler | 10                    | _    | _     | ns           | parameter 42       |

| 42*          | Tt0P      | T0CKI Period                                |                       | No Prescaler   | Tcy + 40              | _    | _     | ns           |                    |

|              |           |                                             |                       | With Prescaler | Greater of:           | —    | —     | ns           | N = prescale value |

|              |           |                                             |                       |                | 20 or <u>Tcy + 40</u> |      |       |              | (2, 4,, 256)       |

|              |           |                                             |                       |                | N                     |      |       |              |                    |

| 45*          | Tt1H      | T1CKI High Time                             | Synchronous, Pr       | escaler = 1    | 0.5Tcy + 20           | —    | I     | -            | Must also meet     |

|              |           | Synchronous,                                | Standard(F)           | 15             |                       | I    | ns    | parameter 47 |                    |

|              |           |                                             | Prescaler = $2,4,8$   | Extended(LF)   | 25                    |      | _     | ns           |                    |

|              |           |                                             | Asynchronous          | Standard(F)    | 30                    |      | _     | ns           |                    |

|              |           |                                             |                       | Extended(LF)   | 50                    | _    | -     | ns           |                    |

| 46*          | Tt1L      | T1CKI Low Time                              | Synchronous, Pr       | escaler = 1    | 0.5TCY + 20           | —    | —     | ns           | Must also meet     |

|              |           |                                             | Synchronous,          | Standard(F)    | 15                    |      | _     | ns           | parameter 47       |

|              |           |                                             | Prescaler = 2,4,8     | Extended(LF)   | 25                    | —    |       | ns           |                    |

|              |           |                                             | Asynchronous          | Standard(F)    | 30                    | —    |       | ns           |                    |

|              |           |                                             |                       | Extended(LF)   | 50                    | —    |       | ns           |                    |

| 47*          | Tt1P      | T1CKI input                                 | Synchronous           | Standard(F)    | Greater of:           | —    | —     | ns           | N = prescale value |

|              |           | period                                      |                       |                | 30 or <u>Tcy + 40</u> |      |       |              | (1, 2, 4, 8)       |

|              |           |                                             |                       |                | N                     |      |       |              |                    |

|              |           |                                             |                       | Extended(LF)   | Greater of:           |      |       |              | N = prescale value |

|              |           |                                             |                       |                | 50 OR <u>TCY + 40</u> |      |       |              | (1, 2, 4, 8)       |

|              |           |                                             |                       | -              | N                     |      |       |              |                    |

|              |           |                                             | Asynchronous          | Standard(F)    | 60                    |      | _     | ns           |                    |

|              |           |                                             |                       | Extended(LF)   | 100                   | —    | —     | ns           |                    |

|              | Ft1       | Timer1 oscillator ir<br>(oscillator enabled |                       | DC             | -                     | 200  | kHz   |              |                    |

| 48           | TCKEZtmr1 | Delay from externa                          | al clock edge to tir  | ner increment  | 2Tosc                 | —    | 7Tosc | _            |                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| TABLE 15-9: I <sup>2</sup> C BUS DATA REQUI |

|---------------------------------------------|

|---------------------------------------------|

| Param<br>No. | Sym     | Characte               | eristic      | Min        | Max  | Units | Conditions                                     |

|--------------|---------|------------------------|--------------|------------|------|-------|------------------------------------------------|

| 100          | Thigh   | Clock high time        | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a minimum of 1.5 MHz    |

|              |         |                        | 400 kHz mode | 0.6        | —    | μs    | Device must operate at a<br>minimum of 10 MHz  |

|              |         |                        | SSP Module   | 0.5Tcy     |      |       |                                                |

| 101          | Tlow    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a<br>minimum of 1.5 MHz |

|              |         |                        | 400 kHz mode | 1.3        | —    | μs    | Device must operate at a minimum of 10 MHz     |

|              |         |                        | SSP Module   | 0.5TCY     |      |       |                                                |

| 102          | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                                |

|              |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF     |

| 103          | Tf      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                |

|              |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF     |

| 90           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for Repeated                     |

|              |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                |

| 91           | Thd:sta | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period, the first clock             |

|              |         | time                   | 400 kHz mode | 0.6        |      | μS    | pulse is generated                             |

| 106          | Thd:dat | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                |

|              |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                |

| 107          | Tsu:dat | Data input setup time  | 100 kHz mode | 250        | —    | ns    | (Note 2)                                       |

|              |         |                        | 400 kHz mode | 100        | —    | ns    |                                                |

| 92           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                |

|              |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                |

| 109          | Таа     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                       |

|              |         | clock                  | 400 kHz mode | —          | —    | ns    |                                                |

| 110          | Tbuf    | Bus free time          | 100 kHz mode | 4.7        | —    | μS    | Time the bus must be free                      |

|              |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start         |

|              | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that Tsu:dat ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ Tsu:dat = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

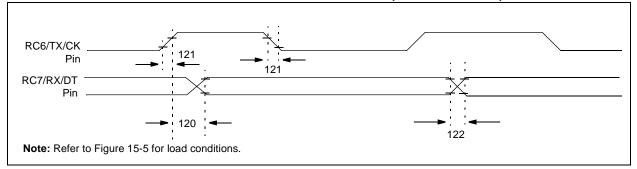

#### FIGURE 15-19: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 15-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                      | Min | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------|----------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)     | Standard( <b>F</b> ) | _   | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | Extended(LF)         | _   | -    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall time | Standard(F)          | _   | _    | 45  | ns    |            |

|              |          | (Master mode)                     | Extended(LF)         | —   | _    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall time  | Standard(F)          | —   | —    | 45  | ns    |            |

|              |          |                                   | Extended(LF)         | _   |      | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

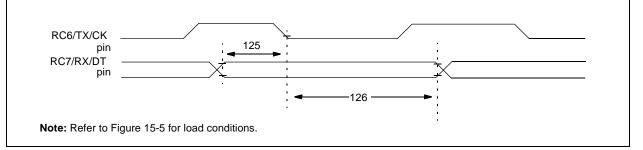

#### FIGURE 15-20: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 15-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                    | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup<br>time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                    | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## PIC16F87X

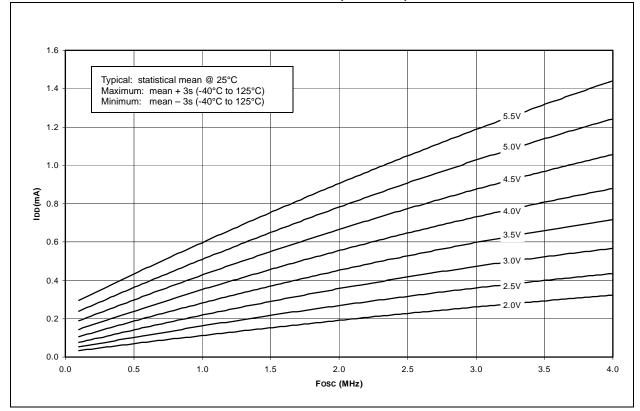

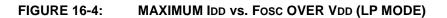

## FIGURE 16-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

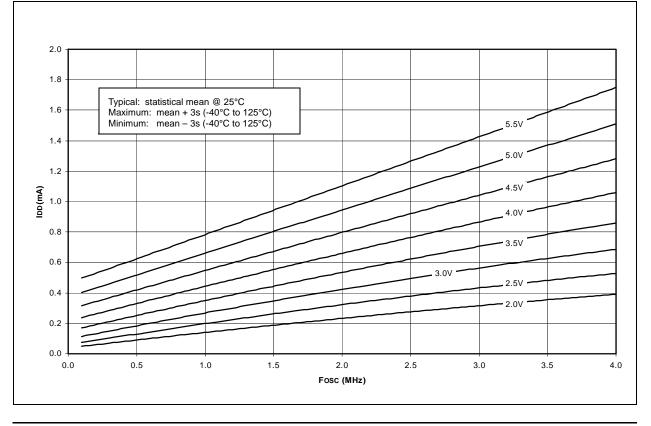

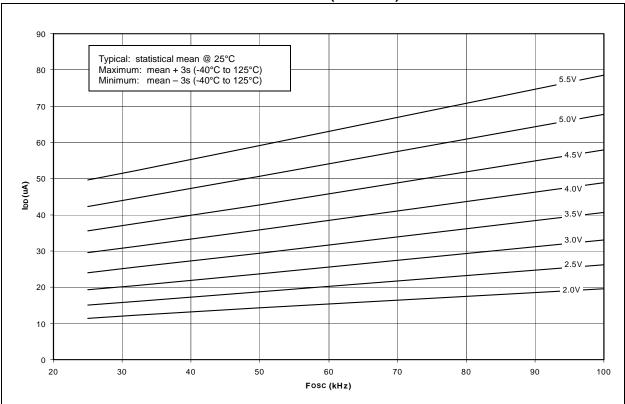

FIGURE 16-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

© 1998-2013 Microchip Technology Inc.

## 0

| On-Line Support                |               |

|--------------------------------|---------------|

| OPCODE Field Descriptions      |               |

| OPTION_REG Register            |               |

| INTEDG Bit                     |               |

|                                |               |

| PS2:PS0 Bits                   |               |

| PSA Bit                        |               |

| T0CS Bit                       |               |

| T0SE Bit                       |               |

| OSC1/CLKIN Pin                 |               |

| OSC2/CLKOUT Pin                |               |

| Oscillator Configuration       |               |

| HS                             |               |

| LP                             |               |

| RC                             | 121, 122, 124 |

| ХТ                             |               |

| Oscillator, WDT                |               |

| Oscillators                    |               |

| Capacitor Selection            |               |

| Crystal and Ceramic Resonators | 121           |

| RC                             |               |

|                                |               |

## Ρ

| P (STOP bit)                            |                 |

|-----------------------------------------|-----------------|

| Package Marking Information             |                 |

| Packaging Information                   |                 |

| Paging, Program Memory                  |                 |

| Parallel Slave Port (PSP)               | 9, 35, 38       |

| Associated Registers                    |                 |

| Block Diagram                           |                 |

| RE0/RD/AN5 Pin                          |                 |

| RE1/WR/AN6 Pin                          | 9, 36, 38       |

| RE2/CS/AN7 Pin                          | 9, 36, 38       |

| Read Waveforms                          |                 |

| Select (PSPMODE Bit)                    | .35, 36, 37, 38 |

| Write Waveforms                         |                 |

| PCL Register                            | 15, 16, 26      |

| PCLATH Register                         | .15, 16, 17, 26 |

| PCON Register                           |                 |

| BOR Bit                                 |                 |

| POR Bit                                 |                 |

| PIC16F876 Pinout Description            | 7               |

| PIC16F87X Product Identification System |                 |

| PICDEM 1 Low Cost PIC MCU               |                 |

| Demonstration Board                     |                 |

| PICDEM 17 Demonstration Board           |                 |

| PICDEM 2 Low Cost PIC16CXX              |                 |

| Demonstration Board                     |                 |

| PICDEM 3 Low Cost PIC16CXXX             |                 |

| Demonstration Board                     |                 |

| PICSTART Plus Entry Level               |                 |

| Development Programmer                  |                 |

| PIE1 Register                           | 21              |

| PIE2 Register                           | 23              |

| Pinout Descriptions                     |                 |

| PIC16F873/PIC16F876                     | 7               |

| PIC16F874/PIC16F877                     | 8               |

| PIR1 Register                           |                 |

| PIR2 Register                           |                 |

| POP                                     |                 |

| POR. See Power-on Reset                 |                 |

| POR | RTA7, 8                            |          |

|-----|------------------------------------|----------|

|     | Analog Port Pins                   | 7, 8     |

|     | Associated Registers               | 30       |

|     | Block Diagram                      |          |

|     | RA3:RA0 and RA5 Pins               | 20       |

|     |                                    |          |

|     | RA4/T0CKI Pin                      |          |

|     | Initialization                     | 29       |

|     | PORTA Register1                    | 5, 29    |

|     | RA3                                |          |

|     | RA0 and RA5 Port Pins              | . 29     |

|     | RA4/T0CKI Pin                      |          |

|     |                                    |          |

|     | RA5/SS/AN4 Pin                     |          |

|     | TRISA Register                     |          |

| POR | ЯТВ7,                              | 8, 17    |

|     | Associated Registers               | 32       |

|     | Block Diagram                      |          |

|     | RB3:RB0 Port Pins                  | 31       |

|     | RB7:RB4 Port Pins                  |          |

|     |                                    |          |

|     | PORTB Register1                    | 5, 31    |

|     | RB0/INT Edge Select (INTEDG Bit)   |          |

|     | RB0/INT Pin, External7, 8          | , 130    |

|     | RB7:RB4 Interrupt on Change        | . 130    |

|     | RB7:RB4 Interrupt on Change Enable |          |

|     | (RBIE Bit)                         | 130      |

|     |                                    | . 150    |

|     | RB7:RB4 Interrupt on Change Flag   |          |

|     | (RBIF Bit)                         | . 130    |

|     | RB7:RB4 Interrupt-on-Change Enable |          |

|     | (RBIE Bit)                         | 20       |

|     | RB7:RB4 Interrupt-on-Change Flag   |          |

|     | (RBIF Bit)2                        | 0 31     |

|     | TRISB Register                     |          |

|     |                                    |          |

| POR | RTC                                |          |

|     | Associated Registers               | 34       |

|     | Block Diagrams                     |          |

|     | Peripheral Output Override         |          |

|     | (RC 0:2, 5:7)                      | 33       |

|     | Peripheral Output Override         |          |

|     | (RC 3:4)                           | 22       |

|     |                                    |          |

|     | PORTC Register1                    |          |

|     | RC0/T1OSO/T1CKI Pin                |          |

|     | RC1/T1OSI/CCP2 Pin                 | 7, 9     |

|     | RC2/CCP1 Pin                       | 7, 9     |

|     | RC3/SCK/SCL Pin                    | 7.9      |

|     | RC4/SDI/SDA Pin                    |          |

|     | RC5/SDO Pin                        |          |

|     |                                    |          |

|     | RC6/TX/CK Pin7,                    |          |

|     | RC7/RX/DT Pin7, 9, 9               |          |

|     | TRISC Register                     | 3, 95    |

| POR | RTD                                | 7, 38    |

|     | Associated Registers               |          |

|     | Block Diagram                      |          |

|     | Devolution Days (DCD) Function     | ათ<br>იი |

|     | Parallel Slave Port (PSP) Function |          |

|     | PORTD Register1                    |          |

|     | TRISD Register                     | 35       |

NOTES: