Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-20i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                              | File<br>Address             | A                                                                     | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>  | 00h                         | Indirect addr.(*)                                                     | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                           | 01h                         | OPTION_REG                                                            | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                            | 02h                         | PCL                                                                   | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                         | 03h                         | STATUS                                                                | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                            | 04h                         | FSR                                                                   | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                          | 05h                         | TRISA                                                                 | 85h            |                     | 105h            |                         | 185h           |

| PORTB                          | 06h                         | TRISB                                                                 | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                          | 07h                         | TRISC                                                                 | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>           | 08h                         | TRISD <sup>(1)</sup>                                                  | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>           | 09h                         | TRISE <sup>(1)</sup>                                                  | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                         | 0Ah                         | PCLATH                                                                | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                         | 0Bh                         | INTCON                                                                | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                           | 0Ch                         | PIE1                                                                  | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                           | 0Dh                         | PIE2                                                                  | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                          | 0Eh                         | PCON                                                                  | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                          | 0Fh                         |                                                                       | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                          | 10h                         |                                                                       | 90h            |                     | 110h            |                         | 190h           |

| TMR2                           | 11h                         | SSPCON2                                                               | 91h            |                     |                 |                         |                |

| T2CON                          | 12h                         | PR2                                                                   | 92h            |                     |                 |                         |                |

| SSPBUF                         | 13h                         | SSPADD                                                                | 93h            |                     |                 |                         |                |

| SSPCON                         | 14h                         | SSPSTAT                                                               | 94h            |                     |                 |                         |                |

| CCPR1L                         | 15h                         |                                                                       | 95h            |                     |                 |                         |                |

| CCPR1H                         | 16h                         |                                                                       | 96h            |                     |                 |                         |                |

| CCP1CON                        | 17h                         |                                                                       | 97h            |                     |                 |                         |                |

| RCSTA                          | 18h                         | TXSTA                                                                 | 98h            |                     |                 |                         |                |

| TXREG                          | 19h                         | SPBRG                                                                 | 99h            |                     |                 |                         |                |

| RCREG                          | 1Ah                         |                                                                       | 9Ah            |                     |                 |                         |                |

| CCPR2L                         | 1Bh                         |                                                                       | 9Bh            |                     |                 |                         |                |

| CCPR2H                         | 1Ch                         |                                                                       | 9Ch            |                     |                 |                         |                |

| CCP2CON                        | 1Dh                         |                                                                       | 9Dh            |                     |                 |                         |                |

| ADRESH                         | 1Eh                         | ADRESL                                                                | 9Eh            |                     |                 |                         |                |

| ADCON0                         | 1Fh                         | ADCON1                                                                | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                | 20h                         |                                                                       | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register |                             | General<br>Purpose<br>Register                                        |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                       |                             | 96 Bytes                                                              |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                | 754                         |                                                                       |                |                     | 1756            |                         | 4              |

| Bank 0                         | J 7Fh                       | Bank 1                                                                | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| * Not a<br>Note 1: These       | physical reg<br>e registers | data memory locat<br>gister.<br>are not implemen<br>are reserved, mai | ted on the     | e PIC16F873.        |                 |                         |                |

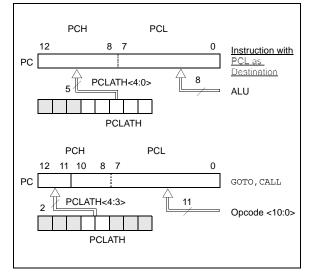

# 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| SUB1_P1 | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

| Name                   | Bit# | Buffer                | Function                                                                                                                                          |

|------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

## TABLE 3-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# 4.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F87X device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

# TABLE 4-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Со  | nfiguration | Bits | Manageral          | Internal | Internal |           |            |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |

| 0   | 0           | x    | All program memory | Yes      | No       | No        | No         |

| 0   | 1           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 0   | 1           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 0   | 1           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 0   | 1           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 1   | 0           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 1   | 0           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |

| TABLE 4-2: | REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH |

|------------|-----------------------------------------------------|

|            |                                                     |

| Address                 | Name   | Bit 7  | Bit 6     | Bit 5                 | Bit 4     | Bit 3        | Bit 2     | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|-----------|-----------------------|-----------|--------------|-----------|-------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE      | TOIE                  | INTE      | RBIE         | TOIF      | INTF  | RBIF   | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPRON | Address   | s Register            | , Low Byt | е            |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Fh                    | EEADRH | —      | —         | —                     | EEPRON    | Address,     | High Byte | )     |        | xxxx xxxx                | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPRON | l Data Re | egister, Lo           | w Byte    |              |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | —      | —         | EEPRO                 | M Data Re | egister, Hig | h Byte    |       |        | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | _         | _                     | —         | WRERR        | WREN      | WR    | RD     | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPRON | I Control | _                     | _         |              |           |       |        |                          |                                 |

| 8Dh                     | PIE2   | —      | (1)       | - EEIE BCLIE - CCP2IE |           |              |           |       |        | -r-0 00                  | -r-0 00                         |

| 0Dh                     | PIR2   | _      | (1)       | _                     | EEIF      | BCLIF        | _         | _     | CCP2IF | -r-0 00                  | -r-0 00                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### CCP1 Module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

#### CCP2 Module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

# TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                          |

|-----------|-----------|--------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)               |

| PWM       | Capture   | None                                                                                 |

| PWM       | Compare   | None                                                                                 |

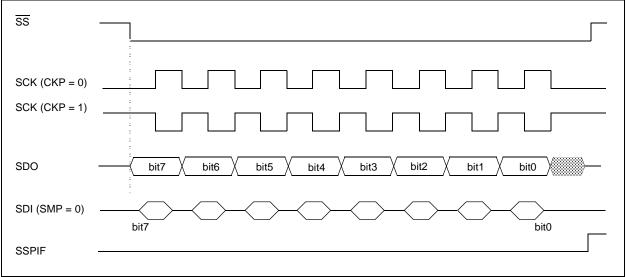

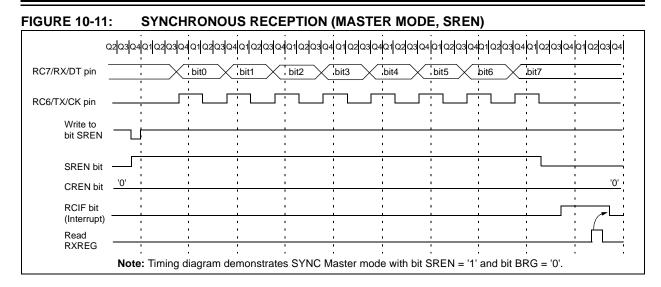

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

# FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

## TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|---------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ve Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р       | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

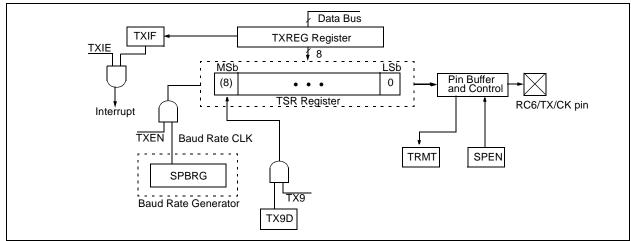

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

# PIC16F87X

# 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

## TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                | Name   | Bit 7                        | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|------------------------------|-------------------------|-------|-------|-------|-----------|-----------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE                    | TOIE  | INTE  | RBIE  | TOIF      | INTF      | R0IF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF                    | RCIF  | TXIF  | SSPIF | CCP1IF    | TMR2IF    | TMR1IF    | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                         | RX9                     | SREN  | CREN  | ADDEN | FERR      | OERR      | RX9D      | 0000 000x             | x000 0000                       |

| 19h                    | TXREG  | USART Tr                     | USART Transmit Register |       |       |       |           |           | 0000 0000 | 0000 0000             |                                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE                    | RCIE  | TXIE  | SSPIE | CCP1IE    | TMR2IE    | TMR1IE    | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                         | TX9                     | TXEN  | SYNC  | —     | BRGH      | TRMT      | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate Generator Register |                         |       |       |       | 0000 0000 | 0000 0000 |           |                       |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear. These steps should be followed for doing an A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before the next acquisition starts.

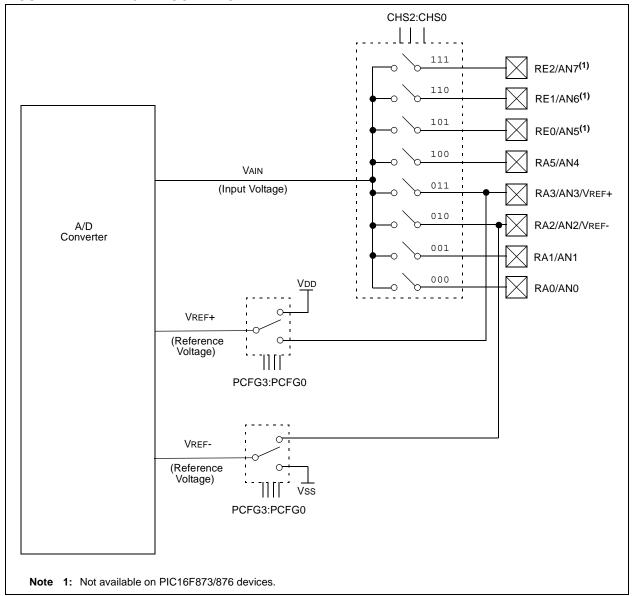

#### FIGURE 11-1: A/D BLOCK DIAGRAM

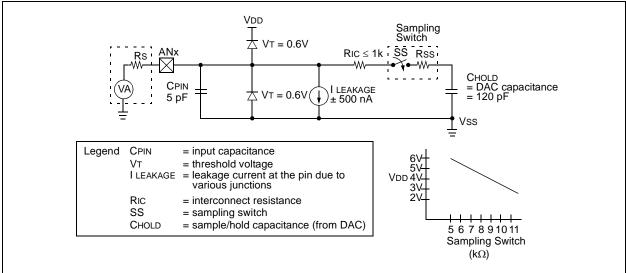

## 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

## EQUATION 11-1: ACQUISITION TIME

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the  $PIC^{\textcircled{R}}$  MCU Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient    |

|------|---------------------------------------------------------------------------------------------|

|      | = TAMP + TC + TCOFF                                                                         |

|      | $= 2\mu s + TC + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$                         |

| TC   | = CHOLD (RIC + RSS + RS) $In(1/2047)$                                                       |

|      | = $-120 \text{pF} (1 \text{k}\Omega + 7 \text{k}\Omega + 10 \text{k}\Omega) \ln(0.0004885)$ |

|      | $= 16.47 \mu s$                                                                             |

| TACQ | = $2\mu s + 16.47\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$                |

|      | $= 19.72 \mu s$                                                                             |

| L    |                                                                                             |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

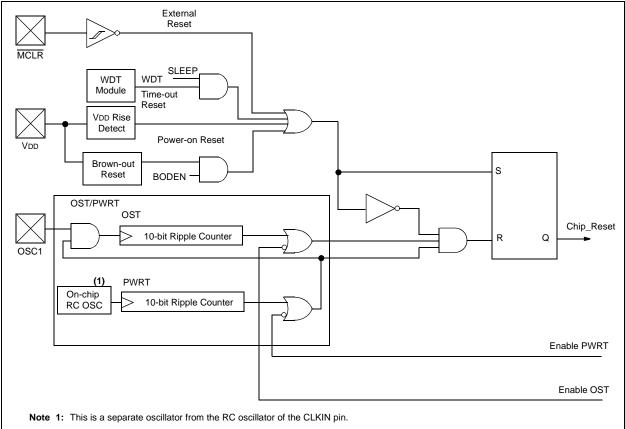

# 12.3 **RESET**

The PIC16F87X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different RESET situations as indicated in Table 12-4. These bits are used in software to determine the nature of the RESET. See Table 12-6 for a full description of RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

# PIC16F87X

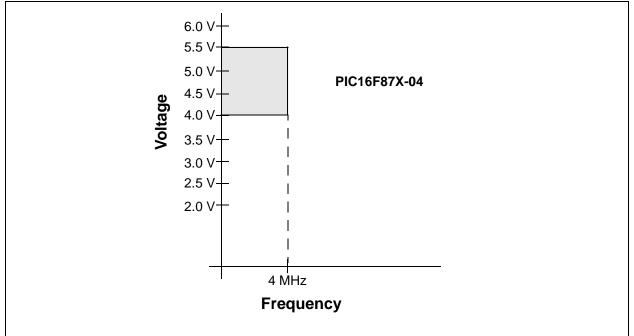

#### FIGURE 15-2: PIC16LF87X-04 VOLTAGE-FREQUENCY GRAPH (COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES ONLY)

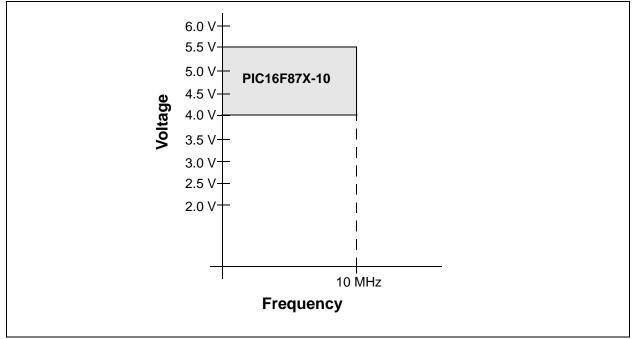

#### FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

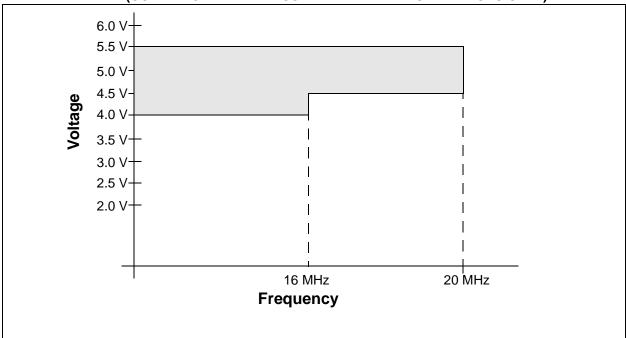

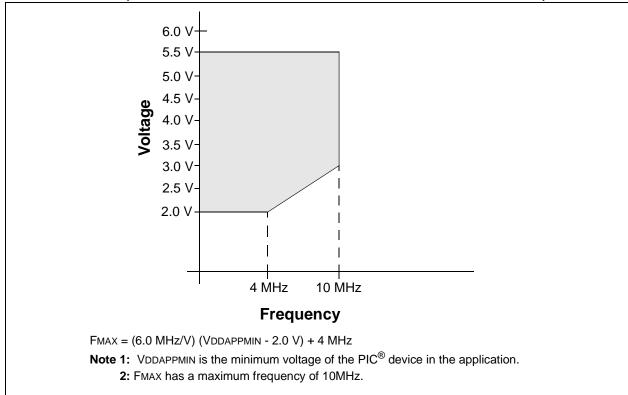

# 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| DC CHA       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                            |           |      |     |       |                                                                        |

|--------------|------------------------------------------------------|--------------------------------------------|-----------|------|-----|-------|------------------------------------------------------------------------|

| Param<br>No. | Sym                                                  | Characteristic                             | Min       | Тур† | Мах | Units | Conditions                                                             |

|              | Vol                                                  | Output Low Voltage                         |           |      |     |       |                                                                        |

| D080         |                                                      | I/O ports                                  |           |      | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

| D083         |                                                      | OSC2/CLKOUT (RC osc config)                | —         | —    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

|              | Voн                                                  | Output High Voltage                        |           |      |     |       |                                                                        |

| D090         |                                                      | I/O ports <sup>(3)</sup>                   | Vdd - 0.7 |      |     | V     | Юн = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |

| D092         |                                                      | OSC2/CLKOUT (RC osc config)                | Vdd - 0.7 | _    | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                           |

| D150*        | Vod                                                  | Open-Drain High Voltage                    |           | _    | 8.5 | V     | RA4 pin                                                                |

|              |                                                      | Capacitive Loading Specs on<br>Output Pins |           |      |     |       |                                                                        |

| D100         | Cosc2                                                | OSC2 pin                                   | _         |      | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101         | Cio                                                  | All I/O pins and OSC2 (RC mode)            | _         | —    | 50  | pF    |                                                                        |

| D102         | Св                                                   | SCL, SDA (I <sup>2</sup> C mode)           |           | _    | 400 | pF    |                                                                        |

|              |                                                      | Data EEPROM Memory                         |           |      |     |       |                                                                        |

| D120         | ED                                                   | Endurance                                  | 100K      | —    | —   |       | 25°C at 5V                                                             |

| D121         | Vdrw                                                 | VDD for read/write                         | Vmin      | —    | 5.5 | V     | Using EECON to read/write<br>VMIN = min. operating voltage             |

| D122         | TDEW                                                 | Erase/write cycle time                     |           | 4    | 8   | ms    |                                                                        |

|              |                                                      | Program FLASH Memory                       |           |      |     |       |                                                                        |

| D130         | Eр                                                   | Endurance                                  | 1000      | —    | —   |       | 25°C at 5V                                                             |

| D131         | Vpr                                                  | VDD for read                               | Vmin      | —    | 5.5 | V     | VMIN = min operating voltage                                           |

| D132A        |                                                      | VDD for erase/write                        | Vmin      | —    | 5.5 | V     | Using EECON to read/write,<br>VMIN = min. operating voltage            |

| D133         |                                                      | Erase/Write cycle time                     |           | 4    | 8   | ms    |                                                                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

## 15.4 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| DC CHARACTERISTICS |       |                                         | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section 15.1) |      |         |       |                                                             |  |  |

|--------------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|-------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                          | Min                                                                                                                                                                                                        | Тур† | Max     | Units | Conditions                                                  |  |  |

|                    | VIL   | Input Low Voltage                       |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

|                    |       | I/O ports                               |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

| D030               |       | with TTL buffer                         | Vss                                                                                                                                                                                                        | —    | 0.15Vdd |       | For entire VDD range                                        |  |  |

| D030A              |       |                                         | Vss                                                                                                                                                                                                        | —    | 0.8V    | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |

| D031               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                        | —    | 0.2Vdd  | V     |                                                             |  |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss                                                                                                                                                                                                        | —    | 0.2Vdd  | V     |                                                             |  |  |

| D033               |       | OSC1 (in XT, HS and LP)                 | Vss                                                                                                                                                                                                        | —    | 0.3Vdd  | V     | (Note 1)                                                    |  |  |

|                    |       | Ports RC3 and RC4                       |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

| D034               |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                        | —    | 0.3Vdd  | V     | For entire VDD range                                        |  |  |

| D034A              |       | with SMBus                              | -0.5                                                                                                                                                                                                       | —    | 0.6     | V     | for $VDD = 4.5$ to $5.5V$                                   |  |  |

|                    | Vih   | Input High Voltage                      |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

|                    |       | I/O ports                               |                                                                                                                                                                                                            | —    |         |       |                                                             |  |  |

| D040               |       | with TTL buffer                         | 2.0                                                                                                                                                                                                        | —    | Vdd     | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |  |

| D040A              |       |                                         | 0.25Vdd                                                                                                                                                                                                    | —    | Vdd     | V     | For entire VDD range                                        |  |  |

|                    |       |                                         | + 0.8V                                                                                                                                                                                                     |      |         |       |                                                             |  |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8Vdd                                                                                                                                                                                                     | —    | Vdd     | V     | For entire VDD range                                        |  |  |

| D042               |       | MCLR                                    | 0.8Vdd                                                                                                                                                                                                     | —    | Vdd     | V     |                                                             |  |  |

| D042A              |       | OSC1 (XT, HS and LP)                    | 0.7Vdd                                                                                                                                                                                                     | —    | Vdd     | V     | (Note 1)                                                    |  |  |

| D043               |       | OSC1 (in RC mode)                       | 0.9Vdd                                                                                                                                                                                                     | —    | Vdd     | V     |                                                             |  |  |

|                    |       | Ports RC3 and RC4                       |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7VDD                                                                                                                                                                                                     | —    | Vdd     | V     | For entire VDD range                                        |  |  |

| D044A              |       | with SMBus                              | 1.4                                                                                                                                                                                                        | —    | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |  |  |

| D070A              | IPURB |                                         | 50                                                                                                                                                                                                         | 250  | 400     | μA    | VDD = 5V, VPIN = VSS,                                       |  |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                                            |      |         |       |                                                             |  |  |

| D060               |       | I/O ports                               | -                                                                                                                                                                                                          | -    | ±1      | μΑ    | $Vss \le VPIN \le VDD,$                                     |  |  |

|                    |       |                                         |                                                                                                                                                                                                            |      |         |       | Pin at hi-impedance                                         |  |  |

| D061               |       | MCLR, RA4/T0CKI                         | -                                                                                                                                                                                                          | -    | ±5      | μΑ    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |  |

| D063               |       | OSC1                                    | -                                                                                                                                                                                                          | -    | ±5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# PIC16F87X

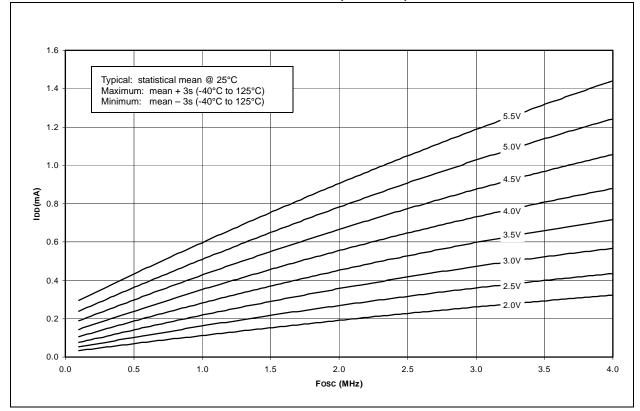

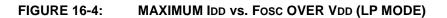

# FIGURE 16-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

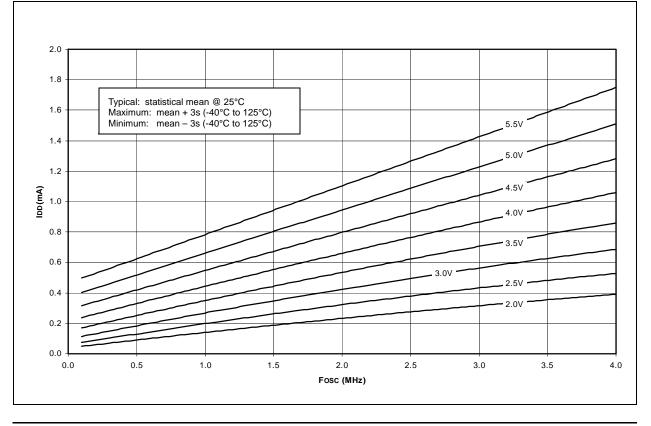

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----|---------|------|-------------|-------|-------|-------|

| Dimension                | MIN | NOM     | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins           | n   |         | 44   |             |       | 44    |       |

| Pitch                    | р   |         | .050 |             |       | 1.27  |       |

| Pins per Side            | n1  |         | 11   |             |       | 11    |       |

| Overall Height           | А   | .165    | .173 | .180        | 4.19  | 4.39  | 4.57  |

| Molded Package Thickness | A2  | .145    | .153 | .160        | 3.68  | 3.87  | 4.06  |

| Standoff §               | A1  | .020    | .028 | .035        | 0.51  | 0.71  | 0.89  |

| Side 1 Chamfer Height    | A3  | .024    | .029 | .034        | 0.61  | 0.74  | 0.86  |

| Corner Chamfer 1         | CH1 | .040    | .045 | .050        | 1.02  | 1.14  | 1.27  |

| Corner Chamfer (others)  | CH2 | .000    | .005 | .010        | 0.00  | 0.13  | 0.25  |

| Overall Width            | Е   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Overall Length           | D   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Molded Package Width     | E1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Molded Package Length    | D1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Footprint Width          | E2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Footprint Length         | D2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Lead Thickness           | С   | .008    | .011 | .013        | 0.20  | 0.27  | 0.33  |

| Upper Lead Width         | B1  | .026    | .029 | .032        | 0.66  | 0.74  | 0.81  |

| Lower Lead Width         | В   | .013    | .020 | .021        | 0.33  | 0.51  | 0.53  |

| Mold Draft Angle Top     | α   | 0       | 5    | 10          | 0     | 5     | 10    |

| Mold Draft Angle Bottom  | β   | 0       | 5    | 10          | 0     | 5     | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-047

Drawing No. C04-048

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|--|--|

| Pins              | 28/40                                               | 28/40                                                      |  |  |

| Timers            | 3                                                   | 3                                                          |  |  |

| Interrupts        | 11 or 12                                            | 13 or 14                                                   |  |  |

| Communication     | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Slave) | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Master/Slave) |  |  |

| Frequency         | 20 MHz                                              | 20 MHz                                                     |  |  |

| Voltage           | 2.5V - 5.5V                                         | 2.0V - 5.5V                                                |  |  |

| A/D               | 8-bit                                               | 10-bit                                                     |  |  |

| CCP               | 2                                                   | 2                                                          |  |  |

| Program<br>Memory | 4K, 8K<br>EPROM                                     | 4K, 8K<br>FLASH                                            |  |  |

| RAM               | 192, 368<br>bytes                                   | 192, 368<br>bytes                                          |  |  |

| EEPROM data       | None                                                | 128, 256<br>bytes                                          |  |  |

| Other             | _                                                   | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming      |  |  |

## W

| Wake-up from SLEEP 119, 132                |

|--------------------------------------------|

| Interrupts 125, 126                        |

| MCLR Reset126                              |

| Timing Diagram133                          |

| WDT Reset 126                              |

| Watchdog Timer (WDT) 119, 131              |

| Block Diagram131                           |

| Enable (WDTE Bit)131                       |

| Postscaler. See Postscaler, WDT            |

| Programming Considerations131              |

| RC Oscillator131                           |

| Time-out Period131                         |

| WDT Reset, Normal Operation 123, 125, 126  |

| WDT Reset, SLEEP 123, 125, 126             |

| Waveform for General Call Address Sequence |

| WCOL                                       |

| WCOL Status Flag80                         |

| Write Collision Detect bit, WCOL67         |

| Write Verify                               |

| Data EEPROM and FLASH Program Memory45     |

| WWW, On-Line Support4                      |