Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877t-04-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | I/O Ports                                                                   |     |

| 4.0   | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0   | Timer0 Module                                                               |     |

| 6.0   | Timer1 Module                                                               |     |

| 7.0   | Timer2 Module                                                               |     |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0  | Special Features of the CPU                                                 | 119 |

| 13.0  | Instruction Set Summary                                                     | 135 |

|       | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 16.0  | DC and AC Characteristics Graphs and Tables                                 | 177 |

| 17.0  | Packaging Information                                                       | 189 |

| Appe  | ndix A: Revision History                                                    | 197 |

| Appe  | ndix B: Device Differences                                                  | 197 |

|       | ndix C: Conversion Considerations                                           |     |

| Index | (                                                                           | 199 |

|       | ine Support                                                                 |     |

| Read  | ler Response                                                                | 208 |

| PIC1  | 6F87X Product Identification System                                         | 209 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                   | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|--|--|

|               | GIE                                                                                     | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |  |  |

|               | bit 7                                                                                   |                               |               |              |                  |             |                | bit 0      |  |  |  |  |

|               |                                                                                         |                               |               |              |                  |             |                |            |  |  |  |  |

| bit 7         | GIE: Globa                                                                              | al Interrupt E                | nable bit     |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | s all unmas                   |               | ots          |                  |             |                |            |  |  |  |  |

| <b>h</b> :+ C |                                                                                         | es all interru                |               | L:4          |                  |             |                |            |  |  |  |  |

| bit 6         | PEIE: Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts |                               |               |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | es all periph                 |               | •            | 5                |             |                |            |  |  |  |  |

| bit 5         |                                                                                         | 0 Overflow                    | =             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | s the TMR0                    |               |              |                  |             |                |            |  |  |  |  |

|               | 0 = Disable                                                                             | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |  |  |

| bit 4         |                                                                                         | /INT Externa                  | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |  |  |

| bit 3         |                                                                                         | Port Change                   |               | •            |                  |             |                |            |  |  |  |  |

| bit 0         |                                                                                         | s the RB po                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | es the RB po                  |               |              |                  |             |                |            |  |  |  |  |

| bit 2         | TOIF: TMR                                                                               | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |  |  |

|               |                                                                                         |                               |               |              | eared in softwa  | re)         |                |            |  |  |  |  |

|               |                                                                                         | register did                  |               |              |                  |             |                |            |  |  |  |  |

| bit 1         |                                                                                         | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |  |  |

|               |                                                                                         | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |  |  |

| bit 0         |                                                                                         | Port Change                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                         | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |  |  |

|               |                                                                                         | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |  |  |

|               |                                                                                         | be cleared in<br>of the RB7:R | ,             | ve changed   | stata            |             |                |            |  |  |  |  |

|               |                                                                                         |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |  |  |

|               | Legend:                                                                                 |                               |               |              |                  |             |                |            |  |  |  |  |

|               | R = Reada                                                                               | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |  |  |

|               | - n = Value                                                                             |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |  |  |

|               |                                                                                         |                               |               |              |                  |             |                | -          |  |  |  |  |

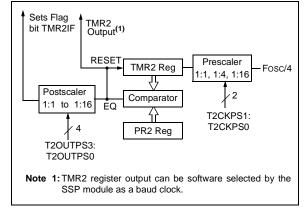

## 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

## REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

|         | U-0               | R/W-0               | R/W-0       | R/W-0        | R/W-0         | R/W-0     | R/W-0        | R/W-0   |

|---------|-------------------|---------------------|-------------|--------------|---------------|-----------|--------------|---------|

|         | _                 | TOUTPS3             | TOUTPS2     | TOUTPS1      | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |

|         | bit 7             | •                   |             |              |               |           |              | bit 0   |

|         |                   |                     |             |              |               |           |              |         |

| bit 7   | Unimplen          | n <b>ented:</b> Rea | d as '0'    |              |               |           |              |         |

| bit 6-3 | TOUTPS3           | :TOUTPS0:           | Timer2 Out  | put Postscal | e Select bits |           |              |         |

|         | 0000 = 1:         | 1 Postscale         |             |              |               |           |              |         |

|         |                   | 2 Postscale         |             |              |               |           |              |         |

|         | •                 | 3 Postscale         |             |              |               |           |              |         |

|         | •                 |                     |             |              |               |           |              |         |

|         | •                 |                     |             |              |               |           |              |         |

|         | 1111 <b>= 1</b> : | 16 Postscale        | <b>;</b>    |              |               |           |              |         |

| bit 2   | -                 | Timer2 On I         | bit         |              |               |           |              |         |

|         | 1 = Timer2        |                     |             |              |               |           |              |         |

|         | 0 = Timer2        |                     |             |              |               |           |              |         |

| bit 1-0 |                   | :T2CKPS0:           | Timer2 Cloc | k Prescale S | Select bits   |           |              |         |

|         | 00 = Pres         |                     |             |              |               |           |              |         |

|         | 1x = Pres         |                     |             |              |               |           |              |         |

|         |                   |                     |             |              |               |           |              |         |

|         | Legend:           |                     |             |              |               |           |              |         |

|         | R = Reada         | able bit            | W = W       | /ritable bit | U = Unim      | plemented | bit, read as | '0'     |

|         | - n = Value       | e at POR            | '1' = B     | it is set    | '0' = Bit i   | s cleared | x = Bit is u | nknown  |

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POF<br>BO | R,   | Valu<br>all o<br>RES | ther |

|------------------------|---------|----------------------|-------------------------------------|-------------|---------|---------|--------|---------|---------|--------------------|------|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE        | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 (             | 000x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000               | 0000 | 0000                 | 0000 |

| 0Dh                    | PIR2    | _                    | —                                   | _           | _       | —       | _      | _       | CCP2IF  |                    | 0    |                      | 0    |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000               | 0000 | 0000                 | 0000 |

| 8Dh                    | PIE2    | —                    | —                                   | —           | _       | —       | _      | —       | CCP2IE  |                    | 0    |                      | 0    |

| 87h                    | TRISC   | PORTC D              | Data Directio                       | n Register  |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Regi                        | ster        |         |         |        |         |         | 0000               | 0000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Perio                       | od Register |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 12h                    | T2CON   | —                    | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 (             | 0000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PW                          | /M Register | 1 (LSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PW                          | /M Register | 1 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | —                    |                                     | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 (               | 0000 | 00                   | 0000 |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |             |         |         |        |         |         |                    |      | uuuu                 | uuuu |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PW                          |             | XXXX X  | xxxx    | uuuu   | uuuu    |         |                    |      |                      |      |

| 1Dh                    | CCP2CON | —                    | —                                   | CCP2X       | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 (               | 0000 | 00                   | 0000 |

| <b>TABLE 8-5</b> : | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--------------------|-------------------------------------------------|

|--------------------|-------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

### TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|---------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ve Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р       | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

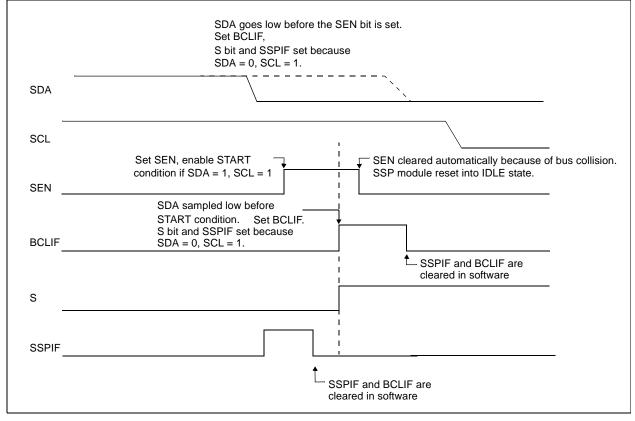

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

|       | SPEN<br>bit 7                                                                           | RX9                                                                  |                   |               |                |              |                |           |  |  |  |

|-------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------|---------------|----------------|--------------|----------------|-----------|--|--|--|

|       | bit 7                                                                                   |                                                                      | SREN              | CREN          | ADDEN          | FERR         | OERR           | RX9D      |  |  |  |

|       |                                                                                         |                                                                      |                   |               |                |              |                | bit C     |  |  |  |

| bit 7 | 1 = Serial p                                                                            | ial Port Ena<br>port enabled                                         | l (configures     | RC7/RX/D      | T and RC6/T    | X/CK pins a  | as serial port | pins)     |  |  |  |

| bit 6 | 1 = Selects                                                                             | Receive Ena<br>9-bit recep<br>8-bit recep                            | tion              |               |                |              |                |           |  |  |  |

| bit 5 | SREN: Sin                                                                               | gle Receive                                                          | Enable bit        |               |                |              |                |           |  |  |  |

|       | Asynchron<br>Don't care                                                                 | ous mode:                                                            |                   |               |                |              |                |           |  |  |  |

|       | 1 = Enable<br>0 = Disable                                                               | <u>us mode - n</u><br>s single rec<br>es single rec<br>cleared after | eive              | s complete.   |                |              |                |           |  |  |  |

|       | <u>Synchrono</u><br>Don't care                                                          | <u>us mode - s</u>                                                   | lave:             |               |                |              |                |           |  |  |  |

| bit 4 | CREN: Cor                                                                               | ntinuous Re                                                          | ceive Enabl       | e bit         |                |              |                |           |  |  |  |

|       | Asynchronous mode:<br>1 = Enables continuous receive<br>0 = Disables continuous receive |                                                                      |                   |               |                |              |                |           |  |  |  |

|       |                                                                                         |                                                                      |                   | til enable bi | t CREN is cle  | eared (CRE   | N overrides    | SREN)     |  |  |  |

| bit 3 | ADDEN: A                                                                                | ddress Dete                                                          | ect Enable b      | it            |                |              |                |           |  |  |  |

|       | 1 = Enable<br>RSR<8                                                                     | s address d<br>⊳ is set                                              |                   | ables interru | ipt and load o |              |                |           |  |  |  |

| bit 2 | FERR: Fra                                                                               | ming Error b<br>g error (can                                         | pit               |               | RCREG regi     |              |                | 1 9       |  |  |  |

| bit 1 |                                                                                         | -                                                                    | bit<br>be cleared | by clearing   | bit CREN)      |              |                |           |  |  |  |

| bit 0 | <b>RX9D:</b> 9th                                                                        | bit of Rece                                                          | ived Data (c      | an be parity  | bit, but mus   | t be calcula | ted by user    | firmware) |  |  |  |

|       | Legend:                                                                                 |                                                                      |                   |               |                |              |                |           |  |  |  |

|       | R = Reada                                                                               | ble bit                                                              | W = W             | /ritable bit  | U = Unim       | plemented    | bit, read as   | ʻ0'       |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

## REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

- n = Value at POR

x = Bit is unknown

### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|-----------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9                         | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9                         | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | aud Rate Generator Register |       |       |       |       |       |       |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

## TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | F       | osc = 20 M | IHz                         | F       | osc = 16 N | IHz                         | Fosc = 10 MHz |            |                             |  |

|-------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -          | -                           | -       | -          | -                           | -             | -          | -                           |  |

| 1.2         | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202         | 0.17       | 129                         |  |

| 2.4         | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404         | 0.17       | 64                          |  |

| 9.6         | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766         | 1.73       | 15                          |  |

| 19.2        | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531        | 1.72       | 7                           |  |

| 28.8        | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250        | 8.51       | 4                           |  |

| 33.6        | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250        | 6.99       | 4                           |  |

| 57.6        | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083        | 9.58       | 2                           |  |

| HIGH        | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610         | -          | 255                         |  |

| LOW         | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250       | -          | 0                           |  |

| DAUD                |        | Fosc = 4 M | Hz                          | Fo    | Fosc = 3.6864 MHz |                             |  |  |  |

|---------------------|--------|------------|-----------------------------|-------|-------------------|-----------------------------|--|--|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR        | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3   | 0                 | 191                         |  |  |  |

| 1.2                 | 1.202  | 0.17       | 51                          | 1.2   | 0                 | 47                          |  |  |  |

| 2.4                 | 2.404  | 0.17       | 25                          | 2.4   | 0                 | 23                          |  |  |  |

| 9.6                 | 8.929  | 6.99       | 6                           | 9.6   | 0                 | 5                           |  |  |  |

| 19.2                | 20.833 | 8.51       | 2                           | 19.2  | 0                 | 2                           |  |  |  |

| 28.8                | 31.250 | 8.51       | 1                           | 28.8  | 0                 | 1                           |  |  |  |

| 33.6                | -      | -          | -                           | -     | -                 | -                           |  |  |  |

| 57.6                | 62.500 | 8.51       | 0                           | 57.6  | 0                 | 0                           |  |  |  |

| HIGH                | 0.244  | -          | 255                         | 0.225 | -                 | 255                         |  |  |  |

| LOW                 | 62.500 | -          | 0                           | 57.6  | -                 | 0                           |  |  |  |

## TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 20 MHz |            |                             | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

|-------------|---------------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -             | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 1.2         | -             | -          | -                           | -        | -          | -                           | -             | -          | -                           |  |

| 2.4         | -             | -          | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |  |

| 9.6         | 9.615         | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2        | 19.231        | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8        | 29.070        | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6        | 33.784        | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6        | 59.524        | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH        | 4.883         | -          | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |  |

| LOW         | 1250.000      | -          | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |  |

| BAUD        | F       | osc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | -       | -          | -                           | -                 | -          | -                           |  |  |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2               | 0          | 191                         |  |  |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4               | 0          | 95                          |  |  |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6               | 0          | 23                          |  |  |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2              | 0          | 11                          |  |  |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8              | 0          | 7                           |  |  |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9              | 2.04       | 6                           |  |  |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6              | 0          | 3                           |  |  |

| HIGH        | 0.977   | -          | 255                         | 0.9               | -          | 255                         |  |  |

| LOW         | 250.000 | -          | 0                           | 230.4             | -          | 0                           |  |  |

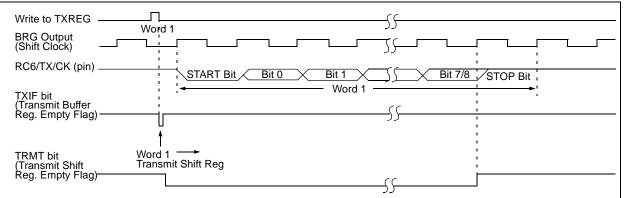

When setting up an Asynchronous Transmission, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

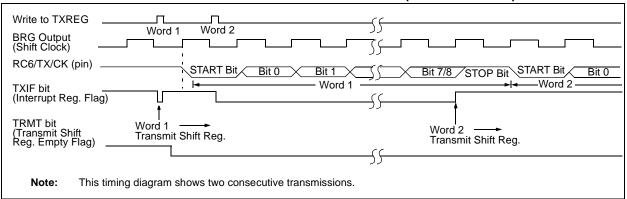

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|----------------------------------------|----------------------|-----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TOIE   | INTE  | RBIE  | T0IF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG                                  | USART Tra            | insmit Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

|                            | Q1 Q2 Q3 Q4                                                          | Q1 Q2 Q3 Q4       | Q1          |             | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      |

|----------------------------|----------------------------------------------------------------------|-------------------|-------------|-------------|--------------|-------------------|-------------------|------------------|

| OSC1                       | ·/~~~~/                                                              |                   |             | -           |              | <u>;</u> ~~~~~~   |                   |                  |

| CLKOUT <sup>(4)</sup>      | \/\                                                                  |                   | <u> </u>    | Tost(2)     | /            | \                 | ¦/ \              |                  |

| INT pin                    | · · ·                                                                | 1                 |             | · ·         |              | 1<br>1            | 1 I<br>1 I        |                  |

| INTF Flag<br>(INTCON<1>)   |                                                                      | י<br>י<br>י<br>י  | Ĺ           | /           |              | Interrupt Latency | (2)               | <br>  <br> <br>  |

| GIE bit<br>(INTCON<7>)     | 1 I<br>1 I<br>1 I<br>1 I<br>1 I                                      | i<br>             | Processor i | n           |              | ·                 | 1 1<br>1 1<br>1 1 | ו<br>ו<br>ו<br>ו |

| INSTRUCTIO                 | N FLOW                                                               |                   |             | · ·         |              | 1                 | 1 1<br>1 1        | 1                |

| PC                         | Х РС Х                                                               | PC+1              | ХР          | C+2         | PC+2         | X PC + 2          | <u>X 0004h X</u>  | 0005h            |

| Instruction {<br>Fetched { | Inst(PC) = SLEEP                                                     | Inst(PC + 1)      |             | 1           | Inst(PC + 2) | 1<br>1<br>1       | Inst(0004h)       | Inst(0005h)      |

| Instruction                | Inst(PC - 1)                                                         | SLEEP             |             | ,<br>,<br>, | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h)      |

| 2: Tost                    | HS or LP oscillator n<br>τ = 1024Tosc (drawi<br>= '1' assumed. In th | ing not to scale) |             |             |              |                   |                   |                  |

## F

If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

# 12.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-8 shows which features are consumed by the background debugger.

| TABLE 12-8: DE | BUGGER RESOURCES |

|----------------|------------------|

|----------------|------------------|

| I/O pins       | RB6, RB7                                     |  |  |  |  |  |

|----------------|----------------------------------------------|--|--|--|--|--|

| Stack          | 1 level                                      |  |  |  |  |  |

| Program Memory | Address 0000h must be NOP                    |  |  |  |  |  |

|                | Last 100h words                              |  |  |  |  |  |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |  |  |  |  |  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

# 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in the W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                          |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow$ (W)                                                                                                |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |  |  |

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |      |      |                                               |  |  |  |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|------|-----------------------------------------------|--|--|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                                  |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |                                               |  |  |  |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                                        | Min Typ† Max Units Conditions                        |                                                      |      |      |                                               |  |  |  |

|                                                                                  | Vdd    | Supply Voltage                                                   |                                                      |                                                      |      |      |                                               |  |  |  |

| D001                                                                             |        | 16LF87X                                                          | 2.0                                                  |                                                      | 5.5  | V    | LP, XT, RC osc configuration<br>(DC to 4 MHz) |  |  |  |

| D001                                                                             |        | 16F87X                                                           | 4.0                                                  | _                                                    | 5.5  | V    | LP, XT, RC osc configuration                  |  |  |  |

| D001A                                                                            |        |                                                                  | 4.5                                                  |                                                      | 5.5  | V    | HS osc configuration                          |  |  |  |

|                                                                                  |        |                                                                  | VBOR                                                 |                                                      | 5.5  | V    | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>     |  |  |  |

| D002                                                                             | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                    | 1.5                                                  |      | V    |                                               |  |  |  |

| D003                                                                             | Vpor   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                    | Vss                                                  | _    | V    | See section on Power-on Reset for details     |  |  |  |

| D004                                                                             | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                 | —                                                    | —    | V/ms | See section on Power-on Reset for details     |  |  |  |

| D005                                                                             | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                  | 4.0                                                  | 4.35 | V    | BODEN bit in configuration word<br>enabled    |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

### 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40$ °C $\leq$ TA $\leq$ +125 °C |                |     |      |      |                                            |  |  |  |  |  |  |

|--------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------|----------------|-----|------|------|--------------------------------------------|--|--|--|--|--|--|

| Param<br>No.                                                       | Symbol | Characteristic/<br>Device                                                                                          |                |     |      |      |                                            |  |  |  |  |  |  |

|                                                                    | Vdd    | Supply Voltage                                                                                                     | Supply Voltage |     |      |      |                                            |  |  |  |  |  |  |

| D001                                                               |        |                                                                                                                    | 4.0            | —   | 5.5  | V    | LP, XT, RC osc configuration               |  |  |  |  |  |  |

| D001A                                                              |        |                                                                                                                    | 4.5            |     | 5.5  | V    | HS osc configuration                       |  |  |  |  |  |  |

| D001A                                                              |        |                                                                                                                    | VBOR           |     | 5.5  | V    | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |  |  |  |  |  |  |

| D002                                                               | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                       | —              | 1.5 | _    | V    |                                            |  |  |  |  |  |  |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal                                                   | —              | Vss | _    | V    | See section on Power-on Reset for details  |  |  |  |  |  |  |

| D004                                                               | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal                                                       | 0.05           | —   | —    | V/ms | See section on Power-on Reset for details  |  |  |  |  |  |  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                                                                         | 3.7            | 4.0 | 4.35 | V    | BODEN bit in configuration word<br>enabled |  |  |  |  |  |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

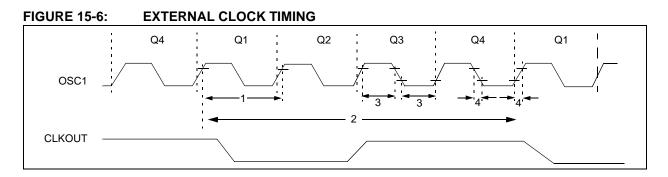

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                     | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|------------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency           | DC  |      | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                           | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                    | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | DC  | —    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency               | DC  |      | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                           | 0.1 | —    | 4      | MHz   | XT osc mode        |

|                  |       |                                    | 4   | —    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | 4   | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | 5   |      | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period              | 250 |      | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                           | 250 | _    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | —      | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μS    | LP osc mode        |

|                  |       | Oscillator Period                  | 250 | _    | —      | ns    | RC osc mode        |

|                  |       | (Note 1)                           | 250 | —    | 10,000 | ns    | XT osc mode        |

|                  |       |                                    | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time<br>(Note 1) | 200 | TCY  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or   | 100 |      | —      | ns    | XT oscillator      |

|                  | TosH  | Low Time                           | 2.5 | —    | —      | μS    | LP oscillator      |

|                  |       |                                    | 15  | —    | —      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or   |     |      | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                          | —   | —    | 50     | ns    | LP oscillator      |

|                  |       |                                    | —   | —    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

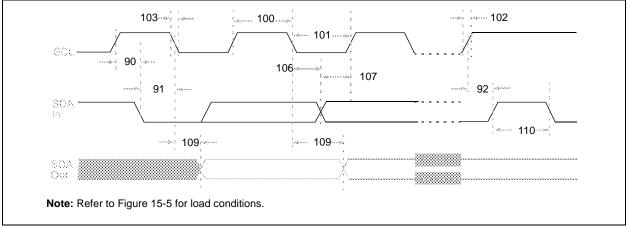

| Parameter<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                                            |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-------------------------------------------------------|

| 90               | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for Repeated                            |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | START condition                                       |

| 91               | Thd:sta | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period, the first clock pulse is generated |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   |       |                                                       |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                                       |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | _   |       |                                                       |

| 93               | Thd:sto | STOP condition  | 100 kHz mode | 4000 | -   | _   | ns    |                                                       |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       |                                                       |

| TABLE 15-8: | I <sup>2</sup> C BUS START/STOP BITS REQUIREMENTS |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

# FIGURE 15-18: I<sup>2</sup>C BUS DATA TIMING

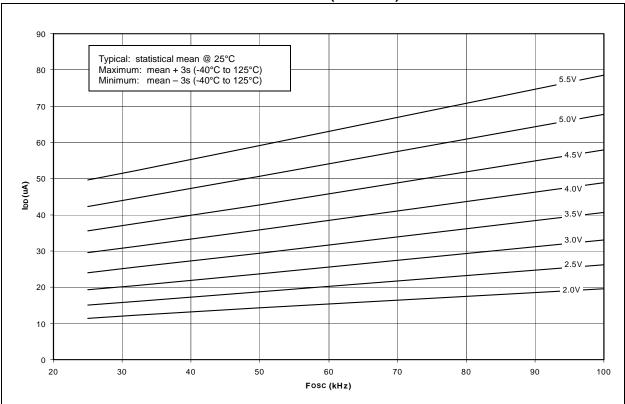

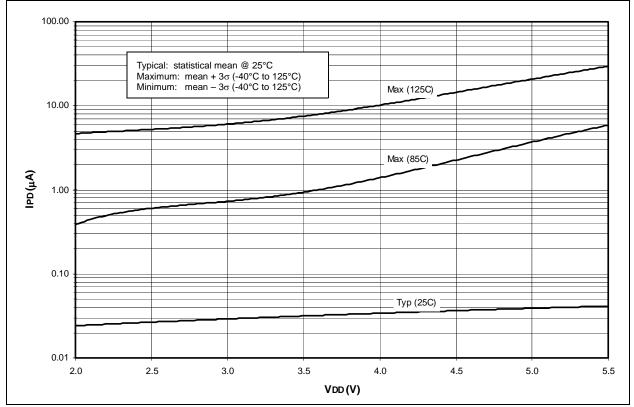

FIGURE 16-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

© 1998-2013 Microchip Technology Inc.

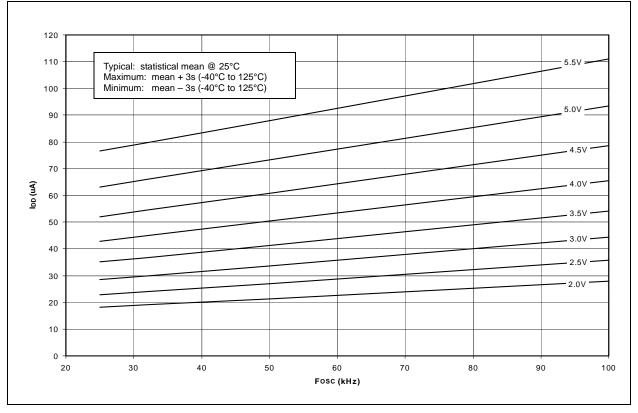

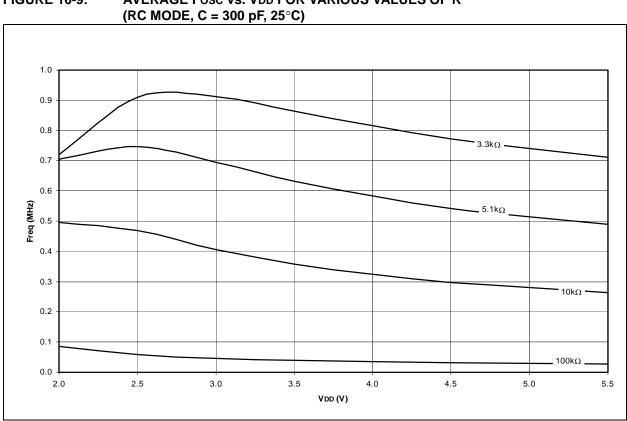

**FIGURE 16-9:** AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R

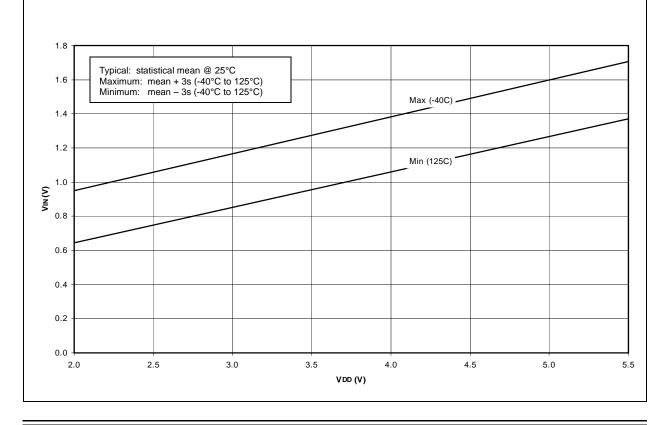

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. Vdd, (TTL INPUT, -40°C TO 125°C)

NOTES: