Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877t-20-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PIC16F873 AND PIC16F876 PINOUT DESCRIPTION

| Pin Name         | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|------------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT      | 10          | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP         | 1           | 1            | I/P           | ST                     | Master Clear (Reset) input or programming voltage input. This pin is an active low RESET to the device.                                                                                                      |

|                  |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0          | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1          | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-    | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+    | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI        | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4       | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                  |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software                                                                                                                                                    |

|                  |             |              |               | (1)                    | programmed for internal weak pull-up on all inputs.                                                                                                                                                          |

| RB0/INT          | 21          | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1              | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2              | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3/PGM          | 24          | 24           | I/O           | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4              | 25          | 25           | 1/0           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5              | 26          | 26           | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC          | 27          | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming clock.                                                                                                                                |

| RB7/PGD          | 28          | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                  |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI  | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2   | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1         | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL      | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA      | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO          | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK        | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                        |

| RC7/RX/DT        | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                          |

| Vss              | 8, 19       | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD              | 20          | 20           | Р             | _                      | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: L= input | O = outr    | 4            | 1/0           | input/output           | P = nower                                                                                                                                                                                                    |

$Legend: \quad I = input$

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| bit 7 |       | •     |       |       |       |       | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE  | T0IF  | INTF  | RBIF  |

| R/W-0 | R/W-x |

Note:

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 **PEIE**: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 **T0IE**: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 **T0IF**: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state; a mismatch condition will continue to set the bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared (must be cleared in software).

0 = None of the RB7:RB4 pins have changed state

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

| P | IC1 | 6 | F8 | <b>7</b> X |

|---|-----|---|----|------------|

|   |     | v |    | ,,,,       |

NOTES:

# PIC16F87X

NOTES:

# 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- · PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### **CCP1 Module:**

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

#### CCP2 Module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the  $PIC^{\otimes}$  MCU Mid-Range Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |  |  |

|----------|----------------|--|--|

| Capture  | Timer1         |  |  |

| Compare  | Timer1         |  |  |

| PWM      | Timer2         |  |  |

TABLE 8-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | <b>CCPy Mode</b> | Interaction                                                                          |

|-----------|------------------|--------------------------------------------------------------------------------------|

| Capture   | Capture          | Same TMR1 time-base                                                                  |

| Capture   | Compare          | The compare should be configured for the special event trigger, which clears TMR1    |

| Compare   | Compare          | The compare(s) should be configured for the special event trigger, which clears TMR1 |

| PWM       | PWM              | The PWMs will have the same frequency and update rate (TMR2 interrupt)               |

| PWM       | Capture          | None                                                                                 |

| PWM       | Compare          | None                                                                                 |

### REGISTER 9-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/A | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

bit 7 SMP: Sample bit

#### SPI Master mode:

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

#### SPI Slave mode:

SMP must be cleared when SPI is used in slave mode

#### In I<sup>2</sup>C Master or Slave mode:

- 1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)

- 0 = Slew rate control enabled for high speed mode (400 kHz)

- bit 6 **CKE**: SPI Clock Edge Select (Figure 9-2, Figure 9-3 and Figure 9-4)

#### SPI mode:

For CKP = 0

- 1 = Data transmitted on rising edge of SCK

- 0 = Data transmitted on falling edge of SCK

For CKP =

- 1 = Data transmitted on falling edge of SCK

- 0 = Data transmitted on rising edge of SCK

#### In I<sup>2</sup>C Master or Slave mode:

- 1 = Input levels conform to SMBus spec

- 0 =Input levels conform to  $I^2C$  specs

- bit 5 **D/A**: Data/Address bit (I<sup>2</sup>C mode only)

- 1 = Indicates that the last byte received or transmitted was data

- 0 = Indicates that the last byte received or transmitted was address

- bit 4 P: STOP bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

- 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)

- 0 = STOP bit was not detected last

- bit 3 S: START bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

- 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)

- 0 = START bit was not detected last

- bit 2 **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only)

This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit or not  $\overline{ACK}$  bit.

#### In I<sup>2</sup>C Slave mode:

- 1 = Read

- 0 = Write

# In I<sup>2</sup>C Master mode:

- 1 = Transmit is in progress

- 0 = Transmit is not in progress

Logical OR of this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode.

- bit 1 **UA**: Update Address (10-bit I<sup>2</sup>C mode only)

- 1 = Indicates that the user needs to update the address in the SSPADD register

- 0 = Address does not need to be updated

- bit **BF**: Buffer Full Status bit

### Receive (SPI and I<sup>2</sup>C modes):

- 1 = Receive complete, SSPBUF is full

- 0 = Receive not complete, SSPBUF is empty

#### Transmit (I<sup>2</sup>C mode only):

- 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full

- 0 = Data transmit complete (does not include the ACK and STOP bits), SSPBUF is empty

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### **REGISTER 9-2:** SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 0

WCOL: Write Collision Detect bit bit 7

Master mode:

- 1 = A write to SSPBUF was attempted while the I2C conditions were not valid

- 0 = No collision

#### Slave mode:

- 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software)

- 0 = No collision

- bit 6 SSPOV: Receive Overflow Indicator bit

#### In SPI mode:

- 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

#### In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

- 0 = No overflow

- bit 5 SSPEN: Synchronous Serial Port Enable bit

#### In SPI mode,

When enabled, these pins must be properly configured as input or output

- 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

#### In I<sup>2</sup>C mode,

When enabled, these pins must be properly configured as input or output

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4 CKP: Clock Polarity Select bit

#### In SPI mode:

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

# In I<sup>2</sup>C Slave mode:

### SCK release control

- 1 = Enable clock

- 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

#### In I<sup>2</sup>C Master mode:

Unused in this mode

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = Fosc/16

- 0010 = SPI Master mode, clock = Fosc/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 = SPI Slave mode, clock = SCK pin. SS pin control enabled.

- 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin.

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- 1000 =  $I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))

- 1011 = I<sup>2</sup>C Firmware Controlled Master mode (slave idle)

- 1110 = I<sup>2</sup>C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled

- 1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled

- 1001, 1010, 1100, 1101 = Reserved

| Ιe | a | er     | nd |   |

|----|---|--------|----|---|

|    | ч | $\sim$ | ·u | • |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

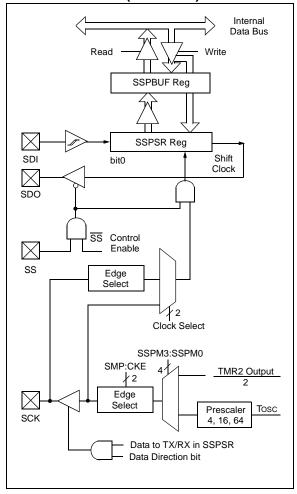

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and \$\overline{SS}\$ pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

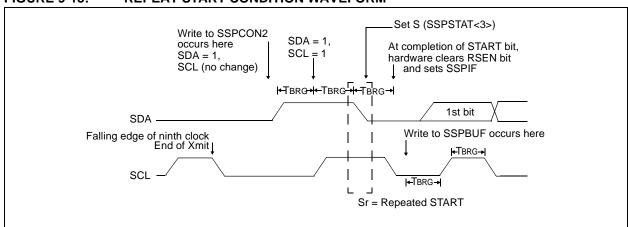

# 9.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG, while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

**Note** 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 9.2.10.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

#### FIGURE 9-13: REPEAT START CONDITION WAVEFORM

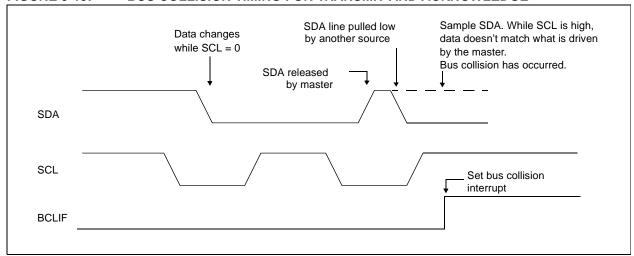

# 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $\rm I^2C$  port to its IDLE state (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $\rm I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-to-zero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

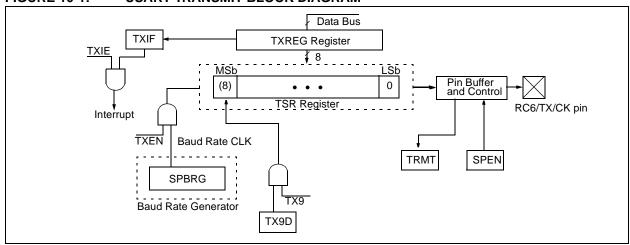

# 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

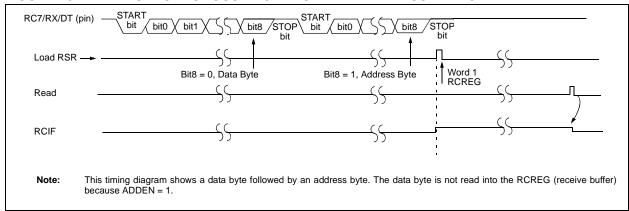

#### FIGURE 10-7: ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT

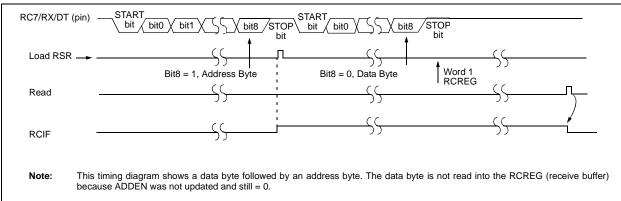

### FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other RESETS |

|------------------------|--------|----------------------|----------|-----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE      | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                 |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 1Ah                    | RCREG  | USART Re             | ceive Re | gister    |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h                    | SPBRG  | Baud Rate            | Generato | r Registe | r     |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# PIC16F87X

**NOTES:**

# 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16F87X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

LP Low Power CrystalXT Crystal/Resonator

• HS High Speed Crystal/Resonator

• RC Resistor/Capacitor

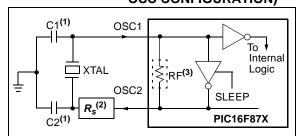

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

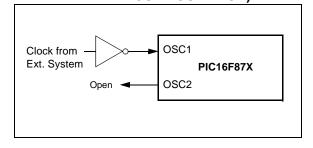

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F87X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 12-2).

FIGURE 12-1: CRYSTAL/CERAMIC

RESONATOR OPERATION

(HS, XT OR LP

OSC CONFIGURATION)

Note 1: See Table 12-1 and Table 12-2 for recommended values of C1 and C2.

- 2: A series resistor (R<sub>s</sub>) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen.

FIGURE 12-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR

LP OSC

CONFIGURATION)

TABLE 12-1: CERAMIC RESONATORS

| Ranges Tested: |          |             |             |  |  |  |  |

|----------------|----------|-------------|-------------|--|--|--|--|

| Mode           | OSC2     |             |             |  |  |  |  |

| XT             | 455 kHz  | 68 - 100 pF | 68 - 100 pF |  |  |  |  |

|                | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |  |

|                | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |  |

| HS             | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |  |  |  |  |

|                | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |  |  |  |  |

These values are for design guidance only. See notes following Table 12-2.

| Resonators Used: |                                                       |        |  |  |  |  |

|------------------|-------------------------------------------------------|--------|--|--|--|--|

| 455 kHz          | ± 0.3%                                                |        |  |  |  |  |

| 2.0 MHz          | Murata Erie CSA2.00MG                                 | ± 0.5% |  |  |  |  |

| 4.0 MHz          | Murata Erie CSA4.00MG                                 | ± 0.5% |  |  |  |  |

| 8.0 MHz          | Murata Erie CSA8.00MT                                 | ± 0.5% |  |  |  |  |

| 16.0 MHz         | Murata Erie CSA16.00MX                                | ± 0.5% |  |  |  |  |

| All resonat      | All resonators used did not have built-in capacitors. |        |  |  |  |  |

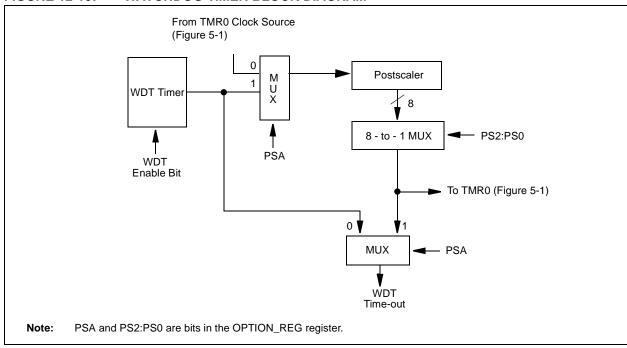

# 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of these bits.

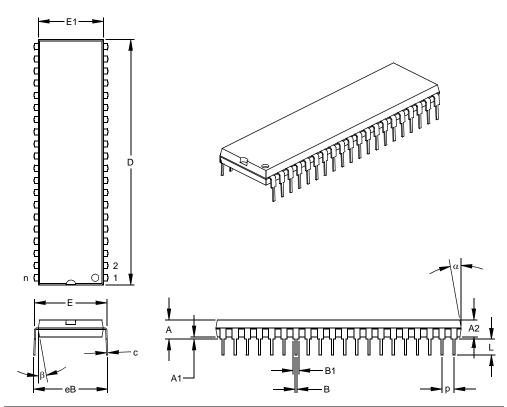

# 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units  | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|--------|---------|-------|-------|-------------|-------|-------|--|

| Dimension                  | Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n      |         | 40    |       |             | 40    |       |  |

| Pitch                      | р      |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α      | .160    | .175  | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2     | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1     | .015    |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | Е      | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1     | .530    | .545  | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D      | 2.045   | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L      | .120    | .130  | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С      | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1     | .030    | .050  | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В      | .014    | .018  | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eВ     | .620    | .650  | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α      | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β      | 5       | 10    | 15    | 5           | 10    | 15    |  |

<sup>\*</sup> Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>§</sup> Significant Characteristic

# **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                                                            |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 1998 | This is a new data sheet. However, these devices are similar to the PIC16C7X devices found in the PIC16C7X Data Sheet (DS30390). Data Memory Map for PIC16F873/874, moved ADFM bit from ADCON1<5> to ADCON1<7>. |

| В       | 1999 | FLASH EEPROM access information.                                                                                                                                                                                |

| С       | 2000 | DC characteristics updated. DC performance graphs added.                                                                                                                                                        |

| D       | 2013 | Added a note to each package drawing.                                                                                                                                                                           |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Difference             | PIC16F876/873                                             | PIC16F877/874                                               |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------|

| A/D                    | 5 channels,<br>10-bits                                    | 8 channels,<br>10-bits                                      |

| Parallel<br>Slave Port | no                                                        | yes                                                         |

| Packages               | 28-pin PDIP,<br>28-pin windowed<br>CERDIP, 28-pin<br>SOIC | 40-pin PDIP,<br>44-pin TQFP,<br>44-pin MQFP,<br>44-pin PLCC |

# PIC16F87X

| 0                                                  |

|----------------------------------------------------|

| On-Line Support                                    |

| OPCODE Field Descriptions                          |

| OPTION_REG Register                                |

| INTEDG Bit19                                       |

| PS2:PS0 Bits                                       |

| PSA Bit19                                          |

| T0CS Bit19                                         |

| T0SE Bit19                                         |

| OSC1/CLKIN Pin                                     |

| OSC2/CLKOUT Pin                                    |

| Oscillator Configuration                           |

| HS121, 124                                         |

| LP                                                 |

| RC                                                 |

| XT                                                 |

| Oscillator, WDT                                    |

| Oscillators                                        |

| Capacitor Selection                                |

| Crystal and Ceramic Resonators                     |

| RC                                                 |

| 122                                                |

| P                                                  |

| P (STOP bit)                                       |

| Package Marking Information                        |

| Packaging Information                              |

| Paging, Program Memory11, 26                       |

| Parallel Slave Port (PSP)                          |

| Associated Registers                               |

| Block Diagram38                                    |

| RE0/RD/AN5 Pin                                     |

| RE1/WR/AN6 Pin                                     |

| RE2/CS/AN7 Pin                                     |

| Read Waveforms                                     |

| Select (PSPMODE Bit)35, 36, 37, 38                 |

| Write Waveforms                                    |

| PCL Register                                       |

| PCLATH Register                                    |

|                                                    |

| PCON Register                                      |

| POR Bit                                            |

| PIC16F876 Pinout Description                       |

| PIC16F87X Product Identification System            |

| PICDEM 1 Low Cost PIC MCU                          |

|                                                    |

| Demonstration Board                                |

| PICDEM 2 Low Cost PIC16CXX                         |

|                                                    |

| Demonstration Board145 PICDEM 3 Low Cost PIC16CXXX |

|                                                    |

| Demonstration Board                                |

| PICSTART Plus Entry Level                          |

| Development Programmer                             |

| PIE1 Register                                      |

| PIE2 Register                                      |

| Pinout Descriptions                                |

| PIC16F873/PIC16F876                                |

| PIC16F874/PIC16F8778                               |

| PIR1 Register                                      |

| PIR2 Register                                      |

| POP26                                              |

| POR. See Power-on Reset                            |

| PORTA                              | 7, 8, 17  |

|------------------------------------|-----------|

| Analog Port Pins                   |           |

| Associated Registers               |           |

| Block Diagram                      |           |

| RA3:RA0 and RA5 Pins               | 29        |

| RA4/T0CKI Pin                      |           |

| Initialization                     |           |

| PORTA Register                     |           |

| RA3                                | 10, 23    |

| RA0 and RA5 Port Pins              | 20        |

| RA4/T0CKI Pin                      |           |

|                                    |           |

| RA5/SS/AN4 Pin                     |           |

| TRISA Register                     |           |

| PORTB                              |           |

| Associated Registers               | 32        |

| Block Diagram                      |           |

| RB3:RB0 Port Pins                  |           |

| RB7:RB4 Port Pins                  |           |

| PORTB Register                     | 15, 31    |

| RB0/INT Edge Select (INTEDG Bit)   |           |

| RB0/INT Pin, External              | 7, 8, 130 |

| RB7:RB4 Interrupt on Change        | 130       |

| RB7:RB4 Interrupt on Change Enable |           |

| (RBIE Bit)                         | 130       |

| RB7:RB4 Interrupt on Change Flag   |           |

| (RBIF Bit)                         | 130       |

| RB7:RB4 Interrupt-on-Change Enable |           |

| (RBIE Bit)                         | 20        |

| RB7:RB4 Interrupt-on-Change Flag   |           |

| (RBIF Bit)                         | 20 31     |

| TRISB Register                     |           |

| PORTC                              |           |

| Associated Registers               |           |

| Block Diagrams                     | 34        |

| S .                                |           |

| Peripheral Output Override         | 0.0       |

| (RC 0:2, 5:7)                      | 33        |

| Peripheral Output Override         |           |

| (RC 3:4)                           |           |

| PORTC Register                     |           |

| RC0/T10S0/T1CKI Pin                |           |

| RC1/T1OSI/CCP2 Pin                 |           |

| RC2/CCP1 Pin                       |           |

| RC3/SCK/SCL Pin                    | 7, 9      |

| RC4/SDI/SDA Pin                    | 7, 9      |

| RC5/SDO Pin                        | 7, 9      |

| RC6/TX/CK Pin                      | 7, 9, 96  |

| RC7/RX/DT Pin                      |           |

| TRISC Register                     |           |

| PORTD                              |           |

| Associated Registers               |           |

| Block Diagram                      |           |

| Parallel Slave Port (PSP) Function |           |

| PORTD Register                     |           |

| TRISD Register                     |           |

| I MOD Megiolei                     |           |

### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

# Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events