Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877t-20i-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

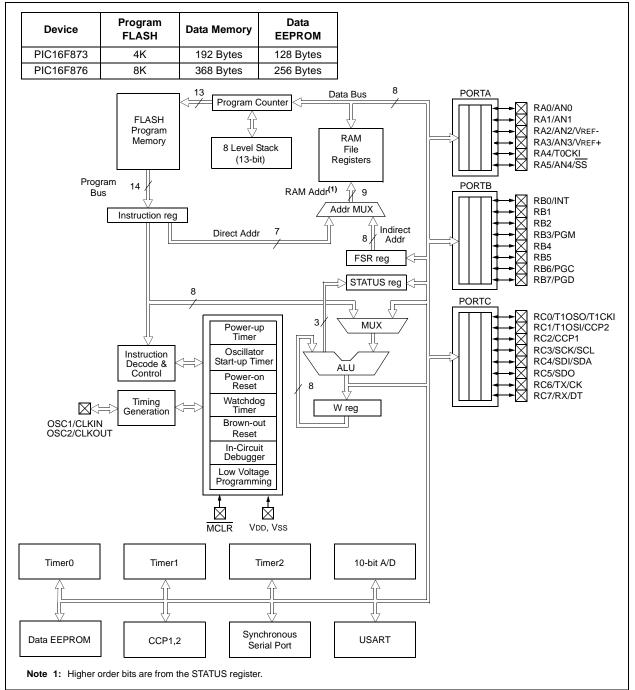

# 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin#     | l/O/P<br>Type        | Buffer<br>Type         | Description                                                                                            |

|-------------------|----------------|-------------------|-----------------|----------------------|------------------------|--------------------------------------------------------------------------------------------------------|

|                   |                |                   |                 |                      |                        | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15             | 16                | 32              | I/O                  | ST                     | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16             | 18                | 35              | I/O                  | ST                     | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17             | 19                | 36              | I/O                  | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                        |

| RC3/SCK/SCL       | 18             | 20                | 37              | I/O                  | ST                     | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23             | 25                | 42              | I/O                  | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                        |

| RC5/SDO           | 24             | 26                | 43              | I/O                  | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25             | 27                | 44              | I/O                  | ST                     | RC6 can also be the USART Asynchronous Transmi<br>or Synchronous Clock.                                |

| RC7/RX/DT         | 26             | 29                | 1               | I/O                  | ST                     | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                   |                |                   |                 |                      |                        | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19             | 21                | 38              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD1/PSP1          | 20             | 22                | 39              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD2/PSP2          | 21             | 23                | 40              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD3/PSP3          | 22             | 24                | 41              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD4/PSP4          | 27             | 30                | 2               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD5/PSP5          | 28             | 31                | 3               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD6/PSP6          | 29             | 32                | 4               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD7/PSP7          | 30             | 33                | 5               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

|                   |                |                   |                 |                      |                        | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8              | 9                 | 25              | I/O                  | ST/TTL <sup>(3)</sup>  | RE0 can also be read control for the parallel slave port, or analog input5.                            |

| RE1/WR/AN6        | 9              | 10                | 26              | I/O                  | ST/TTL <sup>(3)</sup>  | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10             | 11                | 27              | I/O                  | ST/TTL <sup>(3)</sup>  | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31          | 13,34             | 6,29            | Р                    | _                      | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32          | 12,35             | 7,28            | Р                    | _                      | Positive supply for logic and I/O pins.                                                                |

| NC                | -              | 1,17,28,<br>40    | 12,13,<br>33,34 |                      | —                      | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |                 | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                |

#### TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

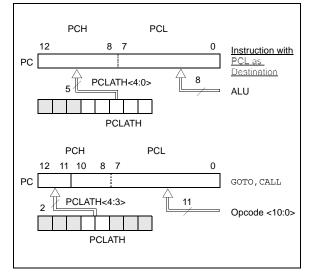

## 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| 5051_11 | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

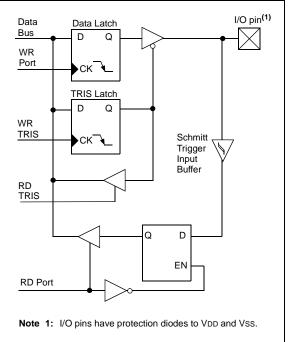

#### 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

#### FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name            | Bit# | Buffer Type           | Function                                                                                                                                                                                                                              |

|-----------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | hit0 | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| RE0/RD/AN5 bit0 |      | 51/112 /              | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6      | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7      | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE [ | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

#### 4.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F87X device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

#### TABLE 4-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Со  | nfiguration | Bits | Manageral          | Internal | Internal |           | ICSP Write |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP write |

| 0   | 0           | x    | All program memory | Yes      | No       | No        | No         |

| 0   | 1           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 0   | 1           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 0   | 1           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 0   | 1           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 1   | 0           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 1   | 0           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |

| TABLE 4-2: | REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH |

|------------|-----------------------------------------------------|

|            |                                                     |

| Address                 | Name   | Bit 7                                              | Bit 6     | Bit 5       | Bit 4     | Bit 3        | Bit 2     | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|----------------------------------------------------|-----------|-------------|-----------|--------------|-----------|-------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE                                                | PEIE      | TOIE        | INTE      | RBIE         | TOIF      | INTF  | RBIF   | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPRON                                             | Address   | s Register  | , Low Byt | е            |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Fh                    | EEADRH | —                                                  | —         | —           | EEPRON    | Address,     | High Byte | )     |        | xxxx xxxx                | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPRON                                             | l Data Re | egister, Lo | w Byte    |              |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | —                                                  | —         | EEPRO       | M Data Re | egister, Hig | h Byte    |       |        | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD                                              | _         | _           | —         | WRERR        | WREN      | WR    | RD     | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPROM Control Register2 (not a physical register) |           |             |           |              |           |       | _      | _                        |                                 |

| 8Dh                     | PIE2   | —                                                  | (1)       |             | EEIE      | BCLIE        | —         | _     | CCP2IE | -r-0 00                  | -r-0 00                         |

| 0Dh                     | PIR2   | _                                                  | (1)       | _           | EEIF      | BCLIF        | _         | _     | CCP2IF | -r-0 00                  | -r-0 00                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

#### TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6                                                    | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|----------------------------------------------------------|-------|-------|-------|--------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                                     | TOIE  | INTE  | RBIE  | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                     | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                     | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | Synchronous Serial Port Receive Buffer/Transmit Register |       |       |       |        |        |        |                       | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV                                                    | SSPEN | CKP   | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE                                                      | D/A   | Р     | S     | R/W    | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

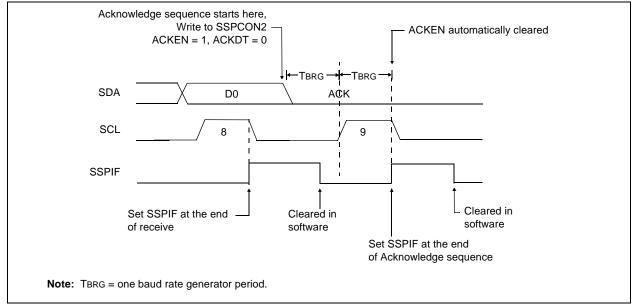

#### 9.2.13 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted high. When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode (Figure 9-16).

#### 9.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-16: ACKNOWLEDGE SEQUENCE WAVEFORM

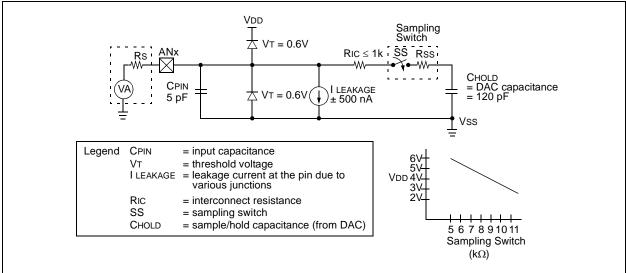

#### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

#### EQUATION 11-1: ACQUISITION TIME

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the  $PIC^{\textcircled{R}}$  MCU Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient    |

|------|---------------------------------------------------------------------------------------------|

|      | = $TAMP + TC + TCOFF$                                                                       |

|      | $= 2\mu s + TC + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$                         |

| TC   | = CHOLD (RIC + RSS + RS) $In(1/2047)$                                                       |

|      | = $-120 \text{pF} (1 \text{k}\Omega + 7 \text{k}\Omega + 10 \text{k}\Omega) \ln(0.0004885)$ |

|      | $= 16.47 \mu s$                                                                             |

| TACQ | = $2\mu s + 16.47\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$                |

|      | $= 19.72 \mu s$                                                                             |

| L    |                                                                                             |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

## 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

#### 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5   | Bit 4                                               | Bit 3 | Bit 2    | Bit 1       | Bit 0  | Value on<br>POR,<br>BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|------------|---------|-----------------------------------------------------|-------|----------|-------------|--------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE    | INTE                                                | RBIE  | TOIF     | INTF        | RBIF   | 0000 000x               | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF    | TXIF                                                | SSPIF | CCP1IF   | TMR2IF      | TMR1IF | 0000 0000               | 0000 0000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE    | TXIE                                                | SSPIE | CCP1IE   | TMR2IE      | TMR1IE | 0000 0000               | 0000 0000                         |

| 1Eh                   | ADRESH | A/D Resul            | t Register | High By | High Byte                                           |       |          |             |        |                         | uuuu uuuu                         |

| 9Eh                   | ADRESL | A/D Resul            | t Register | Low Byt | e                                                   |       |          |             |        | xxxx xxxx               | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2    | CHS1                                                | CHS0  | GO/DONE  | _           | ADON   | 0000 00-0               | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | —          | _       | _                                                   | PCFG3 | PCFG2    | PCFG1       | PCFG0  | 0- 0000                 | 0- 0000                           |

| 85h                   | TRISA  | —                    | —          | PORTA   | PORTA Data Direction Register                       |       |          |             |        |                         | 11 1111                           |

| 05h                   | PORTA  |                      | —          | PORTA   | PORTA Data Latch when written: PORTA pins when read |       |          |             |        | 0x 0000                 | 0u 0000                           |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV    | PSPMODE                                             | _     | PORTE Da | ta Directio | n bits | 0000 -111               | 0000 -111                         |

| 09h <sup>(1)</sup>    | PORTE  | —                    | —          |         | —                                                   | —     | RE2      | RE1         | RE0    | xxx                     | uuu                               |

## TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

#### 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

#### 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

#### 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

## 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| Register   |     | Dev | ices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|------------|-----|-----|------|-----|------------------------------------|---------------------------|---------------------------------|--|

| W          | 873 | 874 | 876  | 877 | XXXX XXXX                          | <u>uuuu</u> uuuu          | uuuu uuuu                       |  |

| INDF       | 873 | 874 | 876  | 877 | N/A                                | N/A                       | N/A                             |  |

| TMR0       | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |

| PCL        | 873 | 874 | 876  | 877 | 0000h                              | 0000h                     | PC + 1 <sup>(2)</sup>           |  |

| STATUS     | 873 | 874 | 876  | 877 | 0001 1xxx                          | 000q quuu <sup>(3)</sup>  | uuuq quuu <sup>(3)</sup>        |  |

| FSR        | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| PORTA      | 873 | 874 | 876  | 877 | 0x 0000                            | 0u 0000                   | uu uuuu                         |  |

| PORTB      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| PORTC      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| PORTD      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| PORTE      | 873 | 874 | 876  | 877 | xxx                                | uuu                       | uuu                             |  |

| PCLATH     | 873 | 874 | 876  | 877 | 0 0000                             | 0 0000                    | u uuuu                          |  |

| INTCON     | 873 | 874 | 876  | 877 | x000 0000                          | 0000 000u                 | uuuu uuuu <b>(1)</b>            |  |

| PIR1       | 873 | 874 | 876  | 877 | r000 0000                          | r000 0000                 | ruuu uuuu <b>(1)</b>            |  |

|            | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu <b>(1)</b>            |  |

| PIR2       | 873 | 874 | 876  | 877 | -r-0 00                            | -r-0 00                   | -r-u uu <b>(1)</b>              |  |

| TMR1L      | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |  |

| TMR1H      | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |  |

| T1CON      | 873 | 874 | 876  | 877 | 00 0000                            | uu uuuu                   | uu uuuu                         |  |

| TMR2       | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |

| T2CON      | 873 | 874 | 876  | 877 | -000 0000                          | -000 0000                 | -uuu uuuu                       |  |

| SSPBUF     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |

| SSPCON     | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | սսսս սսսս                       |  |

| CCPR1L     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |  |

| CCPR1H     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |

| CCP1CON    | 873 | 874 | 876  | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |  |

| RCSTA      | 873 | 874 | 876  | 877 | x000 0000                          | 0000 000x                 | uuuu uuuu                       |  |

| TXREG      | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |

| RCREG      | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |

| CCPR2L     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |  |

| CCPR2H     | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| CCP2CON    | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |

| ADRESH     | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |  |

| ADCON0     | 873 | 874 | 876  | 877 | 0000 00-0                          | 0000 00-0                 | uuuu uu-u                       |  |

| OPTION_REG | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |

| TRISA      | 873 | 874 | 876  | 877 | 11 1111                            | 11 1111                   | uu uuuu                         |  |

| TRISB      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |

| TRISC      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |

| TRISD      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |  |

| TRISE      | 873 | 874 | 876  | 877 | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |  |

| PIE1       | 873 | 874 | 876  | 877 | r000 0000                          | r000 0000                 | ruuu uuuu                       |  |

|            | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |  |

#### TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

## 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

#### 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

## 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

#### 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

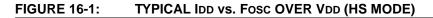

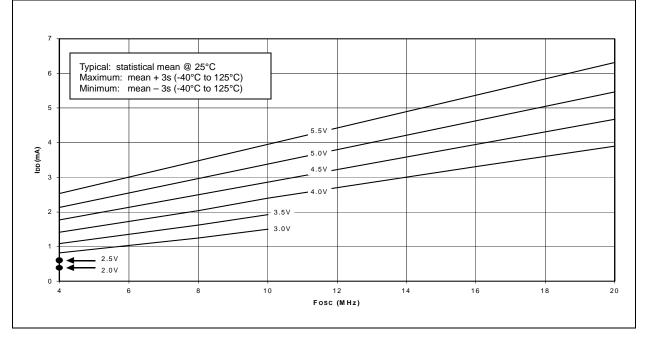

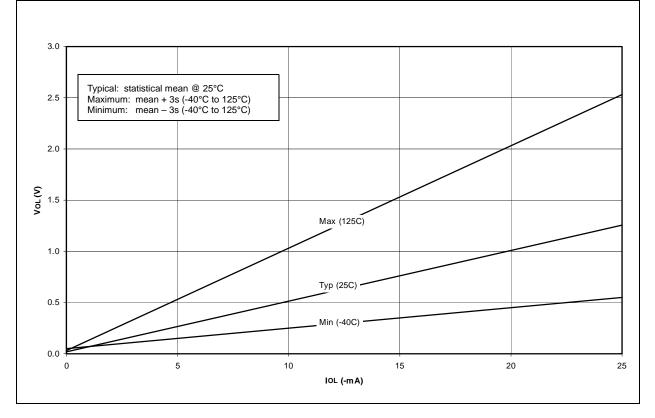

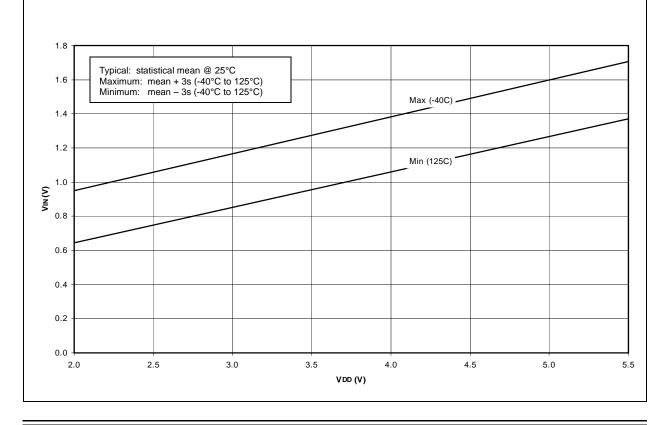

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented is **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

# PIC16F87X

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. Vdd, (TTL INPUT, -40°C TO 125°C)

# 17.0 PACKAGING INFORMATION

## 17.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

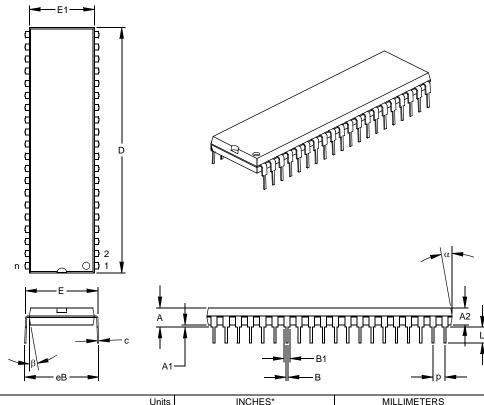

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | Units INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-------|---------------|-------|-------|-------------|-------|-------|--|

| Dimensio                   | MIN   | NOM           | MAX   | MIN   | NOM         | MAX   |       |  |

| Number of Pins             | n     |               | 40    |       |             | 40    |       |  |

| Pitch                      | р     |               | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .160          | .175  | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2    | .140          | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1    | .015          |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E     | .595          | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1    | .530          | .545  | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D     | 2.045         | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L     | .120          | .130  | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С     | .008          | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1    | .030          | .050  | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В     | .014          | .018  | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eB    | .620          | .650  | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α     | 5             | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β     | 5             | 10    | 15    | 5           | 10    | 15    |  |

| * 0 / " D /                |       |               |       |       |             |       |       |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

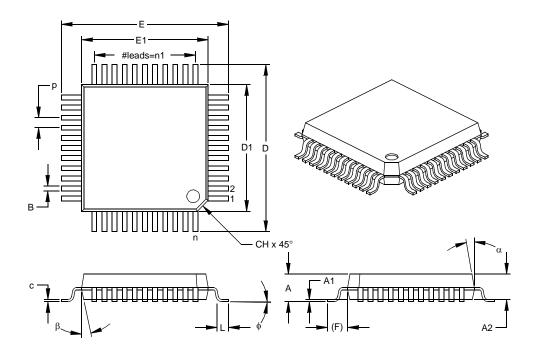

## 44-Lead Plastic Metric Quad Flatpack (PQ) 10x10x2 mm Body, 1.6/0.15 mm Lead Form (MQFP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      |      |      | MILLIMETERS* |       |       |

|--------------------------|-------|------|------|------|--------------|-------|-------|

| Dimension Limits         |       | MIN  | NOM  | MAX  | MIN          | NOM   | MAX   |

| Number of Pins           | n     |      | 44   |      |              | 44    |       |

| Pitch                    | р     |      | .031 |      |              | 0.80  |       |

| Pins per Side            | n1    |      | 11   |      |              | 11    |       |

| Overall Height           | А     | .079 | .086 | .093 | 2.00         | 2.18  | 2.35  |

| Molded Package Thickness | A2    | .077 | .080 | .083 | 1.95         | 2.03  | 2.10  |

| Standoff §               | A1    | .002 | .006 | .010 | 0.05         | 0.15  | 0.25  |

| Foot Length              | L     | .029 | .035 | .041 | 0.73         | 0.88  | 1.03  |

| Footprint (Reference)    | (F)   |      | .063 |      |              | 1.60  |       |

| Foot Angle               | ø     | 0    | 3.5  | 7    | 0            | 3.5   | 7     |

| Overall Width            | E     | .510 | .520 | .530 | 12.95        | 13.20 | 13.45 |

| Overall Length           | D     | .510 | .520 | .530 | 12.95        | 13.20 | 13.45 |

| Molded Package Width     | E1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Molded Package Length    | D1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Lead Thickness           | С     | .005 | .007 | .009 | 0.13         | 0.18  | 0.23  |

| Lead Width               | В     | .012 | .015 | .018 | 0.30         | 0.38  | 0.45  |

| Pin 1 Corner Chamfer     | СН    | .025 | .035 | .045 | 0.64         | 0.89  | 1.14  |

| Mold Draft Angle Top     | α     | 5    | 10   | 15   | 5            | 10    | 15    |

| Mold Draft Angle Bottom  | β     | 5    | 10   | 15   | 5            | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-022 Drawing No. C04-071

| PWM Mode61                                   |

|----------------------------------------------|

| Block Diagram61                              |

| Duty Cycle61                                 |

| Example Frequencies/Resolutions (Table)62    |

| PWM Period61                                 |

| Special Event Trigger and A/D Conversions60  |

| CCP. See Capture/Compare/PWM                 |

| CCP1CON                                      |

| CCP2CON                                      |

| CCPR1H Register 15, 17, 57                   |

| CCPR1L Register 17, 57                       |

| CCPR2H Register                              |

| CCPR2L Register 15, 17                       |

| CCPxM0 bit58                                 |

| CCPxM1 bit58                                 |

| CCPxM2 bit58                                 |

| CCPxM3 bit58                                 |

| CCPxX bit                                    |

| CCPxY bit58                                  |

| CKE                                          |

| CKP67                                        |

| Clock Polarity Select bit, CKP67             |

| Code Examples                                |

| Call of a Subroutine in Page 1 from Page 026 |

| EEPROM Data Read43                           |

| EEPROM Data Write43                          |

| FLASH Program Read44                         |

| FLASH Program Write45                        |

| Indirect Addressing27                        |

| Initializing PORTA29                         |

| Saving STATUS, W and PCLATH Registers        |

| Code Protected Operation                     |

| Data EEPROM and FLASH Program Memory45       |

| Code Protection                              |

| Computed GOTO26                              |

| Configuration Bits119                        |

| Configuration Word120                        |

| Conversion Considerations                    |

|                                              |

# D

| D/Ā                                           |         |

|-----------------------------------------------|---------|

| Data EEPROM                                   |         |

| Associated Registers                          | 46      |

| Code Protection                               | 45      |

| Reading                                       |         |

| Special Functions Registers                   | 41      |

| Spurious Write Protection                     | 45      |

| Write Verify                                  | 45      |

| Writing to                                    | 43      |

| Data Memory                                   | 12      |

| Bank Select (RP1:RP0 Bits)                    | 12, 18  |

| General Purpose Registers                     | 12      |

| Register File Map                             | 13, 14  |

| Special Function Registers                    | 15      |

| Data/Address bit, D/A                         | 66      |

| DC and AC Characteristics Graphs and Tables . |         |

| DC Characteristics                            |         |

| Commercial and Industrial                     | 152–156 |

| Extended                                      | 157–160 |

| Development Support                           | 143     |

| Device Differences                            |         |

| Device Overview                               | 5       |

| Direct Addressing                             | 27      |

|                                               |         |

## Е

| Electrical Characteristics                                | . 149 |

|-----------------------------------------------------------|-------|

| Errata<br>External Clock Input (RA4/T0CKI). See Timer0    | 4     |

| External Interrupt Input (RB0/INT). See Interrupt Source: | s     |

| F                                                         |       |

| Firmware Instructions                                     | . 135 |

| FLASH Program Memory                                      | 41    |

| FLASH Program Memory                    | 41            |

|-----------------------------------------|---------------|

| Associated Registers                    | 46            |

| Code Protection                         | 45            |

| Configuration Bits and Read/Write State | 46            |

| Reading                                 | 44            |

| Special Function Registers              | 41            |

| Spurious Write Protection               | 45            |

| Write Protection                        | 46            |

| Write Verify                            | 45            |

| Writing to                              | 44            |

| FSR Register1                           | 5, 16, 17, 27 |

| -                                       |               |

# G

| General Call Address Sequence | 76 |

|-------------------------------|----|

| General Call Address Support  |    |

| General Call Enable bit       | 68 |

## L

| -                                                     |    |   |

|-------------------------------------------------------|----|---|

| I/O Ports                                             | 29 | Э |

| I <sup>2</sup> C                                      | 73 | 3 |

| I <sup>2</sup> C Bus                                  |    |   |

| Connection Considerations                             | -  |   |

| Sample Device Configuration                           |    |   |

| I <sup>2</sup> C Master Mode Reception                |    |   |

| I <sup>2</sup> C Master Mode Repeated START Condition |    |   |

| I <sup>2</sup> C Mode Selection                       | 73 | 3 |

| I <sup>2</sup> C Module                               |    |   |

| Acknowledge Sequence Timing                           |    |   |

| Addressing                                            |    |   |

| Associated Registers                                  |    |   |

| Baud Rate Generator                                   |    |   |

| Block Diagram                                         |    |   |

| BRG Block Diagram                                     |    |   |

| BRG Reset due to SDA Collision                        |    |   |

| BRG Timing                                            |    |   |

| Bus Arbitration                                       |    |   |

| Bus Collision                                         |    |   |

| Acknowledge<br>Repeated START Condition               |    |   |

| Repeated START Condition Timing                       | 92 | - |

| (Case1)                                               | 0  | 2 |

| Repeated START Condition Timing                       | 92 | - |

| (Case2)                                               | 92 | , |

| START Condition                                       |    |   |

| START Condition Timing                                |    |   |

| STOP Condition                                        |    |   |

| STOP Condition Timing (Case1)                         |    |   |

| STOP Condition Timing (Case2)                         |    |   |

| Transmit Timing                                       |    |   |

| Bus Collision Timing                                  |    |   |

| Clock Arbitration                                     | 88 | 3 |

| Clock Arbitration Timing (Master Transmit)            |    |   |

| Conditions to not give ACK Pulse                      |    |   |

| General Call Address Support                          |    |   |

| Master Mode                                           | 78 | 3 |

| Master Mode 7-bit Reception Timing                    | 85 | 5 |

| Master Mode Block Diagram                             | 78 | 3 |

## 0

| On-Line Support                |               |

|--------------------------------|---------------|

| OPCODE Field Descriptions      |               |

| OPTION_REG Register            |               |

| INTEDG Bit                     |               |

|                                |               |

| PS2:PS0 Bits                   |               |

| PSA Bit                        |               |

| T0CS Bit                       |               |

| T0SE Bit                       |               |

| OSC1/CLKIN Pin                 |               |

| OSC2/CLKOUT Pin                |               |

| Oscillator Configuration       |               |

| HS                             |               |

| LP                             |               |

| RC                             | 121, 122, 124 |

| ХТ                             |               |

| Oscillator, WDT                |               |

| Oscillators                    |               |

| Capacitor Selection            |               |

| Crystal and Ceramic Resonators | 121           |

| RC                             |               |

|                                |               |

## Ρ

| P (STOP bit)                            |                 |

|-----------------------------------------|-----------------|

| Package Marking Information             |                 |

| Packaging Information                   |                 |

| Paging, Program Memory                  |                 |

| Parallel Slave Port (PSP)               | 9, 35, 38       |

| Associated Registers                    |                 |

| Block Diagram                           |                 |

| RE0/RD/AN5 Pin                          |                 |

| RE1/WR/AN6 Pin                          | 9, 36, 38       |

| RE2/CS/AN7 Pin                          | 9, 36, 38       |

| Read Waveforms                          |                 |

| Select (PSPMODE Bit)                    | .35, 36, 37, 38 |

| Write Waveforms                         |                 |

| PCL Register                            | 15, 16, 26      |

| PCLATH Register                         | .15, 16, 17, 26 |

| PCON Register                           |                 |

| BOR Bit                                 | 25              |

| POR Bit                                 |                 |

| PIC16F876 Pinout Description            | 7               |

| PIC16F87X Product Identification System |                 |

| PICDEM 1 Low Cost PIC MCU               |                 |

| Demonstration Board                     |                 |

| PICDEM 17 Demonstration Board           |                 |

| PICDEM 2 Low Cost PIC16CXX              |                 |

| Demonstration Board                     |                 |

| PICDEM 3 Low Cost PIC16CXXX             |                 |

| Demonstration Board                     |                 |

| PICSTART Plus Entry Level               |                 |

| Development Programmer                  |                 |

| PIE1 Register                           | 21              |

| PIE2 Register                           | 23              |

| Pinout Descriptions                     |                 |

| PIC16F873/PIC16F876                     | 7               |

| PIC16F874/PIC16F877                     | 8               |

| PIR1 Register                           |                 |

| PIR2 Register                           |                 |

| POP                                     |                 |

| POR. See Power-on Reset                 |                 |

| POR | RTA7, 8                            |          |

|-----|------------------------------------|----------|

|     | Analog Port Pins                   | 7, 8     |

|     | Associated Registers               | 30       |

|     | Block Diagram                      |          |

|     | RA3:RA0 and RA5 Pins               | 20       |

|     |                                    |          |

|     | RA4/T0CKI Pin                      |          |

|     | Initialization                     | 29       |

|     | PORTA Register1                    | 5, 29    |

|     | RA3                                |          |

|     | RA0 and RA5 Port Pins              | . 29     |

|     | RA4/T0CKI Pin                      |          |

|     |                                    |          |

|     | RA5/SS/AN4 Pin                     |          |

|     | TRISA Register                     |          |

| POR | ЯТВ7,                              | 8, 17    |

|     | Associated Registers               | 32       |

|     | Block Diagram                      |          |

|     | RB3:RB0 Port Pins                  | 31       |

|     | RB7:RB4 Port Pins                  |          |

|     |                                    |          |

|     | PORTB Register1                    | 5, 31    |

|     | RB0/INT Edge Select (INTEDG Bit)   |          |

|     | RB0/INT Pin, External7, 8          | , 130    |

|     | RB7:RB4 Interrupt on Change        | . 130    |

|     | RB7:RB4 Interrupt on Change Enable |          |

|     | (RBIE Bit)                         | 130      |

|     |                                    | . 150    |

|     | RB7:RB4 Interrupt on Change Flag   |          |

|     | (RBIF Bit)                         | . 130    |

|     | RB7:RB4 Interrupt-on-Change Enable |          |

|     | (RBIE Bit)                         | 20       |

|     | RB7:RB4 Interrupt-on-Change Flag   |          |

|     | (RBIF Bit)2                        | 0 31     |

|     | TRISB Register                     |          |

|     |                                    |          |

| POR | RTC                                |          |

|     | Associated Registers               | 34       |

|     | Block Diagrams                     |          |

|     | Peripheral Output Override         |          |

|     | (RC 0:2, 5:7)                      | 33       |

|     | Peripheral Output Override         |          |

|     | (RC 3:4)                           | 22       |

|     |                                    |          |

|     | PORTC Register1                    |          |

|     | RC0/T1OSO/T1CKI Pin                |          |

|     | RC1/T1OSI/CCP2 Pin                 | 7, 9     |

|     | RC2/CCP1 Pin                       | 7, 9     |

|     | RC3/SCK/SCL Pin                    | 7.9      |

|     | RC4/SDI/SDA Pin                    |          |

|     | RC5/SDO Pin                        |          |

|     |                                    |          |

|     | RC6/TX/CK Pin7,                    |          |

|     | RC7/RX/DT Pin7, 9, 9               |          |

|     | TRISC Register                     | 3, 95    |

| POR | RTD                                | 7, 38    |

|     | Associated Registers               |          |

|     | Block Diagram                      |          |

|     | Devolution Days (DCD) Function     | ათ<br>იი |

|     | Parallel Slave Port (PSP) Function |          |

|     | PORTD Register1                    |          |

|     | TRISD Register                     | 35       |

NOTES: