#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf873-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

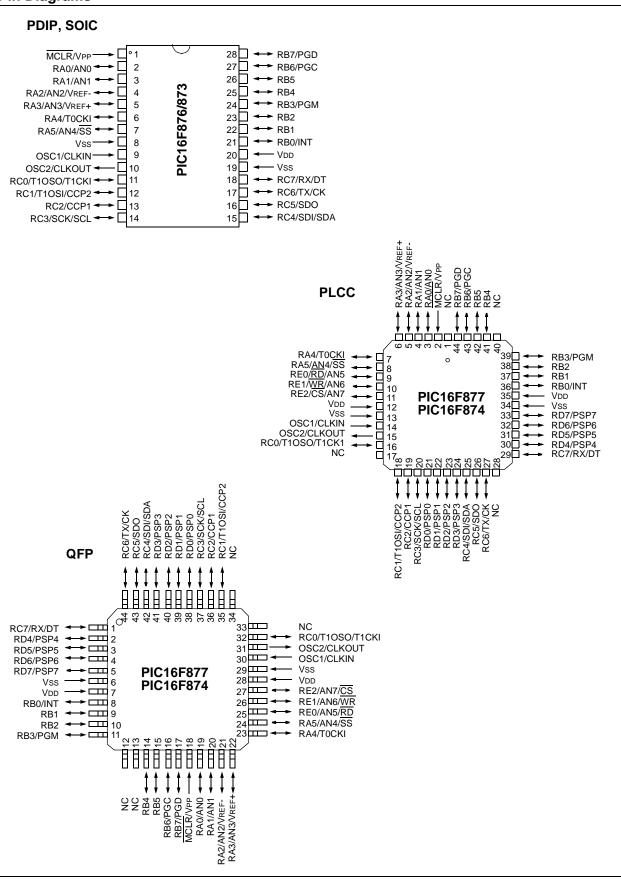

#### **Pin Diagrams**

#### **Table of Contents**

| 1.0   | Device Overview                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | I/O Ports                                                                   |     |

| 4.0   | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0   | Timer0 Module                                                               |     |

| 6.0   | Timer1 Module                                                               |     |

| 7.0   | Timer2 Module                                                               |     |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0  | Special Features of the CPU                                                 | 119 |

| 13.0  | Instruction Set Summary                                                     | 135 |

|       | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 16.0  | DC and AC Characteristics Graphs and Tables                                 | 177 |

| 17.0  | Packaging Information                                                       | 189 |

| Appe  | ndix A: Revision History                                                    | 197 |

| Appe  | ndix B: Device Differences                                                  | 197 |

|       | ndix C: Conversion Considerations                                           |     |

| Index | (                                                                           | 199 |

|       | ine Support                                                                 |     |

| Read  | ler Response                                                                | 208 |

| PIC1  | 6F87X Product Identification System                                         | 209 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin# | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|----------------|-------------------|-------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13             | 14                | 30          | I                    | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14             | 15                | 31          | 0                    | —                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1              | 2                 | 18          | I/P                  | ST                     | Master Clear (Reset) input or programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                        |

|                   |                |                   |             |                      |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2              | 3                 | 19          | I/O                  | TTL                    | RA0 can also be analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 3              | 4                 | 20          | I/O                  | TTL                    | RA1 can also be analog input1.                                                                                                                                                                                    |

| RA2/AN2/VREF-     | 4              | 5                 | 21          | I/O                  | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                               |

| RA3/AN3/VREF+     | 5              | 6                 | 22          | I/O                  | TTL                    | RA3 can also be analog input3 or positive<br>analog reference voltage.                                                                                                                                            |

| RA4/T0CKI         | 6              | 7                 | 23          | I/O                  | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                          |

| RA5/SS/AN4        | 7              | 8                 | 24          | I/O                  | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                                |

|                   |                |                   |             |                      |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33             | 36                | 8           | I/O                  | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1               | 34             | 37                | 9           | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB2               | 35             | 38                | 10          | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB3/PGM           | 36             | 39                | 11          | I/O                  | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                                |

| RB4               | 37             | 41                | 14          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB5               | 38             | 42                | 15          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB6/PGC           | 39             | 43                | 16          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                                  |

| RB7/PGD           | 40             | 44                | 17          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                                   |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |             | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

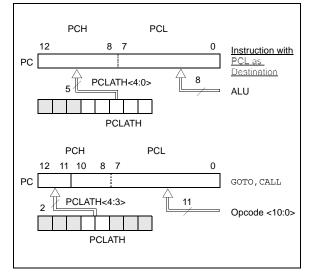

## 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| _       | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

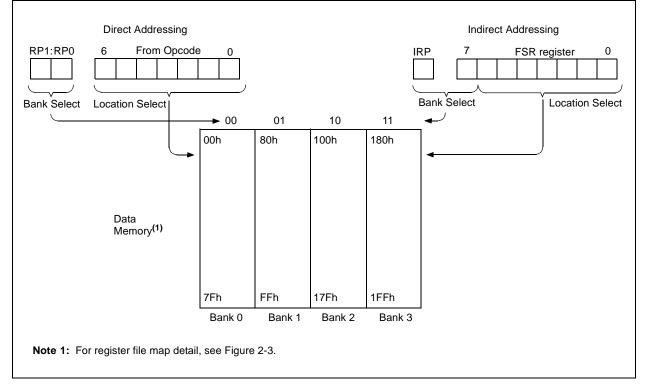

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

NOTES:

#### 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

### 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

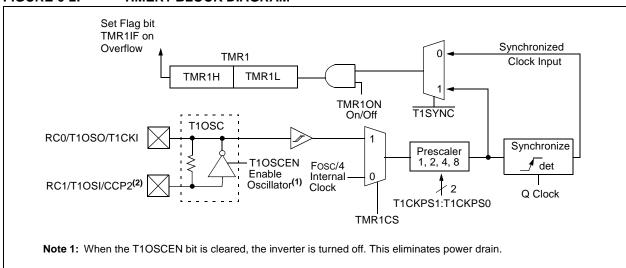

# 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

|         | U-0                                                                    | U-0                                                | R/W-0           | R/W-0          | R/W-0            | R/W-0       | R/W-0         | R/W-0  |  |

|---------|------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|------------------|-------------|---------------|--------|--|

|         | _                                                                      | _                                                  | T1CKPS1         | T1CKPS0        | T1OSCEN          | T1SYNC      | TMR1CS        | TMR10N |  |

|         | bit 7                                                                  |                                                    |                 |                |                  |             |               | bit 0  |  |

|         |                                                                        |                                                    |                 |                |                  |             |               |        |  |

| bit 7-6 | Unimplem                                                               | ented: Rea                                         | id as '0'       |                |                  |             |               |        |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits               |                                                    |                 |                |                  |             |               |        |  |

|         |                                                                        | 11 = 1:8 Prescale value                            |                 |                |                  |             |               |        |  |

|         |                                                                        | 10 = 1:4 Prescale value<br>01 = 1:2 Prescale value |                 |                |                  |             |               |        |  |

|         | • = • • • • •                                                          | rescale valu                                       |                 |                |                  |             |               |        |  |

| bit 3   | T1OSCEN                                                                | : Timer1 Os                                        | cillator Enal   | ble Control b  | it               |             |               |        |  |

|         | 1 = Oscillat                                                           | tor is enable                                      | ed              |                |                  |             |               |        |  |

|         | 0 = Oscillat                                                           | tor is shut-c                                      | off (the oscill | ator inverter  | is turned off to | eliminate p | ower drain    | )      |  |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Control bit        |                                                    |                 |                |                  |             |               |        |  |

|         | <u>When TMR1CS = 1:</u><br>1 = Do not synchronize external clock input |                                                    |                 |                |                  |             |               |        |  |

|         |                                                                        | •                                                  |                 |                |                  |             |               |        |  |

|         | When TMR                                                               |                                                    | nal clock inp   | Jul            |                  |             |               |        |  |

|         |                                                                        |                                                    | ner1 uses th    | e internal clo | ock when TMR     | 1CS = 0.    |               |        |  |

| bit 1   | TMR1CS: Timer1 Clock Source Select bit                                 |                                                    |                 |                |                  |             |               |        |  |

|         | 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)       |                                                    |                 |                |                  |             |               |        |  |

|         | 0 = Internal clock (Fosc/4)                                            |                                                    |                 |                |                  |             |               |        |  |

| bit 0   | TMR10N:                                                                |                                                    | bit             |                |                  |             |               |        |  |

|         | 1 = Enables Timer1                                                     |                                                    |                 |                |                  |             |               |        |  |

|         | 0 = Stops Timer1                                                       |                                                    |                 |                |                  |             |               |        |  |

|         | · · ·                                                                  |                                                    |                 |                |                  |             |               |        |  |

|         | Legend:                                                                |                                                    |                 |                |                  |             |               |        |  |

|         | R = Reada                                                              |                                                    |                 | Vritable bit   | U = Unimpl       |             |               |        |  |

|         | - n = Value                                                            | at POR                                             | '1' = E         | Bit is set     | '0' = Bit is c   | leared      | x = Bit is ur | nknown |  |

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

#### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

#### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

#### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                    | Freq. C1 C2                          |              |           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|-----------|--|--|--|

| LP                                                                                                                                                                                                                                                                                                          | 32 kHz                               | 33 pF        | 33 pF     |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 100 kHz                              | 15 pF        | 15 pF     |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 200 kHz                              | 15 pF        | 15 pF     |  |  |  |

| These va                                                                                                                                                                                                                                                                                                    | lues are for o                       | design guida | nce only. |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                            |                                      |              |           |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                  | Hz Epson C-001R32.768K-A ± 20 PPM    |              |           |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                     | 00 kHz Epson C-2 100.00 KC-P ± 20 PP |              |           |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                     | STD XTL 200.000 kHz ± 20 PPM         |              |           |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                      |              |           |  |  |  |

#### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address                                | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h                                    | TXSTA | CSRC  | TX9   | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h                                    | RCSTA | SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                       |

| 99h SPBRG Baud Rate Generator Register |       |       |       |       |       |       |       |       |       | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

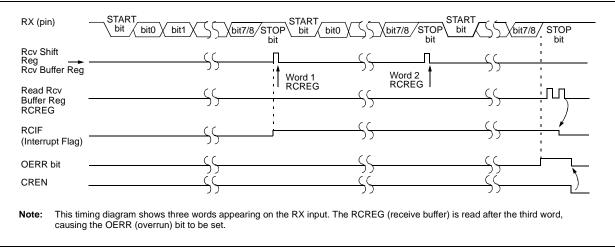

#### FIGURE 10-5: ASYNCHRONOUS RECEPTION

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                                | Name   | Bit 7                | Bit 6       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|----------------------------------------|--------|----------------------|-------------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE        | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9         | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                                    | RCREG  | USART R              | leceive Reg | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9         | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |             |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

#### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

NOTES:

|                       | >                    | >                                |                                                                    |                                                                                            |                                          |                                | ``````````````````````````````````````               | *                                           |                                  |                                  |                                  |                                                 |                                   | >                                 | >                                  | >                         | >                                 | >                                                 | >                                                   |                             |

|-----------------------|----------------------|----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|------------------------------------------------------|---------------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------------------------------|-----------------------------------|-----------------------------------|------------------------------------|---------------------------|-----------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|

|                       | _                    | >                                | × × ×                                                              | ~                                                                                          |                                          |                                | >                                                    |                                             |                                  |                                  |                                  |                                                 |                                   | >                                 | >                                  |                           |                                   |                                                   |                                                     |                             |

|                       | _                    | >                                | <b>`</b>                                                           | ~                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       | _                    | >                                | >                                                                  | ~                                                                                          |                                          |                                | >                                                    |                                             |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       | _                    |                                  |                                                                    |                                                                                            |                                          |                                | L                                                    | >                                           |                                  | >                                |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     | <u> </u>                    |

|                       | >                    |                                  | >                                                                  | ~                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 | >                                 |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  |                                                                    |                                                                                            |                                          |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  | >                                |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          |                                          | >                              | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        | *                              | >                                                    | >                                           | <b>*</b> +                       | ,+                               |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | **/                                                                                        |                                          |                                | **/                                                  | **/                                         |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        | *                              | >                                                    | >                                           |                                  | ÷,                               |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          | >                                        |                                | >                                                    | >                                           | >                                |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | >                                                                                          |                                          |                                | >                                                    | >                                           |                                  |                                  |                                  | `                                               |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

|                       |                      |                                  | >                                                                  | `                                                                                          | >                                        |                                | >                                                    | >                                           |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

| MBLAB® C17 C Compiler | PLAB® C17 C Compiler | PLAB <sup>®</sup> C18 C Compiler | PASM <sup>TM</sup> Assembler/<br>PLINK <sup>TM</sup> Object Linker | MPLAB <sup>®</sup> ICE In-Circuit Emulator                                                 | ICEPIC <sup>TM</sup> In-Circuit Emulator | PLAB®ICD In-Circuit<br>ebugger | PICSTART® Plus Entry Level<br>Development Programmer | PRO MATE® II<br>Universal Device Programmer | PICDEM™ 1 Demonstration<br>Board | PICDEM™ 2 Demonstration<br>Board | PICDEM™ 3 Demonstration<br>Board | PICDEM <sup>TM</sup> 14A Demonstration<br>Board | PICDEM™ 17 Demonstration<br>Board | EELoo <sup>®</sup> Evaluation Kit | εεLoα <sup>®</sup> Transponder Kit | iicrolD™ Programmer's Kit | 25 kHz microlD™<br>eveloper's Kit | 125 kHz Anticollision microlD™<br>Developer's Kit | 13.56 MHz Anticollision<br>microlD™ Developer's Kit | MCP2510 CAN Developer's Kit |

|                       |                      |                                  |                                                                    | MPLAB® C17 C Compile<br>MPLAB® C18 C Compile<br>MPASM™ Assembler/<br>MPLINK™ Object Linker |                                          |                                |                                                      |                                             |                                  |                                  |                                  |                                                 |                                   |                                   |                                    |                           |                                   |                                                   |                                                     |                             |

| TABLE 14-1: | DEVELOPMENT TOOLS FROM MICROCHIP |

|-------------|----------------------------------|

|-------------|----------------------------------|

© 1998-2013 Microchip Technology Inc.

## 15.5 Timing Parameter Symbology

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                    | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                       | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                       |           |                                        |

| F                     | Frequency                             | т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:  |           |                                        |

| рр                    |                                       |           |                                        |

| сс                    | CCP1                                  | osc       | OSC1                                   |

| ck                    | CLKOUT                                | rd        | RD                                     |

| cs                    | CS                                    | rw        | RD or WR                               |

| di                    | SDI                                   | sc        | SCK                                    |

| do                    | SDO                                   | SS        | SS                                     |

| dt                    | Data in                               | tO        | TOCKI                                  |

| io                    | I/O port                              | t1        | T1CKI                                  |

| mc                    | MCLR                                  | wr        | WR                                     |

| Upperca               | ase letters and their meanings:       |           |                                        |

| S                     |                                       |           |                                        |

| F                     | Fall                                  | Р         | Period                                 |

| Н                     | High                                  | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                | V         | Valid                                  |

| L                     | Low                                   | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                       |           |                                        |

| AA                    | output access                         | High      | High                                   |

| BUF                   | Bus free                              | Low       | Low                                    |

| Tcc:st (              | I <sup>2</sup> C specifications only) |           |                                        |

| CC                    |                                       |           |                                        |

| HD                    | Hold                                  | SU        | Setup                                  |

| ST                    |                                       |           |                                        |

| DAT                   | DATA input hold                       | STO       | STOP condition                         |

| STA                   | START condition                       |           |                                        |

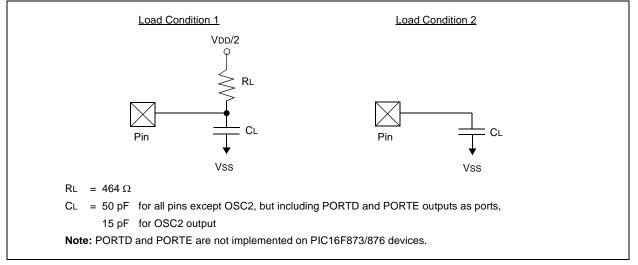

#### FIGURE 15-5: LOAD CONDITIONS

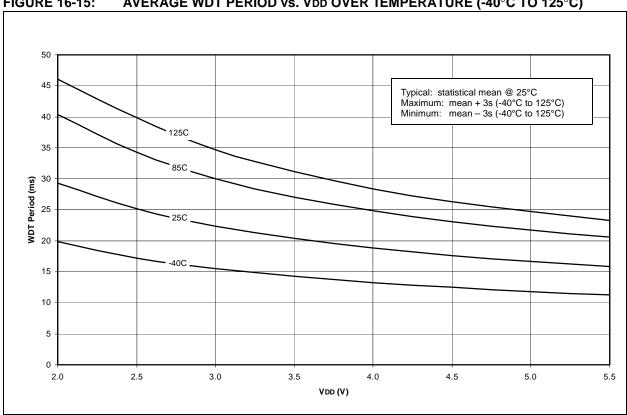

#### FIGURE 16-15: AVERAGE WDT PERIOD vs. VDD OVER TEMPERATURE (-40°C TO 125°C)

NOTES:

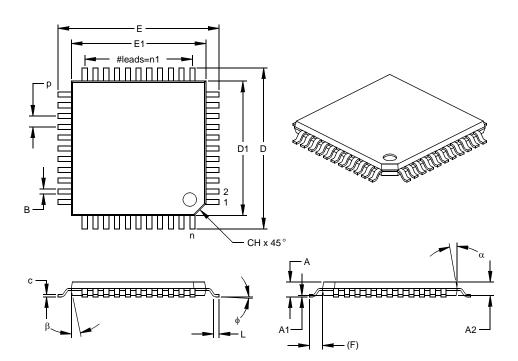

## 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES |      | MILLIMETERS* |       |       |  |  |

|--------------------------|----------|------|--------|------|--------------|-------|-------|--|--|

| Dimension                | n Limits | MIN  | NOM    | MAX  | MIN          | NOM   | MAX   |  |  |

| Number of Pins           | n        |      | 44     |      |              | 44    |       |  |  |

| Pitch                    | р        |      | .031   |      |              | 0.80  |       |  |  |

| Pins per Side            | n1       |      | 11     |      |              | 11    |       |  |  |

| Overall Height           | А        | .039 | .043   | .047 | 1.00         | 1.10  | 1.20  |  |  |

| Molded Package Thickness | A2       | .037 | .039   | .041 | 0.95         | 1.00  | 1.05  |  |  |

| Standoff §               | A1       | .002 | .004   | .006 | 0.05         | 0.10  | 0.15  |  |  |

| Foot Length              | L        | .018 | .024   | .030 | 0.45         | 0.60  | 0.75  |  |  |

| Footprint (Reference)    | (F)      |      | .039   |      | 1.00         |       |       |  |  |

| Foot Angle               | φ        | 0    | 3.5    | 7    | 0            | 3.5   | 7     |  |  |

| Overall Width            | Е        | .463 | .472   | .482 | 11.75        | 12.00 | 12.25 |  |  |

| Overall Length           | D        | .463 | .472   | .482 | 11.75        | 12.00 | 12.25 |  |  |

| Molded Package Width     | E1       | .390 | .394   | .398 | 9.90         | 10.00 | 10.10 |  |  |

| Molded Package Length    | D1       | .390 | .394   | .398 | 9.90         | 10.00 | 10.10 |  |  |

| Lead Thickness           | С        | .004 | .006   | .008 | 0.09         | 0.15  | 0.20  |  |  |

| Lead Width               | В        | .012 | .015   | .017 | 0.30         | 0.38  | 0.44  |  |  |

| Pin 1 Corner Chamfer     | СН       | .025 | .035   | .045 | 0.64         | 0.89  | 1.14  |  |  |

| Mold Draft Angle Top     | α        | 5    | 10     | 15   | 5            | 10    | 15    |  |  |

| Mold Draft Angle Bottom  | β        | 5    | 10     | 15   | 5            | 10    | 15    |  |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-026 Drawing No. C04-076

## APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|

| Pins              | 28/40                                               | 28/40                                                      |

| Timers            | 3                                                   | 3                                                          |

| Interrupts        | 11 or 12                                            | 13 or 14                                                   |

| Communication     | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Slave) | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Master/Slave) |

| Frequency         | 20 MHz                                              | 20 MHz                                                     |

| Voltage           | 2.5V - 5.5V                                         | 2.0V - 5.5V                                                |

| A/D               | 8-bit                                               | 10-bit                                                     |

| CCP               | 2                                                   | 2                                                          |

| Program<br>Memory | 4K, 8K<br>EPROM                                     | 4K, 8K<br>FLASH                                            |

| RAM               | 192, 368<br>bytes                                   | 192, 368<br>bytes                                          |

| EEPROM data       | None                                                | 128, 256<br>bytes                                          |

| Other             | _                                                   | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming      |

| Bus Collision During a Repeated                         |        |

|---------------------------------------------------------|--------|

| START Condition (Case 1)                                | 2      |

| Bus Collision During a Repeated                         |        |

| START Condition (Case2)92                               | 2      |

| Bus Collision During a START                            |        |

| Condition (SCL = 0)                                     |        |

| Bus Collision During a STOP Condition                   |        |

| Bus Collision for Transmit and Acknowledge              |        |

| Capture/Compare/PWM                                     | 2<br>2 |

| I <sup>2</sup> C Bus Data                               | י<br>1 |

| I <sup>2</sup> C Bus START/STOP bits                    | י<br>ר |

| I <sup>2</sup> C Master Mode First START Bit Timing     |        |

| I <sup>2</sup> C Master Mode Reception Timing           |        |

| I <sup>2</sup> C Master Mode Transmission Timing83      | 3      |

| Master Mode Transmit Clock Arbitration                  | 3      |

| Power-up Timer164                                       | 1      |

| Repeat START Condition81                                |        |

| RESET164                                                |        |

| SPI Master Mode70                                       |        |

| SPI Slave Mode (CKE = 1)                                |        |

| SPI Slave Mode Timing (CKE = 0)                         |        |

| Start-up Timer164<br>STOP Condition Receive or Transmit |        |

| Time-out Sequence on Power-up                           |        |

| Timer0                                                  |        |

| Timer1                                                  |        |

| USART Asynchronous Master Transmission                  |        |

| USART Asynchronous Reception                            |        |

| USART Synchronous Receive 173                           |        |

| USART Synchronous Reception 108                         |        |