Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 5x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

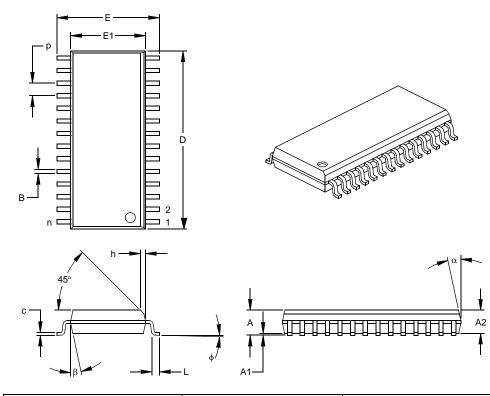

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf873t-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | I/O Ports                                                                   |     |

| 4.0   | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0   | Timer0 Module                                                               |     |

| 6.0   | Timer1 Module                                                               |     |

| 7.0   | Timer2 Module                                                               |     |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0  | Special Features of the CPU                                                 | 119 |

| 13.0  | Instruction Set Summary                                                     | 135 |

|       | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 16.0  | DC and AC Characteristics Graphs and Tables                                 | 177 |

| 17.0  | Packaging Information                                                       | 189 |

| Appe  | ndix A: Revision History                                                    | 197 |

| Appe  | ndix B: Device Differences                                                  | 197 |

|       | ndix C: Conversion Considerations                                           |     |

| Index | (                                                                           | 199 |

|       | ine Support                                                                 |     |

| Read  | ler Response                                                                | 208 |

| PIC1  | 6F87X Product Identification System                                         | 209 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|---------------------|--------------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                  | 10           | 0             | —                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                   | 1            | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                     |              |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                   | 2            | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                   | 3            | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                   | 4            | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                   | 5            | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                   | 6            | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                   | 7            | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                     |              |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                  | 22           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                  | 23           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                  | 24           | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                  | 25           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                  | 26           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                     |              |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                  | 11           | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                  | 12           | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                  | 13           | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                  | 14           | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                  | 15           | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                  | 16           | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                  | 17           | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                  | 18           | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19               | 8, 19        | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                  | 20           | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not |              |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| Address              | Name       | Bit 7                | Bit 6           | Bit 5                      | Bit 4          | Bit 3        | Bit 2             | Bit 1        | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|------------|----------------------|-----------------|----------------------------|----------------|--------------|-------------------|--------------|----------|--------------------------|------------------------|

| Bank 1               |            |                      |                 |                            |                |              |                   |              |          |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | g this location | n uses conte               | ents of FSR to | address dat  | a memory (no      | a physical r | egister) | 0000 0000                | 27                     |

| 81h                  | OPTION_REG | RBPU                 | INTEDG          | TOCS                       | T0SE           | PSA          | PS2               | PS1          | PS0      | 1111 1111                | 19                     |

| 82h <sup>(3)</sup>   | PCL        | Program C            | Counter (PC)    | Least Signif               | icant Byte     |              |                   |              |          | 0000 0000                | 26                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1             | RP0                        | TO             | PD           | Z                 | DC           | С        | 0001 1xxx                | 18                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ata Memory A    | Address Poir               | nter           |              |                   |              |          | xxxx xxxx                | 27                     |

| 85h                  | TRISA      | _                    |                 | PORTA Da                   | ta Direction R | egister      |                   |              |          | 11 1111                  | 29                     |

| 86h                  | TRISB      | PORTB Da             | ata Direction   | Register                   |                |              |                   |              |          | 1111 1111                | 31                     |

| 87h                  | TRISC      | PORTC D              | ata Direction   | Register                   |                |              |                   |              |          | 1111 1111                | 33                     |

| 88h <sup>(4)</sup>   | TRISD      | PORTD D              | ata Direction   | Register                   |                |              |                   |              |          | 1111 1111                | 35                     |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF             | IBOV                       | PSPMODE        |              | PORTE Data        | Direction Bi | its      | 0000 -111                | 37                     |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _                    | _               | _                          | Write Buffer   | for the uppe | r 5 bits of the F | Program Cou  | unter    | 0 0000                   | 26                     |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE            | TOIE                       | INTE           | RBIE         | T0IF              | INTF         | RBIF     | 0000 000x                | 20                     |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE            | RCIE                       | TXIE           | SSPIE        | CCP1IE            | TMR2IE       | TMR1IE   | 0000 0000                | 21                     |

| 8Dh                  | PIE2       | _                    | (5)             |                            | EEIE           | BCLIE        | _                 |              | CCP2IE   | -r-0 00                  | 23                     |

| 8Eh                  | PCON       | _                    | POR BOR         |                            |                |              |                   |              |          | dd                       | 25                     |

| 8Fh                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | —                      |

| 90h                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT         | ACKDT                      | ACKEN          | RCEN         | PEN               | RSEN         | SEN      | 0000 0000                | 68                     |

| 92h                  | PR2        | Timer2 Pe            | riod Register   | r                          |                |              |                   |              |          | 1111 1111                | 55                     |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po   | ort (I <sup>2</sup> C mode | ) Address Re   | gister       |                   |              |          | 0000 0000                | 73, 74                 |

| 94h                  | SSPSTAT    | SMP                  | CKE             | D/A                        | Р              | S            | R/W               | UA           | BF       | 0000 0000                | 66                     |

| 95h                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 96h                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 97h                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 98h                  | TXSTA      | CSRC                 | TX9             | TXEN                       | SYNC           | _            | BRGH              | TRMT         | TX9D     | 0000 -010                | 95                     |

| 99h                  | SPBRG      | Baud Rate            | e Generator F   | Register                   |                |              |                   |              |          | 0000 0000                | 97                     |

| 9Ah                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 9Bh                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 9Ch                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 9Dh                  | —          | Unimplem             | ented           |                            |                |              |                   |              |          | _                        | _                      |

| 9Eh                  | ADRESL     | A/D Result           | t Register Lo   | w Byte                     |                |              |                   |              |          | xxxx xxxx                | 116                    |

| 9Fh                  | ADCON1     | ADFM                 | _               | _                          | —              | PCFG3        | PCFG2             | PCFG1        | PCFG0    | 0 0000                   | 112                    |

#### **TABLE 2-1:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

## 3.4 **PORTD and TRISD Registers**

PORTD and TRISD are not implemented on the PIC16F873 or PIC16F876.

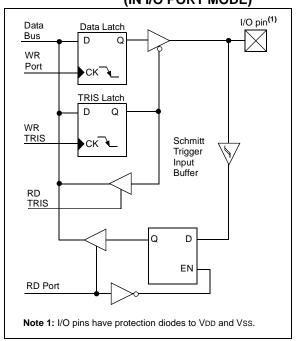

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

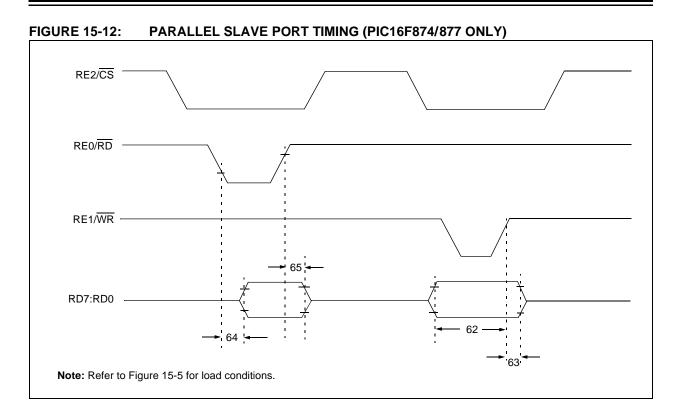

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

#### FIGURE 3-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

## TABLE 3-7: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

## TABLE 3-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6                         | Bit 5 | Bit 4                               | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|-------------------------------|-------|-------------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 08h     | PORTD | RD7   | RD6                           | RD5   | RD4                                 | RD3   | RD2   | RD1   | RD0   | xxxx xxxx                | uuuu uuuu                       |

| 88h     | TRISD | PORT  | PORTD Data Direction Register |       |                                     |       |       |       |       | 1111 1111                | 1111 1111                       |

| 89h     | TRISE | IBF   | OBF                           | IBOV  | PSPMODE — PORTE Data Direction Bits |       |       |       |       | 0000 -111                | 0000 -111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

## 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

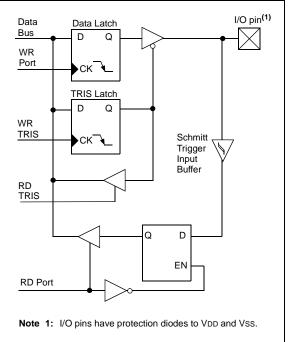

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

## FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit#                   | Buffer Type           | Function                                                                                                                                                                                                                              |

|------------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0                   | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| REU/RD/ANS | DITU                   | 51/11L <sup>,</sup>   | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6 | bit1                   | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7 | RE2/CS/AN7 bit2 ST/TTL |                       | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

## TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE [ | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

## 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

## 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

#### 5.2 Using Timer0 with an External Clock

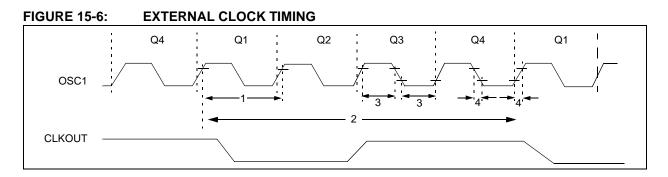

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**REGISTER 5-1: OPTION REG REGISTER**

DANA

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|               | R/W-1                                                                                                                                                                                                                                                                                                             | R/W-1        | R/W-1        | R/W-1        | R/W-1          | R/W-1     | R/W-1          | R/W-1  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|----------------|-----------|----------------|--------|--|

|               | RBPU                                                                                                                                                                                                                                                                                                              | INTEDG       | T0CS         | TOSE         | PSA            | PS2       | PS1            | PS0    |  |

|               | bit 7                                                                                                                                                                                                                                                                                                             |              |              |              |                |           |                | bit 0  |  |

|               |                                                                                                                                                                                                                                                                                                                   |              |              |              |                |           |                |        |  |

| bit 7         | RBPU                                                                                                                                                                                                                                                                                                              |              |              |              |                |           |                |        |  |

| bit 6         | INTEDG                                                                                                                                                                                                                                                                                                            |              |              |              |                |           |                |        |  |

| bit 5         | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                                                                                                                                                                        |              |              |              |                |           |                |        |  |

| bit 4         | <b>T0SE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin                                                                                                                                                         |              |              |              |                |           |                |        |  |

| bit 3         | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                                                                                                                                                           |              |              |              |                |           |                |        |  |

| bit 2-0       | PS2:PS0:                                                                                                                                                                                                                                                                                                          | Prescaler Ra | ite Select b | oits         |                |           |                |        |  |

|               | Bit Value                                                                                                                                                                                                                                                                                                         | TMR0 Rate    | WDT Rat      | e            |                |           |                |        |  |

|               | 000         1:2         1:1           001         1:4         1:2           010         1:8         1:4           011         1:16         1:8           100         1:32         1:16           101         1:64         1:32           110         1:128         1:64           111         1:256         1:128 |              |              |              |                |           |                |        |  |

|               | Legend:                                                                                                                                                                                                                                                                                                           |              |              |              |                |           |                |        |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                         | able bit     | VV = V       | Vritable bit | U = Unimple    | emented b | it, read as '( | )'     |  |

|               | - n = Value                                                                                                                                                                                                                                                                                                       | e at POR     | '1' = E      | Bit is set   | '0' = Bit is c | leared    | x = Bit is ur  | nknown |  |

|               |                                                                                                                                                                                                                                                                                                                   |              |              |              |                |           |                |        |  |

| ily Reference | To avoid an unintended device RESET, the instruction sequence shown in the PIC <sup>®</sup> MCU Mid-Range Fam-<br>ily Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0<br>to the WDT. This sequence must be followed even if the WDT is disabled.                   |              |              |              |                |           |                |        |  |

Note:

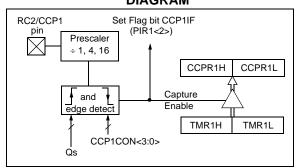

## 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

The type of event is configured by control bits CCP1M3:CCP1M0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

## 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

## 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in operating mode.

## 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       | •           |   |                        |

|-------|-------------|---|------------------------|

| CLRF  | CCP1CON     | ; | Turn CCP module off    |

| MOVLW | NEW_CAPT_PS | ; | Load the W reg with    |

|       |             | ; | the new prescaler      |

|       |             | ; | move value and CCP ON  |

| MOVWF | CCP1CON     | ; | Load CCP1CON with this |

|       |             | ; | value                  |

|       |             |   |                        |

| 1     |             |   |                        |

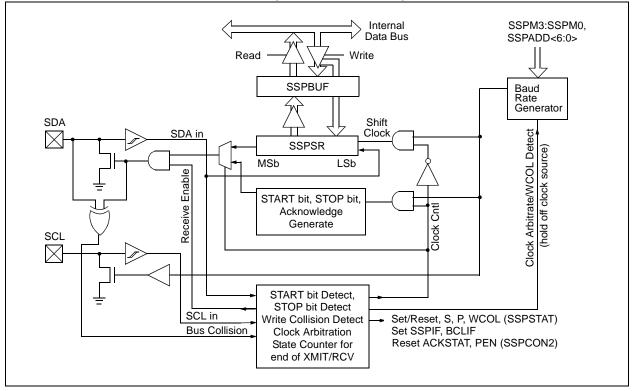

## 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

## FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

## 9.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP module must be in an IDLE state     |

|-------|---------------------------------------------|

|       | before the RCEN bit is set, or the RCEN bit |

|       | will be disregarded.                        |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high), and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

## 9.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 9.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

## 9.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

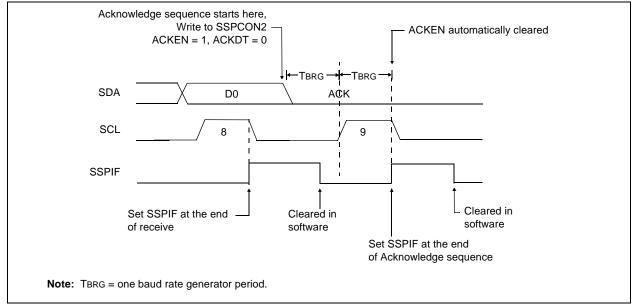

#### 9.2.13 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted high. When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode (Figure 9-16).

#### 9.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-16: ACKNOWLEDGE SEQUENCE WAVEFORM

## 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth

receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6      | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|------------|-----------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE      | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9        | SREN      | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re  | gister    |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9        | TXEN      | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Generate | or Regist | er    |       |        |        |        | 0000 0000                | 0000 0000                       |

## TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the other devices.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, VSS, RA2, or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the  $PIC^{\textcircled{R}}$  MCU Mid-Range Family Reference Manual (DS33023).

## REGISTER 11-1: ADCON0 REGISTER (ADDRESS: 1Fh)

|         |                                                                                                                                                                                                                                                                                                                       |             | -      | -     |       |         |     |       |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|-------|-------|---------|-----|-------|--|

|         | R/W-0                                                                                                                                                                                                                                                                                                                 | R/W-0       | R/W-0  | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |  |

|         | ADCS1                                                                                                                                                                                                                                                                                                                 | ADCS0       | CHS2   | CHS1  | CHS0  | GO/DONE | —   | ADON  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                 |             |        |       |       |         |     | bit 0 |  |

|         |                                                                                                                                                                                                                                                                                                                       |             |        |       |       |         |     |       |  |

| bit 7-6 | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from the internal A/D module RC oscillator)                                                                                                                                                    |             |        |       |       |         |     |       |  |

| bit 5-3 | <b>CHS2:CHS0</b> : Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)<br>$101 = channel 5, (RE0/AN5)^{(1)}$<br>$110 = channel 6, (RE1/AN6)^{(1)}$<br>$111 = channel 7, (RE2/AN7)^{(1)}$ |             |        |       |       |         |     |       |  |

| bit 2   | <ul> <li>GO/DONE: A/D Conversion Status bit</li> <li>If ADON = 1:</li> <li>1 = A/D conversion in progress (setting this bit starts the A/D conversion)</li> <li>0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)</li> </ul>                     |             |        |       |       |         |     |       |  |

| bit 1   | Unimpleme                                                                                                                                                                                                                                                                                                             | ented: Read | as '0' |       |       |         |     |       |  |

| bit 0   | ADON: A/D On bit<br>1 = A/D converter module is operating<br>0 = A/D converter module is shut-off and consumes no operating current                                                                                                                                                                                   |             |        |       |       |         |     |       |  |

|         | <b>Note 1:</b> These channels are not available on PIC16F873/876 devices.                                                                                                                                                                                                                                             |             |        |       |       |         |     |       |  |

|         | Legend:                                                                                                                                                                                                                                                                                                               |             |        |       |       |         |     |       |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 3.2).

## 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F873/874 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876/877 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

| MOVWF  | W TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

|        |                | · 1                                                     |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W TEMP,W       | ;Swap W TEMP into W                                     |

|        | -              | - <u>-</u>                                              |

#### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

## 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

|              | Param Sum Characteristic |                                            |           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commerciaOperating voltage VDD range as described in DC specification(Section 15.1) |     |       |                                                                        |  |  |

|--------------|--------------------------|--------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym                      | Characteristic                             | Min       | Тур†                                                                                                                                                                                                                                                            | Мах | Units | Conditions                                                             |  |  |

|              | Vol                      | Output Low Voltage                         |           |                                                                                                                                                                                                                                                                 |     |       |                                                                        |  |  |

| D080         |                          | I/O ports                                  |           |                                                                                                                                                                                                                                                                 | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |  |

| D083         |                          | OSC2/CLKOUT (RC osc config)                | —         | —                                                                                                                                                                                                                                                               | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |  |

|              | Voh                      | Output High Voltage                        |           |                                                                                                                                                                                                                                                                 |     |       |                                                                        |  |  |

| D090         |                          | I/O ports <sup>(3)</sup>                   | Vdd - 0.7 |                                                                                                                                                                                                                                                                 | _   | V     | Юн = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |

| D092         |                          | OSC2/CLKOUT (RC osc config)                | Vdd - 0.7 | _                                                                                                                                                                                                                                                               | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                           |  |  |

| D150*        | Vod                      | Open-Drain High Voltage                    |           | _                                                                                                                                                                                                                                                               | 8.5 | V     | RA4 pin                                                                |  |  |

|              |                          | Capacitive Loading Specs on<br>Output Pins |           |                                                                                                                                                                                                                                                                 |     |       |                                                                        |  |  |

| D100         | Cosc2                    | OSC2 pin                                   | _         |                                                                                                                                                                                                                                                                 | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |  |  |

| D101         | Cio                      | All I/O pins and OSC2 (RC mode)            | _         | —                                                                                                                                                                                                                                                               | 50  | pF    |                                                                        |  |  |

| D102         | Св                       | SCL, SDA (I <sup>2</sup> C mode)           |           | _                                                                                                                                                                                                                                                               | 400 | pF    |                                                                        |  |  |