Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874-04-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

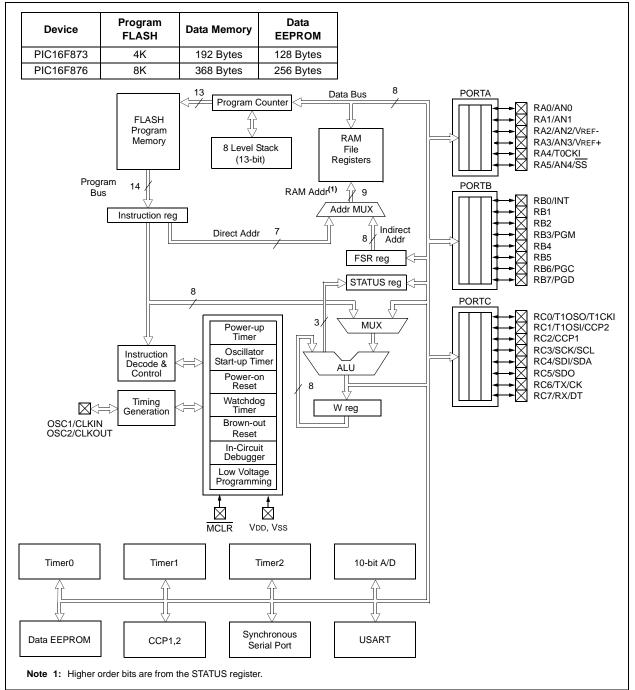

# 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

# PIC16F87X

NOTES:

## 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                        | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|--|--|

|               | GIE                                                                                          | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |  |  |

|               | bit 7                                                                                        |                               |               |              |                  |             |                | bit 0      |  |  |  |  |

|               |                                                                                              |                               |               |              |                  |             |                |            |  |  |  |  |

| bit 7         | GIE: Global Interrupt Enable bit                                                             |                               |               |              |                  |             |                |            |  |  |  |  |

|               | <ul> <li>1 = Enables all unmasked interrupts</li> <li>0 = Disables all interrupts</li> </ul> |                               |               |              |                  |             |                |            |  |  |  |  |

| <b>h</b> :+ C |                                                                                              |                               |               | L:4          |                  |             |                |            |  |  |  |  |

| bit 6         | -                                                                                            | pheral Interr                 | •             |              | -                |             |                |            |  |  |  |  |

|               |                                                                                              | s all unmas                   |               | •            | 5                |             |                |            |  |  |  |  |

| bit 5         |                                                                                              | 0 Overflow                    | =             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                              | s the TMR0                    |               |              |                  |             |                |            |  |  |  |  |

|               | 0 = Disable                                                                                  | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |  |  |

| bit 4         |                                                                                              | /INT Externa                  | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                              | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |  |  |

| bit 3         |                                                                                              | Port Change                   |               | •            |                  |             |                |            |  |  |  |  |

| bit 0         |                                                                                              | s the RB po                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                              | es the RB po                  |               |              |                  |             |                |            |  |  |  |  |

| bit 2         | TOIF: TMR                                                                                    | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |  |  |

|               |                                                                                              |                               |               |              | eared in softwa  | re)         |                |            |  |  |  |  |

|               |                                                                                              | register did                  |               |              |                  |             |                |            |  |  |  |  |

| bit 1         |                                                                                              | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |  |  |

|               |                                                                                              | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |  |  |

| bit 0         |                                                                                              | Port Change                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                              | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |  |  |

|               |                                                                                              | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |  |  |

|               |                                                                                              | be cleared in<br>of the RB7:R | ,             | ve changed   | stata            |             |                |            |  |  |  |  |

|               |                                                                                              |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |  |  |

|               | Legend:                                                                                      |                               |               |              |                  |             |                |            |  |  |  |  |

|               | R = Reada                                                                                    | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |  |  |

|               | - n = Value                                                                                  |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |  |  |

|               |                                                                                              |                               |               |              |                  |             |                | -          |  |  |  |  |

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt, the SSP bus collision interrupt and the EEPROM write operation interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

R = Readable bit

- n = Value at POR

| U-0   | R/W-0    | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|----------|-----|-------|-------|-----|-----|--------|

| -     | Reserved | —   | EEIF  | BCLIF | —   | —   | CCP2IF |

| bit 7 |          |     |       |       |     |     | bit 0  |

| Unimplemented: Read as '0'                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                             |

| Reserved: Always maintain this bit clear                                                                                                                                    |

| Unimplemented: Read as '0'                                                                                                                                                  |

| EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                             |

| <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                   |

| BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                     |

| <ul> <li>1 = A bus collision has occurred in the SSP, when configured for I2C Master mode</li> <li>0 = No bus collision has occurred</li> </ul>                             |

| Unimplemented: Read as '0'                                                                                                                                                  |

| CCP2IF: CCP2 Interrupt Flag bit                                                                                                                                             |

| Capture mode:                                                                                                                                                               |

| <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> <li><u>Compare mode:</u></li> </ul>         |

| <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> <li><u>PWM mode:</u></li> </ul> |

| Unused<br>Leaend:                                                                                                                                                           |

|                                                                                                                                                                             |

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

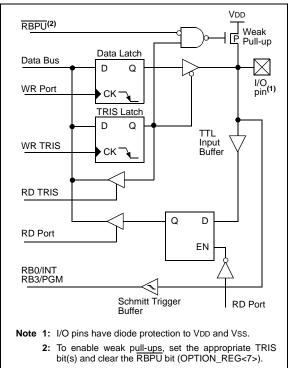

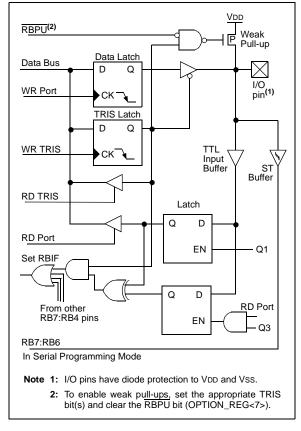

# 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the Low Voltage Programming function: RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in the Special Features Section.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins, RB7:RB4, have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, *"Implementing Wake-up on Key Strokes"* (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.10.1.

#### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

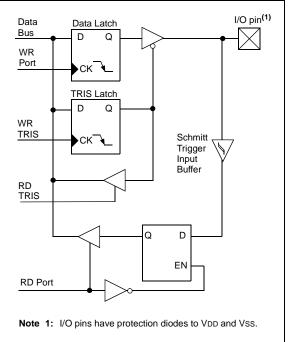

# 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

#### FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                              |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| REU/RD/ANS | bito | 51/112 /              | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

## TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE [ | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

NOTES:

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

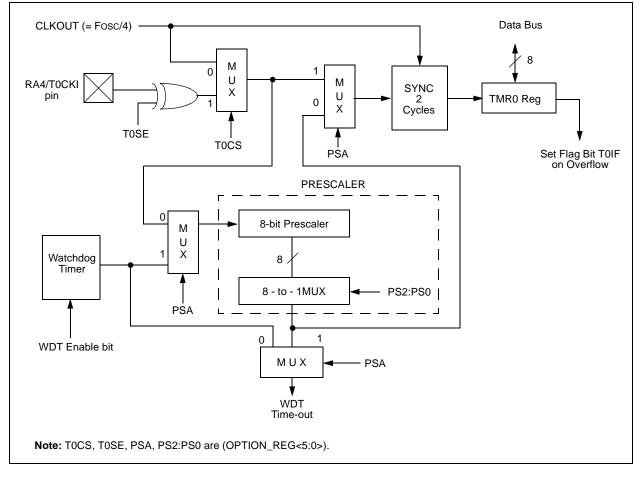

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

# 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# PIC16F87X

NOTES:

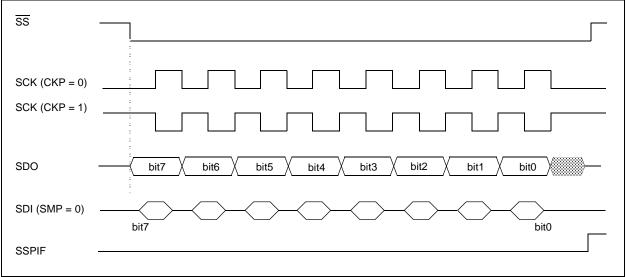

## 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

# FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

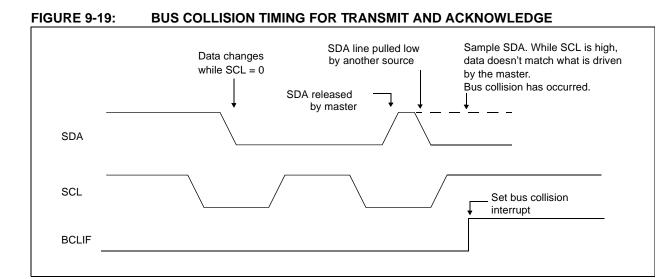

#### 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$ port to its IDLE state (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

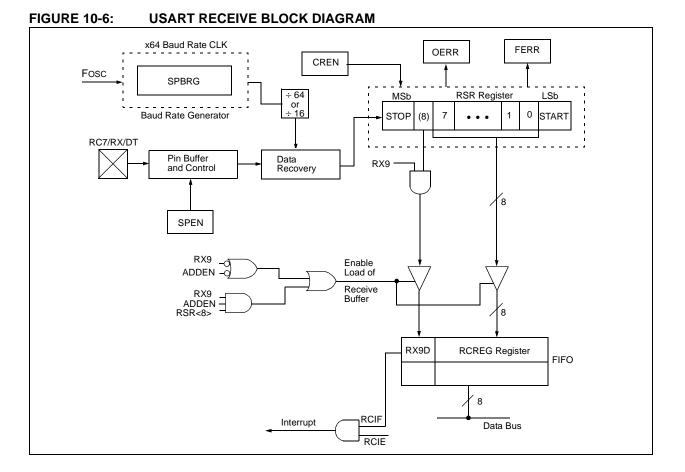

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

# 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHA           | RACTE | RISTICS                                 | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC specification(Section 15.1) |      |         |       |                                                             |  |  |  |

|------------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|-------------------------------------------------------------|--|--|--|

| Param<br>No. Sym |       | Characteristic                          | Min                                                                                                                                                                                                                                                              | Тур† | Max     | Units | Conditions                                                  |  |  |  |

|                  | VIL   | Input Low Voltage                       |                                                                                                                                                                                                                                                                  |      |         |       |                                                             |  |  |  |

|                  |       | I/O ports                               |                                                                                                                                                                                                                                                                  |      |         |       |                                                             |  |  |  |

| D030             |       | with TTL buffer                         | Vss                                                                                                                                                                                                                                                              | —    | 0.15Vdd | V     | For entire VDD range                                        |  |  |  |

| D030A            |       |                                         | Vss                                                                                                                                                                                                                                                              | —    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                     |  |  |  |

| D031             |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                              | —    | 0.2Vdd  | V     |                                                             |  |  |  |

| D032             |       | MCLR, OSC1 (in RC mode)                 | Vss                                                                                                                                                                                                                                                              | —    | 0.2Vdd  | V     |                                                             |  |  |  |

| D033             |       | OSC1 (in XT, HS and LP)                 | Vss                                                                                                                                                                                                                                                              | —    | 0.3Vdd  | V     | (Note 1)                                                    |  |  |  |

|                  |       | Ports RC3 and RC4                       |                                                                                                                                                                                                                                                                  | —    |         |       |                                                             |  |  |  |

| D034             |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                              | —    | 0.3Vdd  | V     | For entire VDD range                                        |  |  |  |

| D034A            |       | with SMBus                              | -0.5                                                                                                                                                                                                                                                             | —    | 0.6     | V     | for VDD = $4.5$ to $5.5$ V                                  |  |  |  |

|                  | Vih   | Input High Voltage                      |                                                                                                                                                                                                                                                                  |      | r       |       | 1                                                           |  |  |  |

|                  |       | I/O ports                               |                                                                                                                                                                                                                                                                  | —    |         |       |                                                             |  |  |  |

| D040             |       | with TTL buffer                         | 2.0                                                                                                                                                                                                                                                              | —    | Vdd     | -     | $4.5V \leq VDD \leq 5.5V$                                   |  |  |  |

| D040A            |       |                                         | 0.25VDD<br>+ 0.8V                                                                                                                                                                                                                                                | _    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D041             |       | with Schmitt Trigger buffer             | 0.8Vdd                                                                                                                                                                                                                                                           | —    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D042             |       | MCLR                                    | 0.8Vdd                                                                                                                                                                                                                                                           | —    | Vdd     | V     |                                                             |  |  |  |

| D042A            |       | OSC1 (XT, HS and LP)                    | 0.7Vdd                                                                                                                                                                                                                                                           | —    | Vdd     | V     | (Note 1)                                                    |  |  |  |

| D043             |       | OSC1 (in RC mode)<br>Ports RC3 and RC4  | 0.9Vdd                                                                                                                                                                                                                                                           | —    | Vdd     | V     |                                                             |  |  |  |

| D044             |       | with Schmitt Trigger buffer             | 0.7Vdd                                                                                                                                                                                                                                                           | —    | Vdd     | V     | For entire VDD range                                        |  |  |  |

| D044A            |       | with SMBus                              | 1.4                                                                                                                                                                                                                                                              | —    | 5.5     | V     | for VDD = $4.5$ to $5.5$ V                                  |  |  |  |

| D070             | IPURB | PORTB Weak Pull-up Current              | 50                                                                                                                                                                                                                                                               | 250  | 400     | μA    | VDD = 5V, VPIN = VSS,<br>-40°C TO +85°C                     |  |  |  |

|                  | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                                                                                                  |      |         |       |                                                             |  |  |  |

| D060             |       | I/O ports                               | —                                                                                                                                                                                                                                                                | —    | ±1      | μΑ    | $Vss \le VPIN \le VDD,$<br>Pin at hi-impedance              |  |  |  |

| D061             |       | MCLR, RA4/T0CKI                         | _                                                                                                                                                                                                                                                                | _    | ±5      | uΑ    | $Vss \leq VPIN \leq VDD$                                    |  |  |  |

| D063             |       | OSC1                                    | —                                                                                                                                                                                                                                                                | _    | ±5      | •     | $Vss \le VPIN \le VDD$ , XT, HS<br>and LP osc configuration |  |  |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

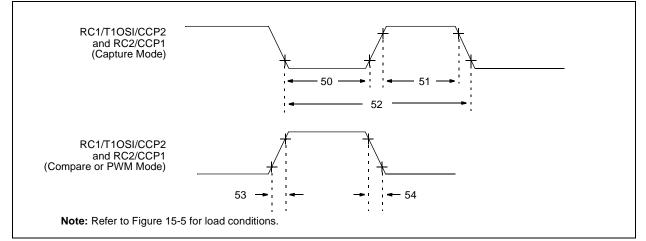

## FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

# TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym  |                  | Characteris      | stic         | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|------|------------------|------------------|--------------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | TccL | CCP1 and CCP2    | No Prescaler     | No Prescaler |                       | —    | _   | ns    |                                    |

|              |      | input low time   |                  | Standard(F)  | 10                    | _    | _   | ns    |                                    |

|              |      |                  | With Prescaler   | Extended(LF) | 20                    | _    | _   | ns    |                                    |

| 51*          | TccH | CCP1 and CCP2    | No Prescaler     |              | 0.5TCY + 20           | _    | _   | ns    |                                    |

|              |      | input high time  |                  | Standard(F)  | 10                    | —    | _   | ns    |                                    |

|              |      |                  | With Prescaler   | Extended(LF) | 20                    | —    | _   | ns    |                                    |

| 52*          | TccP | CCP1 and CCP2 in | nput period      |              | <u>3TCY + 40</u><br>N | _    | _   | ns    | N = prescale<br>value (1, 4 or 16) |

| 53*          | TccR | CCP1 and CCP2 c  | output rise time | Standard(F)  | —                     | 10   | 25  | ns    |                                    |

|              |      |                  |                  | Extended(LF) | —                     | 25   | 50  | ns    |                                    |

| 54*          | TccF | CCP1 and CCP2 c  | utput fall time  | Standard(F)  | —                     | 10   | 25  | ns    |                                    |

|              |      |                  |                  | Extended(LF) | —                     | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| TABLE 15-9: I <sup>2</sup> C BUS DATA REQUI |

|---------------------------------------------|

|---------------------------------------------|

| Param<br>No. | Sym     | Characte               | eristic      | Min        | Max  | Units | Conditions                                     |

|--------------|---------|------------------------|--------------|------------|------|-------|------------------------------------------------|

| 100          | Thigh   | Clock high time        | 100 kHz mode | 4.0        | —    | μS    | Device must operate at a minimum of 1.5 MHz    |

|              |         |                        | 400 kHz mode | 0.6        | —    | μs    | Device must operate at a<br>minimum of 10 MHz  |

|              |         |                        | SSP Module   | 0.5Tcy     |      |       |                                                |

| 101          | Tlow    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a<br>minimum of 1.5 MHz |

|              |         |                        | 400 kHz mode | 1.3        | —    | μs    | Device must operate at a minimum of 10 MHz     |

|              |         |                        | SSP Module   | 0.5TCY     |      |       |                                                |

| 102          | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                                |

|              |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF     |

| 103          | Tf      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                                |

|              |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF     |

| 90           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for Repeated                     |

|              |         | setup time             | 400 kHz mode | 0.6        |      | μs    | START condition                                |

| 91           | Thd:sta | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period, the first clock             |

|              |         | time                   | 400 kHz mode | 0.6        |      | μS    | pulse is generated                             |

| 106          | Thd:dat | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                |

|              |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                |

| 107          | Tsu:dat | Data input setup time  | 100 kHz mode | 250        | —    | ns    | (Note 2)                                       |

|              |         |                        | 400 kHz mode | 100        | —    | ns    |                                                |

| 92           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                |

|              |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                |

| 109          | Таа     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                       |

|              |         | clock                  | 400 kHz mode | —          | —    | ns    |                                                |

| 110          | Tbuf    | Bus free time          | 100 kHz mode | 4.7        | —    | μS    | Time the bus must be free                      |

|              |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission<br>can start         |

|              | Cb      | Bus capacitive loading |              | —          | 400  | pF    |                                                |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that Tsu:dat ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ Tsu:dat = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

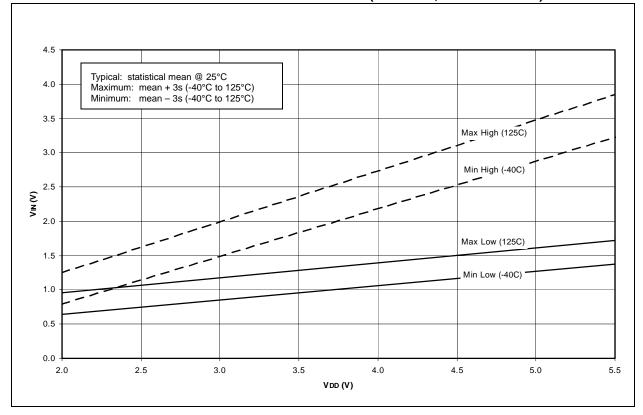

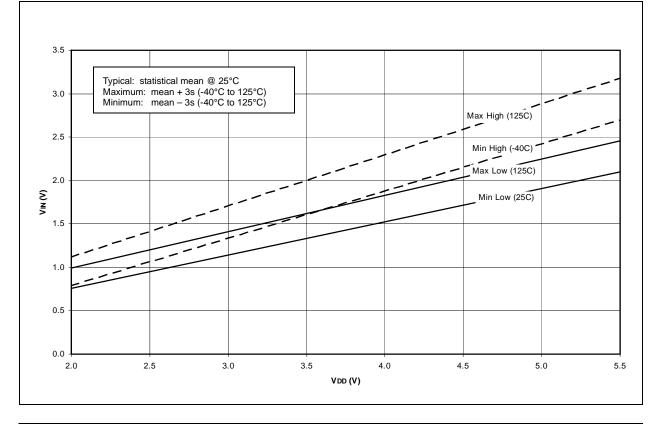

FIGURE 16-21: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO 125°C)

© 1998-2013 Microchip Technology Inc.

# 17.0 PACKAGING INFORMATION

# 17.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

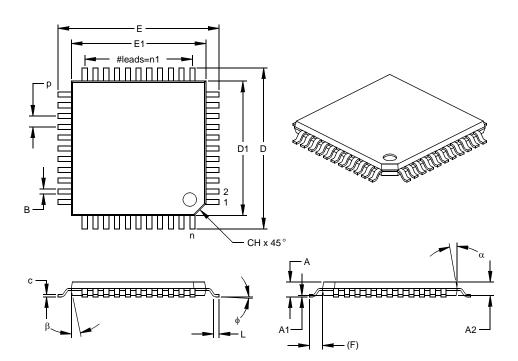

# 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |      |      |      | MILLIMETERS* |       |       |  |

|--------------------------|-------|------|------|------|--------------|-------|-------|--|

| Dimension                | MIN   | NOM  | MAX  | MIN  | NOM          | MAX   |       |  |

| Number of Pins           | n     |      | 44   |      |              | 44    |       |  |

| Pitch                    | р     |      | .031 |      |              | 0.80  |       |  |

| Pins per Side            | n1    |      | 11   |      |              | 11    |       |  |

| Overall Height           | А     | .039 | .043 | .047 | 1.00         | 1.10  | 1.20  |  |

| Molded Package Thickness | A2    | .037 | .039 | .041 | 0.95         | 1.00  | 1.05  |  |

| Standoff §               | A1    | .002 | .004 | .006 | 0.05         | 0.10  | 0.15  |  |

| Foot Length              | L     | .018 | .024 | .030 | 0.45         | 0.60  | 0.75  |  |

| Footprint (Reference)    | (F)   |      | .039 |      | 1.00         |       |       |  |

| Foot Angle               | φ     | 0    | 3.5  | 7    | 0            | 3.5   | 7     |  |

| Overall Width            | Е     | .463 | .472 | .482 | 11.75        | 12.00 | 12.25 |  |

| Overall Length           | D     | .463 | .472 | .482 | 11.75        | 12.00 | 12.25 |  |

| Molded Package Width     | E1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Molded Package Length    | D1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Lead Thickness           | С     | .004 | .006 | .008 | 0.09         | 0.15  | 0.20  |  |

| Lead Width               | В     | .012 | .015 | .017 | 0.30         | 0.38  | 0.44  |  |

| Pin 1 Corner Chamfer     | СН    | .025 | .035 | .045 | 0.64         | 0.89  | 1.14  |  |

| Mold Draft Angle Top     | α     | 5    | 10   | 15   | 5            | 10    | 15    |  |

| Mold Draft Angle Bottom  | β     | 5    | 10   | 15   | 5            | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-026 Drawing No. C04-076

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events