Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

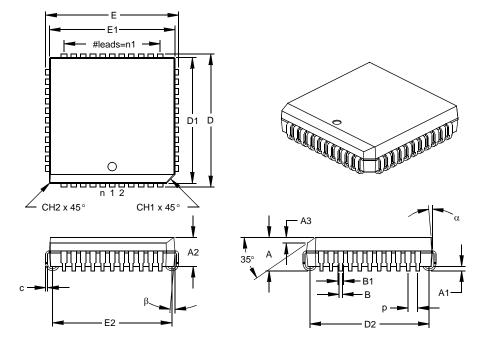

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874-04i-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address              | Name       | Bit 7                               | Bit 6                                  | Bit 5                      | Bit 4          | Bit 3        | Bit 2             | Bit 1        | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|------------|-------------------------------------|----------------------------------------|----------------------------|----------------|--------------|-------------------|--------------|----------|--------------------------|------------------------|

| Bank 1               |            |                                     |                                        |                            |                |              |                   |              |          |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressing                          | g this locatio                         | n uses conte               | ents of FSR to | address dat  | a memory (no      | a physical r | egister) | 0000 0000                | 27                     |

| 81h                  | OPTION_REG | RBPU                                | INTEDG                                 | TOCS                       | T0SE           | PSA          | PS2               | PS1          | PS0      | 1111 1111                | 19                     |

| 82h <sup>(3)</sup>   | PCL        | Program C                           | Counter (PC)                           | Least Signif               | icant Byte     |              |                   |              |          | 0000 0000                | 26                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP                                 | RP1                                    | RP0                        | TO             | PD           | Z                 | DC           | С        | 0001 1xxx                | 18                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da                         | ata Memory A                           | Address Poir               | nter           |              |                   |              |          | xxxx xxxx                | 27                     |

| 85h                  | TRISA      | _                                   |                                        | PORTA Da                   | ta Direction R | egister      |                   |              |          | 11 1111                  | 29                     |

| 86h                  | TRISB      | PORTB Da                            | ata Direction                          | Register                   |                |              |                   |              |          | 1111 1111                | 31                     |

| 87h                  | TRISC      | PORTC D                             | ata Direction                          | Register                   |                |              |                   |              |          | 1111 1111                | 33                     |

| 88h <sup>(4)</sup>   | TRISD      | PORTD D                             | ata Direction                          | Register                   |                |              |                   |              |          | 1111 1111                | 35                     |

| 89h <sup>(4)</sup>   | TRISE      | IBF                                 | OBF                                    | IBOV                       | PSPMODE        |              | PORTE Data        | Direction Bi | its      | 0000 -111                | 37                     |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _                                   | _                                      | _                          | Write Buffer   | for the uppe | r 5 bits of the F | Program Cou  | unter    | 0 0000                   | 26                     |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                                 | PEIE                                   | TOIE                       | INTE           | RBIE         | T0IF              | INTF         | RBIF     | 0000 000x                | 20                     |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup>                | ADIE                                   | RCIE                       | TXIE           | SSPIE        | CCP1IE            | TMR2IE       | TMR1IE   | 0000 0000                | 21                     |

| 8Dh                  | PIE2       | _                                   | (5)                                    |                            | EEIE           | BCLIE        | _                 |              | CCP2IE   | -r-0 00                  | 23                     |

| 8Eh                  | PCON       | _                                   | _                                      |                            | -              |              | -                 | POR          | BOR      | dd                       | 25                     |

| 8Fh                  | —          | Unimplem                            | ented                                  |                            |                |              |                   |              |          | _                        | —                      |

| 90h                  | —          | Unimplem                            | ented                                  |                            |                |              |                   |              |          | _                        | _                      |

| 91h                  | SSPCON2    | GCEN                                | ACKSTAT                                | ACKDT                      | ACKEN          | RCEN         | PEN               | RSEN         | SEN      | 0000 0000                | 68                     |

| 92h                  | PR2        | Timer2 Pe                           | riod Register                          | r                          |                |              |                   |              |          | 1111 1111                | 55                     |

| 93h                  | SSPADD     | Synchrono                           | ous Serial Po                          | ort (I <sup>2</sup> C mode | ) Address Re   | gister       |                   |              |          | 0000 0000                | 73, 74                 |

| 94h                  | SSPSTAT    | SMP                                 | CKE                                    | D/A                        | Р              | S            | R/W               | UA           | BF       | 0000 0000                | 66                     |

| 95h                  | —          | Unimplem                            | ented                                  |                            |                |              |                   |              |          | _                        | _                      |

| 96h                  | —          | Unimplem                            | ented                                  |                            |                |              |                   |              |          | _                        | _                      |

| 97h                  | —          | Unimplem                            | ented                                  |                            |                |              |                   |              |          | _                        | _                      |

| 98h                  | TXSTA      | CSRC                                | TX9                                    | TXEN                       | SYNC           | _            | BRGH              | TRMT         | TX9D     | 0000 -010                | 95                     |

| 99h                  | SPBRG      | Baud Rate Generator Register 0000 0 |                                        |                            |                | 0000 0000    | 97                |              |          |                          |                        |

| 9Ah                  | —          | Unimplem                            | Unimplemented                          |                            |                |              | _                 | _            |          |                          |                        |

| 9Bh                  | —          | Unimplem                            | Unimplemented —                        |                            |                |              | _                 |              |          |                          |                        |

| 9Ch                  | —          | Unimplem                            | Unimplemented —                        |                            |                |              | _                 |              |          |                          |                        |

| 9Dh                  | —          | Unimplem                            | Unimplemented —                        |                            |                |              | _                 | _            |          |                          |                        |

| 9Eh                  | ADRESL     | A/D Result                          | A/D Result Register Low Byte xxxx xxxx |                            |                |              | 116               |              |          |                          |                        |

| 9Fh                  | ADCON1     | ADFM                                | _                                      | _                          | —              | PCFG3        | PCFG2             | PCFG1        | PCFG0    | 0 0000                   | 112                    |

#### **TABLE 2-1:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

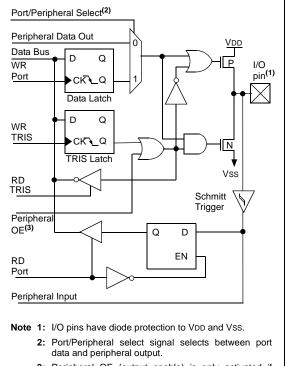

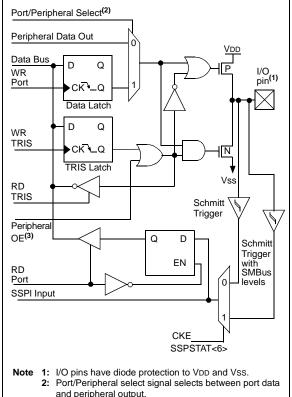

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

# FIGURE 3-6:

# PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

#### **TRISE REGISTER (ADDRESS 89h)** R/W-1 R-0 R-0 R/W-0 R/W-0 U-0 R/W-1 R/W-1 IBF OBF **IBOV PSPMODE** Bit2 Bit1 Bit0 bit 7 bit 0 Parallel Slave Port Status/Control Bits: bit 7 IBF: Input Buffer Full Status bit 1 = A word has been received and is waiting to be read by the CPU 0 = No word has been received bit 6 **OBF**: Output Buffer Full Status bit 1 = The output buffer still holds a previously written word 0 = The output buffer has been read bit 5 **IBOV**: Input Buffer Overflow Detect bit (in Microprocessor mode) 1 = A write occurred when a previously input word has not been read (must be cleared in software) 0 = No overflow occurred bit 4 PSPMODE: Parallel Slave Port Mode Select bit 1 = PORTD functions in Parallel Slave Port mode 0 = PORTD functions in general purpose I/O mode Unimplemented: Read as '0' bit 3 **PORTE Data Direction Bits:** Bit2: Direction Control bit for pin RE2/CS/AN7 bit 2 1 = Input0 = OutputBit1: Direction Control bit for pin RE1/WR/AN6 bit 1 1 = Input 0 = Output Bit0: Direction Control bit for pin RE0/RD/AN5 bit 0 1 = Input 0 = Output Legend:

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

R = Readable bit

- n = Value at POR

**REGISTER 3-1:**

NOTES:

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the other devices.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, VSS, RA2, or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

# REGISTER 11-1: ADCON0 REGISTER (ADDRESS: 1Fh)

|         | R/W-0                                                                                                                                                                                                                                                                                                                              | R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0   | U-0 | R/W-0 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------------------|-------|---------|-----|-------|

|         | ADCS1                                                                                                                                                                                                                                                                                                                              | ADCS0        | CHS2  | CHS1             | CHS0  | GO/DONE | _   | ADON  |

|         | bit 7                                                                                                                                                                                                                                                                                                                              |              |       |                  |       |         |     | bit 0 |

|         |                                                                                                                                                                                                                                                                                                                                    |              |       |                  |       |         |     |       |

| bit 7-6 | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from the internal A/D module RC oscillator)                                                                                                                                                                 |              |       |                  |       |         |     |       |

| bit 5-3 | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)<br>101 = channel 5, (RE0/AN5) <sup>(1)</sup><br>110 = channel 6, (RE1/AN6) <sup>(1)</sup><br>111 = channel 7, (RE2/AN7) <sup>(1)</sup> |              |       |                  |       |         |     |       |

| bit 2   | <ul> <li>GO/DONE: A/D Conversion Status bit</li> <li><u>If ADON = 1:</u></li> <li>1 = A/D conversion in progress (setting this bit starts the A/D conversion)</li> <li>0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)</li> </ul>                           |              |       |                  |       | he A/D  |     |       |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                         |              |       |                  |       |         |     |       |

| bit 0   |                                                                                                                                                                                                                                                                                                                                    | verter modul | •     | g<br>and consume |       |         |     |       |

|         |                                                                                                                                                                                                                                                                                                                                    |              |       | vailable on PIC  | ·     | 0       |     |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock                | AD Clock Source (TAD) |          |

|-------------------------|-----------------------|----------|

| Operation               | ADCS1:ADCS0           | Max.     |

| 2Tosc                   | 0 0                   | 1.25 MHz |

| 8Tosc                   | 01                    | 5 MHz    |

| 32Tosc                  | 10                    | 20 MHz   |

| RC <sup>(1, 2, 3)</sup> | 11                    | (Note 1) |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s, but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 15.1 and 15.2).

# 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

| Note | 1: When reading the port register, any pin   |

|------|----------------------------------------------|

|      | configured as an analog input channel will   |

|      | read as cleared (a low level). Pins config-  |

|      | ured as digital inputs will convert an ana-  |

|      | log input. Analog levels on a digitally      |

|      | configured input will not affect the conver- |

|      | sion accuracy.                               |

2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

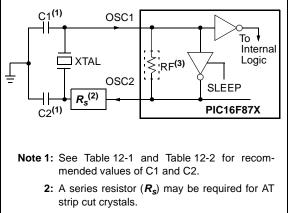

#### 12.2 **Oscillator Configurations**

#### 12.2.1 **OSCILLATOR TYPES**

The PIC16F87X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- Crystal/Resonator • XT

- High Speed Crystal/Resonator HS

- RC Resistor/Capacitor

#### 12.2.2 **CRYSTAL OSCILLATOR/CERAMIC** RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F87X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 12-2).

#### **FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION** (HS, XT OR LP **OSC CONFIGURATION)**

3: RF varies with the crystal chosen.

# **EXTERNAL CLOCK INPUT OPERATION (HS, XT OR** LP OSC **CONFIGURATION**) OSC1 Clock from Ext. System PIC16F87X OSC2 Open

# TABLE 12-1: CERAMIC RESONATORS

| Ranges Tested: |          |             |             |  |

|----------------|----------|-------------|-------------|--|

| Mode           | Freq.    | OSC1        | OSC2        |  |

| ХТ             | 455 kHz  | 68 - 100 pF | 68 - 100 pF |  |

|                | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |

|                | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |

| HS             | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |  |

|                | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |  |

These values are for design guidance only. See notes following Table 12-2.

#### **Resonators Used:**

| 455 kHz                                               | Panasonic EFO-A455K04B | $\pm 0.3\%$ |  |

|-------------------------------------------------------|------------------------|-------------|--|

| 2.0 MHz                                               | Murata Erie CSA2.00MG  | $\pm 0.5\%$ |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG  | $\pm 0.5\%$ |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT  | $\pm 0.5\%$ |  |

| 16.0 MHz                                              | Murata Erie CSA16.00MX | $\pm 0.5\%$ |  |

| All resonators used did not have built-in capacitors. |                        |             |  |

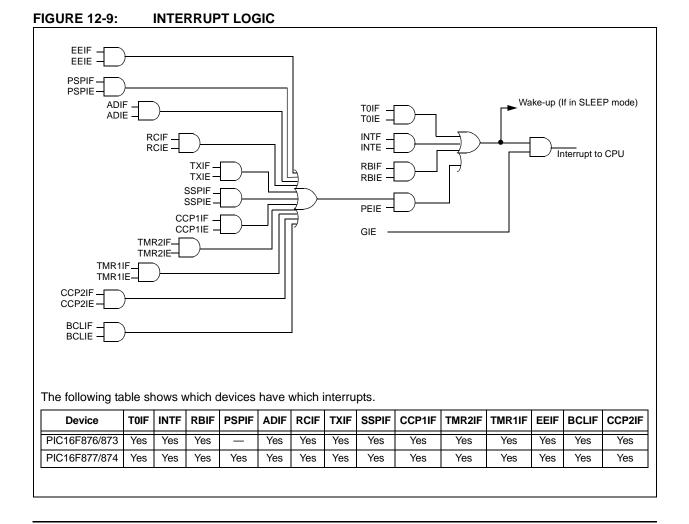

# 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

<sup>© 1998-2013</sup> Microchip Technology Inc.

# PIC16F87X

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| COMF             | Complement f                                                                                                                                            |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                         |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |

|                  |                                                                                                                                                                                                               |  |  |  |  |  |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \rightarrow (W)$                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                       |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:             | [ label ] SUBWF f,d                                                                                                                                                                     |  |  |  |

| Operands:           | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                      |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHA       | RACTE | RISTICS                                 | Operating         | i temp | erature | -40°C<br>0°C | The second seco |

|--------------|-------|-----------------------------------------|-------------------|--------|---------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                          | Min               | Тур†   | Max     | Units        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | VIL   | Input Low Voltage                       |                   |        |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              |       | I/O ports                               |                   |        |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D030         |       | with TTL buffer                         | Vss               | —      | 0.15Vdd | V            | For entire VDD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D030A        |       |                                         | Vss               | —      | 0.8V    | V            | $4.5V \le VDD \le 5.5V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D031         |       | with Schmitt Trigger buffer             | Vss               | —      | 0.2Vdd  | V            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D032         |       | MCLR, OSC1 (in RC mode)                 | Vss               | —      | 0.2Vdd  | V            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D033         |       | OSC1 (in XT, HS and LP)                 | Vss               | —      | 0.3Vdd  | V            | (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              |       | Ports RC3 and RC4                       |                   | —      |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D034         |       | with Schmitt Trigger buffer             | Vss               | —      | 0.3Vdd  | V            | For entire VDD range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D034A        |       | with SMBus                              | -0.5              | —      | 0.6     | V            | for VDD = $4.5$ to $5.5$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | Vih   | Input High Voltage                      |                   |        | r       |              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |       | I/O ports                               |                   | —      |         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |