#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 × 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin# | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|----------------|-------------------|-------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13             | 14                | 30          | I                    | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14             | 15                | 31          | 0                    | —                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1              | 2                 | 18          | I/P                  | ST                     | Master Clear (Reset) input or programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                        |

|                   |                |                   |             |                      |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2              | 3                 | 19          | I/O                  | TTL                    | RA0 can also be analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 3              | 4                 | 20          | I/O                  | TTL                    | RA1 can also be analog input1.                                                                                                                                                                                    |

| RA2/AN2/VREF-     | 4              | 5                 | 21          | I/O                  | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                               |

| RA3/AN3/VREF+     | 5              | 6                 | 22          | I/O                  | TTL                    | RA3 can also be analog input3 or positive<br>analog reference voltage.                                                                                                                                            |

| RA4/T0CKI         | 6              | 7                 | 23          | I/O                  | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                          |

| RA5/SS/AN4        | 7              | 8                 | 24          | I/O                  | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                                |

|                   |                |                   |             |                      |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33             | 36                | 8           | I/O                  | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1               | 34             | 37                | 9           | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB2               | 35             | 38                | 10          | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB3/PGM           | 36             | 39                | 11          | I/O                  | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                                |

| RB4               | 37             | 41                | 14          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB5               | 38             | 42                | 15          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB6/PGC           | 39             | 43                | 16          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                                  |

| RB7/PGD           | 40             | 44                | 17          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                                   |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |             | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | and digit borrow bit, respectively, in sub- |  |  |  |  |  |  |  |  |  |  |

|       | traction. See the SUBLW and SUBWF           |  |  |  |  |  |  |  |  |  |  |

|       | instructions for examples.                  |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                                                | R/W-0            | R-1           | R-1                          | R/W-x | R/W-x | R/W-x |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------|---------------|------------------------------|-------|-------|-------|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                      | RP1                                                                                  | RP0              | TO            | PD                           | Z     | DC    | С     |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                    |                                                                                      |                  |               |                              |       |       | bit 0 |  |  |  |  |

|         |                                                                                                                                                                                                                                                          |                                                                                      |                  |               | <i>.</i>                     |       |       |       |  |  |  |  |

| bit 7   | IRP: Register Bank Select bit (used for indirect addressing)                                                                                                                                                                                             |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | 1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                                                                 |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

| bit 6-5 | RP1:RP0                                                                                                                                                                                                                                                  | : Register Ba                                                                        | nk Select bi     | its (used for | direct addressi              | ng)   |       |       |  |  |  |  |

|         | 10 = Ban<br>01 = Ban<br>00 = Ban                                                                                                                                                                                                                         | k 3 (180h - 1 <br>k 2 (100h - 1]<br>k 1 (80h - FF<br>k 0 (00h - 7F <br>k is 128 byte | 7Fh)<br>h)<br>h) |               |                              |       |       |       |  |  |  |  |

| bit 4   | <b>TO</b> : Time                                                                                                                                                                                                                                         | -out bit                                                                             |                  |               |                              |       |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | power-up, CL<br>T time-out o                                                         |                  | iction, or SI | EEP instruction              |       |       |       |  |  |  |  |

| bit 3   | PD: Powe                                                                                                                                                                                                                                                 | er-down bit                                                                          |                  |               |                              |       |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | power-up or l<br>ecution of the                                                      |                  |               | on                           |       |       |       |  |  |  |  |

| bit 2   | Z: Zero bi                                                                                                                                                                                                                                               | it                                                                                   |                  |               |                              |       |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | esult of an ar<br>esult of an ar                                                     |                  |               | on is zero<br>on is not zero |       |       |       |  |  |  |  |

| bit 1   | DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                                                                                                     |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | (for borrow, the polarity is reversed)                                                                                                                                                                                                                   |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>                                                                                                 |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                                                                                                            |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                  |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high, or low order bit of the source register. |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                  |                                                                                      |                  |               |                              |       |       |       |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

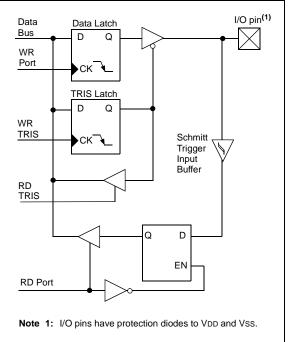

# 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | Bank0                 |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0x06    |     | ; | Configure all pins    |

| MOVWF | ADCON1  |     | ; | as digital inputs     |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6>are always  |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

|       |         |     |   |                       |

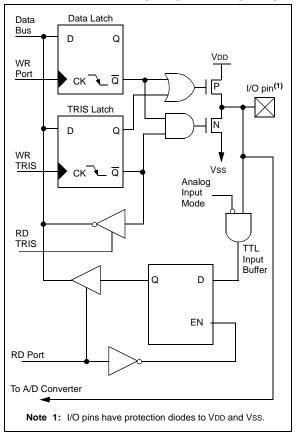

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

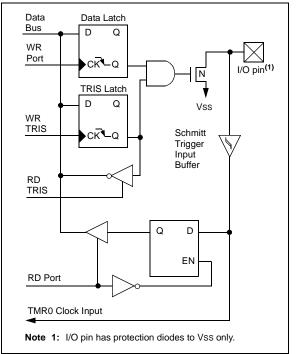

# FIGURE 3-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

| Name         | Bit# | Buffer | Function                                                                        |  |  |  |  |

|--------------|------|--------|---------------------------------------------------------------------------------|--|--|--|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |  |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |  |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |  |  |  |  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |  |  |  |  |

#### TABLE 3-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|--------|------------|---------|---------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     |       | RA5   | RA4    | RA3        | RA2     | RA1     | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | _     | _     | PORTA | Data D | irection F | 11 1111 | 11 1111 |       |                          |                                 |

| 9Fh     | ADCON1 | ADFM  |       | _     |        | PCFG3      | PCFG2   | PCFG1   | PCFG0 | 0- 0000                  | 0-0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.

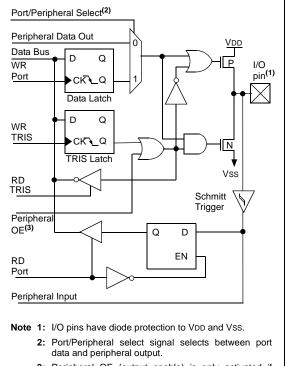

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

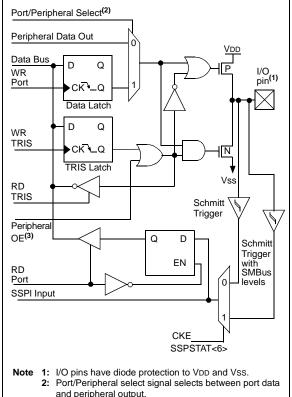

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

# FIGURE 3-6:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

## 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

#### FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                              |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| RE0/RD/ANS | DILU | 51/11L <sup>4</sup> / | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                     | Bit 1 | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------------------------|-------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2                       | RE1   | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE Data Direction Bits |       | 0000 -111 | 0000 -111             |                                 |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2                     | PCFG1 | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

# PIC16F87X

NOTES:

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

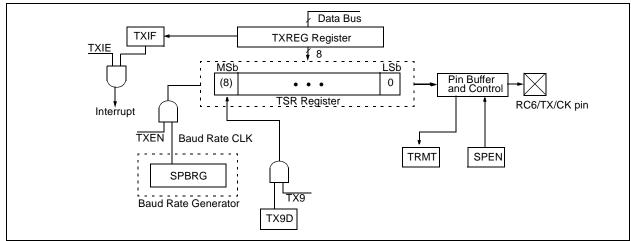

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

# PIC16F87X

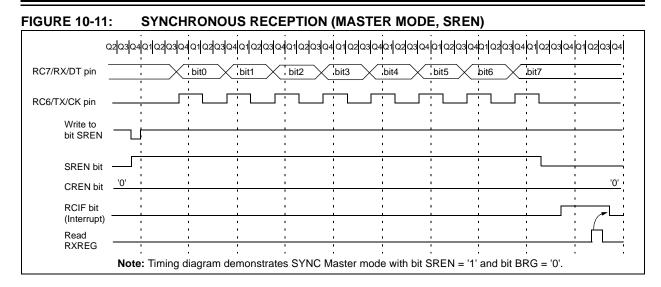

# 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                | Name                               | Bit 7                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other<br>RESETS |

|------------------------|------------------------------------|----------------------|-------|-------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                             | GIE                  | PEIE  | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                               | PSPIF <sup>(1)</sup> | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA                              | SPEN                 | RX9   | SREN  | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | x000 0000                       |

| 19h                    | 19h TXREG USART Transmit Register  |                      |       |       |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                               | PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA                              | CSRC                 | TX9   | TXEN  | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register |                      |       |       |       |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

#### 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present. When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

f,b

#### **Instruction Descriptions** 13.1

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |  |  |  |

|                  | and the result is placed in the W register. |       |  |  |  |  |  |  |

|------------------|---------------------------------------------|-------|--|--|--|--|--|--|

| ADDWF            | Add W and f                                 | BSF   |  |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] ADDWF f,d                  | Synt  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$          | Ope   |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)       | Ope   |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                    | State |  |  |  |  |  |  |

| Description:     | Add the contents of the W register          | Des   |  |  |  |  |  |  |

with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in

| Status Affected: | None                                |

|------------------|-------------------------------------|

| Description:     | Bit 'b' in register 'f' is cleared. |

|                  |                                     |

|                  |                                     |

| BSF              | Bit Set f                           |

| Syntax:          | [ <i>label</i> ] BSF f,b            |

|                  | 0 (1 (107                           |

Bit Clear f

[*label*] BCF

$0 \leq f \leq 127$  $0 \le b \le 7$

$0 \rightarrow (f < b >)$

BCF

Syntax:

Operands:

Operation:

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

|------------------|---------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |  |  |

register 'f'.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TCY instruction. |  |  |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |  |  |  |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |  |  |  |  |  |  |  |

# 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |      |                                                                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                               |  |  |  |

|----------------------------------------------------------------------------------|------|------------------------------------------------------------------|------|------------------------------------------------------|------|-------|-----------------------------------------------|--|--|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |      |                                                                  |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                               |  |  |  |

| ParamSymbolCharacteristic/No.Device                                              |      |                                                                  | Min  | Тур†                                                 | Мах  | Units | Conditions                                    |  |  |  |

|                                                                                  | Vdd  | Supply Voltage                                                   |      |                                                      |      |       |                                               |  |  |  |

| D001                                                                             |      | 16LF87X                                                          | 2.0  |                                                      | 5.5  | V     | LP, XT, RC osc configuration<br>(DC to 4 MHz) |  |  |  |

| D001                                                                             |      | 16F87X                                                           | 4.0  | _                                                    | 5.5  | V     | LP, XT, RC osc configuration                  |  |  |  |

| D001A                                                                            |      |                                                                  | 4.5  |                                                      | 5.5  | V     | HS osc configuration                          |  |  |  |

|                                                                                  |      |                                                                  | VBOR |                                                      | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>     |  |  |  |

| D002                                                                             | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —    | 1.5                                                  |      | V     |                                               |  |  |  |

| D003                                                                             | Vpor | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —    | Vss                                                  | _    | V     | See section on Power-on Reset for details     |  |  |  |

| D004                                                                             | Svdd | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05 | —                                                    | —    | V/ms  | See section on Power-on Reset for details     |  |  |  |

| D005                                                                             | VBOR | Brown-out Reset<br>Voltage                                       | 3.7  | 4.0                                                  | 4.35 | V     | BODEN bit in configuration word<br>enabled    |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

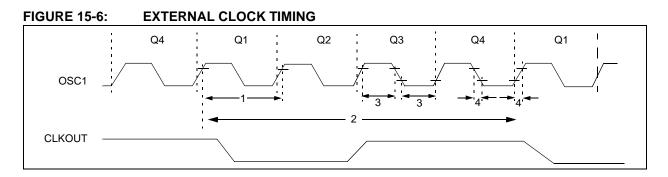

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                     | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|------------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency           | DC  |      | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                           | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                    | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | DC  | —    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency               | DC  |      | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                           | 0.1 | —    | 4      | MHz   | XT osc mode        |

|                  |       |                                    | 4   | —    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | 4   | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | 5   |      | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period              | 250 |      | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                           | 250 | _    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | —      | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μS    | LP osc mode        |

|                  |       | Oscillator Period                  | 250 | _    | —      | ns    | RC osc mode        |

|                  |       | (Note 1)                           | 250 | —    | 10,000 | ns    | XT osc mode        |

|                  |       |                                    | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time<br>(Note 1) | 200 | TCY  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or   | 100 |      | —      | ns    | XT oscillator      |

|                  | TosH  | Low Time                           | 2.5 | —    | —      | μS    | LP oscillator      |

|                  |       |                                    | 15  | —    | —      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or   |     |      | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                          | —   | —    | 50     | ns    | LP oscillator      |

|                  |       |                                    | —   | —    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

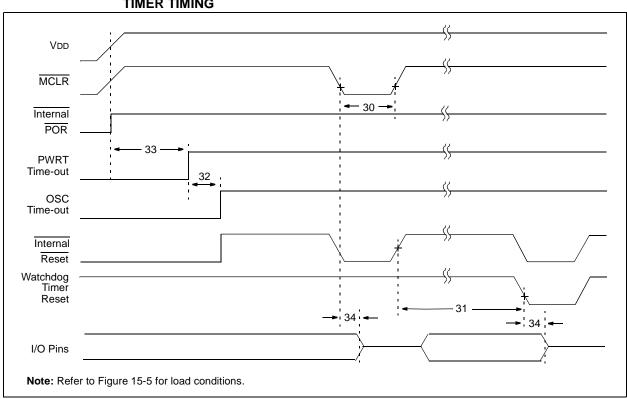

# FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

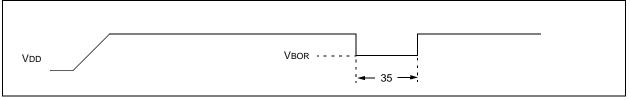

## FIGURE 15-9: BROWN-OUT RESET TIMING

# TABLE 15-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|------------------|--------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30               | TmcL   | MCLR Pulse Width (low)                                 | 2   | -         | _   | μs    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt   | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost   | Oscillation Start-up Timer Period                      | _   | 1024 Tosc |     | —     | Tosc = OSC1 period       |

| 33*              | Tpwrt  | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | —         | 2.1 | μS    |                          |

| 35               | TBOR   | Brown-out Reset pulse width                            | 100 | _         | _   | μs    | $VDD \le VBOR (D005)$    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

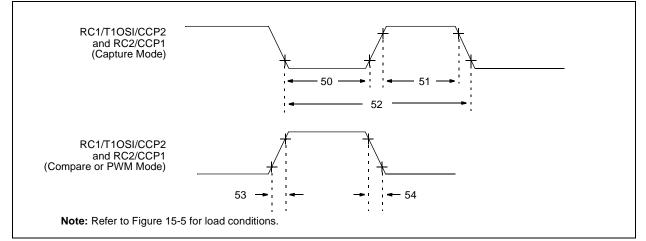

#### FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

## TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym                             |                                | Min              | Тур†         | Max                   | Units | Conditions |    |                                    |

|--------------|---------------------------------|--------------------------------|------------------|--------------|-----------------------|-------|------------|----|------------------------------------|

| 50*          | TccL                            | CCP1 and CCP2 No Prescaler     |                  |              | 0.5Tcy + 20           | —     | _          | ns |                                    |

|              |                                 | input low time                 | With Droppolor   | Standard(F)  | 10                    | _     | _          | ns |                                    |

|              |                                 |                                |                  | Extended(LF) | 20                    | _     | _          | ns |                                    |

| 51*          | TccH CCP1 and CCP2 No Prescaler |                                | No Prescaler     |              | 0.5Tcy + 20           | _     | _          | ns |                                    |

|              |                                 | input high time                |                  | Standard(F)  | 10                    | —     | _          | ns |                                    |

|              |                                 |                                | With Prescaler   | Extended(LF) | 20                    | —     | _          | ns |                                    |

| 52*          | TccP                            | CCP1 and CCP2 input period     |                  |              | <u>3TCY + 40</u><br>N | _     | _          | ns | N = prescale<br>value (1, 4 or 16) |

| 53*          | TccR                            | CCP1 and CCP2 c                | output rise time | Standard(F)  | —                     | 10    | 25         | ns |                                    |

|              |                                 |                                |                  | Extended(LF) | —                     | 25    | 50         | ns |                                    |

| 54*          | TccF                            | CCP1 and CCP2 output fall time |                  | Standard(F)  | —                     | 10    | 25         | ns |                                    |

|              |                                 |                                |                  | Extended(LF) | —                     | 25    | 45         | ns |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| TABLE 15-9: I <sup>2</sup> C BUS DATA REQU | IREMENTS |

|--------------------------------------------|----------|

|--------------------------------------------|----------|

| Param<br>No. Sym |         | Characte                   | Min          | Max        | Units | Conditions |                                                |

|------------------|---------|----------------------------|--------------|------------|-------|------------|------------------------------------------------|

| 100              | Thigh   | Clock high time            | 100 kHz mode | 4.0        | —     | μS         | Device must operate at a minimum of 1.5 MHz    |

|                  |         |                            | 400 kHz mode | 0.6        | —     | μs         | Device must operate at a<br>minimum of 10 MHz  |

|                  |         |                            | SSP Module   | 0.5Tcy     |       |            |                                                |

| 101              | Tlow    | Clock low time             | 100 kHz mode | 4.7        | —     | μs         | Device must operate at a<br>minimum of 1.5 MHz |

|                  |         |                            | 400 kHz mode | 1.3        | —     | μs         | Device must operate at a minimum of 10 MHz     |

|                  |         |                            | SSP Module   | 0.5TCY     |       |            |                                                |

| 102              | Tr      | SDA and SCL rise           | 100 kHz mode | —          | 1000  | ns         |                                                |

|                  |         | time                       | 400 kHz mode | 20 + 0.1Cb | 300   | ns         | Cb is specified to be from<br>10 to 400 pF     |

| 103              | Tf      | SDA and SCL fall time      | 100 kHz mode | —          | 300   | ns         |                                                |

|                  |         |                            | 400 kHz mode | 20 + 0.1Cb | 300   | ns         | Cb is specified to be from<br>10 to 400 pF     |

| 90               | Tsu:sta | START condition            | 100 kHz mode | 4.7        | —     | μs         | Only relevant for Repeated                     |

|                  |         | setup time                 | 400 kHz mode | 0.6        |       | μs         | START condition                                |

| 91               | Thd:sta | START condition hold       | 100 kHz mode | 4.0        | —     | μs         | After this period, the first clock             |

|                  |         | time                       | 400 kHz mode | 0.6        |       | μS         | pulse is generated                             |

| 106              | Thd:dat | d:dat Data input hold time | 100 kHz mode | 0          | —     | ns         |                                                |

|                  |         |                            | 400 kHz mode | 0          | 0.9   | μs         |                                                |

| 107              | Tsu:dat | Data input setup time      | 100 kHz mode | 250        | —     | ns         | (Note 2)                                       |

|                  |         |                            | 400 kHz mode | 100        | —     | ns         |                                                |

| 92               | Tsu:sto | STOP condition setup       | 100 kHz mode | 4.7        | —     | μs         |                                                |

|                  |         | time                       | 400 kHz mode | 0.6        | —     | μs         |                                                |

| 109              | Таа     | Output valid from          | 100 kHz mode | —          | 3500  | ns         | (Note 1)                                       |

|                  |         | clock                      | 400 kHz mode | —          | —     | ns         |                                                |

| 110              | Tbuf    | Bus free time              | 100 kHz mode | 4.7        | —     | μS         | Time the bus must be free                      |

|                  |         |                            | 400 kHz mode | 1.3        | —     | μs         | before a new transmission<br>can start         |

|                  | Cb      | Bus capacitive loading     |              | —          | 400   | pF         |                                                |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that Tsu:dat ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ Tsu:dat = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

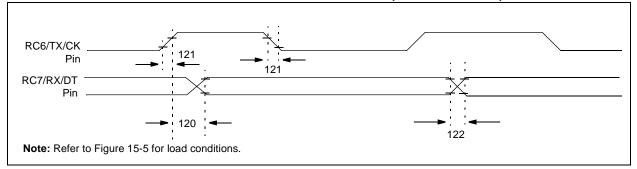

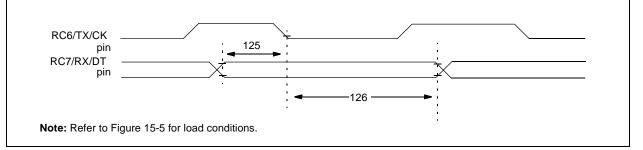

#### FIGURE 15-19: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 15-10: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                      |   | Тур† | Max | Units | Conditions |

|--------------|----------|-----------------------------------|----------------------|---|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)     | Standard( <b>F</b> ) | _ | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | Extended(LF)         | _ | -    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall time | Standard(F)          | _ | _    | 45  | ns    |            |

|              |          | (Master mode)                     | Extended(LF)         | _ | —    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall time  | Standard(F)          | — | —    | 45  | ns    |            |

|              |          |                                   | Extended(LF)         | _ |      | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 15-20: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 15-11: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                    | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup<br>time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                    | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 15-12:PIC16F87X-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)PIC16F87X-10 (EXTENDED)PIC16F87X-20 (COMMERCIAL, INDUSTRIAL)PIC16LF87X-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym   | Characteristic                              |          | Min         | Тур†       | Мах          | Units | Conditions                                                                                                  |

|--------------|-------|---------------------------------------------|----------|-------------|------------|--------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                                  |          | _           | _          | 10-bits      | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |