#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874-04i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

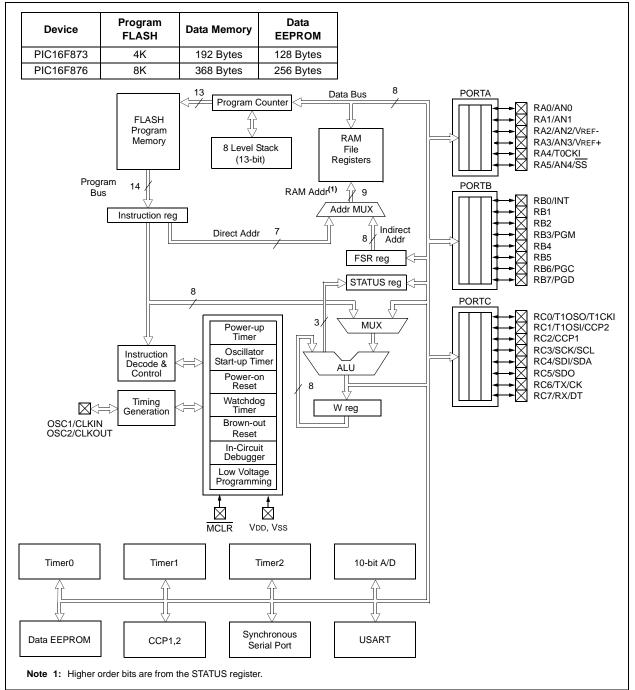

### 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2             | Bit 1          | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|----------------------|----------------|---------------|----------------|----------------|-------------------|----------------|----------|--------------------------|------------------------|

| Bank 0               |         |                      |                |               |                |                |                   |                |          |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio | n uses conte  | ents of FSR to | address dat    | a memory (no      | t a physical r | egister) | 0000 0000                | 27                     |

| 01h                  | TMR0    | Timer0 Mc            | dule Registe   | er            |                |                |                   |                |          | xxxx xxxx                | 47                     |

| 02h <sup>(3)</sup>   | PCL     | Program C            | Counter (PC)   | Least Signif  | icant Byte     |                |                   |                |          | 0000 0000                | 26                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1            | RP0           | TO             | PD             | Z                 | DC             | С        | 0001 1xxx                | 18                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ata Memory /   | Address Poir  | nter           |                |                   |                |          | xxxx xxxx                | 27                     |

| 05h                  | PORTA   | _                    | _              | PORTA Da      | ta Latch whe   | n written: POI | RTA pins whe      | n read         |          | 0x 0000                  | 29                     |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh   | en written: P | ORTB pins w    | /hen read      |                   |                |          | xxxx xxxx                | 31                     |

| 07h                  | PORTC   | PORTC D              | ata Latch wh   | en written: F | ORTC pins v    | vhen read      |                   |                |          | xxxx xxxx                | 33                     |

| 08h <sup>(4)</sup>   | PORTD   | PORTD D              | ata Latch wh   | en written: F | ORTD pins v    | vhen read      |                   |                |          | xxxx xxxx                | 35                     |

| 09h <sup>(4)</sup>   | PORTE   | _                    | _              | _             | _              | _              | RE2               | RE1            | RE0      | xxx                      | 36                     |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    |                |               | Write Buffer   | for the upper  | r 5 bits of the I | Program Cou    | unter    | 0 0000                   | 26                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE           | T0IE          | INTE           | RBIE           | T0IF              | INTF           | RBIF     | 0000 000x                | 20                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF           | RCIF          | TXIF           | SSPIF          | CCP1IF            | TMR2IF         | TMR1IF   | 0000 0000                | 22                     |

| 0Dh                  | PIR2    | —                    | (5)            | _             | EEIF           | BCLIF          | —                 |                | CCP2IF   | -r-0 00                  | 24                     |

| 0Eh                  | TMR1L   | Holding re           | gister for the | Least Signif  | ficant Byte of | the 16-bit TM  | IR1 Register      |                |          | xxxx xxxx                | 52                     |

| 0Fh                  | TMR1H   | Holding re           | gister for the | Most Signifi  | cant Byte of t | the 16-bit TM  | R1 Register       |                |          | xxxx xxxx                | 52                     |

| 10h                  | T1CON   | _                    | _              | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC            | TMR1CS         | TMR10N   | 00 0000                  | 51                     |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe   | er            |                |                |                   |                |          | 0000 0000                | 55                     |

| 12h                  | T2CON   | _                    | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON            | T2CKPS1        | T2CKPS0  | -000 0000                | 55                     |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po  | rt Receive B  | uffer/Transm   | it Register    |                   |                |          | xxxx xxxx                | 70, 73                 |

| 14h                  | SSPCON  | WCOL                 | SSPOV          | SSPEN         | CKP            | SSPM3          | SSPM2             | SSPM1          | SSPM0    | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI     | M Register1   | (LSB)          |                |                   |                |          | XXXX XXXX                | 57                     |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI     | M Register1   | (MSB)          |                |                   |                |          | XXXX XXXX                | 57                     |

| 17h                  | CCP1CON | _                    | _              | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2            | CCP1M1         | CCP1M0   | 00 0000                  | 58                     |

| 18h                  | RCSTA   | SPEN                 | RX9            | SREN          | CREN           | ADDEN          | FERR              | OERR           | RX9D     | 0000 000x                | 96                     |

| 19h                  | TXREG   | USART Tr             | ansmit Data    | Register      |                |                |                   |                |          | 0000 0000                | 99                     |

| 1Ah                  | RCREG   | USART Re             | eceive Data I  | Register      |                |                |                   |                |          | 0000 0000                | 101                    |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI     | V Register2   | (LSB)          |                |                   |                |          | xxxx xxxx                | 57                     |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI     | M Register2   | (MSB)          |                |                   |                |          | xxxx xxxx                | 57                     |

| 1Dh                  | CCP2CON | _                    | _              | CCP2X         | CCP2Y          | CCP2M3         | CCP2M2            | CCP2M1         | CCP2M0   | 00 0000                  | 58                     |

| 1Eh                  | ADRESH  | A/D Result           | t Register Hi  | gh Byte       |                |                |                   |                |          | xxxx xxxx                | 116                    |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0          | CHS2          | CHS1           | CHS0           | GO/DONE           | _              | ADON     | 0000 00-0                | 111                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

#### 2.2.2.4 **PIE1** Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

#### PIE1 REGISTER (ADDRESS 8Ch) **REGISTER 2-4:**

|       | R/W-0                                                                                        | R/W-0                        | R/W-0          | R/W-0         | R/W-0           | R/W-0  | R/W-0  | R/W-0  |  |  |  |

|-------|----------------------------------------------------------------------------------------------|------------------------------|----------------|---------------|-----------------|--------|--------|--------|--|--|--|

|       | PSPIE <sup>(1)</sup>                                                                         | ADIE                         | RCIE           | TXIE          | SSPIE           | CCP1IE | TMR2IE | TMR1IE |  |  |  |

|       | bit 7                                                                                        |                              |                |               |                 |        |        | bit 0  |  |  |  |

|       |                                                                                              |                              |                |               |                 |        |        |        |  |  |  |

| bit 7 | PSPIE <sup>(1)</sup> : F                                                                     | Parallel Slav                | e Port Read    | d/Write Inter | rupt Enable bit |        |        |        |  |  |  |

|       |                                                                                              | s the PSP r<br>s the PSP i   |                |               |                 |        |        |        |  |  |  |

| bit 6 | ADIE: A/D                                                                                    | Converter I                  | nterrupt Ena   | able bit      |                 |        |        |        |  |  |  |

|       |                                                                                              | s the A/D co<br>es the A/D c |                |               |                 |        |        |        |  |  |  |

| bit 5 | RCIE: USA                                                                                    | RT Receive                   | e Interrupt E  | nable bit     |                 |        |        |        |  |  |  |

|       |                                                                                              | s the USAR                   |                |               |                 |        |        |        |  |  |  |

|       |                                                                                              | es the USAF                  |                |               |                 |        |        |        |  |  |  |

| bit 4 |                                                                                              | RT Transmi                   | -              |               |                 |        |        |        |  |  |  |

|       |                                                                                              | s the USAR                   |                | •             |                 |        |        |        |  |  |  |

| bit 3 | SSPIE: Syl                                                                                   | nchronous S                  | Serial Port In | nterrupt Ena  | ıble bit        |        |        |        |  |  |  |

|       | <b>SSPIE</b> : Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt |                              |                |               |                 |        |        |        |  |  |  |

|       | 0 = Disable                                                                                  | es the SSP i                 | nterrupt       |               |                 |        |        |        |  |  |  |

| bit 2 |                                                                                              | CP1 Interru                  | •              | it            |                 |        |        |        |  |  |  |

|       |                                                                                              | s the CCP1                   | •              |               |                 |        |        |        |  |  |  |

|       |                                                                                              | es the CCP1                  | •              |               |                 |        |        |        |  |  |  |

| bit 1 |                                                                                              | MR2 to PR2                   |                | •             |                 |        |        |        |  |  |  |

|       |                                                                                              | s the TMR2<br>es the TMR2    |                | •             |                 |        |        |        |  |  |  |

| bit 0 |                                                                                              |                              |                |               | L               |        |        |        |  |  |  |

|       |                                                                                              | MR1 Overfless the TMR1       | -              |               |                 |        |        |        |  |  |  |

|       |                                                                                              | es the TMR1                  |                | •             |                 |        |        |        |  |  |  |

|       |                                                                                              |                              |                |               |                 |        |        |        |  |  |  |

Note 1: PSPIE is reserved on PIC16F873/876 devices; always maintain this bit clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt, the SSP bus collision interrupt and the EEPROM write operation interrupt.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

R = Readable bit

- n = Value at POR

| U-0   | R/W-0    | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|----------|-----|-------|-------|-----|-----|--------|

| -     | Reserved | —   | EEIF  | BCLIF | —   | —   | CCP2IF |

| bit 7 |          |     |       |       |     |     | bit 0  |

| Unimplemented: Read as '0'                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                             |

| Reserved: Always maintain this bit clear                                                                                                                                    |

| Unimplemented: Read as '0'                                                                                                                                                  |

| EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                             |

| <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                   |

| BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                     |

| <ul> <li>1 = A bus collision has occurred in the SSP, when configured for I2C Master mode</li> <li>0 = No bus collision has occurred</li> </ul>                             |

| Unimplemented: Read as '0'                                                                                                                                                  |

| CCP2IF: CCP2 Interrupt Flag bit                                                                                                                                             |

| Capture mode:                                                                                                                                                               |

| <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> <li><u>Compare mode:</u></li> </ul>         |

| <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> <li><u>PWM mode:</u></li> </ul> |

| Unused<br>Leaend:                                                                                                                                                           |

|                                                                                                                                                                             |

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

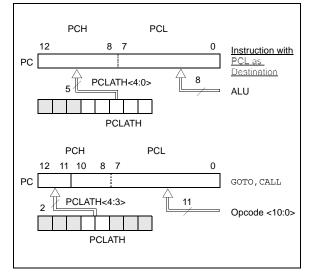

#### 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

#### 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | unchanged after a RETURN or RETFIE         |  |  |  |  |  |  |  |  |

|       | instruction is executed. The user must     |  |  |  |  |  |  |  |  |

|       | rewrite the contents of the PCLATH regis-  |  |  |  |  |  |  |  |  |

|       | ter for any subsequent subroutine calls or |  |  |  |  |  |  |  |  |

|       | GOTO instructions.                         |  |  |  |  |  |  |  |  |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| _       | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

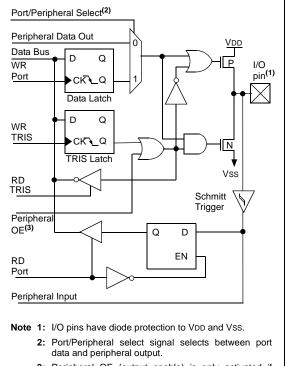

#### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

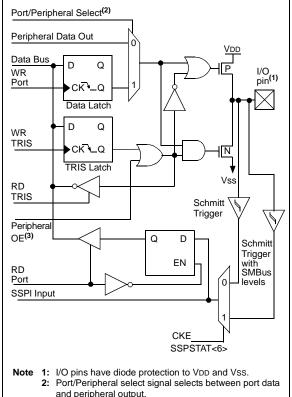

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

#### FIGURE 3-6:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

| TABLE 5-1: | <b>REGISTERS ASSOCIATED WITH TIMER0</b> |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| Address               | Name       | Bit 7  | Bit 6      | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|------------|----------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Module's F | Register | •     |       |       |       |       | XXXX XXXX                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE     | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | T0CS     | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

| Address                | Name    | Bit 7                | Bit 6         | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POF<br>BO | R,   | Valu<br>all o<br>RES | ther |

|------------------------|---------|----------------------|---------------|-------------|---------|---------|--------|---------|---------|--------------------|------|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE          | TOIE        | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 (             | 000x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF          | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000               | 0000 | 0000                 | 0000 |

| 0Dh                    | PIR2    | _                    | —             | _           | _       | —       | _      | _       | CCP2IF  |                    | 0    |                      | 0    |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE          | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000               | 0000 | 0000                 | 0000 |

| 8Dh                    | PIE2    | —                    | —             | —           | _       | —       | _      | —       | CCP2IE  |                    | 0    |                      | 0    |

| 87h                    | TRISC   | PORTC D              | Data Directio | n Register  |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Regi  | ster        |         |         |        |         |         | 0000               | 0000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Perio | od Register |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 12h                    | T2CON   | —                    | TOUTPS3       | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 (             | 0000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PW    | /M Register | 1 (LSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PW    | /M Register | 1 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | —                    |               | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 (               | 0000 | 00                   | 0000 |

| 1Bh                    | CCPR2L  | Capture/C            | Compare/PW    | /M Register | 2 (LSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PW    | /M Register | 2 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 1Dh                    | CCP2CON | —                    | —             | CCP2X       | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 (               | 0000 | 00                   | 0000 |

| <b>TABLE 8-5</b> : | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--------------------|-------------------------------------------------|

|--------------------|-------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

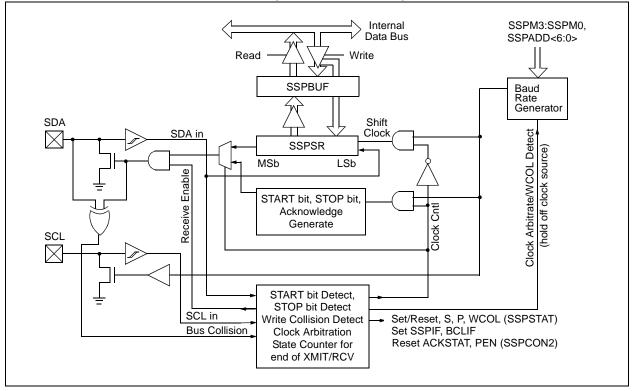

#### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

#### FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

#### 9.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP module must be in an IDLE state     |

|-------|---------------------------------------------|

|       | before the RCEN bit is set, or the RCEN bit |

|       | will be disregarded.                        |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high), and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 9.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 9.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

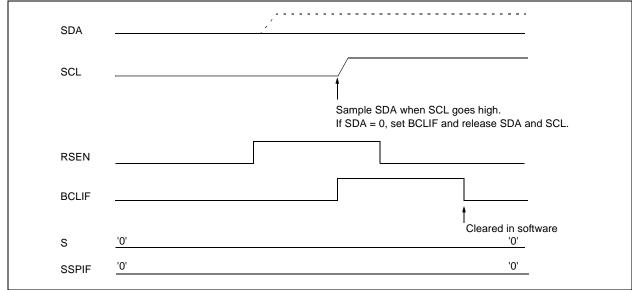

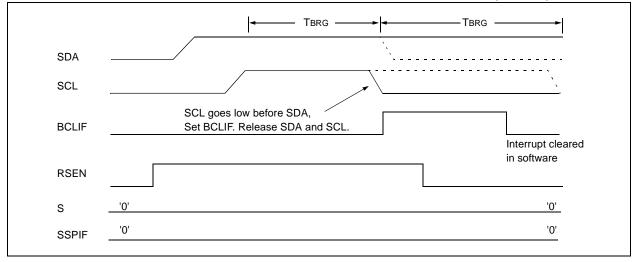

# 9.2.18.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data'0'). If, however,

SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data'1' during the Repeated START condition.

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete (Figure 9-23).

#### FIGURE 9-23: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 9-24: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

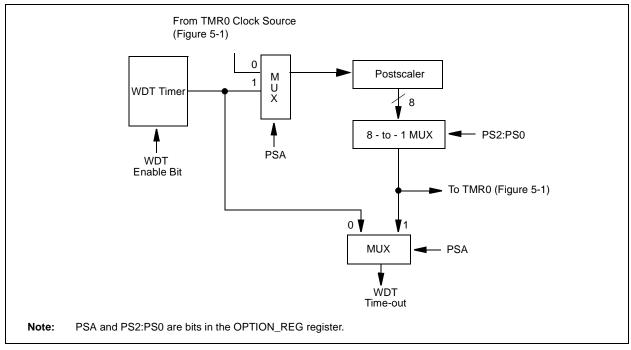

#### 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer. **Note 1:** See Register 12-1 for operation of these bits.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                       |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                 |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |  |  |

| ORLW Inclusive OR Literal with W |                                                                                                                           |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:                        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |

| Operation:                       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected:                 | Z                                                                                                                         |  |  |  |  |

| Description:                     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |

| INCF Increment f |                                                                                                                                                                        | IORWF            | Inclusive OR W with f                                                                                                                                                 |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                       | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                              |  |  |  |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                                     |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |

# PIC16F87X

NOTES:

## 15.0 ELECTRICAL CHARACTERISTICS

| Absolute Maximum Ratings † | Absolute | Maximum | Ratings † |

|----------------------------|----------|---------|-----------|

|----------------------------|----------|---------|-----------|

| Ambient temperature under bias                                                                              |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3 V to (VDD + 0.3 V)             |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5 V                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14 V                         |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +8.5 V                        |

| Total power dissipation (Note 1)                                                                            | 1.0 W                              |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into Vod pin                                                                                | 250 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| <b>2:</b> Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80   | mA <u>, may cause latch-up</u> .   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on PIC16F873/876 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

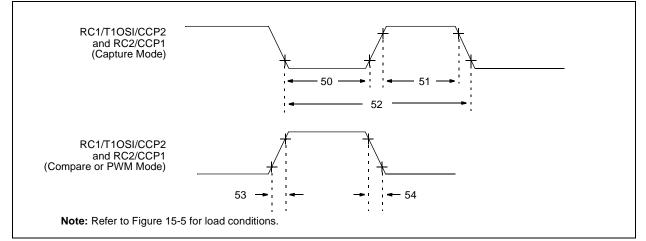

#### FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym  |                                | Min              | Тур†         | Max                   | Units | Conditions |    |                                    |

|--------------|------|--------------------------------|------------------|--------------|-----------------------|-------|------------|----|------------------------------------|

| 50*          | TccL | CCP1 and CCP2                  | No Prescaler     |              | 0.5Tcy + 20           | —     | _          | ns |                                    |

|              |      | input low time                 |                  | Standard(F)  | 10                    | _     | _          | ns |                                    |

|              |      |                                | With Prescaler   | Extended(LF) | 20                    | _     | _          | ns |                                    |

| 51*          | TccH | CCP1 and CCP2                  | No Prescaler     |              | 0.5TCY + 20           | _     | _          | ns |                                    |

|              |      | input high time                |                  | Standard(F)  | 10                    | —     | _          | ns |                                    |

|              |      |                                | With Prescaler   | Extended(LF) | 20                    | —     | _          | ns |                                    |

| 52*          | TccP | CCP1 and CCP2 input period     |                  |              | <u>3TCY + 40</u><br>N | _     | _          | ns | N = prescale<br>value (1, 4 or 16) |

| 53*          | TccR | CCP1 and CCP2 c                | output rise time | Standard(F)  | —                     | 10    | 25         | ns |                                    |

|              |      |                                |                  | Extended(LF) | —                     | 25    | 50         | ns |                                    |

| 54*          | TccF | CCP1 and CCP2 output fall time |                  | Standard(F)  | —                     | 10    | 25         | ns |                                    |

|              |      |                                |                  | Extended(LF) | —                     | 25    | 45         | ns |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

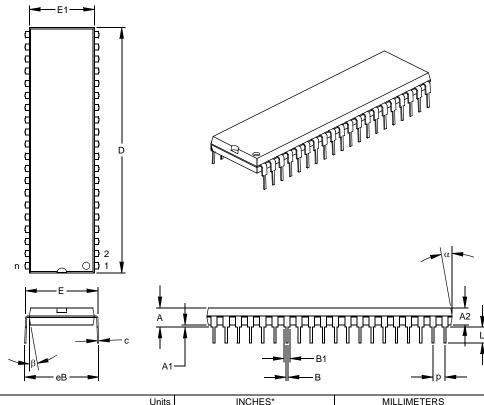

#### 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |     | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-----|---------|-------|-------|-------------|-------|-------|--|

| Dimensio                   | MIN | NOM     | MAX   | MIN   | NOM         | MAX   |       |  |

| Number of Pins             | n   |         | 40    |       |             | 40    |       |  |

| Pitch                      | р   |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α   | .160    | .175  | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2  | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1  | .015    |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E   | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1  | .530    | .545  | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D   | 2.045   | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L   | .120    | .130  | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С   | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1  | .030    | .050  | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В   | .014    | .018  | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eB  | .620    | .650  | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α   | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β   | 5       | 10    | 15    | 5           | 10    | 15    |  |

| * 0 / " D /                |     |         |       |       |             |       |       |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

#### APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 1998 | This is a new data sheet.<br>However, these devices are<br>similar to the PIC16C7X<br>devices found in the<br>PIC16C7X Data Sheet<br>(DS30390). Data Memory<br>Map for PIC16F873/874,<br>moved ADFM bit from<br>ADCON1<5> to ADCON1<7>. |

| В       | 1999 | FLASH EEPROM access<br>information.                                                                                                                                                                                                     |

| С       | 2000 | DC characteristics updated.<br>DC performance graphs<br>added.                                                                                                                                                                          |

| D       | 2013 | Added a note to each package drawing.                                                                                                                                                                                                   |

### APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

| Difference             | PIC16F876/873                                             | PIC16F877/874                                               |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------|

| A/D                    | 5 channels,<br>10-bits                                    | 8 channels,<br>10-bits                                      |

| Parallel<br>Slave Port | no                                                        | yes                                                         |

| Packages               | 28-pin PDIP,<br>28-pin windowed<br>CERDIP, 28-pin<br>SOIC | 40-pin PDIP,<br>44-pin TQFP,<br>44-pin MQFP,<br>44-pin PLCC |

# PIC16F87X

| PORTE                                          |

|------------------------------------------------|

| Analog Port Pins9, 36, 38                      |

| Associated Registers                           |

| Block Diagram                                  |

| Input Buffer Full Status (IBF Bit)             |

| Input Buffer Overflow (IBOV Bit)               |

| Output Buffer Full Status (OBF Bit)            |

| PORTE Register 15, 36                          |

| PSP Mode Select (PSPMODE Bit)                  |

| RE0/RD/AN5 Pin9, 36, 38                        |

| RE1/WR/AN6 Pin9, 36, 38                        |

| RE2/CS/AN7 Pin9, 36, 38                        |

| TRISE Register                                 |

| Postscaler, WDT                                |

| Assignment (PSA Bit)19                         |

| Rate Select (PS2:PS0 Bits) 19                  |

| Power-down Mode. See SLEEP                     |

| Power-on Reset (POR)119, 123, 124, 125, 126    |

| Oscillator Start-up Timer (OST) 119, 124       |

| POR Status (POR Bit)25                         |

| Power Control (PCON) Register                  |

| Power-down (PD Bit)18, 123                     |

| Power-up <u>Tim</u> er (PWRT)119, 124          |

| Time-out (TO Bit)18, 123                       |

| Time-out Sequence on Power-up 127, 128         |

| PR2 Register 16, 55                            |

| Prescaler, Timer0                              |

| Assignment (PSA Bit)19                         |

| Rate Select (PS2:PS0 Bits) 19                  |

| PRO MATE II Universal Device Programmer        |

| Program Counter                                |

| RESET Conditions 125                           |

| Program Memory11                               |

| Interrupt Vector11                             |

| Paging 11, 26                                  |

| Program Memory Map11                           |

| RESET Vector 11                                |

| Program Verification                           |

| Programming Pin (VPP)7, 8                      |

| Programming, Device Instructions               |

| PSP. See Parallel Slave Port                   |

| Pulse Width Modulation.SeeCapture/Compare/PWM, |

| PWM Mode.                                      |

| PUSH                                           |

## R

| R/W                                   |        |

|---------------------------------------|--------|

| R/W bit                               | 74     |

| R/W bit                               | 74     |

| RAM. See Data Memory                  |        |

| RCREG                                 |        |

| RCSTA Register                        | 17, 96 |

| ADDEN Bit                             |        |

| CREN Bit                              |        |

| FERR Bit                              |        |

| OERR Bit                              |        |

| RX9 Bit                               |        |

| RX9D Bit                              |        |

| SPEN Bit                              |        |

| SREN Bit                              |        |

| Read/Write bit, R/W                   |        |

| Reader Response                       |        |

| Receive Enable bit                    |        |

| Receive Overflow Indicator bit, SSPOV | 67     |

| Register File                         |        |

| Register File Map                     |        |

|                                       |        |

| Registers                                        |

|--------------------------------------------------|

| ADCON0 (A/D Control 0) 111                       |

| ADCON1 (A/D Control 1) 112                       |

| CCP1CON (CCP Control 1) 58                       |

| EECON2 41                                        |

| FSR                                              |

| INTCON 20                                        |

| OPTION_REG19, 48                                 |

| PCON (Power Control) 25                          |

| PIE1 (Peripheral Interrupt Enable 1) 21          |

| PIE2 (Peripheral Interrupt Enable 2)             |

| PIR1 (Peripheral Interrupt Request 1) 22         |

| PIR2 (Peripheral Interrupt Request 2) 24         |

| RCSTA (Receive Status and Control)               |

| Special Function, Summary 15                     |

| SSPCON2 (Sync Serial Port Control 2) 68          |

| STATUS                                           |

| T1CON (Timer1 Control) 51                        |

| T2CON (Timer 2 Control)                          |

| Timer2                                           |

| T2CON Register                                   |

| TRISE                                            |

| TXSTA (Transmit Status and Control)              |

| Repeated START Condition Enable bit              |

| RESET                                            |

| Block Diagram                                    |

| RESET                                            |

| Brown-out Reset (BOR). See Brown-out Reset (BOR) |

| Power-on Reset (POR). See Power-on Reset (POR)   |

| RESET Conditions for PCON Register               |

| RESET Conditions for Program Counter             |

| RESET Conditions for STATUS Register             |

| WDT Reset. See Watchdog Timer (WDT)              |

| Revision History                                 |

|                                                  |

| S                                                |

| S (START bit)<br>Sales and Support<br>SCI. See USART |               |

|------------------------------------------------------|---------------|

| SCK                                                  | 69            |

| SCL                                                  | 74            |

| SDA                                                  | 74            |

| SDI                                                  | 69            |

| SDO                                                  |               |

| Serial Clock, SCK                                    | 69            |

| Serial Clock, SCL                                    | 74            |

| Serial Communication Interface. See USART            |               |

| Serial Data Address, SDA                             | 74            |

| Serial Data In, SDI                                  | 69            |

| Serial Data Out, SDO                                 | 69            |

| Slave Select, SS                                     | 69            |

| SLEEP                                                | 119, 123, 132 |

| SMP                                                  | 66            |

| Software Simulator (MPLAB SIM)                       | 144           |

| SPBRG Register                                       |               |

| Special Features of the CPU                          | 119           |

| Special Function Registers                           | 15            |

| Special Function Registers (SFRs)                    | 15            |

| Data EEPROM and FLASH Program Mem                    |               |

| Speed, Operating                                     | 1             |

$\odot$  1998-2013 Microchip Technology Inc.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12