Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874t-04i-l |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for  |

|-------|--------------------------------------------|

|       | the TMR0 register, assign the prescaler to |

|       | the Watchdog Timer.                        |

#### **R/W-1** R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 bit 7 bit 0 **RBPU:** PORTB Pull-up Enable bit bit 7 1 = PORTB pull-ups are disabled 0 = PORTB pull-ups are enabled by individual port latch values bit 6 **INTEDG:** Interrupt Edge Select bit 1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin bit 5 TOCS: TMR0 Clock Source Select bit 1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) bit 4 TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin bit 3 PSA: Prescaler Assignment bit 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS2:PS0: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 000 1:1 1:2 1:2 001 1:4 010 1:4 1:8 011 1:8 1:16 1:16 100 1:32 101 1:32 1:64 110 1:128 1:64 111 1:128 1:256 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device

#### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

#### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, and the EEPROM write operation interrupt.

### REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

|         | U-0                        | R/W-0          | U-0           | R/W-0        | R/W-0          | U-0       | U-0            | R/W-0  |  |  |  |  |  |

|---------|----------------------------|----------------|---------------|--------------|----------------|-----------|----------------|--------|--|--|--|--|--|

|         | —                          | Reserved       | —             | EEIE         | BCLIE          | —         | —              | CCP2IE |  |  |  |  |  |

|         | bit 7                      |                |               |              |                |           |                | bit 0  |  |  |  |  |  |

|         |                            |                |               |              |                |           |                |        |  |  |  |  |  |

| bit 7   | Unimplemented: Read as '0' |                |               |              |                |           |                |        |  |  |  |  |  |

| bit 6   | Reserved:                  | Always mair    | ntain this bi | it clear     |                |           |                |        |  |  |  |  |  |

| bit 5   | Unimplem                   | ented: Read    | as '0'        |              |                |           |                |        |  |  |  |  |  |

| bit 4   | EEIE: EEP                  | ROM Write C    | Operation I   | nterrupt Ena | able           |           |                |        |  |  |  |  |  |

|         | 1 = Enable                 | EE Write Int   | errupt        |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                | e EE Write In  | terrupt       |              |                |           |                |        |  |  |  |  |  |

| bit 3   | BCLIE: Bu                  | s Collision In | terrupt Ena   | able         |                |           |                |        |  |  |  |  |  |

|         | 1 = Enable                 | Bus Collisio   | n Interrupt   |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                | e Bus Collisio | on Interrupt  |              |                |           |                |        |  |  |  |  |  |

| bit 2-1 | Unimplem                   | ented: Read    | as '0'        |              |                |           |                |        |  |  |  |  |  |

| bit 0   | CCP2IE: C                  | CP2 Interrup   | t Enable b    | it           |                |           |                |        |  |  |  |  |  |

|         | 1 = Enable                 | s the CCP2 i   | nterrupt      |              |                |           |                |        |  |  |  |  |  |

|         | 0 = Disable                | es the CCP2    | interrupt     |              |                |           |                |        |  |  |  |  |  |

|         |                            |                |               |              |                |           |                |        |  |  |  |  |  |

|         | Legend:                    |                |               |              |                |           |                |        |  |  |  |  |  |

|         | R = Reada                  | ble bit        | VV = V        | Vritable bit | U = Unimpl     | emented b | oit, read as ' | 0'     |  |  |  |  |  |

|         | - n = Value                | at POR         | '1' = E       | Bit is set   | '0' = Bit is c | leared    | x = Bit is u   | nknown |  |  |  |  |  |

NOTES:

| Name         | Bit# | Buffer | Function                                                                        |  |  |  |  |  |

|--------------|------|--------|---------------------------------------------------------------------------------|--|--|--|--|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |  |  |  |  |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |  |  |  |  |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |  |  |  |  |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |  |  |  |  |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |  |  |  |  |  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |  |  |  |  |  |

#### TABLE 3-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|--------|------------|---------|---------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     |       | RA5   | RA4    | RA3        | RA2     | RA1     | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     | _     | PORTA | Data D | irection F | 11 1111 | 11 1111 |       |                          |                                 |

| 9Fh     | ADCON1 | ADFM  |       | _     |        | PCFG3      | PCFG2   | PCFG1   | PCFG0 | 0- 0000                  | 0-0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.

| Name                   | Bit# | Buffer                | Function                                                                                                                                          |

|------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 3-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | ORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                       | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

## 8.0 CAPTURE/COMPARE/PWM MODULES

Each Capture/Compare/PWM (CCP) module contains a 16-bit register which can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register

Both the CCP1 and CCP2 modules are identical in operation, with the exception being the operation of the special event trigger. Table 8-1 and Table 8-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### CCP1 Module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match and will reset Timer1.

#### CCP2 Module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. The special event trigger is generated by a compare match and will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

Additional information on CCP modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) and in application note AN594, "Using the CCP Modules" (DS00594).

#### TABLE 8-1: CCP MODE - TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

## TABLE 8-2:INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                          |

|-----------|-----------|--------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1 |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt)               |

| PWM       | Capture   | None                                                                                 |

| PWM       | Compare   | None                                                                                 |

| REGISTER 0-1: | -1: CCPTCON REGISTER/CCP2CON REGISTER (ADDRESS: 171/101)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |             |              |                |             |              |        |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------|--------------|----------------|-------------|--------------|--------|--|--|--|--|

|               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                     | R/W-0       | R/W-0        | R/W-0          | R/W-0       | R/W-0        | R/W-0  |  |  |  |  |

|               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                       | CCPxX       | CCPxY        | CCPxM3         | CCPxM2      | CCPxM1       | CCPxM0 |  |  |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |             |              |                |             |              | bit 0  |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |              |                |             |              |        |  |  |  |  |

| bit 7-6       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |             |              |                |             |              |        |  |  |  |  |

| bit 5-4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CCPxX:CCPxY: PWM Least Significant bits |             |              |                |             |              |        |  |  |  |  |

|               | <u>Capture mode</u> :<br>Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                         |             |              |                |             |              |        |  |  |  |  |

|               | <u>Compare mode:</u><br>Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |             |              |                |             |              |        |  |  |  |  |

|               | <u>PWM mode</u><br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | LSbs of the | e PWM duty   | cycle. The eig | ght MSbs ar | e found in C | CPRxL. |  |  |  |  |

| bit 3-0       | CCPxM3:C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CPxM0: C                                | CPx Mode S  | Select bits  |                |             |              |        |  |  |  |  |

|               | <ul> <li>CCPxM3:CCPxM0: CCPx Mode Select bits</li> <li>0000 = Capture/Compare/PWM disabled (resets CCPx module)</li> <li>0100 = Capture mode, every falling edge</li> <li>0101 = Capture mode, every rising edge</li> <li>0110 = Capture mode, every 4th rising edge</li> <li>0111 = Capture mode, every 16th rising edge</li> <li>1000 = Compare mode, set output on match (CCPxIF bit is set)</li> <li>1001 = Compare mode, clear output on match (CCPxIF bit is set)</li> <li>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)</li> <li>1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled)</li> <li>11xx = PWM mode</li> </ul> |                                         |             |              |                |             |              |        |  |  |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |             |              |                |             |              |        |  |  |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ble bit                                 | VV = V      | Vritable bit | U = Unim       | plemented l | bit, read as | ʻ0'    |  |  |  |  |

'1' = Bit is set

- n = Value at POR

## REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

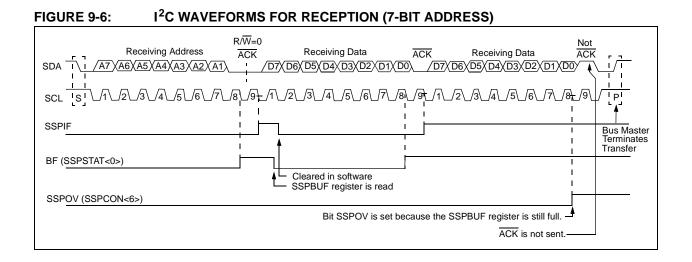

| Status Bits as Data<br>Transfer is Received |       | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|---------------------------------------------|-------|---------------------------|-----------------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                           | ruise                 | if enabled)                            |  |  |

| 0                                           | 0     | Yes                       | Yes                   | Yes                                    |  |  |

| 1                                           | 0     | No                        | No                    | Yes                                    |  |  |

| 1                                           | 1     | No                        | No                    | Yes                                    |  |  |

| 0                                           | 1     | Yes                       | No                    | Yes                                    |  |  |

TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

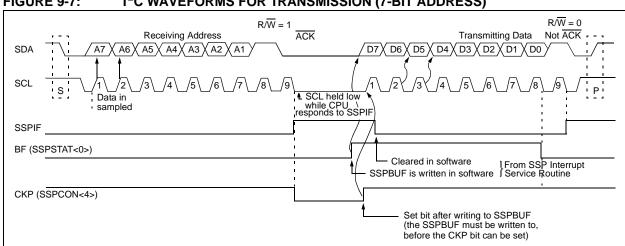

#### 9.2.1.3 Slave Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7). An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting the CKP bit.

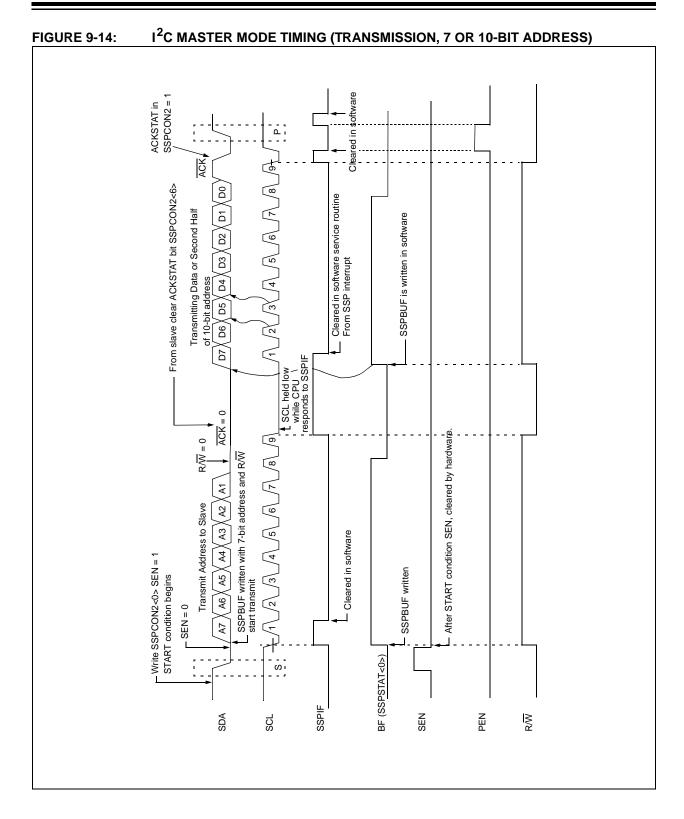

#### FIGURE 9-7: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

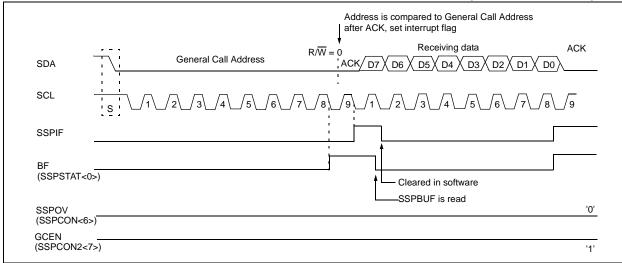

#### 9.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a START bit detect, 8 bits are shifted into SSPSR and the address is compared against SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific, or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set, while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 9-8).

#### FIGURE 9-8: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

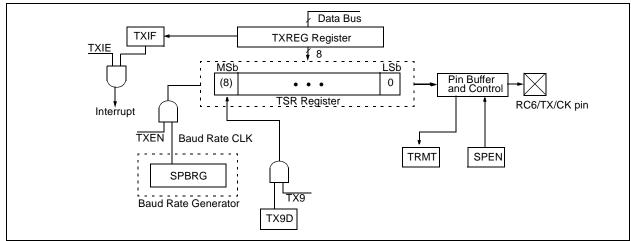

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

NOTES:

#### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

#### bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | А          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | А          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | А          | А          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

#### 12.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge triggered, either rising, if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit, GIE, decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>) (Section 5.0).

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>) (Section 3.2).

### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, (i.e., W register and STATUS register). This will have to be implemented in software.

For the PIC16F873/874 devices, the register W\_TEMP must be defined in both banks 0 and 1 and must be defined at the same offset from the bank base address (i.e., If W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1). The registers, PCLATH\_TEMP and STATUS\_TEMP, are only defined in bank 0.

Since the upper 16 bytes of each bank are common in the PIC16F876/877 devices, temporary holding registers W\_TEMP, STATUS\_TEMP, and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 12-1 can be used.

| MOVWF  | W TEMP         | ;Copy W to TEMP register                                |

|--------|----------------|---------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                         |

|        |                | · 1                                                     |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3             |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

| :      |                |                                                         |

| :(ISR) |                | ;(Insert user code here)                                |

| :      |                |                                                         |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                       |

|        |                | ;(sets bank to original state)                          |

| MOVWF  | STATUS         | ;Move W into STATUS register                            |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                            |

| SWAPF  | W TEMP,W       | ;Swap W TEMP into W                                     |

|        | -              | - <u>-</u>                                              |

#### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

|                            | Q1 Q2 Q3 Q4                                                          | Q1 Q2 Q3 Q4       | Q1          |             | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      |

|----------------------------|----------------------------------------------------------------------|-------------------|-------------|-------------|--------------|-------------------|-------------------|------------------|

| OSC1                       | ·/~~~~/                                                              |                   |             | -           |              | <u>;</u> ~~~~~~   |                   |                  |

| CLKOUT <sup>(4)</sup>      | \/\                                                                  |                   | <u> </u>    | Tost(2)     | /            | \                 | ¦/ \              |                  |

| INT pin                    | · · ·                                                                | 1                 |             | · ·         |              | 1<br>1            | 1 I<br>1 I        |                  |

| INTF Flag<br>(INTCON<1>)   |                                                                      | י<br>י<br>י<br>י  | 4           | /           |              | Interrupt Latency | (2)               | <br>  <br> <br>  |

| GIE bit<br>(INTCON<7>)     | 1 I<br>1 I<br>1 I<br>1 I<br>1 I                                      | i<br>             | Processor i | n           |              | ·                 | 1 1<br>1 1<br>1 1 | ו<br>ו<br>ו<br>ו |

| INSTRUCTIO                 | N FLOW                                                               |                   |             | · ·         |              | 1                 | 1 1<br>1 1        | 1                |

| PC                         | Х РС Х                                                               | PC+1              | ХР          | C+2         | PC+2         | X PC + 2          | <u>X 0004h X</u>  | 0005h            |

| Instruction {<br>Fetched { | Inst(PC) = SLEEP                                                     | Inst(PC + 1)      |             | 1           | Inst(PC + 2) | 1<br>1<br>1       | Inst(0004h)       | Inst(0005h)      |

| Instruction                | Inst(PC - 1)                                                         | SLEEP             |             | ,<br>,<br>, | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h)      |

| 2: Tost                    | HS or LP oscillator n<br>τ = 1024Tosc (drawi<br>= '1' assumed. In th | ing not to scale) |             |             |              |                   |                   |                  |

## F

If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

## 12.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-8 shows which features are consumed by the background debugger.

| TABLE 12-8: DE | BUGGER RESOURCES |

|----------------|------------------|

|----------------|------------------|

| I/O pins       | RB6, RB7                                     |

|----------------|----------------------------------------------|

| Stack          | 1 level                                      |

| Program Memory | Address 0000h must be NOP                    |

|                | Last 100h words                              |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

## 13.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

|------------------|---------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

Bit Clear f

BCF

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |

| Status Affected: | Z                                                                                                                      |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register. |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                     |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                           |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |  |  |  |  |

#### 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

## 14.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC MCU series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

### 14.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC MCU microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 14.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

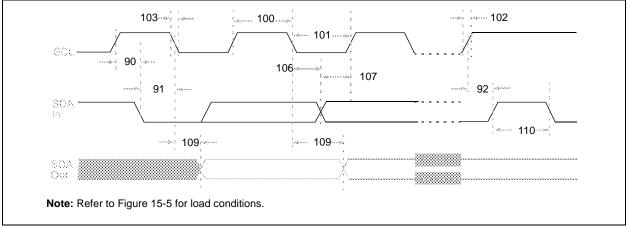

| Parameter<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                         |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|

| 90               | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for Repeated         |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | START condition                    |

| 91               | Thd:sta | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period, the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       | pulse is generated                 |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                    |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | _   |       |                                    |

| 93               | Thd:sto | STOP condition  | 100 kHz mode | 4000 | -   | _   | ns    |                                    |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       |                                    |

| TABLE 15-8: | I <sup>2</sup> C BUS START/STOP BITS REQUIREMENTS |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

## FIGURE 15-18: I<sup>2</sup>C BUS DATA TIMING

## Package Marking Information (Cont'd)

#### 44-Lead TQFP

#### Example

$\bigcirc$

Example

$\lambda \lambda$

PIC16F877-04/P

0112SAA

MICROCHIP

#### 44-Lead MQFP

### Example

#### 44-Lead PLCC

#### Example

\_\_\_\_\_

NOTES: