Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

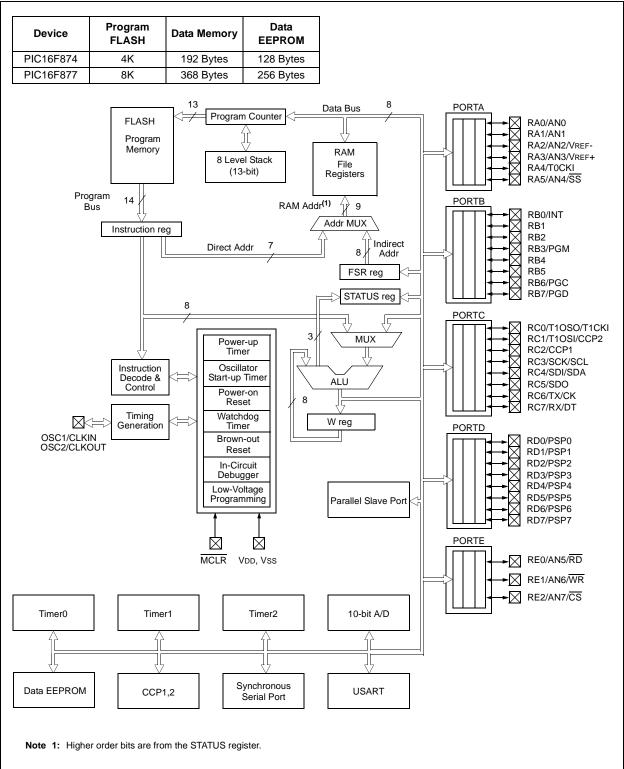

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 33                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-QFP                                                                       |

| Supplier Device Package    | 44-MQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf874t-04i-pq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be found in Section 4.0 of this data sheet. |

|-------|--------------------------------------------------------------------------------|

| 2.2.4 |                                                                                |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

#### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                                                                                                                                                                                                                                                          | File<br>Address | A                              | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>                                                                                                                                                                                                                              | 00h             | Indirect addr.(*)              | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                                                                                                                                                                                                                                                       | 01h             | OPTION_REG                     | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                                                                                                                                                                                                                                                        | 02h             | PCL                            | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                                                                                                                                                                                                                                                     | 03h             | STATUS                         | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                                                                                                                                                                                                                                                        | 04h             | FSR                            | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                                                                                                                                                                                                                                                      | 05h             | TRISA                          | 85h            |                     | 105h            |                         | 185h           |

| PORTB                                                                                                                                                                                                                                                      | 06h             | TRISB                          | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                                                                                                                                                                                                                                                      | 07h             | TRISC                          | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>                                                                                                                                                                                                                                       | 08h             | TRISD <sup>(1)</sup>           | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>                                                                                                                                                                                                                                       | 09h             | TRISE <sup>(1)</sup>           | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                                                                                                                                                                                                                                                     | 0Ah             | PCLATH                         | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                                                                                                                                                                                                                                                     | 0Bh             | INTCON                         | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                                                                                                                                                                                                                                                       | 0Ch             | PIE1                           | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                                                                                                                                                                                                                                                       | 0Dh             | PIE2                           | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                                                                                                                                                                                                                                                      | 0Eh             | PCON                           | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                                                                                                                                                                                                                                                      | 0Fh             |                                | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                                                                                                                                                                                                                                                      | 10h             |                                | 90h            |                     | 110h            |                         | 190h           |

| TMR2                                                                                                                                                                                                                                                       | 11h             | SSPCON2                        | 91h            |                     |                 |                         |                |

| T2CON                                                                                                                                                                                                                                                      | 12h             | PR2                            | 92h            |                     |                 |                         |                |

| SSPBUF                                                                                                                                                                                                                                                     | 13h             | SSPADD                         | 93h            |                     |                 |                         |                |

| SSPCON                                                                                                                                                                                                                                                     | 14h             | SSPSTAT                        | 94h            |                     |                 |                         |                |

| CCPR1L                                                                                                                                                                                                                                                     | 15h             |                                | 95h            |                     |                 |                         |                |

| CCPR1H                                                                                                                                                                                                                                                     | 16h             |                                | 96h            |                     |                 |                         |                |

| CCP1CON                                                                                                                                                                                                                                                    | 17h             |                                | 97h            |                     |                 |                         |                |

| RCSTA                                                                                                                                                                                                                                                      | 18h             | TXSTA                          | 98h            |                     |                 |                         |                |

| TXREG                                                                                                                                                                                                                                                      | 19h             | SPBRG                          | 99h            |                     |                 |                         |                |

| RCREG                                                                                                                                                                                                                                                      | 1Ah             |                                | 9Ah            |                     |                 |                         |                |

| CCPR2L                                                                                                                                                                                                                                                     | 1Bh             |                                | 9Bh            |                     |                 |                         |                |

| CCPR2H                                                                                                                                                                                                                                                     | 1Ch             |                                | 9Ch            |                     |                 |                         |                |

| CCP2CON                                                                                                                                                                                                                                                    | 1Dh             |                                | 9Dh            |                     |                 |                         |                |

| ADRESH                                                                                                                                                                                                                                                     | 1Eh             | ADRESL                         | 9Eh            |                     |                 |                         |                |

| ADCON0                                                                                                                                                                                                                                                     | 1Fh             | ADCON1                         | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                                                                                                                                                                                                                                            | 20h             |                                | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register                                                                                                                                                                                                                             |                 | General<br>Purpose<br>Register |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                                                                                                                                                                                                                                                   |                 | 96 Bytes                       |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                                                                                                                                                                                                                                            | 754             |                                |                |                     | 1756            |                         | 4              |

| Bank 0                                                                                                                                                                                                                                                     | J 7Fh           | Bank 1                         | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>* Not a physical register.</li> <li>Note 1: These registers are not implemented on the PIC16F873.</li> <li>2: These registers are reserved, maintain these registers clear.</li> </ul> |                 |                                |                |                     |                 |                         |                |

NOTES:

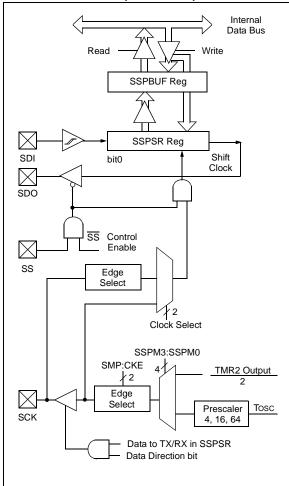

#### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

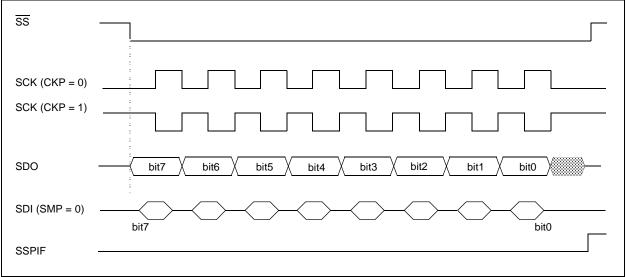

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

#### FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

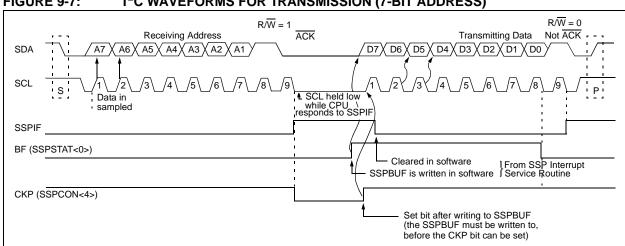

#### FIGURE 9-7: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

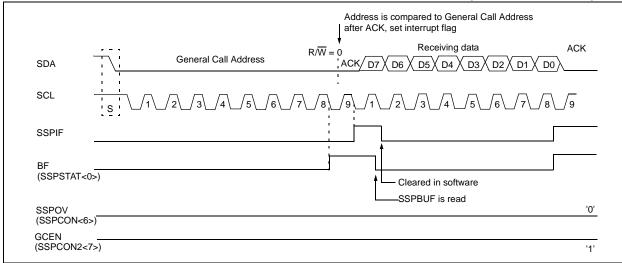

#### 9.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all 0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a START bit detect, 8 bits are shifted into SSPSR and the address is compared against SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPIF flag is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific, or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set, while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the Acknowledge (Figure 9-8).

#### FIGURE 9-8: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

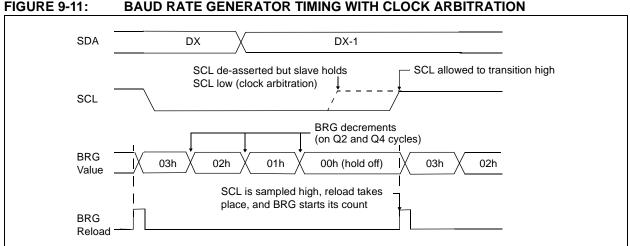

#### BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

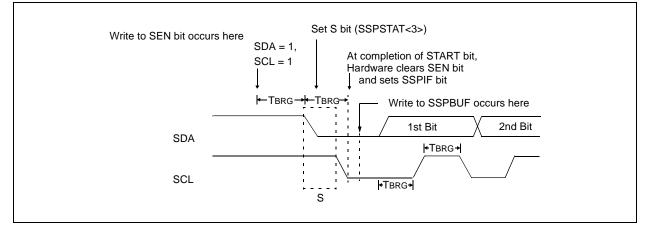

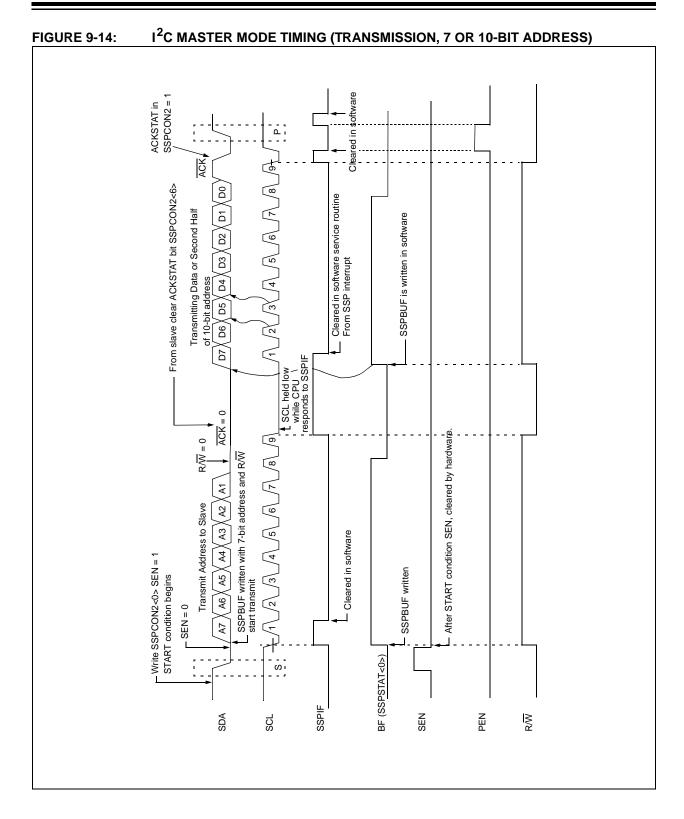

#### 9.2.9 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the START condition, and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware. The baud rate generator is suspended, leaving the SDA line held low, and the START condition is complete.

Note: If, at the beginning of START condition, the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

#### 9.2.9.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

#### **FIGURE 9-12:** FIRST START BIT TIMING

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6                                           | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-------------------------------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                                            | TOIE    | INTE  | RBIE  | T0IF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                            | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                                             | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART R              | eceive R                                        | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                            | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                                             | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | aud Rate Generator Register 0000 0000 0000 0000 |         |       |       |        |        |        |                          |                                 |

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note** 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.

#### REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

#### bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | А          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | А          | А          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | Α          | А          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

## 13.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight bit literal 'k'<br>and the result is placed in the W<br>register. |

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

|------------------|---------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

Bit Clear f

BCF

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |  |  |  |  |  |

| Operation:       | skip if $(f < b) = 0$                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                           |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |  |  |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |

|------------------|---------------|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |

| Operands:        | None          |  |  |  |

| Operation:       | No operation  |  |  |  |

| Status Affected: | None          |  |  |  |

| Description:     | No operation. |  |  |  |

| MOVLW            | Move Literal to W                                                                                |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                             |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                      |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                             |  |  |  |  |

| Operands:        | None                                       |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$ |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                          |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |

#### 15.4 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| DC CHARACTERISTICS |       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section 15.1) |         |      |         |       |                                                             |  |

|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|---------|-------|-------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                             | Min     | Тур† | Max     | Units | Conditions                                                  |  |

|                    | VIL   | Input Low Voltage                                                                                                                                                                                          |         |      |         |       |                                                             |  |

|                    |       | I/O ports                                                                                                                                                                                                  |         |      |         |       |                                                             |  |

| D030               |       | with TTL buffer                                                                                                                                                                                            | Vss     | —    | 0.15Vdd |       | For entire VDD range                                        |  |

| D030A              |       |                                                                                                                                                                                                            | Vss     | —    | 0.8V    | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |

| D031               |       | with Schmitt Trigger buffer                                                                                                                                                                                | Vss     | —    | 0.2Vdd  | V     |                                                             |  |

| D032               |       | MCLR, OSC1 (in RC mode)                                                                                                                                                                                    | Vss     | —    | 0.2Vdd  | V     |                                                             |  |

| D033               |       | OSC1 (in XT, HS and LP)                                                                                                                                                                                    | Vss     | —    | 0.3Vdd  | V     | (Note 1)                                                    |  |

|                    |       | Ports RC3 and RC4                                                                                                                                                                                          |         |      |         |       |                                                             |  |

| D034               |       | with Schmitt Trigger buffer                                                                                                                                                                                | Vss     | —    | 0.3Vdd  | V     | For entire VDD range                                        |  |

| D034A              |       | with SMBus                                                                                                                                                                                                 | -0.5    | —    | 0.6     | V     | for $VDD = 4.5$ to $5.5V$                                   |  |

|                    | Vih   | Input High Voltage                                                                                                                                                                                         |         |      |         |       |                                                             |  |

|                    |       | I/O ports                                                                                                                                                                                                  |         | —    |         |       |                                                             |  |

| D040               |       | with TTL buffer                                                                                                                                                                                            | 2.0     | —    | Vdd     | V     | $4.5V \leq V\text{DD} \leq 5.5V$                            |  |

| D040A              |       |                                                                                                                                                                                                            | 0.25Vdd | —    | Vdd     | V     | For entire VDD range                                        |  |

|                    |       |                                                                                                                                                                                                            | + 0.8V  |      |         |       |                                                             |  |

| D041               |       | with Schmitt Trigger buffer                                                                                                                                                                                | 0.8Vdd  | —    | Vdd     | V     | For entire VDD range                                        |  |

| D042               |       | MCLR                                                                                                                                                                                                       | 0.8Vdd  | —    | Vdd     | V     |                                                             |  |

| D042A              |       | OSC1 (XT, HS and LP)                                                                                                                                                                                       | 0.7Vdd  | —    | Vdd     | V     | (Note 1)                                                    |  |

| D043               |       | OSC1 (in RC mode)                                                                                                                                                                                          | 0.9Vdd  | —    | Vdd     | V     |                                                             |  |

|                    |       | Ports RC3 and RC4                                                                                                                                                                                          |         |      |         |       |                                                             |  |

| D044               |       | with Schmitt Trigger buffer                                                                                                                                                                                | 0.7VDD  | —    | Vdd     | V     | For entire VDD range                                        |  |

| D044A              |       | with SMBus                                                                                                                                                                                                 | 1.4     | —    | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |  |

| D070A              | IPURB |                                                                                                                                                                                                            | 50      | 250  | 400     | μA    | VDD = 5V, VPIN = VSS,                                       |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup>                                                                                                                                                                    |         |      |         |       |                                                             |  |

| D060               |       | I/O ports                                                                                                                                                                                                  | -       | -    | ±1      | μΑ    | $Vss \le VPIN \le VDD,$                                     |  |

|                    |       |                                                                                                                                                                                                            |         |      |         |       | Pin at hi-impedance                                         |  |

| D061               |       | MCLR, RA4/T0CKI                                                                                                                                                                                            | -       | -    | ±5      | μΑ    | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |  |

| D063               |       | OSC1                                                                                                                                                                                                       | -       | -    | ±5      | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

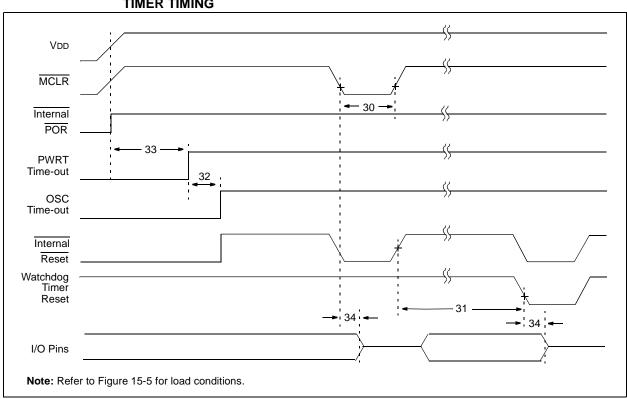

## FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

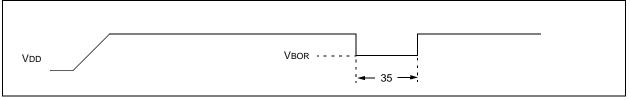

#### FIGURE 15-9: BROWN-OUT RESET TIMING

## TABLE 15-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|------------------|--------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30               | TmcL   | MCLR Pulse Width (low)                                 | 2   | -         | _   | μs    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt   | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost   | Oscillation Start-up Timer Period                      | _   | 1024 Tosc |     | —     | Tosc = OSC1 period       |

| 33*              | Tpwrt  | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | —         | 2.1 | μS    |                          |

| 35               | TBOR   | Brown-out Reset pulse width                            | 100 | _         | _   | μs    | $VDD \le VBOR (D005)$    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

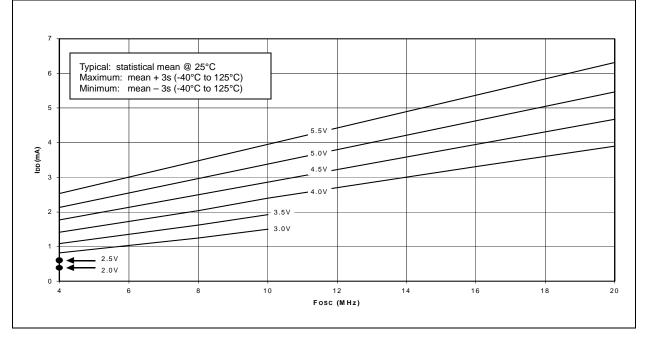

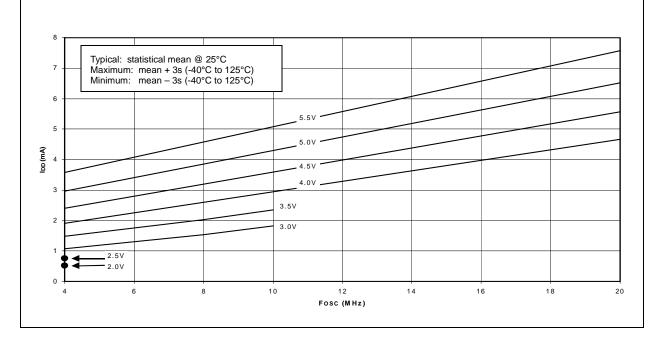

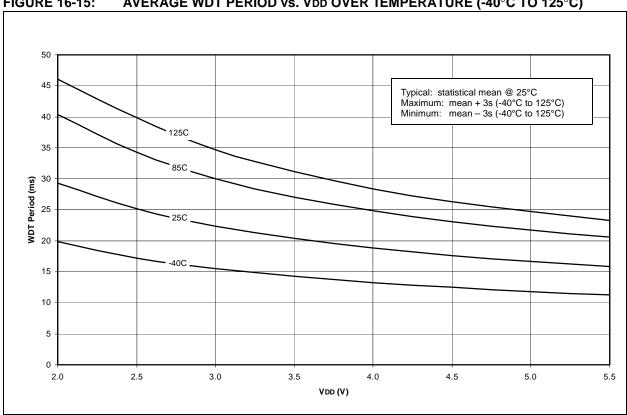

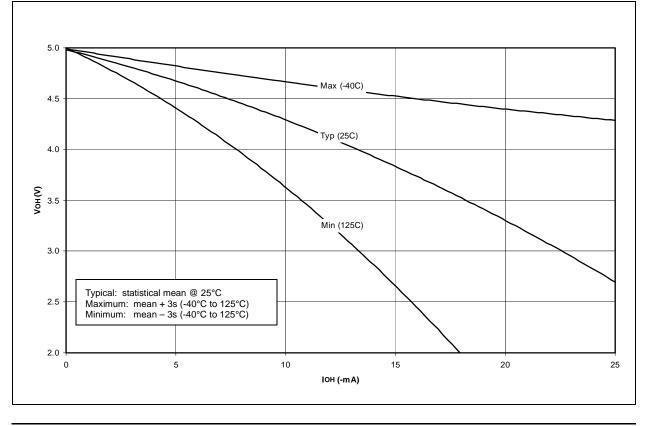

## 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented is **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

#### FIGURE 16-15: AVERAGE WDT PERIOD vs. VDD OVER TEMPERATURE (-40°C TO 125°C)

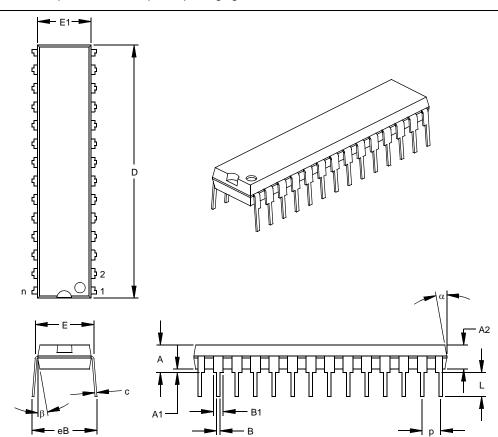

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      | Units INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|------------|---------------|-------|-------|-------------|-------|-------|--|

| Dimens                     | ion Limits | MIN           | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n          |               | 28    |       |             | 28    |       |  |

| Pitch                      | р          |               | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α          | .140          | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Molded Package Thickness   | A2         | .125          | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Base to Seating Plane      | A1         | .015          |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E          | .300          | .310  | .325  | 7.62        | 7.87  | 8.26  |  |

| Molded Package Width       | E1         | .275          | .285  | .295  | 6.99        | 7.24  | 7.49  |  |

| Overall Length             | D          | 1.345         | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |  |

| Tip to Seating Plane       | L          | .125          | .130  | .135  | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С          | .008          | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1         | .040          | .053  | .065  | 1.02        | 1.33  | 1.65  |  |

| Lower Lead Width           | В          | .016          | .019  | .022  | 0.41        | 0.48  | 0.56  |  |

| Overall Row Spacing        | § eB       | .320          | .350  | .430  | 8.13        | 8.89  | 10.92 |  |

| Mold Draft Angle Top       | α          | 5             | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β          | 5             | 10    | 15    | 5           | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

Notes:

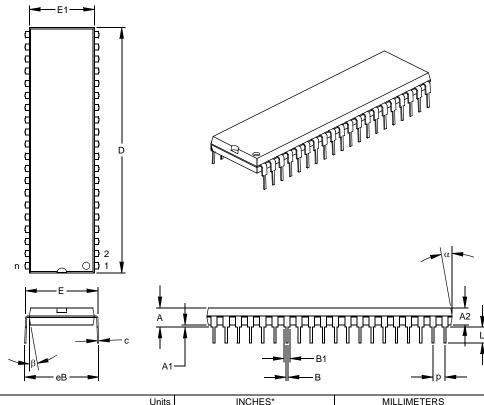

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | its INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|-------|-------------|-------|-------|-------------|-------|-------|

| Dimension Limits           |       | MIN         | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n     |             | 40    |       |             | 40    |       |

| Pitch                      | р     |             | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | А     | .160        | .175  | .190  | 4.06        | 4.45  | 4.83  |

| Molded Package Thickness   | A2    | .140        | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Base to Seating Plane      | A1    | .015        |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е     | .595        | .600  | .625  | 15.11       | 15.24 | 15.88 |

| Molded Package Width       | E1    | .530        | .545  | .560  | 13.46       | 13.84 | 14.22 |

| Overall Length             | D     | 2.045       | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |

| Tip to Seating Plane       | L     | .120        | .130  | .135  | 3.05        | 3.30  | 3.43  |

| Lead Thickness             | С     | .008        | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1    | .030        | .050  | .070  | 0.76        | 1.27  | 1.78  |

| Lower Lead Width           | В     | .014        | .018  | .022  | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eB    | .620        | .650  | .680  | 15.75       | 16.51 | 17.27 |

| Mold Draft Angle Top       | α     | 5           | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β     | 5           | 10    | 15    | 5           | 10    | 15    |

| * 0 / 11' D /              |       |             |       |       |             |       |       |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016