Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf876t-04-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FI | GU | IRF | 2-3      | - |

|----|----|-----|----------|---|

|    |    |     | <u> </u> |   |

#### PIC16F877/876 REGISTER FILE MAP

| Indirect addr.(*)              | 00h        | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 18              |

|--------------------------------|------------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----------------|

| TMR0                           | 01h        | OPTION_REG                                 | 81h        | TMR0                                       | 101h         | OPTION_REG                                 | 18              |

| PCL                            | 02h        | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182             |

| STATUS                         | 03h        | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183             |

| FSR                            | 04h        | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184             |

| PORTA                          | 05h        | TRISA                                      | 85h        |                                            | 105h         |                                            | 18              |

| PORTB                          | 06h        | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186             |

| PORTC                          | 07h        | TRISC                                      | 87h        |                                            | 107h         |                                            | 187             |

| PORTD <sup>(1)</sup>           | 08h        | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188             |

| PORTE <sup>(1)</sup>           | 09h        | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h         |                                            | 189             |

| PCLATH                         | 0Ah        | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18/             |

| INTCON                         | 0Bh        | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18              |

| PIR1                           | 0Ch        | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch         | EECON1                                     | 180             |

| PIR2                           | 0Dh        | PIE2                                       | 8Dh        | EEADR                                      | 10Dh         | EECON2                                     | 181             |

| TMR1L                          | 0Eh        | PCON                                       | 8Eh        | EEDATH                                     | 10Eh         | Reserved <sup>(2)</sup>                    | 18              |

| TMR1H                          | 0Fh        |                                            | 8Fh        | EEADRH                                     | 10Fh         | Reserved <sup>(2)</sup>                    | 18              |

| T1CON                          | 10h        |                                            | 90h        |                                            | 110h         |                                            | 190             |

| TMR2                           | 11h        | SSPCON2                                    | 91h        |                                            | 111h         |                                            | 19 <sup>.</sup> |

| T2CON                          | 12h        | PR2                                        | 92h        |                                            | 112h         |                                            | 192             |

| SSPBUF                         | 13h        | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193             |

| SSPCON                         | 14h        | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194             |

| CCPR1L                         | 15h        |                                            | 95h        |                                            | 115h         |                                            | 19              |

| CCPR1H                         | 16h        |                                            | 96h        |                                            | 116h         |                                            | 196             |

| CCP1CON                        | 17h        |                                            | 97h        | General                                    | 117h         | General                                    | 197             |

| RCSTA                          | 18h        | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198             |

| TXREG                          | 19h        | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199             |

| RCREG                          | 1Ah        |                                            | 9Ah        | -                                          | 11Ah         |                                            | 19/             |

| CCPR2L                         | 1Bh        |                                            | 9Bh        |                                            | 11Bh         |                                            | 198             |

| CCPR2H                         | 1Ch        |                                            | 9Ch        |                                            | 11Ch         |                                            | 190             |

| CCP2CON                        | 1Dh        |                                            | 9Dh        |                                            | 11Dh         |                                            | 19[             |

| ADRESH                         | 1Eh        | ADRESL                                     | 9Eh        |                                            | 11Eh         |                                            | 19              |

| ADCON0                         | 1Fh        | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 191             |

|                                | 20h        |                                            | A0h        |                                            | 120h         |                                            | 1A              |

| General<br>Purpose<br>Register |            | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |                 |

| 96 Bytes                       |            | UU Dyico                                   | EFh        | 00 Dytos                                   | 16Fh         | UU Dyi00                                   | 1EI             |

|                                | 7Fh        | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | 1F(<br>1Fl      |

| Bank 0                         |            | Bank 1                                     | FFII       | Bank 2                                     | <i>.</i>     | Bank 3                                     | 11.1            |

| 1 1 m 1 m 1                    | بارار منعم | a memory location                          | a          |                                            |              |                                            |                 |

2: These registers are reserved, maintain these registers clear.

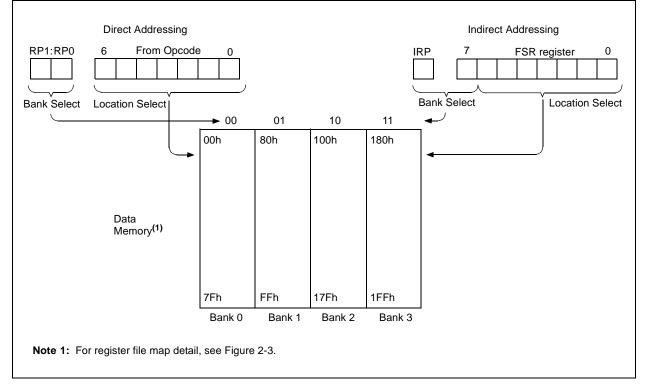

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 3-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     |       | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     | _     | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  |       | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000                  | 0-0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.

Write operations have two control bits, WR and WREN, and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased, followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The desired memory location pointed to by EEADRH:EEADR will be erased. Then, the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the PIC16F87X device has been reset during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location, if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset, or WDT Timeout Reset, during normal operation.

|         | R/W-x                                | U-0                           | U-0                     | U-0          | R/W-x             | R/W-0        | R/S-0         | R/S-0      |

|---------|--------------------------------------|-------------------------------|-------------------------|--------------|-------------------|--------------|---------------|------------|

|         | EEPGD                                | —                             |                         | _            | WRERR             | WREN         | WR            | RD         |

|         | bit 7                                |                               |                         |              |                   |              |               | bit 0      |

|         |                                      |                               |                         |              |                   |              |               |            |

| bit 7   | EEPGD: PI                            | rogram/Data                   | a EEPROM                | Select bit   |                   |              |               |            |

|         |                                      | es program                    |                         |              |                   |              |               |            |

|         |                                      | es data me                    |                         | a read or w  | rite operation is | in progres   | s)            |            |

| bit 6-4 |                                      | ented: Rea                    |                         |              |                   | in progree   | ,             |            |

| bit 3   | •                                    | EPROM Er                      |                         |              |                   |              |               |            |

|         |                                      |                               | 0                       | ly terminate | d                 |              |               |            |

|         | (any M                               | CLR Reset                     | or any WDT              | Reset duri   | ng normal opera   | ation)       |               |            |

|         | 0 <b>= The wr</b>                    | ite operatior                 | n completed             |              |                   |              |               |            |

| bit 2   | WREN: EE                             | PROM Writ                     | e Enable bi             | t            |                   |              |               |            |

|         |                                      | write cycles                  |                         |              |                   |              |               |            |

|         |                                      | write to the                  | EEPROM                  |              |                   |              |               |            |

| bit 1   | WR: Write                            |                               | · / <del>*</del> · · ·· |              |                   | ., .         | <del>.</del>  |            |

|         |                                      | s a write cyc<br>y be set (no |                         |              | y hardware onc    | e write is o | complete. I   | ne VVR bit |

|         |                                      | ycle to the E                 | ,                       | ,            |                   |              |               |            |

| bit 0   | RD: Read (                           | •                             |                         | ·            |                   |              |               |            |

|         | 1 = Initiates                        | s an EEPRO                    | DM read. (R             | D is cleared | l in hardware. T  | he RD bit    | can only be   | set (not   |

|         | cleared) in software.)               |                               |                         |              |                   |              |               |            |

|         | 0 = Does not initiate an EEPROM read |                               |                         |              |                   |              |               |            |

|         | r                                    |                               |                         |              |                   |              |               |            |

|         | Legend:                              |                               |                         |              |                   |              |               |            |

|         | R = Reada                            | ble bit                       | W = V                   | Vritable bit | U = Unimple       | emented b    | it, read as ' | 0'         |

|         | - n = Value                          | at POR                        | '1' = E                 | Bit is set   | '0' = Bit is c    | leared       | x = Bit is ur | nknown     |

#### **REGISTER 4-1:** EECON1 REGISTER (ADDRESS 18Ch)

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|-------------------------------------|--------------|---------------|---------------|------------|----------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE         | INTE          | RBIE          | TOIF       | INTF     | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF         | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF | 0000 0000                | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | _                                   | _            | _             | —             | —          | _        | CCP2IF | 0                        | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE         | TXIE          | SSPIE         | CCP1IE     | TMR2IE   | TMR1IE | 0000 0000                | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | _                                   | —            | _             | _             | —          | —        | CCP2IE | 0                        | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direct                          | tion Registe | er            |               |            |          |        | 1111 1111                | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister for                         | r the Least  | Significant E | Byte of the 1 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister for                         | r the Most S | Significant B | yte of the 16 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                   | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N | 00 0000                  | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | ompare/F                            | WM Regist    | ter1 (LSB)    |               |            |          |        | XXXX XXXX                | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | ompare/F                            | WM Regist    | ter1 (MSB)    |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |

| 17h                    | CCP1CON | —                    | —                                   | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2     | CCP1M1   | CCP1M0 | 00 0000                  | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |              |               |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | Capture/Compare/PWM Register2 (MSB) |              |               |               |            |          |        |                          | uuuu uuuu                       |

| 1Dh                    | CCP2CON | —                    | —                                   | CCP2X        | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0 | 00 0000                  | 00 0000                         |

$\label{eq:legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.$

Note 1: The PSP is not implemented on the PIC16F873/876; always maintain these bits clear.

NOTES:

#### 9.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP module must be in an IDLE state     |

|-------|---------------------------------------------|

|       | before the RCEN bit is set, or the RCEN bit |

|       | will be disregarded.                        |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high), and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 9.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 9.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

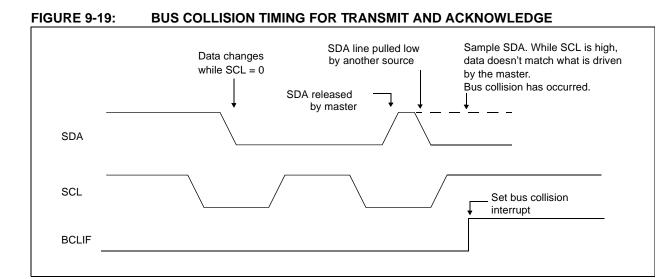

#### 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$ port to its IDLE state (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

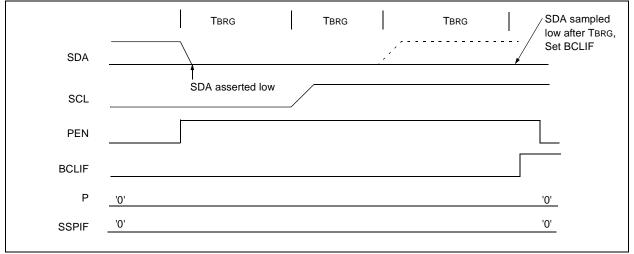

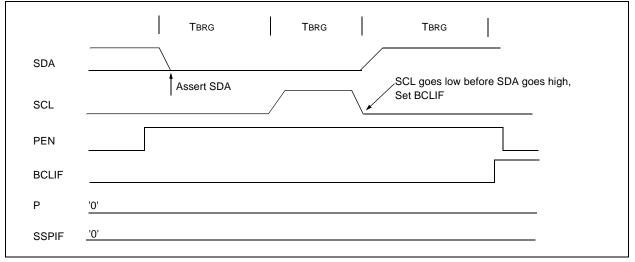

#### 9.2.18.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is a case of another master attempting to drive a data '0' (Figure 9-25).

#### FIGURE 9-25: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 9-26: BUS COLLISION DURING A STOP CONDITION (CASE 2)

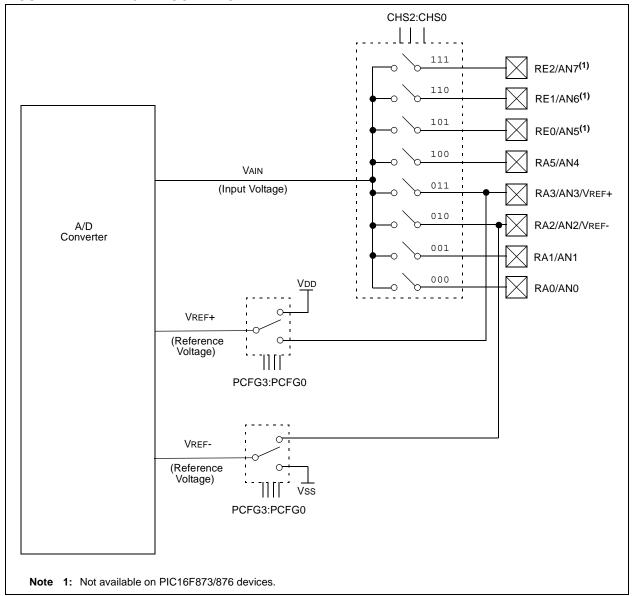

These steps should be followed for doing an A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before the next acquisition starts.

#### FIGURE 11-1: A/D BLOCK DIAGRAM

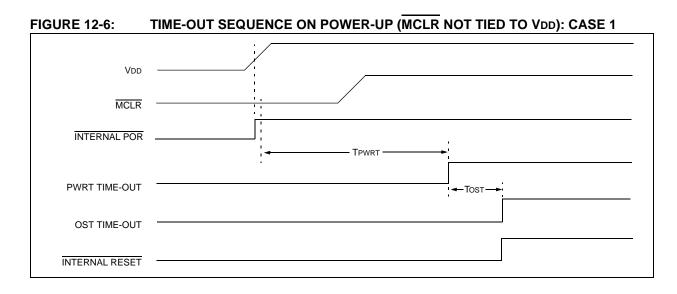

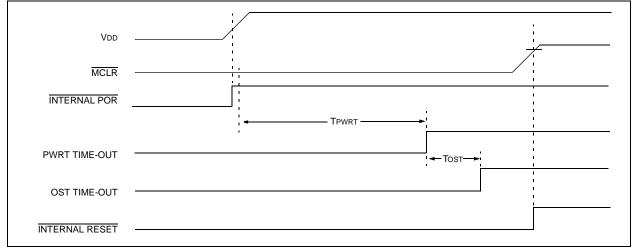

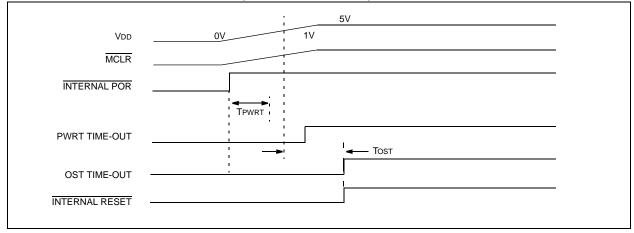

#### FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

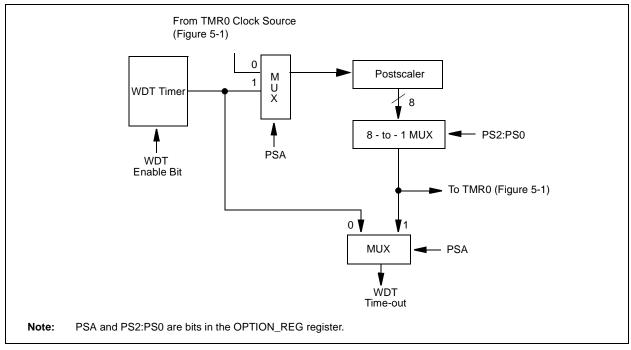

#### 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer. **Note 1:** See Register 12-1 for operation of these bits.

### 13.0 INSTRUCTION SET SUMMARY

Each PIC16F87X instruction is a 14-bit word, divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F87X instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | То                                        | maintain | upward | compatibility | with |  |  |  |  |  |

|-------|-------------------------------------------|----------|--------|---------------|------|--|--|--|--|--|

|       | future PIC16F87X products, do not use the |          |        |               |      |  |  |  |  |  |

|       | OPTION and TRIS instructions.             |          |        |               |      |  |  |  |  |  |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                       |                                                                                       |       |      |            |   |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|------|------------|---|--|--|--|--|

| 13                                                           | 8                                                                                     | 7     | 6    |            | 0 |  |  |  |  |

| OPCODE                                                       |                                                                                       | d     |      | f (FILE #) |   |  |  |  |  |

| d = 1 for dest                                               | d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |       |      |            |   |  |  |  |  |

| Bit-oriented file reg                                        | Bit-oriented file register operations                                                 |       |      |            |   |  |  |  |  |

| 13                                                           | 10                                                                                    | 9     | 7    | 6          | 0 |  |  |  |  |

| OPCODE                                                       |                                                                                       | b (Bl | T #) | f (FILE #) |   |  |  |  |  |

|                                                              | f = 7-bit file register address<br>Literal and control operations<br>General          |       |      |            |   |  |  |  |  |

| 13                                                           |                                                                                       | 8     | 7    |            | 0 |  |  |  |  |

| OPCODE                                                       | OPCODE k (literal)                                                                    |       |      |            |   |  |  |  |  |

| k = 8-bit immediate value<br>CALL and GOTO instructions only |                                                                                       |       |      |            |   |  |  |  |  |

| 13 11                                                        | 10                                                                                    |       |      |            | 0 |  |  |  |  |

| OPCODE k (literal)                                           |                                                                                       |       |      |            |   |  |  |  |  |

| k = 11-bit immediate value                                   |                                                                                       |       |      |            |   |  |  |  |  |

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

#### TABLE 13-2: PIC16F87X INSTRUCTION SET

| Mnemonic,<br>Operands                  |         | Description                                          | Cycles       | 14-Bit Opcode |           |          |           | Status       | Natao   |

|----------------------------------------|---------|------------------------------------------------------|--------------|---------------|-----------|----------|-----------|--------------|---------|

|                                        |         | Description                                          | Cycles       | MSb           |           |          | LSb       | Affected     | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                                      |              |               |           |          |           |              |         |

| ADDWF                                  | f, d    | Add W and f                                          | 1            | 00            | 0111      | dfff     | ffff      | C,DC,Z       | 1,2     |

| ANDWF                                  | f, d    | AND W with f                                         | 1            | 00            | 0101      | dfff     | ffff      | Z            | 1,2     |

| CLRF                                   | f       | Clear f                                              | 1            | 00            | 0001      | lfff     | ffff      | Z            | 2       |

| CLRW                                   | -       | Clear W                                              | 1            | 00            | 0001      | 0xxx     | xxxx      | Z            |         |

| COMF                                   | f, d    | Complement f                                         | 1            | 00            | 1001      | dfff     | ffff      | Z            | 1,2     |

| DECF                                   | f, d    | Decrement f                                          | 1            | 00            | 0011      | dfff     | ffff      | Z            | 1,2     |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                               | 1(2)         | 00            | 1011      | dfff     | ffff      |              | 1,2,3   |

| INCF                                   | f, d    | Increment f                                          | 1            | 00            | 1010      | dfff     | ffff      | Z            | 1,2     |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                               | 1(2)         | 00            | 1111      | dfff     | ffff      |              | 1,2,3   |

| IORWF                                  | f, d    | Inclusive OR W with f                                | 1            | 00            | 0100      | dfff     | ffff      | Z            | 1,2     |

| MOVF                                   | f, d    | Move f                                               | 1            | 00            | 1000      | dfff     | ffff      | Z            | 1,2     |

| MOVWF                                  | f       | Move W to f                                          | 1            | 00            | 0000      | lfff     | ffff      |              |         |

| NOP                                    | -       | No Operation                                         | 1            | 00            | 0000      | 0xx0     | 0000      |              |         |

| RLF                                    | f, d    | Rotate Left f through Carry                          | 1            | 00            | 1101      | dfff     | ffff      | С            | 1,2     |

| RRF                                    | f, d    | Rotate Right f through Carry                         | 1            | 00            | 1100      | dfff     | ffff      | С            | 1,2     |

| SUBWF                                  | f, d    | Subtract W from f                                    | 1            | 00            | 0010      | dfff     | ffff      | C,DC,Z       | 1,2     |

| SWAPF                                  | f, d    | Swap nibbles in f                                    | 1            | 00            | 1110      | dfff     | ffff      |              | 1,2     |

| XORWF                                  | f, d    | Exclusive OR W with f                                | 1            | 00            | 0110      | dfff     | ffff      | Z            | 1,2     |

|                                        |         | BIT-ORIENTED FILE REG                                | ISTER OPER   | RATIO         | NS        |          |           |              |         |

| BCF                                    | f, b    | Bit Clear f                                          | 1            | 01            | 00bb      | bfff     | ffff      |              | 1,2     |

| BSF                                    | f, b    | Bit Set f                                            | 1            | 01            | 01bb      | bfff     | ffff      |              | 1,2     |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                            | 1 (2)        | 01            | 10bb      | bfff     | ffff      |              | 3       |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                              | 1 (2)        | 01            | 11bb      | bfff     | ffff      |              | 3       |

|                                        |         | LITERAL AND CONTR                                    | OL OPERAT    | IONS          |           |          |           |              |         |

| ADDLW                                  | k       | Add literal and W                                    | 1            | 11            | 111x      | kkkk     | kkkk      | C,DC,Z       |         |

| ANDLW                                  | k       | AND literal with W                                   | 1            | 11            | 1001      | kkkk     | kkkk      | Z            |         |

| CALL                                   | k       | Call subroutine                                      | 2            | 10            | 0kkk      | kkkk     | kkkk      |              |         |

| CLRWDT                                 | -       | Clear Watchdog Timer                                 | 1            | 00            | 0000      | 0110     | 0100      | TO,PD        |         |

| GOTO                                   | k       | Go to address                                        | 2            | 10            | 1kkk      | kkkk     | kkkk      |              |         |

| IORLW                                  | k       | Inclusive OR literal with W                          | 1            | 11            | 1000      | kkkk     | kkkk      | Z            |         |

| MOVLW                                  | k       | Move literal to W                                    | 1            | 11            | 00xx      | kkkk     | kkkk      |              |         |

| RETFIE                                 | -       | Return from interrupt                                | 2            | 00            | 0000      | 0000     | 1001      |              |         |

| RETLW                                  | k       | Return with literal in W                             | 2            | 11            | 01xx      | kkkk     | kkkk      |              |         |

| RETURN                                 | -       | Return from Subroutine                               | 2            | 00            | 0000      | 0000     | 1000      |              |         |

| SLEEP                                  | -       | Go into standby mode                                 | 1            | 00            | 0000      | 0110     | 0011      | TO,PD        |         |

| SUBLW                                  | k       | Subtract W from literal                              | 1            | 11            | 110x      | kkkk     | kkkk      | C,DC,Z       |         |

| XORLW                                  | k       | Exclusive OR literal with W                          | 1            | 11            | 1010      | kkkk     | kkkk      | Z            |         |

| Note 1:                                | When an | /O register is modified as a function of itself ( e. | g., MOVF POI | RTB, I        | 1), the v | alue use | ed will b | e that value | present |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

NOTES:

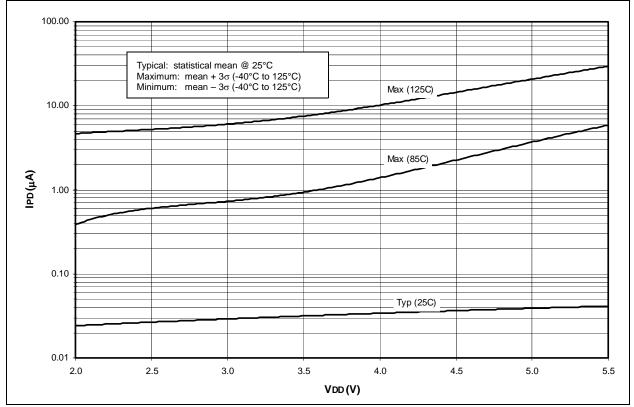

#### 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |      |       |                                            |  |  |  |

|--------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------------------------------------|--|--|--|

| Param<br>No.                                                       | Symbol | Characteristic/<br>Device                                                                                                | Min  | Тур† | Max  | Units | Conditions                                 |  |  |  |

|                                                                    | Vdd    | Supply Voltage                                                                                                           |      |      |      |       |                                            |  |  |  |

| D001                                                               |        |                                                                                                                          | 4.0  | —    | 5.5  | V     | LP, XT, RC osc configuration               |  |  |  |

| D001A                                                              |        |                                                                                                                          | 4.5  |      | 5.5  | V     | HS osc configuration                       |  |  |  |

| D001A                                                              |        |                                                                                                                          | VBOR |      | 5.5  | V     | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |  |  |  |

| D002                                                               | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                             | —    | 1.5  | _    | V     |                                            |  |  |  |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal                                                         | —    | Vss  | _    | V     | See section on Power-on Reset for details  |  |  |  |

| D004                                                               | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal                                                             | 0.05 | —    | —    | V/ms  | See section on Power-on Reset for details  |  |  |  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                                                                               | 3.7  | 4.0  | 4.35 | V     | BODEN bit in configuration word<br>enabled |  |  |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

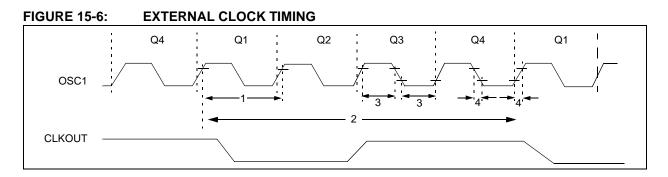

#### TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                     | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|------------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency           | DC  |      | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                           | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                    | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | DC  | —    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency               | DC  |      | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                           | 0.1 | —    | 4      | MHz   | XT osc mode        |

|                  |       |                                    | 4   | —    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                    | 4   | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                    | 5   |      | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period              | 250 |      | _      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                           | 250 | _    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | —      | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μS    | LP osc mode        |

|                  |       | Oscillator Period                  | 250 | _    | —      | ns    | RC osc mode        |

|                  |       | (Note 1)                           | 250 | —    | 10,000 | ns    | XT osc mode        |

|                  |       |                                    | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                    | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                    | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                    | 5   | —    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time<br>(Note 1) | 200 | TCY  | DC     | ns    | Tcy = 4/Fosc       |

| 3                | TosL, | External Clock in (OSC1) High or   | 100 | _    | —      | ns    | XT oscillator      |

|                  | TosH  | Low Time                           | 2.5 | —    | —      | μS    | LP oscillator      |

|                  |       |                                    | 15  | —    | —      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or   | —   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                          | —   | —    | 50     | ns    | LP oscillator      |

|                  |       |                                    | —   | —    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

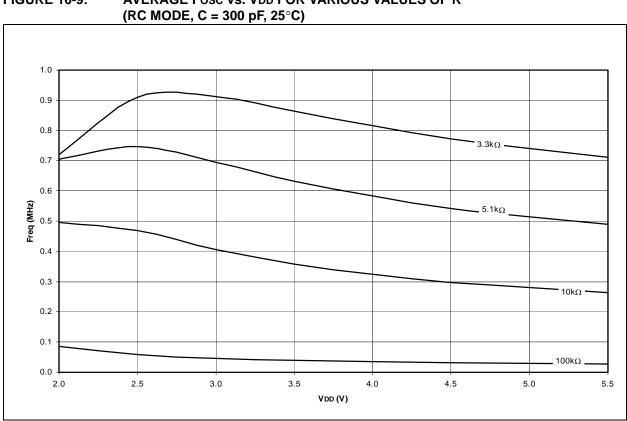

**FIGURE 16-9:** AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R

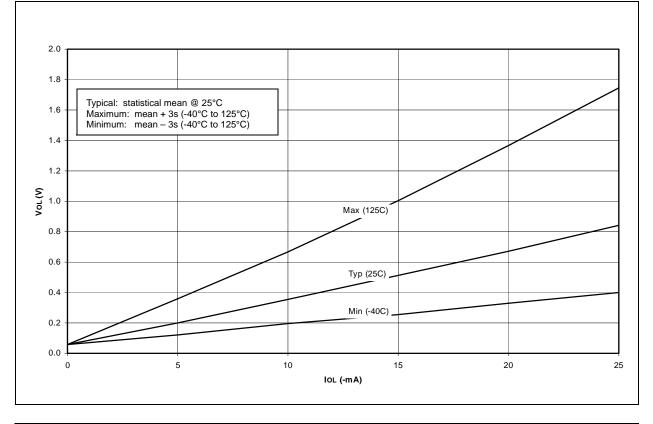

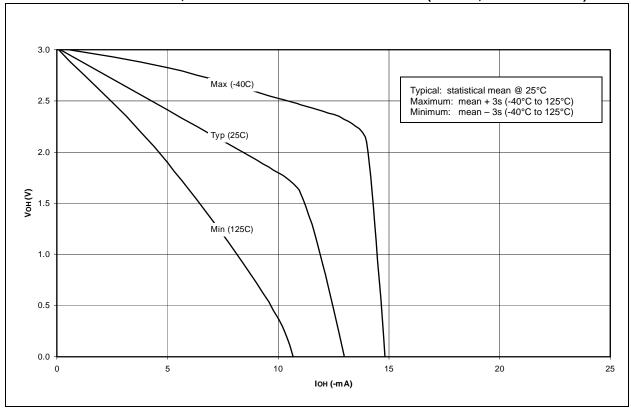

FIGURE 16-17: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD=3V, -40°C TO 125°C)