#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) Since the microcontroller does not execute instructions during the write cycle, the firmware does not necessarily have to check either EEIF, or WR, to determine if the write had finished.

EXAMPLE 4-4: FLASH PROGRAM WRITE

| BSF   | STATUS, RI | P1 ;                         |

|-------|------------|------------------------------|

| BCF   |            | P0 ;Bank 2                   |

| MOVF  | ADDRL, W   | ;Write address               |

| MOVWF | EEADR      | ; of desired                 |

| MOVF  | ADDRH, W   | ;program memory              |

| MOVWF | EEADRH     | ;location                    |

| MOVF  | VALUEL, W  | ;Write value to              |

| MOVWF | EEDATA     | ;program at                  |

| MOVF  | VALUEH, W  | ;desired memory              |

| MOVWF | EEDATH     | ;location                    |

| BSF   | STATUS, R  | P0 ;Bank 3                   |

| BSF   | EECON1, EE | PGD ;Point to Program memory |

| BSF   | EECON1, WI | REN ;Enable writes           |

|       |            | ;Only disable interrupts     |

| BCF   | INTCON, G  | IE ; if already enabled,     |

|       |            | ;otherwise discard           |

| MOVLW | 0x55       | ;Write 55h to                |

| MOVWF | EECON2     | ; EECON2                     |

| MOVLW | 0xAA       | ;Write AAh to                |

| MOVWF | EECON2     | ; EECON2                     |

| BSF   | EECON1, WI | R ;Start write operation     |

| NOP   |            | ;Two NOPs to allow micro     |

| NOP   |            | ;to setup for write          |

|       |            | ;Only enable interrupts      |

| BSF   | INTCON, G  | IE ;if using interrupts,     |

|       |            | ;otherwise discard           |

| BCF   | EECON1, W  | REN ;Disable writes          |

## 4.6 Write Verify

The PIC16F87X devices do not automatically verify the value written during a write operation. Depending on the application, good programming practice may dictate that the value written to memory be verified against the original value. This should be used in applications where excessive writes can stress bits near the specified endurance limits.

## 4.7 Protection Against Spurious Writes

There are conditions when the device may not want to write to the EEPROM data memory or FLASH program memory. To protect against these spurious write conditions, various mechanisms have been built into the PIC16F87X devices. On power-up, the WREN bit is cleared and the Power-up Timer (if enabled) prevents writes.

The write initiate sequence, and the WREN bit together, help prevent any accidental writes during brown-out, power glitches, or firmware malfunction.

## 4.8 Operation While Code Protected

The PIC16F87X devices have two code protect mechanisms, one bit for EEPROM data memory and two bits for FLASH program memory. Data can be read and written to the EEPROM data memory, regardless of the state of the code protection bit, CPD. When code protection is enabled and CPD cleared, external access via ICSP is disabled, regardless of the state of the program memory code protect bits. This prevents the contents of EEPROM data memory from being read out of the device.

The state of the program memory code protect bits, CP0 and CP1, do not affect the execution of instructions out of program memory. The PIC16F87X devices can always read the values in program memory, regardless of the state of the code protect bits. However, the state of the code protect bits and the WRT bit will have different effects on writing to program memory. Table 4-1 shows the effect of the code protect bits and the WRT bit on program memory.

Once code protection has been enabled for either EEPROM data memory or FLASH program memory, only a full erase of the entire device will disable code protection.

## 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

## 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                      | Bit 5        | Bit 4         | Bit 3         | Bit 2     | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------------------------------------------------------------------------|--------------|---------------|---------------|-----------|--------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                                                                       | TOIE         | INTE          | RBIE          | T0IF      | INTF   | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                       | RCIF         | TXIF          | SSPIF         | CCP1IF    | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                       | RCIE         | TXIE          | SSPIE         | CCP1IE    | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            | egister for th                                                             | ne Least Sig | nificant Byte | of the 16-bit | TMR1 Regi | ster   |           | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H  | Holding R            | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |              |               |               |           |        | xxxx xxxx | uuuu uuuu                |                                 |

| 10h                    | T1CON  | —                    | —                                                                          | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC    | TMR1CS | TMR10N    | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

|       | R/W-0                  | R/W-0                                                                                                                                                                                                 | R/W-0                       | R/W-0                      | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |

|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|-------------------------|---------------|---------------|-------------|

|       | GCEN                   | ACKSTAT                                                                                                                                                                                               | ACKDT                       | ACKEN                      | RCEN                    | PEN           | RSEN          | SEN         |

|       | bit 7                  |                                                                                                                                                                                                       |                             |                            |                         |               |               | bit 0       |

| bit 7 | 1 = Enable             | <b>GCEN</b> : General Call Enable bit (In I <sup>2</sup> C Slave mode only)<br>1 = Enable interrupt when a general call address (0000h) is received in the SSPSR<br>0 = General call address disabled |                             |                            |                         |               |               |             |

| bit 6 | ACKSTAT                | Acknowledg                                                                                                                                                                                            | e Status bit                | (In I <sup>2</sup> C Maste | er mode onl             | у)            |               |             |

|       | 1 = Acknow             | <u>Transmit mod</u><br>wledge was n<br>wledge was re                                                                                                                                                  | ot received                 |                            |                         |               |               |             |

| bit 5 | ACKDT: A               | cknowledge [                                                                                                                                                                                          | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m    | ode only)               |               |               |             |

|       | Value that end of a re | knowledge                                                                                                                                                                                             |                             | the user initi             | ates an Ack             | nowledge s    | equence at    | the         |

| bit 4 | ACKEN: A               | cknowledge \$                                                                                                                                                                                         | Sequence E                  | nable bit (In              | I <sup>2</sup> C Master | mode only)    |               |             |

|       | 1 = Initiate<br>Autom  | Receive mode<br>Acknowledge<br>atically cleare<br>wledge seque                                                                                                                                        | e sequence<br>ed by hardw   |                            | I SCL pins a            | and transmit  | ACKDT da      | ta bit.     |

| bit 3 | RCEN: Re               | ceive Enable<br>es Receive mo                                                                                                                                                                         | bit (In I <sup>2</sup> C M  | laster mode                | only)                   |               |               |             |

| bit 2 | PEN: STC               | P Condition I                                                                                                                                                                                         | Enable bit (I               | n I <sup>2</sup> C Master  | r mode only             | )             |               |             |

|       | 1 = Initiate           | ase Control:<br>STOP condit<br>condition idle                                                                                                                                                         |                             | and SCL pir                | ns. Automat             | ically cleare | d by hardwa   | are.        |

| bit 1 | 1 = Initiate           | epeated STAR<br>Repeated ST/<br>ted START co                                                                                                                                                          | ART conditic                | on on SDA an               |                         |               |               | / hardware. |

| bit 0 | 1 = Initiate           | RT Condition<br>START cond<br>condition idl                                                                                                                                                           | lition on SD/               |                            |                         |               | ed by hardv   | vare.       |

|       |                        | For bits ACK<br>mode, this bit<br>writes to the \$                                                                                                                                                    | may not be                  | set (no spo                |                         |               |               |             |

|       | Logondi                |                                                                                                                                                                                                       |                             |                            |                         |               |               |             |

|       | Legend:<br>R = Reada   | blo bit                                                                                                                                                                                               | \\/ _ \\/.                  | itable bit                 |                         | plemented k   | hit road as f | 0'          |

|       | K = Keaua              |                                                                                                                                                                                                       | vv = vvi                    |                            | 0 = 0.000               |               | n, reau as    | 0           |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

## 9.2.15 CLOCK ARBITRATION

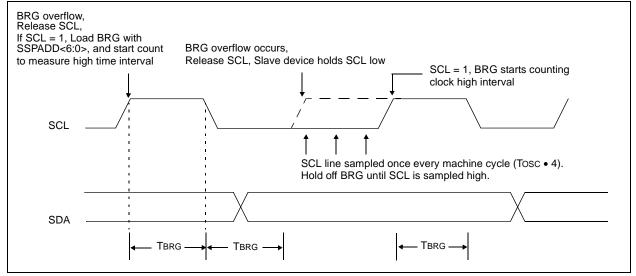

Clock arbitration occurs when the master, during any receive, transmit, or Repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 9-18).

## 9.2.16 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

## 9.2.17 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

#### FIGURE 9-18: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

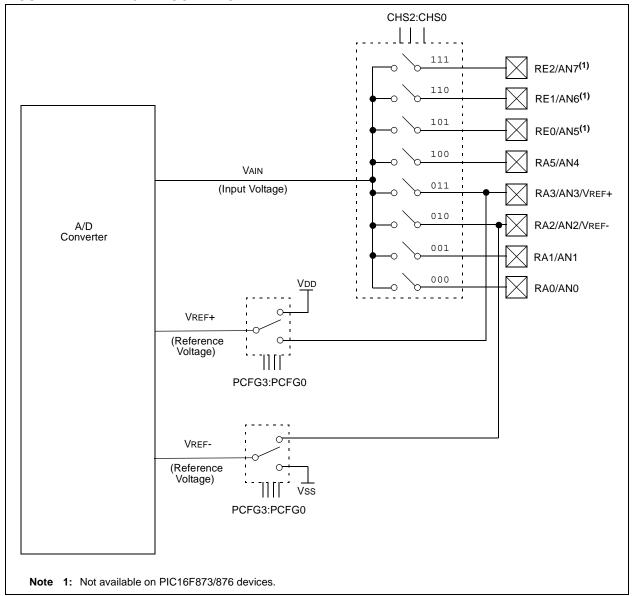

## 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has five inputs for the 28-pin devices and eight for the other devices.

The analog input charges a sample and hold capacitor. The output of the sample and hold capacitor is the input into the converter. The converter then generates a digital result of this analog level via successive approximation. The A/D conversion of the analog input signal results in a corresponding 10-bit digital number. The A/D module has high and low voltage reference input that is software selectable to some combination of VDD, VSS, RA2, or RA3.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D clock must be derived from the A/D's internal RC oscillator. The A/D module has four registers. These registers are:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register0 (ADCON0)

- A/D Control Register1 (ADCON1)

The ADCON0 register, shown in Register 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 11-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be the voltage reference), or as digital I/O.

Additional information on using the A/D module can be found in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

## REGISTER 11-1: ADCON0 REGISTER (ADDRESS: 1Fh)

|         | R/W-0                                                                                                                                                                                                                                                                                                                              | R/W-0         | R/W-0  | R/W-0            | R/W-0 | R/W-0   | U-0 | R/W-0  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|------------------|-------|---------|-----|--------|

|         | ADCS1                                                                                                                                                                                                                                                                                                                              | ADCS0         | CHS2   | CHS1             | CHS0  | GO/DONE | _   | ADON   |

|         | bit 7                                                                                                                                                                                                                                                                                                                              |               |        |                  |       |         |     | bit 0  |

|         |                                                                                                                                                                                                                                                                                                                                    |               |        |                  |       |         |     |        |

| bit 7-6 | ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from the internal A/D module RC oscillator)                                                                                                                                                                 |               |        |                  |       |         |     |        |

| bit 5-3 | CHS2:CHS0: Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)<br>101 = channel 5, (RE0/AN5) <sup>(1)</sup><br>110 = channel 6, (RE1/AN6) <sup>(1)</sup><br>111 = channel 7, (RE2/AN7) <sup>(1)</sup> |               |        |                  |       |         |     |        |

| bit 2   | <ul> <li>GO/DONE: A/D Conversion Status bit</li> <li><u>If ADON = 1:</u></li> <li>1 = A/D conversion in progress (setting this bit starts the A/D conversion)</li> <li>0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)</li> </ul>                           |               |        |                  |       |         |     | he A/D |

| bit 1   | Unimpleme                                                                                                                                                                                                                                                                                                                          | ented: Read a | as '0' |                  |       |         |     |        |

| bit 0   |                                                                                                                                                                                                                                                                                                                                    | verter modul  | •      | g<br>and consume |       |         |     |        |

|         |                                                                                                                                                                                                                                                                                                                                    |               |        | vailable on PIC  | ·     | 0       |     |        |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

These steps should be followed for doing an A/D Conversion:

- 1. Configure the A/D module:

- Configure analog pins/voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts enabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before the next acquisition starts.

## FIGURE 11-1: A/D BLOCK DIAGRAM

## 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next

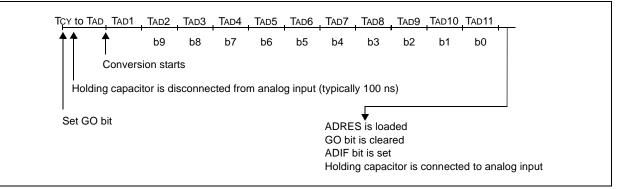

## FIGURE 11-3: A/D CONVERSION TAD CYCLES

acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

## 11.4.1 A/D RESULT REGISTERS

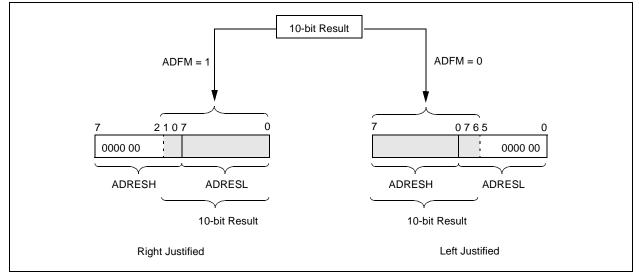

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's'. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

#### FIGURE 11-4: A/D RESULT JUSTIFICATION

## 12.0 SPECIAL FEATURES OF THE CPU

All PIC16F87X devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87X devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the  $PIC^{\mathbb{R}}$  MCU Mid-Range Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

## 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

## 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

## 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

## 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

## 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

## 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present. When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TcY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow PC < 12:11>$                                                                                                                               |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |

| INCF             | Increment f                                                                                                                                                            | IORWF            | Inclusive OR W with f                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                              |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

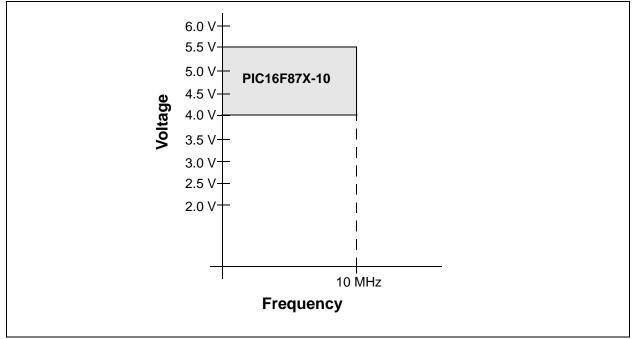

## FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

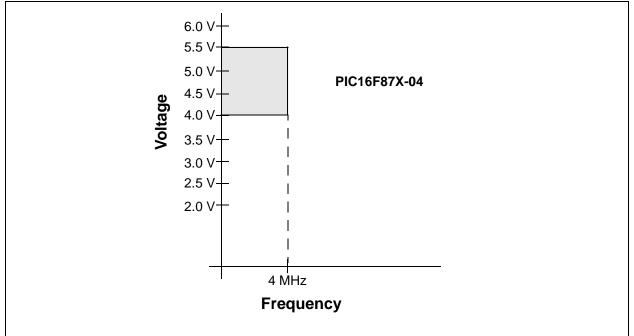

## 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |       |                                            |  |

|--------------------------------------------------------------------|--------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------|--|

| Param<br>No.                                                       | Symbol | Characteristic/<br>Device                                        | Min                                                                                                                      | Тур† | Max  | Units | Conditions                                 |  |

|                                                                    | Vdd    | Supply Voltage                                                   |                                                                                                                          |      |      |       |                                            |  |

| D001                                                               |        |                                                                  | 4.0                                                                                                                      | —    | 5.5  | V     | LP, XT, RC osc configuration               |  |

| D001A                                                              |        |                                                                  | 4.5                                                                                                                      |      | 5.5  | V     | HS osc configuration                       |  |

| D001A                                                              |        |                                                                  | VBOR                                                                                                                     |      | 5.5  | V     | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |  |

| D002                                                               | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                                                                                        | 1.5  | _    | V     |                                            |  |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                        | Vss  | _    | V     | See section on Power-on Reset for details  |  |

| D004                                                               | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                     | —    | —    | V/ms  | See section on Power-on Reset for details  |  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                                                                                      | 4.0  | 4.35 | V     | BODEN bit in configuration word<br>enabled |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

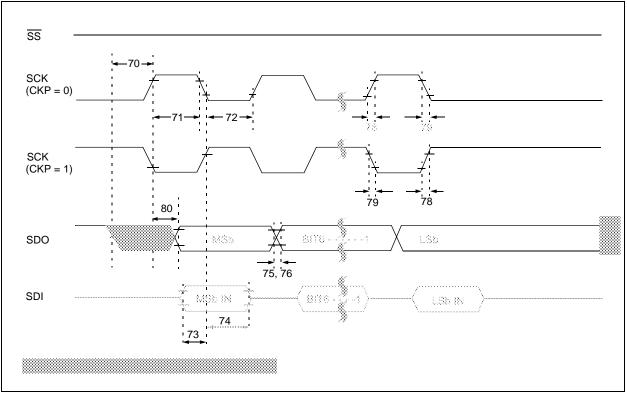

## FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

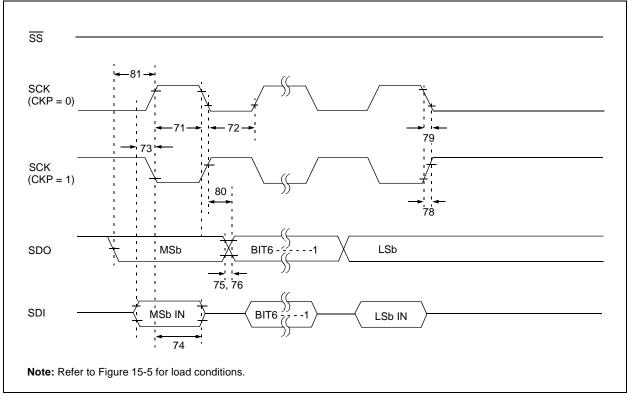

## FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

NOTES:

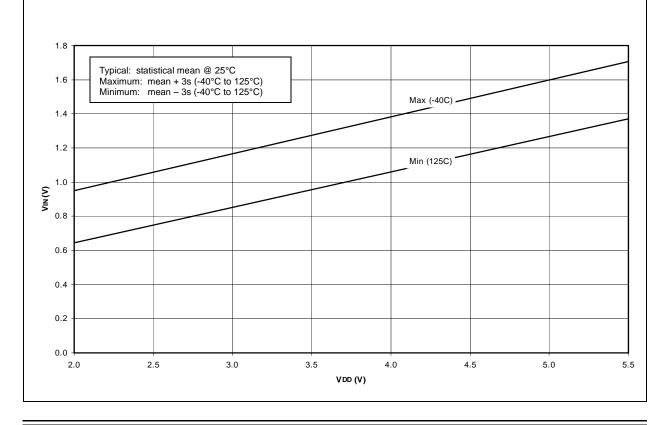

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. Vdd, (TTL INPUT, -40°C TO 125°C)

NOTES:

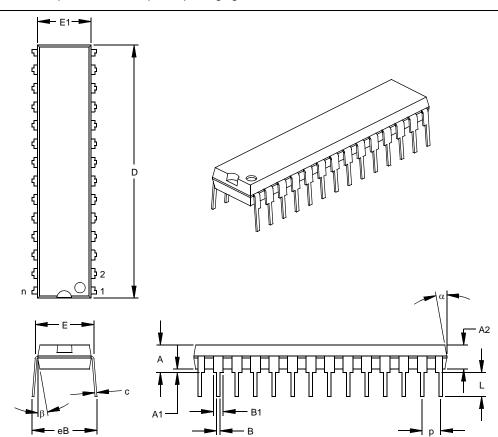

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|------------|---------|-------|-------|-------------|-------|-------|

| Dimens                     | ion Limits | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n          |         | 28    |       |             | 28    |       |

| Pitch                      | р          |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | Α          | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2         | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1         | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | E          | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1         | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D          | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L          | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С          | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1         | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В          | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing        | § eB       | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α          | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β          | 5       | 10    | 15    | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

Notes:

## INDEX

Α

| A/D1                                       | 11  |

|--------------------------------------------|-----|

| Acquisition Requirements1                  |     |

| ADCON0 Register                            |     |

| ADCON1 Register                            |     |

| ADIF bit                                   |     |

| Analog Input Model Block Diagram1          |     |

| Analog Port Pins                           |     |

| Associated Registers and Bits              |     |

| Block Diagram                              |     |

| Calculating Acquisition Time1              |     |

| Configuring Analog Port Pins1              |     |

| Configuring the Interrupt1                 |     |

| Configuring the Module1                    |     |

| Conversion Clock                           |     |

| Conversions1                               |     |

| Delays1                                    |     |

| Effects of a RESET1                        |     |

| GO/DONE bit                                |     |

| Internal Sampling Switch (Rss) Impedence   |     |

| Operation During SLEEP1                    |     |

| Result Registers1                          |     |

| Sampling Requirements1                     |     |

| Source Impedence1                          |     |

| Time Delays1                               |     |

| Absolute Maximum Ratings                   |     |

| ACK                                        |     |

| Acknowledge Data bit                       |     |

| Acknowledge Pulse                          |     |

| Acknowledge Sequence Enable bit            |     |

| Acknowledge Status bit                     |     |

| ADRES Register                             |     |

| Analog Port Pins. See A/D                  | • • |

| Analog-to-Digital Converter. See A/D       |     |

| Application Notes                          |     |

| AN552 (Implementing Wake-up on Key Strokes |     |

| Using PIC16CXXX)                           | 31  |

| AN556 (Implementing a Table Read)          |     |

| AN578 (Use of the SSP Module in the I2C    | 20  |

| Multi-Master Environment)                  | 73  |

| Architecture                               | 10  |

| PIC16F873/PIC16F876 Block Diagram          | 5   |

| PIC16F874/PIC16F877 Block Diagram          |     |

| Assembler                                  | 0   |

| MPASM Assembler1                           | 12  |

|                                            | 40  |

| В                                          |     |

| Banking, Data Memory 12,                   | 18  |

| Baud Rate Generator                        |     |

| BCLIF                                      |     |

| BF74, 82,                                  |     |

| Block Diagrams                             | 57  |

| A/D1                                       | 13  |

| A/D Converter                              |     |

|                                            |     |

Analog Input Model

114

Baud Rate Generator

79

Capture Mode

59

Compare Mode

60

I<sup>2</sup>C Master Mode

78

I<sup>2</sup>C Module

73

I<sup>2</sup>C Slave Mode

73

Interrupt Logic

129

PIC16F873/PIC16F876

5

| PIC16F874/PIC16F877                             | 6        |

|-------------------------------------------------|----------|

| PORTA                                           |          |

| RA3:RA0 and RA5 Pins                            |          |

| RA4/T0CKI Pin                                   | 29       |

| PORTB                                           |          |

| RB3:RB0 Port Pins                               |          |

| RB7:RB4 Port Pins                               | 31       |

| PORTC                                           |          |

| Peripheral Output Override (RC 0:2, 5:7)        |          |

| Peripheral Output Override (RC 3:4)             |          |

| PORTD                                           |          |

| PORTD and PORTE (Parallel Slave Port)           |          |

| PORTE                                           | 36       |

| PWM Mode                                        | 61       |

| RESET Circuit                                   | 123      |

| SSP (I <sup>2</sup> C Mode)                     | 73       |

| SSP (SPI Mode)                                  |          |

| Timer0/WDT Prescaler                            | 47       |

| Timer1                                          | 52       |

| Timer2                                          | 55       |

| USART Asynchronous Receive                      | 101      |

| USART Asynchronous Receive (9-bit Mode)         | 103      |

| USART Transmit                                  | 99       |

| Watchdog Timer                                  | 131      |

| BOR. See Brown-out Reset                        |          |

| BRG                                             | 79       |

| BRGH bit                                        |          |

| Brown-out Reset (BOR) 119, 123, 7               | 125, 126 |

| BOR Status (BOR Bit)                            | 25       |

| Buffer Full bit, BF                             | 74       |

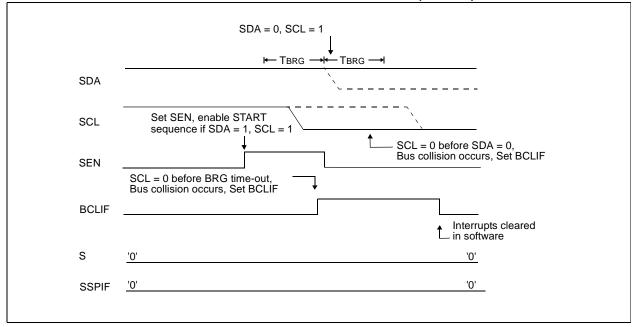

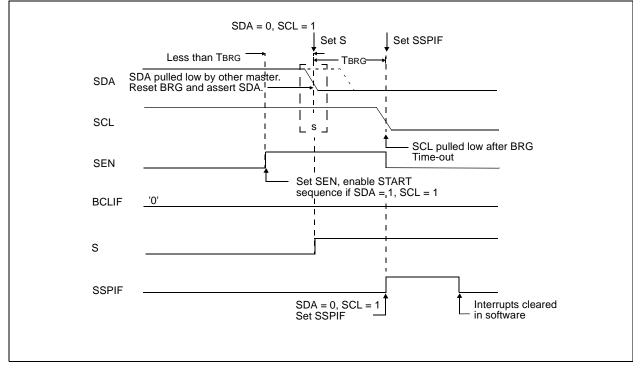

| Bus Arbitration                                 | 89       |

| Bus Collision Section                           | 89       |

| Bus Collision During a Repeated START Condition | 92       |

| Bus Collision During a START Condition          |          |

| Bus Collision During a STOP Condition           | 93       |

| Bus Collision Interrupt Flag bit, BCLIF         | 24       |

|                                                 |          |

## С

| Capture/Compare/PWM (CCP)              | 57   |

|----------------------------------------|------|

| Associated Registers                   |      |

| Capture, Compare and Timer1            | 62   |

| PWM and Timer2                         | 63   |

| Capture Mode                           | 59   |

| Block Diagram                          | 59   |

| CCP1CON Register                       | 58   |

| CCP1IF                                 | 59   |

| Prescaler                              | 59   |

| CCP Timer Resources                    | 57   |

| CCP1                                   |      |

| RC2/CCP1 Pin                           | 7, 9 |

| CCP2                                   |      |

| RC1/T1OSI/CCP2 Pin                     | 7, 9 |

| Compare                                |      |

| Special Trigger Output of CCP1         | 60   |

| Special Trigger Output of CCP2         | 60   |

| Compare Mode                           | 60   |

| Block Diagram                          | 60   |

| Software Interrupt Mode                |      |

| Special Event Trigger                  | 60   |

| Interaction of Two CCP Modules (table) | 57   |

|                                        |      |