Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877-04i-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |

|-------|---------------------------------------------|

|       | and digit borrow bit, respectively, in sub- |

|       | traction. See the SUBLW and SUBWF           |

|       | instructions for examples.                  |

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                            | R/W-0                                                                                                                                                                                                             | R/W-0         | R-1           | R-1                                                      | R/W-x      | R/W-x        | R/W-x |  |  |  |  |  |

|---------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|----------------------------------------------------------|------------|--------------|-------|--|--|--|--|--|

|         | IRP                              | RP1                                                                                                                                                                                                               | RP0           | TO            | PD                                                       | Z          | DC           | С     |  |  |  |  |  |

|         | bit 7                            |                                                                                                                                                                                                                   |               |               |                                                          |            |              | bit 0 |  |  |  |  |  |

|         |                                  |                                                                                                                                                                                                                   |               |               | <i>.</i>                                                 |            |              |       |  |  |  |  |  |

| bit 7   | -                                |                                                                                                                                                                                                                   | -             | d for indire  | ct addressing)                                           |            |              |       |  |  |  |  |  |

|         |                                  | 1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)                                                                                                                                                          |               |               |                                                          |            |              |       |  |  |  |  |  |

| bit 6-5 | RP1:RP0                          | : Register Ba                                                                                                                                                                                                     | nk Select bi  | its (used for | direct addressi                                          | ng)        |              |       |  |  |  |  |  |

|         | 10 = Ban<br>01 = Ban<br>00 = Ban | <b>RP1:RP0</b> : Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes |               |               |                                                          |            |              |       |  |  |  |  |  |

| bit 4   | <b>TO</b> : Time                 | -out bit                                                                                                                                                                                                          |               |               |                                                          |            |              |       |  |  |  |  |  |

|         |                                  | power-up, CL<br>T time-out o                                                                                                                                                                                      |               | iction, or SI | EEP instruction                                          |            |              |       |  |  |  |  |  |

| bit 3   | PD: Powe                         | er-down bit                                                                                                                                                                                                       |               |               |                                                          |            |              |       |  |  |  |  |  |

|         |                                  | power-up or l<br>ecution of the                                                                                                                                                                                   |               |               | on                                                       |            |              |       |  |  |  |  |  |

| bit 2   | Z: Zero bi                       | it                                                                                                                                                                                                                |               |               |                                                          |            |              |       |  |  |  |  |  |

|         |                                  | esult of an ar<br>esult of an ar                                                                                                                                                                                  |               |               | on is zero<br>on is not zero                             |            |              |       |  |  |  |  |  |

| bit 1   | DC: Digit                        | carry/borrow                                                                                                                                                                                                      | bit (ADDWF,   | ADDLW, SU     | BLW, SUBWF ins                                           | tructions) |              |       |  |  |  |  |  |

|         | (for borro                       | w, the polarity                                                                                                                                                                                                   | / is reversed | d)            |                                                          |            |              |       |  |  |  |  |  |

|         |                                  | ry-out from th<br>arry-out from t                                                                                                                                                                                 |               |               | e result occurre<br>the result                           | d          |              |       |  |  |  |  |  |

| bit 0   | C: Carry/                        | borrow bit (AI                                                                                                                                                                                                    | DDWF, ADDLI   | W,SUBLW,S     | UBWF instruction                                         | ons)       |              |       |  |  |  |  |  |

|         |                                  | •                                                                                                                                                                                                                 | •             |               | f the result occu<br>of the result occ                   |            |              |       |  |  |  |  |  |

|         | Note:                            | complemer                                                                                                                                                                                                         | nt of the sec | ond operar    | d. A subtraction<br>d. For rotate (R<br>order bit of the | rf, rlf)   | instructions |       |  |  |  |  |  |

|         | Legend:                          |                                                                                                                                                                                                                   |               |               |                                                          |            |              |       |  |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                      | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|--|--|--|

|               | GIE                                                                                        | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |  |  |  |

|               | bit 7                                                                                      |                               |               |              |                  |             |                | bit 0      |  |  |  |  |  |

|               |                                                                                            |                               |               |              |                  |             |                |            |  |  |  |  |  |

| bit 7         | GIE: Globa                                                                                 | al Interrupt E                | nable bit     |              |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            | s all unmas                   |               | ots          |                  |             |                |            |  |  |  |  |  |

| <b>h</b> :+ C | <ul> <li>Disables all interrupts</li> <li>PEIE: Peripheral Interrupt Enable bit</li> </ul> |                               |               |              |                  |             |                |            |  |  |  |  |  |

| bit 6         | -                                                                                          |                               | •             |              | -                |             |                |            |  |  |  |  |  |

|               |                                                                                            | s all unmas                   |               | •            | 5                |             |                |            |  |  |  |  |  |

| bit 5         |                                                                                            | 0 Overflow                    | =             |              |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            | s the TMR0                    |               |              |                  |             |                |            |  |  |  |  |  |

|               | 0 = Disable                                                                                | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |  |  |  |

| bit 4         |                                                                                            | /INT Externa                  | •             |              |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |  |  |  |

| bit 3         |                                                                                            | Port Change                   |               | •            |                  |             |                |            |  |  |  |  |  |

| bit 0         |                                                                                            | s the RB po                   | •             |              |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            | es the RB po                  |               |              |                  |             |                |            |  |  |  |  |  |

| bit 2         | TOIF: TMR                                                                                  | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            |                               |               |              | eared in softwa  | re)         |                |            |  |  |  |  |  |

|               |                                                                                            | register did                  |               |              |                  |             |                |            |  |  |  |  |  |

| bit 1         |                                                                                            | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |  |  |  |

|               |                                                                                            | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |  |  |  |

| bit 0         |                                                                                            | Port Change                   | •             |              |                  |             |                |            |  |  |  |  |  |

|               |                                                                                            | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |  |  |  |

|               |                                                                                            | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |  |  |  |

|               |                                                                                            | be cleared in<br>of the RB7:R | ,             | ve changed   | stato            |             |                |            |  |  |  |  |  |

|               |                                                                                            |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |  |  |  |

|               | Legend:                                                                                    |                               |               |              |                  |             |                |            |  |  |  |  |  |

|               | R = Reada                                                                                  | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |  |  |  |

|               | - n = Value                                                                                |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |  |  |  |

|               |                                                                                            |                               |               |              |                  |             |                | -          |  |  |  |  |  |

#### 2.2.2.4 **PIE1** Register

The PIE1 register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |

|-------|-------------------------------------|

|       | enable any peripheral interrupt.    |

#### PIE1 REGISTER (ADDRESS 8Ch) **REGISTER 2-4:**

|       | R/W-0                    | R/W-0                        | R/W-0          | R/W-0         | R/W-0           | R/W-0  | R/W-0  | R/W-0  |

|-------|--------------------------|------------------------------|----------------|---------------|-----------------|--------|--------|--------|

|       | PSPIE <sup>(1)</sup>     | ADIE                         | RCIE           | TXIE          | SSPIE           | CCP1IE | TMR2IE | TMR1IE |

|       | bit 7                    |                              |                |               |                 |        |        | bit 0  |

|       |                          |                              |                |               |                 |        |        |        |

| bit 7 | PSPIE <sup>(1)</sup> : F | Parallel Slav                | e Port Read    | d/Write Inter | rupt Enable bit |        |        |        |

|       |                          | s the PSP r<br>s the PSP i   |                |               |                 |        |        |        |

| bit 6 | ADIE: A/D                | Converter I                  | nterrupt Ena   | able bit      |                 |        |        |        |

|       |                          | s the A/D co<br>es the A/D c |                |               |                 |        |        |        |

| bit 5 | RCIE: USA                | RT Receive                   | e Interrupt E  | nable bit     |                 |        |        |        |

|       |                          | s the USAR                   |                |               |                 |        |        |        |

|       |                          | es the USAF                  |                |               |                 |        |        |        |

| bit 4 |                          | RT Transmi                   | -              |               |                 |        |        |        |

|       |                          | s the USAR                   |                | •             |                 |        |        |        |

| bit 3 | SSPIE: Syl               | nchronous S                  | Serial Port In | nterrupt Ena  | ıble bit        |        |        |        |

|       | 1 = Enable               | s the SSP i                  | nterrupt       |               |                 |        |        |        |

|       | 0 = Disable              | es the SSP i                 | nterrupt       |               |                 |        |        |        |

| bit 2 |                          | CP1 Interru                  | •              | it            |                 |        |        |        |

|       |                          | s the CCP1                   | •              |               |                 |        |        |        |

|       |                          | es the CCP1                  | •              |               |                 |        |        |        |

| bit 1 |                          | MR2 to PR2                   |                | •             |                 |        |        |        |

|       |                          | s the TMR2<br>es the TMR2    |                | •             |                 |        |        |        |

| bit 0 |                          |                              |                |               | L               |        |        |        |

|       |                          | MR1 Overfless the TMR1       | -              |               |                 |        |        |        |

|       |                          | es the TMR1                  |                | •             |                 |        |        |        |

|       |                          |                              |                |               |                 |        |        |        |

Note 1: PSPIE is reserved on PIC16F873/876 devices; always maintain this bit clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**REGISTER 5-1: OPTION REG REGISTER**

DANA

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|               | R/W-1                                                                                                                                                     | R/W-1                                                                                                                                      | R/W-1                                                                     | R/W-1        | R/W-1                                                 | R/W-1      | R/W-1                     | R/W-1                  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------|-------------------------------------------------------|------------|---------------------------|------------------------|--|--|--|--|--|

|               | RBPU                                                                                                                                                      | INTEDG                                                                                                                                     | T0CS                                                                      | TOSE         | PSA                                                   | PS2        | PS1                       | PS0                    |  |  |  |  |  |

|               | bit 7                                                                                                                                                     |                                                                                                                                            |                                                                           |              |                                                       |            |                           | bit 0                  |  |  |  |  |  |

|               |                                                                                                                                                           |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 7         | RBPU                                                                                                                                                      |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 6         | INTEDG                                                                                                                                                    |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 5         | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 4         | <b>TOSE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 3         | 1 = Presca                                                                                                                                                | <ul> <li>Prescaler Assignment bit</li> <li>Prescaler is assigned to the WDT</li> <li>Prescaler is assigned to the Timer0 module</li> </ul> |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| bit 2-0       | PS2:PS0:                                                                                                                                                  | Prescaler Ra                                                                                                                               | ite Select b                                                              | oits         |                                                       |            |                           |                        |  |  |  |  |  |

|               | Bit Value                                                                                                                                                 | TMR0 Rate                                                                                                                                  | WDT Rat                                                                   | e            |                                                       |            |                           |                        |  |  |  |  |  |

|               | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                      | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256                                                                                | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 | -            |                                                       |            |                           |                        |  |  |  |  |  |

|               | Legend:                                                                                                                                                   |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

|               | R = Reada                                                                                                                                                 | able bit                                                                                                                                   | VV = V                                                                    | Vritable bit | U = Unimple                                           | emented b  | it, read as '(            | )'                     |  |  |  |  |  |

|               | - n = Value                                                                                                                                               | e at POR                                                                                                                                   | '1' = E                                                                   | Bit is set   | '0' = Bit is c                                        | leared     | x = Bit is ur             | nknown                 |  |  |  |  |  |

|               |                                                                                                                                                           |                                                                                                                                            |                                                                           |              |                                                       |            |                           |                        |  |  |  |  |  |

| ily Reference | ce Manual (                                                                                                                                               | DS33023) m                                                                                                                                 | ust be exe                                                                | cuted when   | ience shown in<br>changing the pr<br>/DT is disabled. | escaler as | MCU Mid-Ra<br>signment fr | ange Fam-<br>om Timer0 |  |  |  |  |  |

Note:

| TABLE 5-1: | <b>REGISTERS ASSOCIATED WITH TIMER0</b> |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| Address               | Name       | Bit 7  | Bit 6      | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|------------|----------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Module's F | Register | •     |       |       |       |       | XXXX XXXX                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE     | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | T0CS     | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

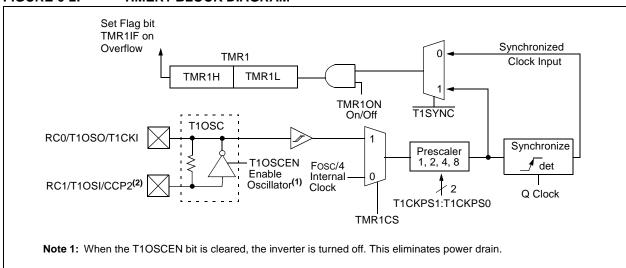

### 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

### 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

#### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

#### FIGURE 6-2: TIMER1 BLOCK DIAGRAM

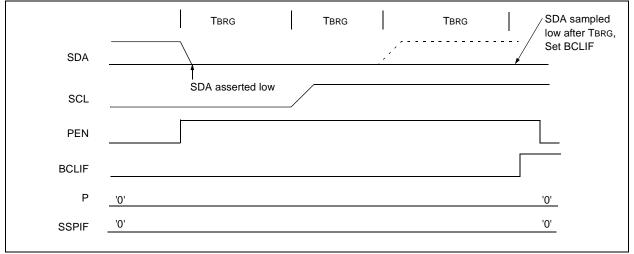

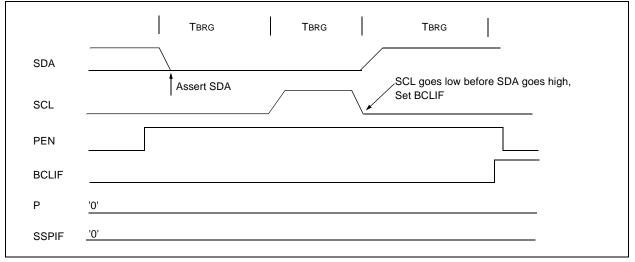

#### 9.2.18.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is a case of another master attempting to drive a data '0' (Figure 9-25).

#### FIGURE 9-25: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 9-26: BUS COLLISION DURING A STOP CONDITION (CASE 2)

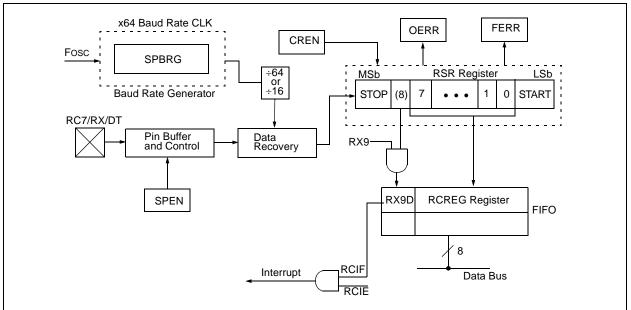

#### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

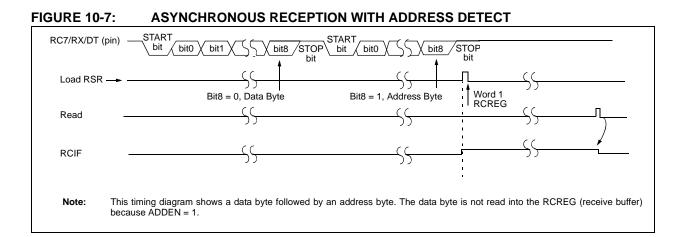

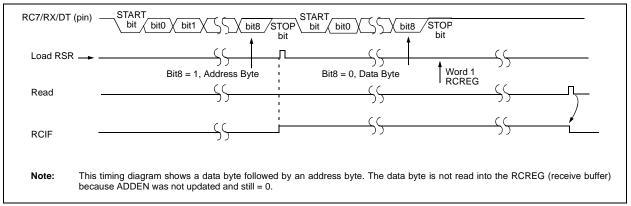

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, and no further data will be received. It is therefore, essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

# FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE       | INTE  | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN       | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART Re             | ceive Re | gister     |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN       | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato | or Registe | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

#### TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6                       | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-----------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                        | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                        | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                         | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr             | ansmit Re                   | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                        | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                         | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | aud Rate Generator Register |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

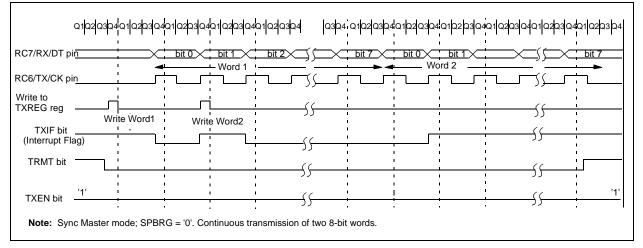

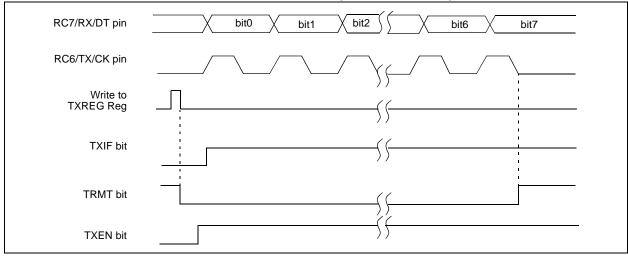

#### FIGURE 10-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 12.2 **Oscillator Configurations**

#### 12.2.1 **OSCILLATOR TYPES**

The PIC16F87X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- Crystal/Resonator • XT

- High Speed Crystal/Resonator HS

- RC Resistor/Capacitor

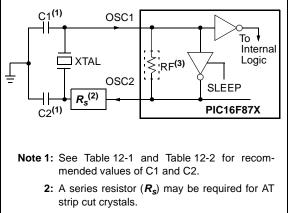

#### 12.2.2 **CRYSTAL OSCILLATOR/CERAMIC** RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F87X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 12-2).

#### **FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION** (HS, XT OR LP **OSC CONFIGURATION)**

3: RF varies with the crystal chosen.

# **EXTERNAL CLOCK INPUT OPERATION (HS, XT OR** LP OSC **CONFIGURATION**) OSC1 Clock from Ext. System PIC16F87X OSC2 Open

#### TABLE 12-1: CERAMIC RESONATORS

|      | Ranges Tested: |             |             |  |  |  |  |  |

|------|----------------|-------------|-------------|--|--|--|--|--|

| Mode | Freq.          | OSC1        | OSC2        |  |  |  |  |  |

| ХТ   | 455 kHz        | 68 - 100 pF | 68 - 100 pF |  |  |  |  |  |

|      | 2.0 MHz        | 15 - 68 pF  | 15 - 68 pF  |  |  |  |  |  |

|      | 4.0 MHz        | 15 - 68 pF  | 15 - 68 pF  |  |  |  |  |  |

| HS   | 8.0 MHz        | 10 - 68 pF  | 10 - 68 pF  |  |  |  |  |  |

|      | 16.0 MHz       | 10 - 22 pF  | 10 - 22 pF  |  |  |  |  |  |

These values are for design guidance only. See notes following Table 12-2.

#### **Resonators Used:**

| 455 kHz                                               | Panasonic EFO-A455K04B | $\pm 0.3\%$ |  |  |  |  |

|-------------------------------------------------------|------------------------|-------------|--|--|--|--|

| 2.0 MHz                                               | Murata Erie CSA2.00MG  | $\pm 0.5\%$ |  |  |  |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG  | $\pm 0.5\%$ |  |  |  |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT  | $\pm 0.5\%$ |  |  |  |  |

| 16.0 MHz                                              | Murata Erie CSA16.00MX | $\pm 0.5\%$ |  |  |  |  |

| All resonators used did not have built-in capacitors. |                        |             |  |  |  |  |

# TABLE 12-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                            |          |  |  |  |  |

|---------------|----------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A      | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz         | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1            | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1            | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C      | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-<br>C | ± 30 PPM |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the startup time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- R<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PIC<sup>®</sup> MCU devices, oscillator performance should be verified.

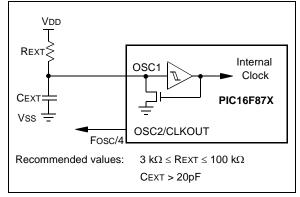

# 12.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F87X.

| Register   |     | Dev | ices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|-----|-----|------|-----|------------------------------------|---------------------------|---------------------------------|

| W          | 873 | 874 | 876  | 877 | XXXX XXXX                          | <u>uuuu</u> uuuu          | uuuu uuuu                       |

| INDF       | 873 | 874 | 876  | 877 | N/A                                | N/A                       | N/A                             |

| TMR0       | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| PCL        | 873 | 874 | 876  | 877 | 0000h                              | 0000h                     | PC + 1 <sup>(2)</sup>           |

| STATUS     | 873 | 874 | 876  | 877 | 0001 1xxx                          | 000q quuu <sup>(3)</sup>  | uuuq quuu <sup>(3)</sup>        |

| FSR        | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTA      | 873 | 874 | 876  | 877 | 0x 0000                            | 0u 0000                   | uu uuuu                         |

| PORTB      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTC      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTD      | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTE      | 873 | 874 | 876  | 877 | xxx                                | uuu                       | uuu                             |

| PCLATH     | 873 | 874 | 876  | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| INTCON     | 873 | 874 | 876  | 877 | x000 0000                          | 0000 000u                 | uuuu uuuu <b>(1)</b>            |

| PIR1       | 873 | 874 | 876  | 877 | r000 0000                          | r000 0000                 | ruuu uuuu <b>(1)</b>            |

|            | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu <b>(1)</b>            |

| PIR2       | 873 | 874 | 876  | 877 | -r-0 00                            | -r-0 00                   | -r-u uu <b>(1)</b>              |

| TMR1L      | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| TMR1H      | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| T1CON      | 873 | 874 | 876  | 877 | 00 0000                            | uu uuuu                   | uu uuuu                         |

| TMR2       | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| T2CON      | 873 | 874 | 876  | 877 | -000 0000                          | -000 0000                 | -uuu uuuu                       |

| SSPBUF     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| SSPCON     | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | սսսս սսսս                       |

| CCPR1L     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| CCPR1H     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP1CON    | 873 | 874 | 876  | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |

| RCSTA      | 873 | 874 | 876  | 877 | x000 0000                          | 0000 000x                 | uuuu uuuu                       |

| TXREG      | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| RCREG      | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| CCPR2L     | 873 | 874 | 876  | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCPR2H     | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP2CON    | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| ADRESH     | 873 | 874 | 876  | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| ADCON0     | 873 | 874 | 876  | 877 | 0000 00-0                          | 0000 00-0                 | uuuu uu-u                       |

| OPTION_REG | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISA      | 873 | 874 | 876  | 877 | 11 1111                            | 11 1111                   | uu uuuu                         |

| TRISB      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISC      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISD      | 873 | 874 | 876  | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISE      | 873 | 874 | 876  | 877 | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |

| PIE1       | 873 | 874 | 876  | 877 | r000 0000                          | r000 0000                 | ruuu uuuu                       |

|            | 873 | 874 | 876  | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

#### TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

# 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |      |       |                                               |  |  |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|-------|-----------------------------------------------|--|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                                  |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                               |  |  |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                                        | Min                                                  | Тур†                                                 | Мах  | Units | Conditions                                    |  |  |

|                                                                                  | Vdd    | Supply Voltage                                                   |                                                      |                                                      |      |       |                                               |  |  |

| D001                                                                             |        | 16LF87X                                                          | 2.0                                                  |                                                      | 5.5  | V     | LP, XT, RC osc configuration<br>(DC to 4 MHz) |  |  |

| D001                                                                             |        | 16F87X                                                           | 4.0                                                  | _                                                    | 5.5  | V     | LP, XT, RC osc configuration                  |  |  |

| D001A                                                                            |        |                                                                  | 4.5                                                  |                                                      | 5.5  | V     | HS osc configuration                          |  |  |

|                                                                                  |        |                                                                  | VBOR                                                 |                                                      | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>     |  |  |

| D002                                                                             | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                    | 1.5                                                  |      | V     |                                               |  |  |

| D003                                                                             | Vpor   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                    | Vss                                                  | _    | V     | See section on Power-on Reset for details     |  |  |

| D004                                                                             | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                 | —                                                    | —    | V/ms  | See section on Power-on Reset for details     |  |  |

| D005                                                                             | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                  | 4.0                                                  | 4.35 | V     | BODEN bit in configuration word<br>enabled    |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHARACTERISTICS |       |                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |         |       |                                                             |  |

|--------------------|-------|-----------------------------------------|------------------------------------------------------|------|---------|-------|-------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                          | Min                                                  | Тур† | Max     | Units | Conditions                                                  |  |

|                    | VIL   | Input Low Voltage                       |                                                      |      |         |       |                                                             |  |

|                    |       | I/O ports                               |                                                      |      |         |       |                                                             |  |

| D030               |       | with TTL buffer                         | Vss                                                  | —    | 0.15Vdd | V     | For entire VDD range                                        |  |

| D030A              |       |                                         | Vss                                                  | —    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                     |  |

| D031               |       | with Schmitt Trigger buffer             | Vss                                                  | —    | 0.2Vdd  | V     |                                                             |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss                                                  | —    | 0.2Vdd  | V     |                                                             |  |

| D033               |       | OSC1 (in XT, HS and LP)                 | Vss                                                  | —    | 0.3Vdd  | V     | (Note 1)                                                    |  |

|                    |       | Ports RC3 and RC4                       |                                                      | —    |         |       |                                                             |  |

| D034               |       | with Schmitt Trigger buffer             | Vss                                                  | —    | 0.3Vdd  | V     | For entire VDD range                                        |  |

| D034A              |       | with SMBus                              | -0.5                                                 | —    | 0.6     | V     | for VDD = $4.5$ to $5.5$ V                                  |  |

|                    | Vih   | Input High Voltage                      |                                                      |      | r       |       | 1                                                           |  |

|                    |       | I/O ports                               |                                                      | —    |         |       |                                                             |  |

| D040               |       | with TTL buffer                         | 2.0                                                  | —    | Vdd     | -     | $4.5V \leq VDD \leq 5.5V$                                   |  |

| D040A              |       |                                         | 0.25VDD<br>+ 0.8V                                    | _    | Vdd     | V     | For entire VDD range                                        |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8Vdd                                               | —    | Vdd     | V     | For entire VDD range                                        |  |

| D042               |       | MCLR                                    | 0.8Vdd                                               | —    | Vdd     | V     |                                                             |  |

| D042A              |       | OSC1 (XT, HS and LP)                    | 0.7Vdd                                               | —    | Vdd     | V     | (Note 1)                                                    |  |

| D043               |       | OSC1 (in RC mode)<br>Ports RC3 and RC4  | 0.9Vdd                                               | —    | Vdd     | V     |                                                             |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7Vdd                                               | —    | Vdd     | V     | For entire VDD range                                        |  |

| D044A              |       | with SMBus                              | 1.4                                                  | —    | 5.5     | V     | for VDD = $4.5$ to $5.5$ V                                  |  |

| D070               | IPURB | PORTB Weak Pull-up Current              | 50                                                   | 250  | 400     | μA    | VDD = 5V, VPIN = VSS,<br>-40°C TO +85°C                     |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                                                      |      |         |       |                                                             |  |

| D060               |       | I/O ports                               | —                                                    | —    | ±1      | μΑ    | $Vss \le VPIN \le VDD,$<br>Pin at hi-impedance              |  |

| D061               |       | MCLR, RA4/T0CKI                         | _                                                    | _    | ±5      | uΑ    | $Vss \leq VPIN \leq VDD$                                    |  |

| D063               |       | OSC1                                    | —                                                    | _    | ±5      | •     | $Vss \le VPIN \le VDD$ , XT, HS<br>and LP osc configuration |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

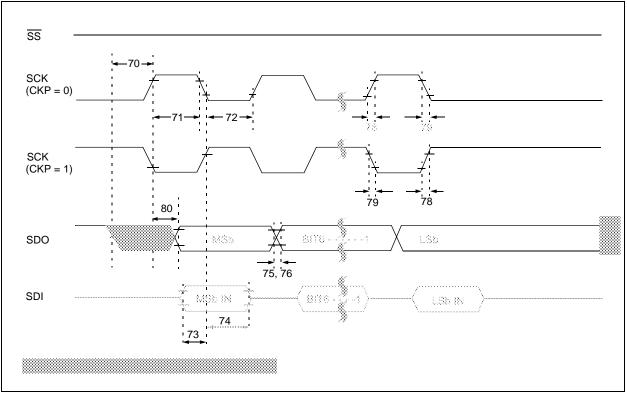

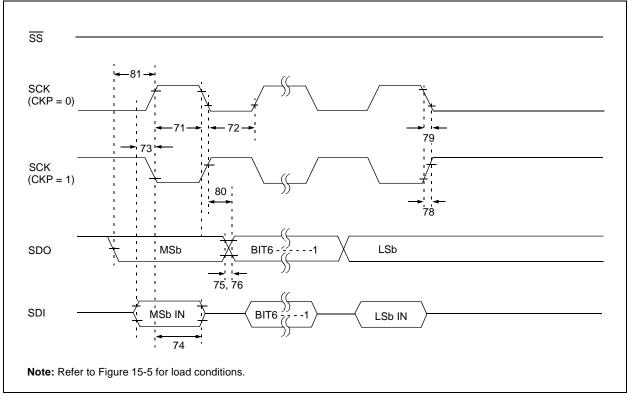

### FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

### FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

| Parameter<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                         |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|--|

| 90               | Tsu:sta | START condition | 100 kHz mode | 4700 | —   | _   | ns    | Only relevant for Repeated         |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | START condition                    |  |

| 91               | Thd:sta | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period, the first clock |  |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       | pulse is generated                 |  |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                    |  |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | _   |       |                                    |  |

| 93               | Thd:sto | STOP condition  | 100 kHz mode | 4000 | _   | —   | ns    |                                    |  |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       |                                    |  |

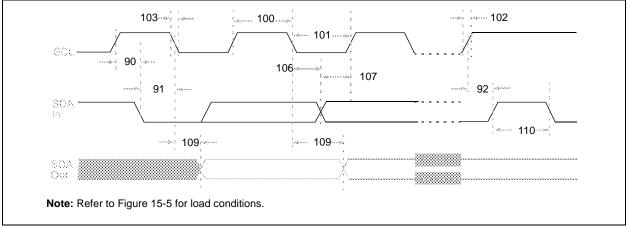

| TABLE 15-8: | I <sup>2</sup> C BUS START/STOP BITS REQUIREMENTS |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

# FIGURE 15-18: I<sup>2</sup>C BUS DATA TIMING

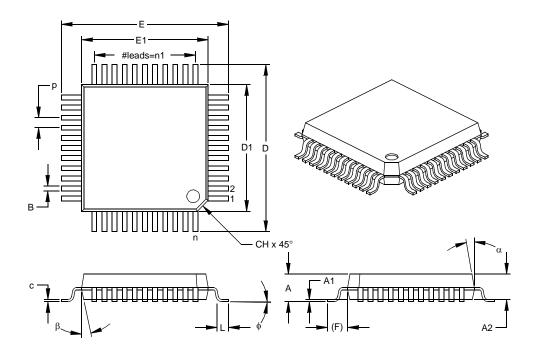

# 44-Lead Plastic Metric Quad Flatpack (PQ) 10x10x2 mm Body, 1.6/0.15 mm Lead Form (MQFP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          |        | INCHES |      | MILLIMETERS* |       |       |       |

|--------------------------|--------|--------|------|--------------|-------|-------|-------|

| Dimensior                | Limits | MIN    | NOM  | MAX          | MIN   | NOM   | MAX   |

| Number of Pins           | n      |        | 44   |              |       | 44    |       |

| Pitch                    | р      |        | .031 |              |       | 0.80  |       |

| Pins per Side            | n1     |        | 11   |              |       | 11    |       |

| Overall Height           | А      | .079   | .086 | .093         | 2.00  | 2.18  | 2.35  |

| Molded Package Thickness | A2     | .077   | .080 | .083         | 1.95  | 2.03  | 2.10  |

| Standoff §               | A1     | .002   | .006 | .010         | 0.05  | 0.15  | 0.25  |

| Foot Length              | L      | .029   | .035 | .041         | 0.73  | 0.88  | 1.03  |

| Footprint (Reference)    | (F)    |        | .063 |              |       | 1.60  |       |

| Foot Angle               | ø      | 0      | 3.5  | 7            | 0     | 3.5   | 7     |

| Overall Width            | E      | .510   | .520 | .530         | 12.95 | 13.20 | 13.45 |

| Overall Length           | D      | .510   | .520 | .530         | 12.95 | 13.20 | 13.45 |

| Molded Package Width     | E1     | .390   | .394 | .398         | 9.90  | 10.00 | 10.10 |

| Molded Package Length    | D1     | .390   | .394 | .398         | 9.90  | 10.00 | 10.10 |

| Lead Thickness           | С      | .005   | .007 | .009         | 0.13  | 0.18  | 0.23  |

| Lead Width               | В      | .012   | .015 | .018         | 0.30  | 0.38  | 0.45  |

| Pin 1 Corner Chamfer     | СН     | .025   | .035 | .045         | 0.64  | 0.89  | 1.14  |

| Mold Draft Angle Top     | α      | 5      | 10   | 15           | 5     | 10    | 15    |

| Mold Draft Angle Bottom  | β      | 5      | 10   | 15           | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-022 Drawing No. C04-071

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|