Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877-04i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | I/O Ports                                                                   |     |

| 4.0   | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0   | Timer0 Module                                                               |     |

| 6.0   | Timer1 Module                                                               |     |

| 7.0   | Timer2 Module                                                               |     |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0  | Special Features of the CPU                                                 | 119 |

| 13.0  | Instruction Set Summary                                                     | 135 |

|       | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 16.0  | DC and AC Characteristics Graphs and Tables                                 | 177 |

| 17.0  | Packaging Information                                                       | 189 |

| Appe  | ndix A: Revision History                                                    | 197 |

| Appe  | ndix B: Device Differences                                                  | 197 |

|       | ndix C: Conversion Considerations                                           |     |

| Index | (                                                                           | 199 |

|       | ine Support                                                                 |     |

| Read  | ler Response                                                                |     |

| PIC1  | 6F87X Product Identification System                                         | 209 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | and digit borrow bit, respectively, in sub- |  |  |  |  |  |  |  |  |  |

|       | traction. See the SUBLW and SUBWF           |  |  |  |  |  |  |  |  |  |

|       | instructions for examples.                  |  |  |  |  |  |  |  |  |  |

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                  | R/W-0        | R-1           | R-1                            | R/W-x      | R/W-x | R/W-x |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|--------------------------------|------------|-------|-------|--|--|--|

|         | IRP                                                                                                                                                                                                                                                      | RP1                                                                                                                                    | RP0          | TO            | PD                             | Z          | DC    | С     |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                    |                                                                                                                                        |              |               |                                |            |       | bit 0 |  |  |  |

|         |                                                                                                                                                                                                                                                          |                                                                                                                                        |              |               | <i>.</i>                       |            |       |       |  |  |  |

| bit 7   | -                                                                                                                                                                                                                                                        |                                                                                                                                        | -            | d for indire  | ct addressing)                 |            |       |       |  |  |  |

|         |                                                                                                                                                                                                                                                          | 2, 3 (100h - <sup>2</sup><br>0, 1 (00h - Fl                                                                                            | ,            |               |                                |            |       |       |  |  |  |

| bit 6-5 | RP1:RP0                                                                                                                                                                                                                                                  | : Register Ba                                                                                                                          | nk Select bi | its (used for | direct addressi                | ng)        |       |       |  |  |  |

|         | 10 = Ban<br>01 = Ban<br>00 = Ban                                                                                                                                                                                                                         | 11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes |              |               |                                |            |       |       |  |  |  |

| bit 4   | <b>TO</b> : Time                                                                                                                                                                                                                                         | -out bit                                                                                                                               |              |               |                                |            |       |       |  |  |  |

|         |                                                                                                                                                                                                                                                          | <ul> <li>1 = After power-up, CLRWDT instruction, or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                  |              |               |                                |            |       |       |  |  |  |

| bit 3   | PD: Powe                                                                                                                                                                                                                                                 | er-down bit                                                                                                                            |              |               |                                |            |       |       |  |  |  |

|         |                                                                                                                                                                                                                                                          | power-up or l<br>ecution of the                                                                                                        |              |               | on                             |            |       |       |  |  |  |

| bit 2   | Z: Zero bi                                                                                                                                                                                                                                               | it                                                                                                                                     |              |               |                                |            |       |       |  |  |  |

|         |                                                                                                                                                                                                                                                          | esult of an ar<br>esult of an ar                                                                                                       |              |               | on is zero<br>on is not zero   |            |       |       |  |  |  |

| bit 1   | DC: Digit                                                                                                                                                                                                                                                | carry/borrow                                                                                                                           | bit (ADDWF,  | ADDLW, SU     | BLW, SUBWF ins                 | tructions) |       |       |  |  |  |

|         | (for borro                                                                                                                                                                                                                                               | (for borrow, the polarity is reversed)                                                                                                 |              |               |                                |            |       |       |  |  |  |

|         |                                                                                                                                                                                                                                                          | ry-out from th<br>arry-out from t                                                                                                      |              |               | e result occurre<br>the result | d          |       |       |  |  |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                                                                                                            |                                                                                                                                        |              |               |                                |            |       |       |  |  |  |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul>                                                                                  |                                                                                                                                        |              |               |                                |            |       |       |  |  |  |

|         | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high, or low order bit of the source register. |                                                                                                                                        |              |               |                                |            |       |       |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                  |                                                                                                                                        |              |               |                                |            |       |       |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

## 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

# 9.2.7 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once Master mode is enabled, the user has six options:

- Assert a START condition on SDA and SCL.

- Assert a Repeated START condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a STOP condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP Module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

#### 9.2.7.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSPBUF. Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

A typical transmit sequence would go as follows:

- a) User generates a START condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) User loads SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) MSSP module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) User loads SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

- MSSP module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) User generates a STOP condition by setting the STOP enable bit, PEN, in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

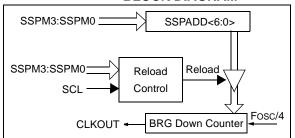

#### 9.2.8 BAUD RATE GENERATOR

In  $I^2C$  Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 9-10). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr), on the Q2 and Q4 clock.

In I<sup>2</sup>C Master mode, the BRG is reloaded automatically. If clock arbitration is taking place, the BRG will be reloaded when the SCL pin is sampled high (Figure 9-11).

Note: Baud Rate = Fosc / (4 \* (SSPADD + 1))

FIGURE 9-10:

#### BAUD RATE GENERATOR BLOCK DIAGRAM

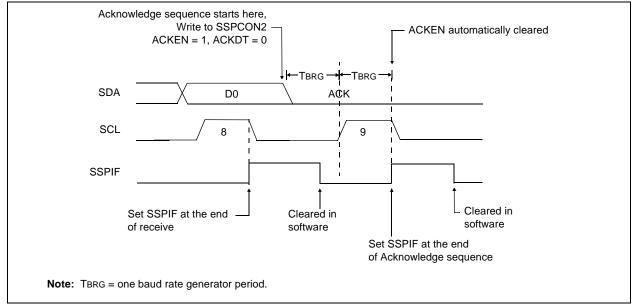

#### 9.2.13 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted high. When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode (Figure 9-16).

#### 9.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-16: ACKNOWLEDGE SEQUENCE WAVEFORM

# PIC16F87X

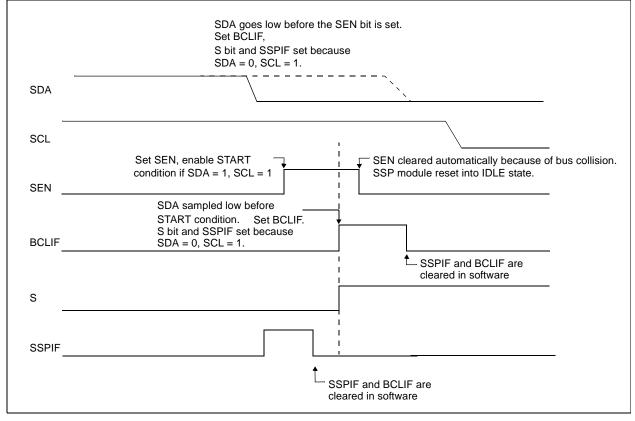

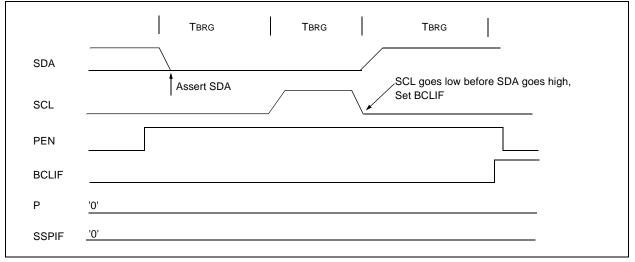

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

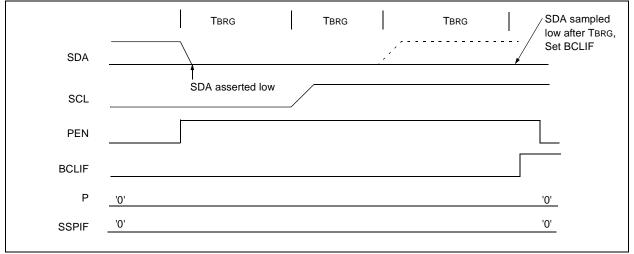

#### 9.2.18.3 Bus Collision During a STOP Condition

Bus collision occurs during a STOP condition if:

- a) After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is a case of another master attempting to drive a data '0' (Figure 9-25).

#### FIGURE 9-25: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 9-26: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

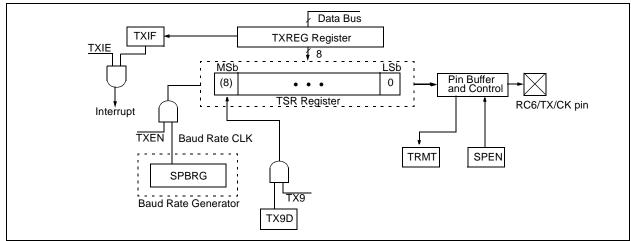

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

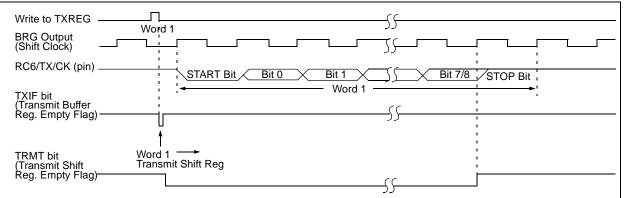

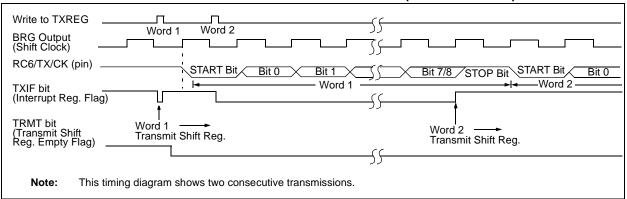

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

When setting up an Asynchronous Transmission, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5       | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|-------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE        | INTE  | RBIE  | T0IF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF        | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN        | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | insmit Re | gister      |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE        | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN        | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  | or Register | •     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock                | AD Clock Source (TAD) |          |  |  |  |  |

|-------------------------|-----------------------|----------|--|--|--|--|

| Operation               | ADCS1:ADCS0           | Max.     |  |  |  |  |

| 2Tosc                   | 0 0                   | 1.25 MHz |  |  |  |  |

| 8Tosc                   | 01                    | 5 MHz    |  |  |  |  |

| 32Tosc                  | 10                    | 20 MHz   |  |  |  |  |

| RC <sup>(1, 2, 3)</sup> | 11                    | (Note 1) |  |  |  |  |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s, but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 15.1 and 15.2).

# 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

| Note | 1: When reading the port register, any pin   |

|------|----------------------------------------------|

|      | configured as an analog input channel will   |

|      | read as cleared (a low level). Pins config-  |

|      | ured as digital inputs will convert an ana-  |

|      | log input. Analog levels on a digitally      |

|      | configured input will not affect the conver- |

|      | sion accuracy.                               |

2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1              | CP0 | DEBUG                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                   | WRT     | CPD       | LVP      | BODEN                                      | CP1     | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|----------|--------------------------------------------|---------|-----|-------|------|-------|-------|

| bit13<br>bit 13- | 12, | CP1:CP0: FLASH Program Memory Code Protection bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                     |         |           |          |                                            |         |     |       |      |       | bit0  |

| bit 5-4          |     | <ul> <li>11 = Code protection off</li> <li>10 = 1F00h to 1FFFh code protected (PIC16F877, 876)</li> <li>10 = 0F00h to 0FFFh code protected (PIC16F874, 873)</li> <li>01 = 1000h to 1FFFh code protected (PIC16F877, 876)</li> <li>01 = 0800h to 0FFFh code protected (PIC16F874, 873)</li> <li>00 = 0000h to 1FFFh code protected (PIC16F877, 876)</li> <li>00 = 0000h to 0FFFh code protected (PIC16F874, 873)</li> </ul> |                                                                                                                                                                                                     |         |           |          |                                            |         |     |       |      |       |       |

| bit 11           |     | 1 = In-Cir                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>DEBUG:</b> In-Circuit Debugger Mode<br>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger. |         |           |          |                                            |         |     |       |      |       |       |

| bit 10           |     | Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                   | nented:                                                                                                                                                                                             | Read as | '1'       |          |                                            |         |     |       |      |       |       |

| bit 9            |     | WRT: FLASH Program Memory Write Enable<br>1 = Unprotected program memory may be written to by EECON control<br>0 = Unprotected program memory may not be written to by EECON control                                                                                                                                                                                                                                       |                                                                                                                                                                                                     |         |           |          |                                            |         |     |       |      |       |       |

| bit 8            |     | <b>CPD:</b> Dat<br>1 = Code<br>0 = Data I                                                                                                                                                                                                                                                                                                                                                                                  | protectio                                                                                                                                                                                           | on off  |           |          | ł                                          |         |     |       |      |       |       |

| bit 7            |     | 1 = RB3/F                                                                                                                                                                                                                                                                                                                                                                                                                  | PGM pin                                                                                                                                                                                             | has PGN | 1 functio | n, low v | iming Enabl<br>oltage prog<br>e used for p | ramming |     | 1     |      |       |       |

| bit 6            |     | 1 = BOR                                                                                                                                                                                                                                                                                                                                                                                                                    | BODEN: Brown-out Reset Enable bit <sup>(3)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                                                                                             |         |           |          |                                            |         |     |       |      |       |       |

| bit 3            |     | 1 = PWR                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(3)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                    |         |           |          |                                            |         |     |       |      |       |       |

| bit 2            |     | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                     |         |           |          |                                            |         |     |       |      |       |       |

| bit 1-0          |     | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (                                                                                                                                                                                                                                                                                                                                                                | oscillator<br>oscillator<br>oscillator                                                                                                                                                              |         | Selectio  | n bits   |                                            |         |     |       |      |       |       |

- **Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

# PIC16F87X

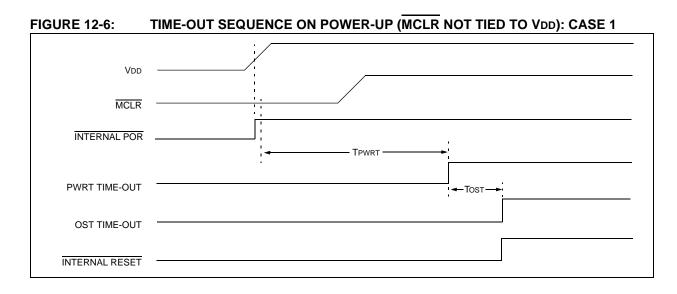

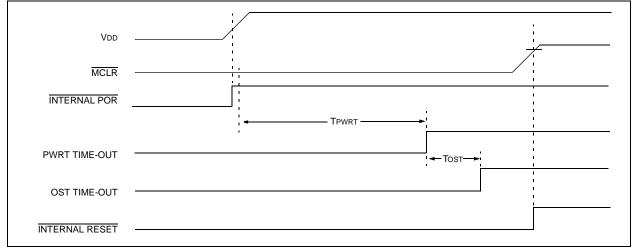

## FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

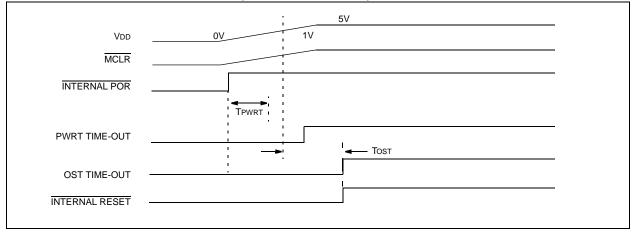

# FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

#### TABLE 13-2: PIC16F87X INSTRUCTION SET

| Mnemonic,<br>Operands                  |         | Description                                          |              | 14-Bit Opcode |           |          |           | Status       | Natao   |

|----------------------------------------|---------|------------------------------------------------------|--------------|---------------|-----------|----------|-----------|--------------|---------|

|                                        |         |                                                      |              | MSb           |           |          | LSb       | Affected     | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                                      |              |               |           |          |           |              |         |

| ADDWF                                  | f, d    | Add W and f                                          | 1            | 00            | 0111      | dfff     | ffff      | C,DC,Z       | 1,2     |

| ANDWF                                  | f, d    | AND W with f                                         | 1            | 00            | 0101      | dfff     | ffff      | Z            | 1,2     |

| CLRF                                   | f       | Clear f                                              | 1            | 00            | 0001      | lfff     | ffff      | Z            | 2       |

| CLRW                                   | -       | Clear W                                              | 1            | 00            | 0001      | 0xxx     | xxxx      | Z            |         |

| COMF                                   | f, d    | Complement f                                         | 1            | 00            | 1001      | dfff     | ffff      | Z            | 1,2     |

| DECF                                   | f, d    | Decrement f                                          | 1            | 00            | 0011      | dfff     | ffff      | Z            | 1,2     |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                               | 1(2)         | 00            | 1011      | dfff     | ffff      |              | 1,2,3   |

| INCF                                   | f, d    | Increment f                                          | 1            | 00            | 1010      | dfff     | ffff      | Z            | 1,2     |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                               | 1(2)         | 00            | 1111      | dfff     | ffff      |              | 1,2,3   |

| IORWF                                  | f, d    | Inclusive OR W with f                                | 1            | 00            | 0100      | dfff     | ffff      | Z            | 1,2     |

| MOVF                                   | f, d    | Move f                                               | 1            | 00            | 1000      | dfff     | ffff      | Z            | 1,2     |

| MOVWF                                  | f       | Move W to f                                          | 1            | 00            | 0000      | lfff     | ffff      |              |         |

| NOP                                    | -       | No Operation                                         | 1            | 00            | 0000      | 0xx0     | 0000      |              |         |

| RLF                                    | f, d    | Rotate Left f through Carry                          | 1            | 00            | 1101      | dfff     | ffff      | С            | 1,2     |

| RRF                                    | f, d    | Rotate Right f through Carry                         | 1            | 00            | 1100      | dfff     | ffff      | С            | 1,2     |

| SUBWF                                  | f, d    | Subtract W from f                                    | 1            | 00            | 0010      | dfff     | ffff      | C,DC,Z       | 1,2     |

| SWAPF                                  | f, d    | Swap nibbles in f                                    | 1            | 00            | 1110      | dfff     | ffff      |              | 1,2     |

| XORWF                                  | f, d    | Exclusive OR W with f                                | 1            | 00            | 0110      | dfff     | ffff      | Z            | 1,2     |

|                                        |         | BIT-ORIENTED FILE REG                                | ISTER OPER   | RATIO         | IS        |          |           |              |         |

| BCF                                    | f, b    | Bit Clear f                                          | 1            | 01            | 00bb      | bfff     | ffff      |              | 1,2     |

| BSF                                    | f, b    | Bit Set f                                            | 1            | 01            | 01bb      | bfff     | ffff      |              | 1,2     |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                            | 1 (2)        | 01            | 10bb      | bfff     | ffff      |              | 3       |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                              | 1 (2)        | 01            | 11bb      | bfff     | ffff      |              | 3       |

|                                        |         | LITERAL AND CONTR                                    | OL OPERAT    | IONS          |           |          |           |              |         |

| ADDLW                                  | k       | Add literal and W                                    | 1            | 11            | 111x      | kkkk     | kkkk      | C,DC,Z       |         |

| ANDLW                                  | k       | AND literal with W                                   | 1            | 11            | 1001      | kkkk     | kkkk      | Z            |         |

| CALL                                   | k       | Call subroutine                                      | 2            | 10            | 0kkk      | kkkk     | kkkk      |              |         |

| CLRWDT                                 | -       | Clear Watchdog Timer                                 | 1            | 00            | 0000      | 0110     | 0100      | TO,PD        |         |

| GOTO                                   | k       | Go to address                                        | 2            | 10            | 1kkk      | kkkk     | kkkk      |              |         |

| IORLW                                  | k       | Inclusive OR literal with W                          | 1            | 11            | 1000      | kkkk     | kkkk      | Z            |         |

| MOVLW                                  | k       | Move literal to W                                    | 1            | 11            | 00xx      | kkkk     | kkkk      |              |         |

| RETFIE                                 | -       | Return from interrupt                                | 2            | 00            | 0000      | 0000     | 1001      |              |         |

| RETLW                                  | k       | Return with literal in W                             | 2            | 11            | 01xx      | kkkk     | kkkk      |              |         |

| RETURN                                 | -       | Return from Subroutine                               | 2            | 00            | 0000      | 0000     | 1000      |              |         |

| SLEEP                                  | -       | Go into standby mode                                 | 1            | 00            | 0000      | 0110     | 0011      | TO,PD        |         |

| SUBLW                                  | k       | Subtract W from literal                              | 1            | 11            | 110x      | kkkk     | kkkk      | C,DC,Z       |         |

| XORLW                                  | k       | Exclusive OR literal with W                          | 1            | 11            | 1010      | kkkk     | kkkk      | Z            |         |

| Note 1:                                | When an | /O register is modified as a function of itself ( e. | g., MOVF POI | RTB,          | 1), the v | alue use | ed will b | e that value | present |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

# 13.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

|------------------|---------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

Bit Clear f

BCF

| ADDWF            | Add W and f                                                                                                                                                                    |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

# 15.0 ELECTRICAL CHARACTERISTICS

| Absolute Maximum Ratings † | Absolute | Maximum | Ratings † |

|----------------------------|----------|---------|-----------|

|----------------------------|----------|---------|-----------|

| Ambient temperature under bias                                                                              |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3 V to (VDD + 0.3 V)             |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5 V                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14 V                         |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +8.5 V                        |

| Total power dissipation (Note 1)                                                                            | 1.0 W                              |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into Vod pin                                                                                | 250 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| <b>2:</b> Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80   | mA <u>, may cause latch-up</u> .   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on PIC16F873/876 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

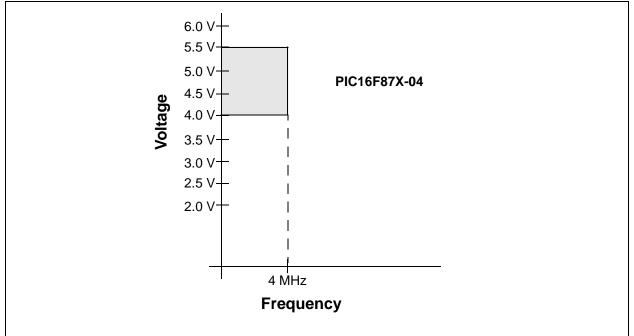

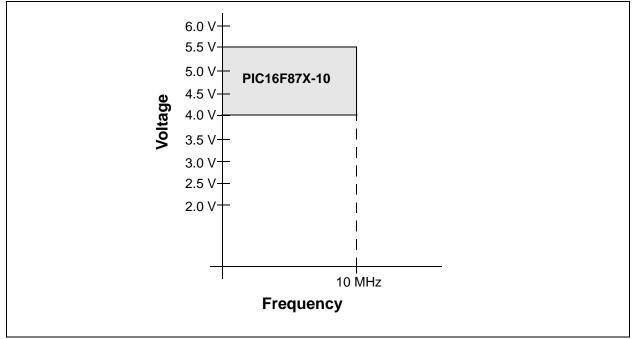

#### FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

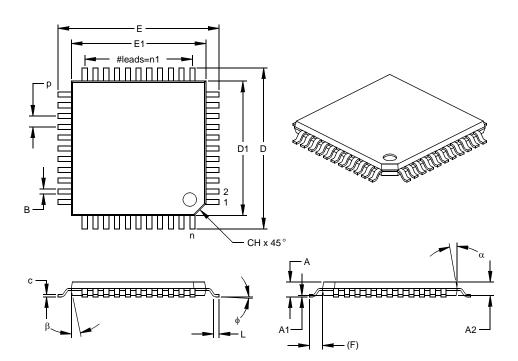

# 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES MILLIMETERS* |      |      | *     |       |       |

|--------------------------|-----|---------------------|------|------|-------|-------|-------|

| Dimension Limits         |     | MIN                 | NOM  | MAX  | MIN   | NOM   | MAX   |

| Number of Pins           | n   |                     | 44   |      |       | 44    |       |

| Pitch                    | р   |                     | .031 |      |       | 0.80  |       |

| Pins per Side            | n1  |                     | 11   |      |       | 11    |       |

| Overall Height           | А   | .039                | .043 | .047 | 1.00  | 1.10  | 1.20  |

| Molded Package Thickness | A2  | .037                | .039 | .041 | 0.95  | 1.00  | 1.05  |

| Standoff §               | A1  | .002                | .004 | .006 | 0.05  | 0.10  | 0.15  |

| Foot Length              | L   | .018                | .024 | .030 | 0.45  | 0.60  | 0.75  |

| Footprint (Reference)    | (F) |                     | .039 |      | 1.00  |       |       |

| Foot Angle               | φ   | 0                   | 3.5  | 7    | 0     | 3.5   | 7     |