Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877t-04-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, and the EEPROM write operation interrupt.

# REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

|         | U-0         | R/W-0          | U-0           | R/W-0        | R/W-0          | U-0       | U-0            | R/W-0  |

|---------|-------------|----------------|---------------|--------------|----------------|-----------|----------------|--------|

|         | —           | Reserved       | —             | EEIE         | BCLIE          | —         | —              | CCP2IE |

|         | bit 7       |                |               |              |                |           |                | bit 0  |

|         |             |                |               |              |                |           |                |        |

| bit 7   | Unimplem    | ented: Read    | as '0'        |              |                |           |                |        |

| bit 6   | Reserved:   | Always mair    | ntain this bi | it clear     |                |           |                |        |

| bit 5   | Unimplem    | ented: Read    | as '0'        |              |                |           |                |        |

| bit 4   | EEIE: EEP   | ROM Write C    | Operation I   | nterrupt Ena | able           |           |                |        |

|         | 1 = Enable  | EE Write Int   | errupt        |              |                |           |                |        |

|         | 0 = Disable | e EE Write In  | terrupt       |              |                |           |                |        |

| bit 3   | BCLIE: Bu   | s Collision In | terrupt Ena   | able         |                |           |                |        |

|         | 1 = Enable  | Bus Collisio   | n Interrupt   |              |                |           |                |        |

|         | 0 = Disable | e Bus Collisio | on Interrupt  |              |                |           |                |        |

| bit 2-1 | Unimplem    | ented: Read    | as '0'        |              |                |           |                |        |

| bit 0   | CCP2IE: C   | CP2 Interrup   | t Enable b    | it           |                |           |                |        |

|         | 1 = Enable  | s the CCP2 i   | nterrupt      |              |                |           |                |        |

|         | 0 = Disable | es the CCP2    | interrupt     |              |                |           |                |        |

|         |             |                |               |              |                |           |                |        |

|         | Legend:     |                |               |              |                |           |                |        |

|         | R = Reada   | ble bit        | VV = V        | Vritable bit | U = Unimpl     | emented b | oit, read as ' | 0'     |

|         | - n = Value | at POR         | '1' = E       | Bit is set   | '0' = Bit is c | leared    | x = Bit is u   | nknown |

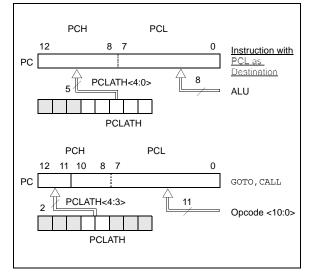

# 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

## FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

# 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

# EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| _       | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

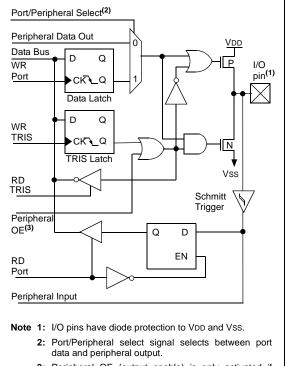

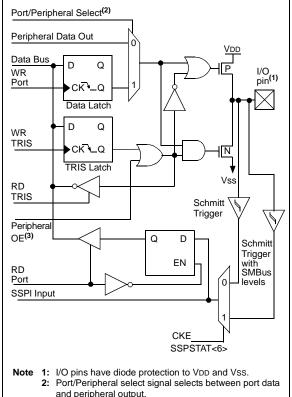

# 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

# FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

# FIGURE 3-6:

# PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

# 3.4 **PORTD and TRISD Registers**

PORTD and TRISD are not implemented on the PIC16F873 or PIC16F876.

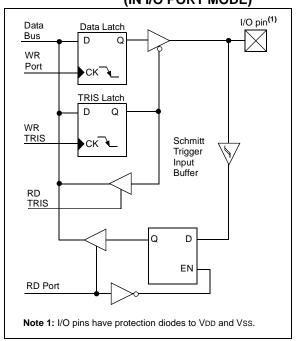

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configureable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

# FIGURE 3-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                           |

|----------|------|-----------------------|----------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0. |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1. |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2. |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3. |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4. |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5. |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6. |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7. |

# TABLE 3-7: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

# TABLE 3-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6  | Bit 5    | Bit 4       | Bit 3                                         | Bit 2     | Bit 2 Bit 1 Bit 0 |           | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|-------|--------|----------|-------------|-----------------------------------------------|-----------|-------------------|-----------|--------------------------|---------------------------------|

| 08h     | PORTD | RD7   | RD6    | RD5      | RD4         | RD3                                           | RD2       | RD1               | RD0       | xxxx xxxx                | uuuu uuuu                       |

| 88h     | TRISD | PORT  | D Data | Directio | on Register |                                               | 1111 1111 | 1111 1111         |           |                          |                                 |

| 89h     | TRISE | IBF   | OBF    | IBOV     | PSPMODE     | <ul> <li>PORTE Data Direction Bits</li> </ul> |           | 0000 -111         | 0000 -111 |                          |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

# 4.4 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program the memory and insert value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

# EXAMPLE 4-3: FLASH PROGRAM READ

| BSF   | STATUS, RP1   | ;                        |

|-------|---------------|--------------------------|

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | ADDRL, W      | ;Write the               |

| MOVWF | EEADR         | ;address bytes           |

| MOVF  | ADDRH,W       | ;for the desired         |

| MOVWF | EEADRH        | ;address to read         |

| BSF   | STATUS, RPO   | ;Bank 3                  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |

| BSF   | EECON1, RD    | ;Start read operation    |

| NOP   |               | ;Required two NOPs       |

| NOP   |               | ;                        |

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |

| MOVWF | DATAL         | ;                        |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |

| MOVWF | DATAH         | ;                        |

|       |               |                          |

# 4.5 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory, is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 4-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

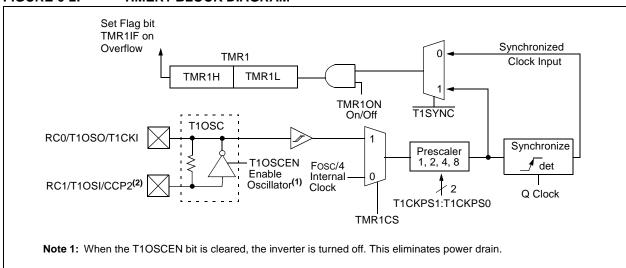

# 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

# 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

# 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

# FIGURE 6-2: TIMER1 BLOCK DIAGRAM

### **REGISTER 9-2:** SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL SSPOV SSPM0 SSPEN CKP SSPM3 SSPM2 SSPM1 bit 7 bit 0 bit 7 WCOL: Write Collision Detect bit Master mode: 1 = A write to SSPBUF was attempted while the I2C conditions were not valid 0 = No collision Slave mode: 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software) 0 = No collision bit 6 SSPOV: Receive Overflow Indicator bit In SPI mode: 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.) 0 = No overflowIn I<sup>2</sup>C mode: 1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.) 0 = No overflowSSPEN: Synchronous Serial Port Enable bit bit 5 In SPI mode, When enabled, these pins must be properly configured as input or output 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins In I<sup>2</sup>C mode, When enabled, these pins must be properly configured as input or output 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins bit 4 CKP: Clock Polarity Select bit In SPI mode: 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level In I<sup>2</sup>C Slave mode: SCK release control 1 = Enable clock 0 = Holds clock low (clock stretch). (Used to ensure data setup time.) In I<sup>2</sup>C Master mode: Unused in this mode bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits 0000 = SPI Master mode, clock = Fosc/4 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64 0011 = SPI Master mode, clock = TMR2 output/2 0100 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled. 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin. $0110 = I^2C$ Slave mode, 7-bit address $0111 = I^2C$ Slave mode, 10-bit address 1000 = I<sup>2</sup>C Master mode, clock = Fosc / (4 \* (SSPADD+1)) $1011 = I^2C$ Firmware Controlled Master mode (slave idle) 1110 = I<sup>2</sup>C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled 1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled 1001, 1010, 1100, 1101 = Reserved

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 9.2.7 I<sup>2</sup>C MASTER MODE SUPPORT

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once Master mode is enabled, the user has six options:

- Assert a START condition on SDA and SCL.

- Assert a Repeated START condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a STOP condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP Module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a START condition and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

# 9.2.7.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated START condition. Since the Repeated START condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSPBUF. Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state.

A typical transmit sequence would go as follows:

- a) User generates a START condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) User loads SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) MSSP module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) User loads SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

- MSSP module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) User generates a STOP condition by setting the STOP enable bit, PEN, in SSPCON2.

- I) Interrupt is generated once the STOP condition is complete.

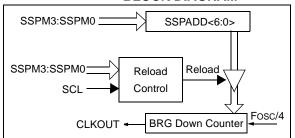

# 9.2.8 BAUD RATE GENERATOR

In  $I^2C$  Master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 9-10). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (Tcr), on the Q2 and Q4 clock.

In I<sup>2</sup>C Master mode, the BRG is reloaded automatically. If clock arbitration is taking place, the BRG will be reloaded when the SCL pin is sampled high (Figure 9-11).

Note: Baud Rate = Fosc / (4 \* (SSPADD + 1))

FIGURE 9-10:

# BAUD RATE GENERATOR BLOCK DIAGRAM

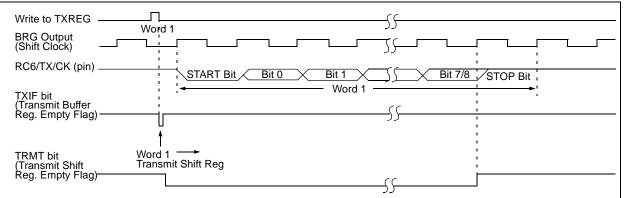

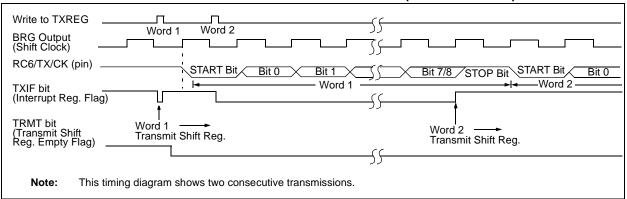

When setting up an Asynchronous Transmission, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

# FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

# FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

# TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|-----------|--------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE   | INTE      | RBIE      | T0IF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF   | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN   | CREN      | _         | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tra            | insmit Re | gister |           |           |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE   | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN   | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato  |        | 0000 0000 | 0000 0000 |        |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

# PIC16F87X

# REGISTER 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | —   | —     | —   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

# bit 6-4 Unimplemented: Read as '0'

bit 3-0 **PCFG3:PCFG0**: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | AN6 <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | Α                         | Α                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 8/0                          |

| 0001            | А                         | А                         | А                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | А          | VREF+      | А          | Α          | Α          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | Α          | D          | Α          | Α          | Vdd   | Vss   | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | Α          | А          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | Vdd   | Vss   | 0/0                          |

| 1000            | А                         | А                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | А                         | А          | Α          | Α          | Α          | Α          | Vdd   | Vss   | 6/0                          |

| 1010            | D                         | D                         | А                         | А          | VREF+      | Α          | А          | Α          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | А                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | А          | VREF+      | VREF-      | Α          | Α          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | А          | А          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | Α          | Vdd   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | Vref-      | D          | А          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the 10-bit result of the A/D conversion. When the A/D conversion is complete, the result is loaded into this A/D result register pair, the GO/DONE bit (ADCON0<2>) is cleared and the A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 11-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine sample time, see Section 11.1. After this acquisition time has elapsed, the A/D conversion can be started.

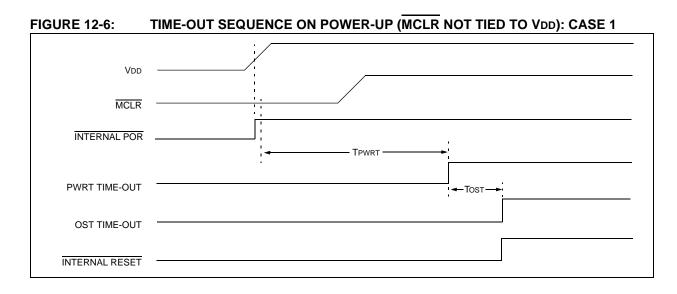

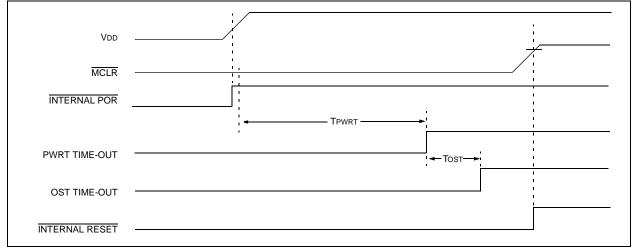

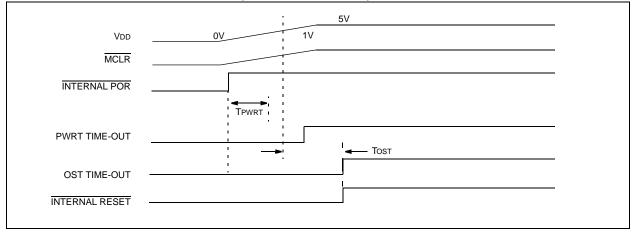

# 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

# 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

# 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

# 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about  $100\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

# 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

# 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power-up         |           | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

# TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

# PIC16F87X

# FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

# 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

# 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

# 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

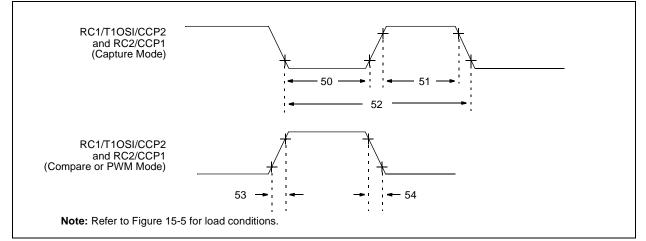

# FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

# TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym  | Characteristic                 |                |                       | Min         | Тур† | Max | Units                              | Conditions |

|--------------|------|--------------------------------|----------------|-----------------------|-------------|------|-----|------------------------------------|------------|

| 50*          | TccL | CCP1 and CCP2 No Prescaler     |                |                       | 0.5Tcy + 20 | —    | _   | ns                                 |            |

|              |      | input low time                 |                | Standard(F)           | 10          | _    | _   | ns                                 |            |

|              |      |                                | With Prescaler | Extended(LF)          | 20          | _    | _   | ns                                 |            |

| 51*          | TccH | CCP1 and CCP2                  | No Prescaler   |                       | 0.5Tcy + 20 | _    | _   | ns                                 |            |

|              |      | input high time                |                | Standard(F)           | 10          | —    | _   | ns                                 |            |

|              |      | Wi                             | With Prescaler | Extended(LF)          | 20          | —    | _   | ns                                 |            |

| 52*          | TccP | CCP1 and CCP2 input period     |                | <u>3TCY + 40</u><br>N | _           | _    | ns  | N = prescale<br>value (1, 4 or 16) |            |

| 53*          | TccR | CCP1 and CCP2 output rise time |                | Standard(F)           | —           | 10   | 25  | ns                                 |            |

|              |      |                                |                | Extended(LF)          | —           | 25   | 50  | ns                                 |            |

| 54*          | TccF | CCP1 and CCP2 output fall time |                | Standard(F)           | —           | 10   | 25  | ns                                 |            |

|              |      |                                |                | Extended(LF)          | —           | 25   | 45  | ns                                 |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

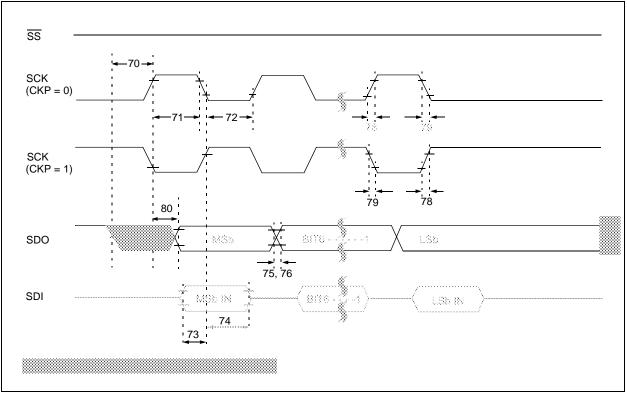

# FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

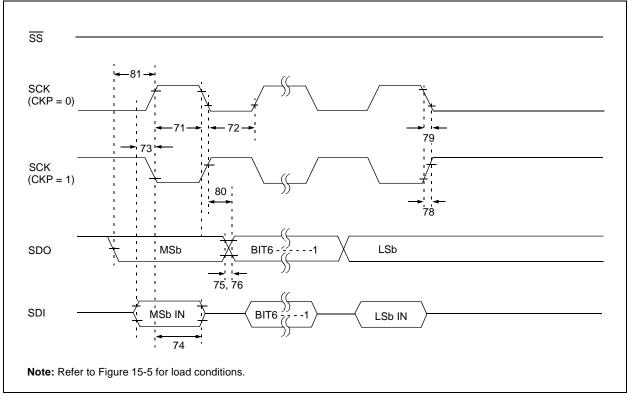

# FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

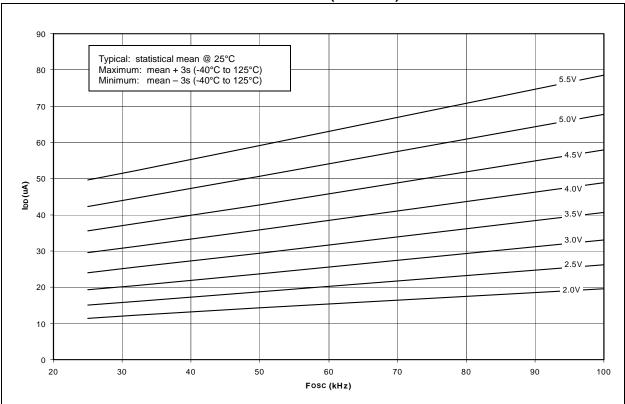

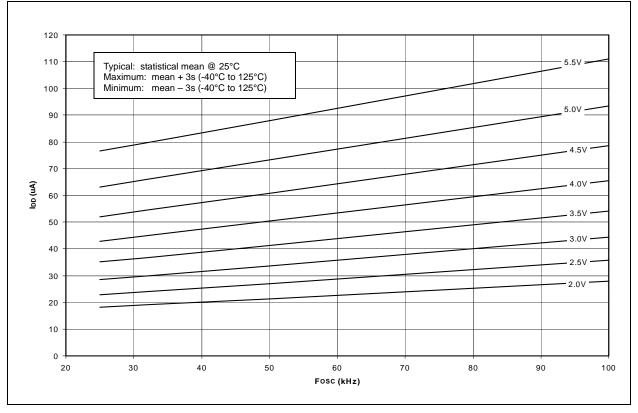

FIGURE 16-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

© 1998-2013 Microchip Technology Inc.

# APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 1998 | This is a new data sheet.<br>However, these devices are<br>similar to the PIC16C7X<br>devices found in the<br>PIC16C7X Data Sheet<br>(DS30390). Data Memory<br>Map for PIC16F873/874,<br>moved ADFM bit from<br>ADCON1<5> to ADCON1<7>. |

| В       | 1999 | FLASH EEPROM access<br>information.                                                                                                                                                                                                     |

| С       | 2000 | DC characteristics updated.<br>DC performance graphs<br>added.                                                                                                                                                                          |

| D       | 2013 | Added a note to each package drawing.                                                                                                                                                                                                   |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

| Difference             | PIC16F876/873                                             | PIC16F877/874                                               |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------|

| A/D                    | 5 channels,<br>10-bits                                    | 8 channels,<br>10-bits                                      |

| Parallel<br>Slave Port | no                                                        | yes                                                         |

| Packages               | 28-pin PDIP,<br>28-pin windowed<br>CERDIP, 28-pin<br>SOIC | 40-pin PDIP,<br>44-pin TQFP,<br>44-pin MQFP,<br>44-pin PLCC |

# PIC16F87X

| PORTE                                                      | 9, 17     |

|------------------------------------------------------------|-----------|

| Analog Port Pins                                           | 9, 36, 38 |

| Associated Registers                                       |           |

| Block Diagram                                              |           |

| Input Buffer Full Status (IBF Bit)                         |           |

| Input Buffer Overflow (IBOV Bit)                           |           |

| Output Buffer Full Status (OBF Bit)                        |           |

| PORTE Register                                             |           |

| PSP Mode Select (PSPMODE Bit)                              | 6, 37, 38 |

| RE0/RD/AN5 Pin                                             |           |

| RE1/WR/AN6 Pin                                             | 9, 36, 38 |

| RE2/CS/AN7 Pin                                             | 9, 36, 38 |

| TRISE Register                                             |           |

| Postscaler, WDT                                            |           |

| Assignment (PSA Bit)                                       |           |

| Rate Select (PS2:PS0 Bits)                                 | 19        |

| Power-down Mode. See SLEEP                                 |           |

| Power-on Reset (POR)119, 123, 124,                         | 125, 126  |

| Oscillator Start-up Timer (OST)                            | 119, 124  |

| POR Status (POR Bit)                                       |           |

| Power Control (PCON) Register                              | 124       |

| Power-down (PD Bit)                                        |           |

| Power-up <u>Tim</u> er (PWRT)                              |           |

| Time-out (TO Bit)                                          |           |

| Time-out Sequence on Power-up                              |           |

| PR2 Register                                               | 16, 55    |

| Prescaler, Timer0                                          |           |

| Assignment (PSA Bit)                                       | 19        |

| Rate Select (PS2:PS0 Bits)                                 |           |

| PRO MATE II Universal Device Programmer                    | 145       |

| Program Counter                                            |           |

| RESET Conditions                                           |           |

| Program Memory                                             |           |

| Interrupt Vector                                           |           |

| Paging                                                     |           |

| Program Memory Map                                         |           |

| RESET Vector                                               |           |

| Program Verification                                       |           |

| Programming Pin (VPP)                                      |           |

| Programming, Device Instructions                           |           |

| PSP. See Parallel Slave Port.                              |           |

| Pulse Width Modulation.SeeCapture/Compare/PWM<br>PWM Mode. | ,         |

| PWM Mode.<br>PUSH                                          | 26        |

|                                                            | 20        |

# R

| R/W                                   |        |

|---------------------------------------|--------|

| R/W bit                               | 74     |

| R/W bit                               | 74     |

| RAM. See Data Memory                  |        |

| RCREG                                 |        |

| RCSTA Register                        | 17, 96 |

| ADDEN Bit                             |        |

| CREN Bit                              |        |

| FERR Bit                              |        |

| OERR Bit                              |        |

| RX9 Bit                               |        |

| RX9D Bit                              |        |

| SPEN Bit                              |        |

| SREN Bit                              |        |

| Read/Write bit, R/W                   |        |

| Reader Response                       |        |

| Receive Enable bit                    |        |

| Receive Overflow Indicator bit, SSPOV | 67     |

| Register File                         |        |

| Register File Map                     |        |

|                                       |        |

| Registers                                        |

|--------------------------------------------------|

| ADCON0 (A/D Control 0) 111                       |

| ADCON1 (A/D Control 1) 112                       |

| CCP1CON (CCP Control 1) 58                       |

| EECON2 41                                        |

| FSR                                              |

| INTCON 20                                        |

| OPTION_REG19, 48                                 |

| PCON (Power Control) 25                          |

| PIE1 (Peripheral Interrupt Enable 1) 21          |

| PIE2 (Peripheral Interrupt Enable 2)             |

| PIR1 (Peripheral Interrupt Request 1) 22         |

| PIR2 (Peripheral Interrupt Request 2) 24         |

| RCSTA (Receive Status and Control)               |

| Special Function, Summary 15                     |

| SSPCON2 (Sync Serial Port Control 2) 68          |

| STATUS                                           |

| T1CON (Timer1 Control) 51                        |

| T2CON (Timer 2 Control)                          |

| Timer2                                           |

| T2CON Register                                   |

| TRISE                                            |

| TXSTA (Transmit Status and Control)              |

| Repeated START Condition Enable bit              |

| RESET                                            |

| Block Diagram                                    |

| RESET                                            |

| Brown-out Reset (BOR). See Brown-out Reset (BOR) |

| Power-on Reset (POR). See Power-on Reset (POR)   |

| RESET Conditions for PCON Register               |

| RESET Conditions for Program Counter             |

| RESET Conditions for STATUS Register             |

| WDT Reset. See Watchdog Timer (WDT)              |

| Revision History                                 |

|                                                  |

| S                                                |

| S (START bit)<br>Sales and Support<br>SCI. See USART |               |

|------------------------------------------------------|---------------|

| SCK                                                  | 69            |

| SCL                                                  | 74            |

| SDA                                                  | 74            |

| SDI                                                  | 69            |

| SDO                                                  |               |

| Serial Clock, SCK                                    | 69            |

| Serial Clock, SCL                                    | 74            |

| Serial Communication Interface. See USART            |               |

| Serial Data Address, SDA                             | 74            |

| Serial Data In, SDI                                  | 69            |

| Serial Data Out, SDO                                 | 69            |

| Slave Select, SS                                     | 69            |

| SLEEP                                                | 119, 123, 132 |

| SMP                                                  | 66            |

| Software Simulator (MPLAB SIM)                       | 144           |

| SPBRG Register                                       |               |

| Special Features of the CPU                          | 119           |

| Special Function Registers                           | 15            |

| Special Function Registers (SFRs)                    | 15            |

| Data EEPROM and FLASH Program Mem                    |               |

| Speed, Operating                                     | 1             |

$\odot$  1998-2013 Microchip Technology Inc.

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:       | To: Technical Publications Manager Total Pa                                            | ges Sent           |

|-----------|----------------------------------------------------------------------------------------|--------------------|

| RE:       | RE: Reader Response                                                                    |                    |

| From      | From: Name                                                                             |                    |

|           | Company                                                                                |                    |

|           | Address                                                                                |                    |

|           | City / State / ZIP / Country                                                           |                    |

|           | Telephone: () FAX: (                                                                   | )                  |

| Appl      | Application (optional):                                                                |                    |

| Wou       | Would you like a reply?YN                                                              |                    |

| Devi      | Device: PIC16F87X Literature Number: DS30292D                                          |                    |

| Que       | Questions:                                                                             |                    |

| 1. \      | 1. What are the best features of this document?                                        |                    |

|           |                                                                                        |                    |

| _         |                                                                                        |                    |

| 2. ł      | 2. How does this document meet your hardware and software development                  | needs?             |

| -         |                                                                                        |                    |

| -<br>2 [  | 2. Do you find the experimentian of this data sheet easy to follow? If not why         | 5                  |

| 3. I      | 3. Do you find the organization of this data sheet easy to follow? If not, why?        |                    |

| -         |                                                                                        |                    |

| 4. \      | 4. What additions to the data sheet do you think would enhance the structure           | e and subject?     |

| -         |                                                                                        |                    |

|           |                                                                                        |                    |

| 5. \      | 5. What deletions from the data sheet could be made without affecting the o            | verall usefulness? |

| -         |                                                                                        |                    |

| 6. I      | 6. Is there any incorrect or misleading information (what and where)?                  |                    |

| _         |                                                                                        |                    |

| -         |                                                                                        |                    |

| 7. H      | 7. How would you improve this document?                                                |                    |

| -         |                                                                                        |                    |

| -<br>8. H | <ol> <li>How would you improve our software, systems, and silicon products?</li> </ol> |                    |

|           |                                                                                        |                    |

# PIC16F87X

NOTES: