Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf877t-04-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2             | Bit 1          | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|----------------------|----------------|---------------|----------------|----------------|-------------------|----------------|----------|--------------------------|------------------------|

| Bank 0               |         |                      |                |               |                |                |                   |                |          |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio | n uses conte  | ents of FSR to | address dat    | a memory (no      | t a physical r | egister) | 0000 0000                | 27                     |

| 01h                  | TMR0    | Timer0 Mo            | dule Registe   | er            |                |                |                   |                |          | xxxx xxxx                | 47                     |

| 02h <sup>(3)</sup>   | PCL     | Program C            | Counter (PC)   | Least Signif  | icant Byte     |                |                   |                |          | 0000 0000                | 26                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1            | RP0           | TO             | PD             | Z                 | DC             | С        | 0001 1xxx                | 18                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ata Memory /   | Address Poir  | nter           |                |                   |                |          | xxxx xxxx                | 27                     |

| 05h                  | PORTA   | _                    | _              | PORTA Da      | ta Latch whe   | n written: POI | RTA pins whe      | n read         |          | 0x 0000                  | 29                     |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh   | en written: P | ORTB pins w    | /hen read      |                   |                |          | xxxx xxxx                | 31                     |

| 07h                  | PORTC   | PORTC D              | ata Latch wh   | en written: F | ORTC pins v    | vhen read      |                   |                |          | xxxx xxxx                | 33                     |

| 08h <sup>(4)</sup>   | PORTD   | PORTD D              | ata Latch wh   | en written: F | ORTD pins v    | vhen read      |                   |                |          | xxxx xxxx                | 35                     |

| 09h <sup>(4)</sup>   | PORTE   | _                    | _              | _             | _              | _              | RE2               | RE1            | RE0      | xxx                      | 36                     |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    |                |               | Write Buffer   | for the upper  | r 5 bits of the I | Program Cou    | unter    | 0 0000                   | 26                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE           | T0IE          | INTE           | RBIE           | T0IF              | INTF           | RBIF     | 0000 000x                | 20                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF           | RCIF          | TXIF           | SSPIF          | CCP1IF            | TMR2IF         | TMR1IF   | 0000 0000                | 22                     |

| 0Dh                  | PIR2    | —                    | (5)            | _             | EEIF           | BCLIF          | —                 |                | CCP2IF   | -r-0 00                  | 24                     |

| 0Eh                  | TMR1L   | Holding re           | gister for the | Least Signif  | ficant Byte of | the 16-bit TM  | IR1 Register      |                |          | xxxx xxxx                | 52                     |

| 0Fh                  | TMR1H   | Holding re           | gister for the | Most Signifi  | cant Byte of t | the 16-bit TM  | R1 Register       |                |          | xxxx xxxx                | 52                     |

| 10h                  | T1CON   | _                    | _              | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC            | TMR1CS         | TMR10N   | 00 0000                  | 51                     |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe   | er            |                |                |                   |                |          | 0000 0000                | 55                     |

| 12h                  | T2CON   | _                    | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON            | T2CKPS1        | T2CKPS0  | -000 0000                | 55                     |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po  | rt Receive B  | uffer/Transm   | it Register    |                   |                |          | xxxx xxxx                | 70, 73                 |

| 14h                  | SSPCON  | WCOL                 | SSPOV          | SSPEN         | CKP            | SSPM3          | SSPM2             | SSPM1          | SSPM0    | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI     | M Register1   | (LSB)          |                |                   |                |          | XXXX XXXX                | 57                     |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI     | M Register1   | (MSB)          |                |                   |                |          | XXXX XXXX                | 57                     |

| 17h                  | CCP1CON | _                    | _              | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2            | CCP1M1         | CCP1M0   | 00 0000                  | 58                     |

| 18h                  | RCSTA   | SPEN                 | RX9            | SREN          | CREN           | ADDEN          | FERR              | OERR           | RX9D     | 0000 000x                | 96                     |

| 19h                  | TXREG   | USART Tr             | ansmit Data    | Register      |                |                |                   |                |          | 0000 0000                | 99                     |

| 1Ah                  | RCREG   | USART Re             | eceive Data I  | Register      |                |                |                   |                |          | 0000 0000                | 101                    |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI     | V Register2   | (LSB)          |                |                   |                |          | xxxx xxxx                | 57                     |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI     | M Register2   | (MSB)          |                |                   |                |          | xxxx xxxx                | 57                     |

| 1Dh                  | CCP2CON | _                    | _              | CCP2X         | CCP2Y          | CCP2M3         | CCP2M2            | CCP2M1         | CCP2M0   | 00 0000                  | 58                     |

| 1Eh                  | ADRESH  | A/D Result           | t Register Hi  | gh Byte       |                |                |                   |                |          | xxxx xxxx                | 116                    |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0          | CHS2          | CHS1           | CHS0           | GO/DONE           |                | ADON     | 0000 00-0                | 111                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | the TMR0 register, assign the prescaler to |  |  |  |  |

|       | the Watchdog Timer.                        |  |  |  |  |

#### **R/W-1** R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 bit 7 bit 0 **RBPU:** PORTB Pull-up Enable bit bit 7 1 = PORTB pull-ups are disabled 0 = PORTB pull-ups are enabled by individual port latch values bit 6 **INTEDG:** Interrupt Edge Select bit 1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin bit 5 TOCS: TMR0 Clock Source Select bit 1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) bit 4 TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin bit 3 PSA: Prescaler Assignment bit 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS2:PS0: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 000 1:1 1:2 1:2 001 1:4 010 1:4 1:8 011 1:8 1:16 1:16 100 1:32 101 1:32 1:64 110 1:128 1:64 111 1:128 1:256 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device

#### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

#### 2.2.2.8 PCON Register

The Power Control (PCON) Register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT), and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | —   | —   | —   |     | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

**BOR**: Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name         | Bit# | Buffer | Function                                                                        |  |

|--------------|------|--------|---------------------------------------------------------------------------------|--|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |  |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |  |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |  |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |  |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |  |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |  |

#### TABLE 3-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     |       | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     | _     | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  |       | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000                  | 0-0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.

#### TABLE 3-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or Synchronous Clock.                          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|-------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                          | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | ORTC Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged

#### **TRISE REGISTER (ADDRESS 89h)** R/W-1 R-0 R-0 R/W-0 R/W-0 U-0 R/W-1 R/W-1 IBF OBF **IBOV PSPMODE** Bit2 Bit1 Bit0 bit 7 bit 0 Parallel Slave Port Status/Control Bits: bit 7 IBF: Input Buffer Full Status bit 1 = A word has been received and is waiting to be read by the CPU 0 = No word has been received bit 6 **OBF**: Output Buffer Full Status bit 1 = The output buffer still holds a previously written word 0 = The output buffer has been read bit 5 **IBOV**: Input Buffer Overflow Detect bit (in Microprocessor mode) 1 = A write occurred when a previously input word has not been read (must be cleared in software) 0 = No overflow occurred bit 4 PSPMODE: Parallel Slave Port Mode Select bit 1 = PORTD functions in Parallel Slave Port mode 0 = PORTD functions in general purpose I/O mode Unimplemented: Read as '0' bit 3 **PORTE Data Direction Bits:** Bit2: Direction Control bit for pin RE2/CS/AN7 bit 2 1 = Input 0 = OutputBit1: Direction Control bit for pin RE1/WR/AN6 bit 1 1 = Input 0 = Output Bit0: Direction Control bit for pin RE0/RD/AN5 bit 0 1 = Input 0 = Output Legend:

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

R = Readable bit

- n = Value at POR

**REGISTER 3-1:**

NOTES:

#### 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

### 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

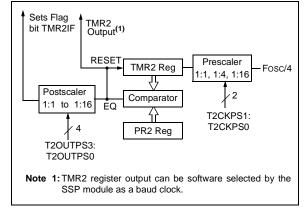

## 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

#### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

|         | U-0                                                  | R/W-0               | R/W-0       | R/W-0        | R/W-0       | R/W-0     | R/W-0        | R/W-0   |

|---------|------------------------------------------------------|---------------------|-------------|--------------|-------------|-----------|--------------|---------|

|         | _                                                    | TOUTPS3             | TOUTPS2     | TOUTPS1      | TOUTPS0     | TMR2ON    | T2CKPS1      | T2CKPS0 |

|         | bit 7                                                | •                   |             |              |             |           |              | bit 0   |

|         |                                                      |                     |             |              |             |           |              |         |

| bit 7   | Unimplen                                             | n <b>ented:</b> Rea | d as '0'    |              |             |           |              |         |

| bit 6-3 | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |                     |             |              |             |           |              |         |

|         | 0000 = 1:                                            | 1 Postscale         |             |              |             |           |              |         |

|         |                                                      | 2 Postscale         |             |              |             |           |              |         |

|         | •                                                    | 3 Postscale         |             |              |             |           |              |         |

|         | •                                                    |                     |             |              |             |           |              |         |

|         | •                                                    |                     |             |              |             |           |              |         |

|         | 1111 <b>= 1</b> :                                    | 16 Postscale        | <b>;</b>    |              |             |           |              |         |

| bit 2   | -                                                    | Timer2 On I         | bit         |              |             |           |              |         |

|         | 1 = Timer2                                           |                     |             |              |             |           |              |         |

|         | 0 = Timer2                                           |                     |             |              |             |           |              |         |

| bit 1-0 |                                                      | :T2CKPS0:           | Timer2 Cloc | k Prescale S | Select bits |           |              |         |

|         | 00 = Pres                                            |                     |             |              |             |           |              |         |

|         | 1x = Pres                                            |                     |             |              |             |           |              |         |

|         |                                                      |                     |             |              |             |           |              |         |

|         | Legend:                                              |                     |             |              |             |           |              |         |

|         | R = Reada                                            | able bit            | W = W       | /ritable bit | U = Unim    | plemented | bit, read as | '0'     |

|         | - n = Value                                          | e at POR            | '1' = B     | it is set    | '0' = Bit i | s cleared | x = Bit is u | nknown  |

### 8.3 PWM Mode (PWM)

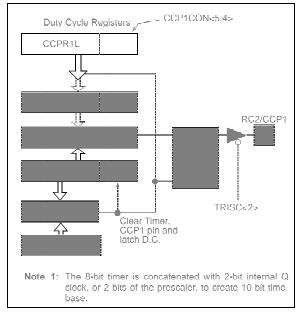

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.3.3.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

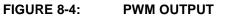

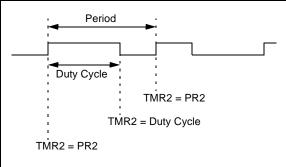

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 7.1) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

PWM duty cycle =(CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitch-free PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock, or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

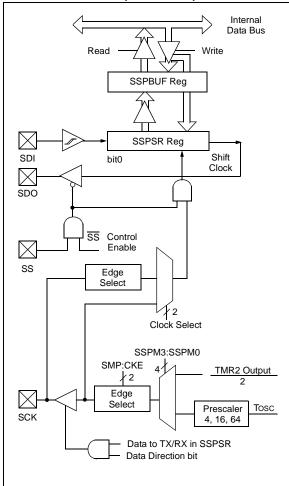

### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

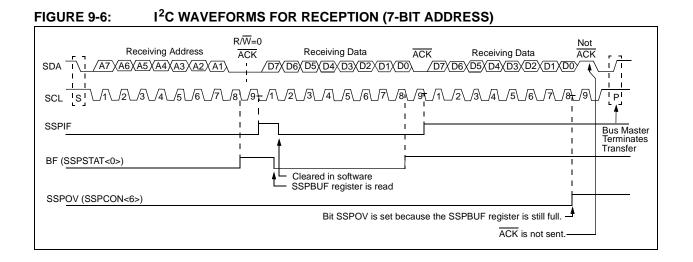

| Status Bits as Data<br>Transfer is Received |       | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|---------------------------------------------|-------|---------------------------|-----------------------|----------------------------------------|--|

| BF                                          | SSPOV |                           | ruise                 | if enabled)                            |  |

| 0                                           | 0     | Yes                       | Yes                   | Yes                                    |  |

| 1                                           | 0     | No                        | No                    | Yes                                    |  |

| 1                                           | 1     | No                        | No                    | Yes                                    |  |

| 0                                           | 1     | Yes                       | No                    | Yes                                    |  |

TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 9.2.1.3 Slave Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7). An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting the CKP bit.

# PIC16F87X

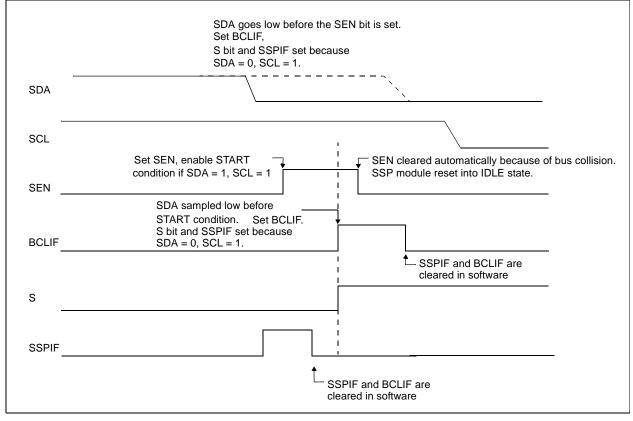

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

## 13.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight bit literal 'k'<br>and the result is placed in the W<br>register. |

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

|------------------|---------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

Bit Clear f

BCF

| ADDWF            | Add W and f                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                       |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in<br>register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2TcY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                            |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2TCY instruction. |

# PIC16F87X

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |  |  |  |  |  |

| Operands:                      | None                                                                                                                                                                                 |  |  |  |  |  |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |  |  |  |  |  |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |  |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |  |

| COMF             | Complement f                                                                                                                                            |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] COMF f,d                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                         |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |

| CLRW             | Clear W                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRW                                                          |  |  |  |

| Operands:        | None                                                                  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |  |  |  |

| DECF             | Decrement f                                                                                                                                   |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                     |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |  |  |  |

| Status Affected: | Z                                                                                                                                             |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                               |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                         |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                               |  |  |  |  |  |  |

### SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                 |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                            |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                       |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |  |  |  |  |  |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                      |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |  |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |

### 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |      |     |       |                                                                    |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------|------------------------------------------------------|------|-----|-------|--------------------------------------------------------------------|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |     |       |                                                                    |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                            | Min                                                  | Тур† | Мах | Units | Conditions                                                         |

|                                                                                  | IDD    | Supply Current <sup>(2,5)</sup>                      |                                                      |      |     |       |                                                                    |

| D010                                                                             |        | 16LF87X                                              | —                                                    | 0.6  | 2.0 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V               |

| D010                                                                             |        | 16F87X                                               | —                                                    | 1.6  | 4   | mA    | RC osc configurations<br>FOSC = 4 MHz, VDD = 5.5V                  |

| D010A                                                                            |        | 16LF87X                                              | —                                                    | 20   | 35  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled |

| D013                                                                             |        | 16F87X                                               | _                                                    | 7    | 15  | mA    | HS osc configuration,<br>Fosc = 20 MHz, VDD = 5.5V                 |

| D015                                                                             | ∆IBOR  | Brown-out<br>Reset Current <sup>(6)</sup>            | —                                                    | 85   | 200 | μΑ    | BOR enabled, VDD = 5.0V                                            |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

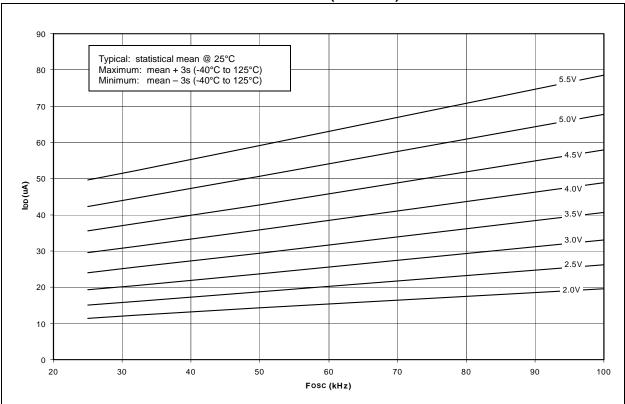

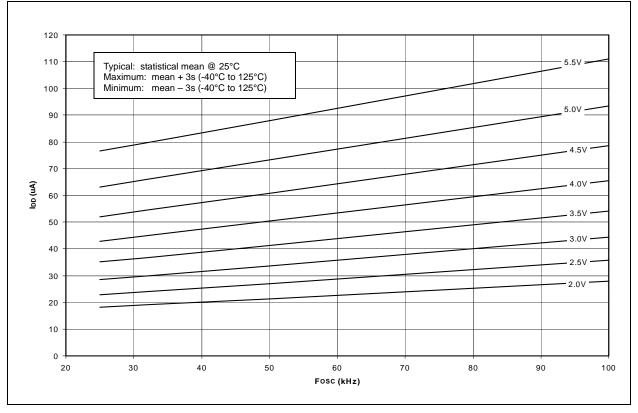

FIGURE 16-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

© 1998-2013 Microchip Technology Inc.

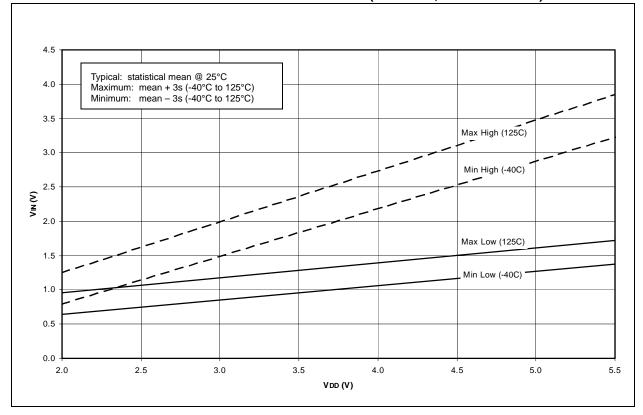

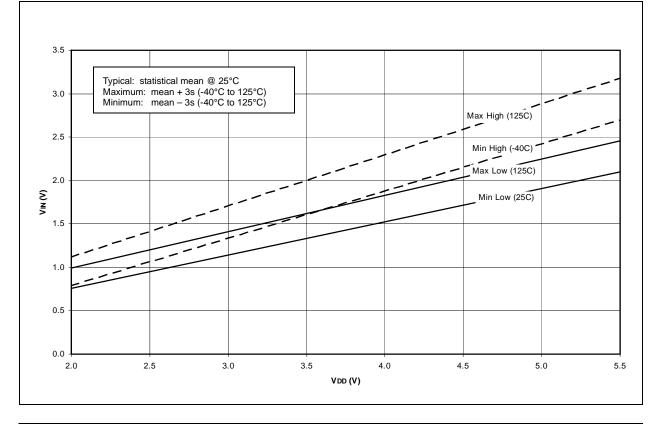

FIGURE 16-21: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO 125°C)

© 1998-2013 Microchip Technology Inc.

# PIC16F87X

| Master Mode Operation       7         Master Mode START Condition       8         Master Mode Transmission       8         Master Mode Transmission       8         Master Mode Transmit Sequence       7         Multi-Master Communication       8         Multi-master Mode       7         Operation       7         Repeat START Condition Timing       8         Slave Mode       7         Block Diagram       7         Slave Reception       7         SSPBUF       7         STOP Condition Receive or Transmit Timing       8         STOP Condition Timing       8         Waveforms for 7-bit Reception       7         I <sup>2</sup> C Slave Mode       7         I <sup>2</sup> C Slave Mode       7         ICEPIC In-Circuit Emulator       14         ID Locations       119, 13         INDF       119, 13         INDF       15, 16, 2         Indirect Addressing       2                                                                         | 30       32         32       79         37       99         37       31         37       34         37       37         37       37         37       37         37       37         37       37         37       37         38       37         39       37         39       37         30       37         31       37         32       37         33       37         34       33         35       37         36       37         37       37         38       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37         39       37 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master Mode Transmission       8         Master Mode Transmit Sequence       7         Multi-Master Communication       8         Multi-master Mode       7         Operation       7         Repeat START Condition Timing       8         Slave Mode       7         Block Diagram       7         Slave Reception       7         Slave Transmission       7         SSPBUF       7         STOP Condition Receive or Transmit Timing       8         STOP Condition Timing       8         Waveforms for 7-bit Reception       7         Vaveforms for 7-bit Reception       7         I <sup>2</sup> C Module Address Register, SSPADD       7         I <sup>2</sup> C Slave Mode       7         ICEPIC In-Circuit Emulator       14         ID Locations       119, 13         In-Circuit Serial Programming (ICSP)       119, 13         INDF       1         INDF Register       15, 16, 2         Indirect Addressing       2                                | 32         79         39         73         73         74         75         76         74         334         75         76         74         334         75         76         74         334         75         76         74         334         77         73         74         334         75         76         73         74         334         75         76         77         73         74         75         76         74         75         76         77         78         79         74         75         76         77         78         79         71         72         73         74         75                                                                                                                                  |