Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1079                                                       |

| Number of Logic Elements/Cells | 21580                                                      |

| Total RAM Bits                 | 1229184                                                    |

| Number of I/O                  | 230                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 484-BBGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1agx20cf484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Transceivers**

Arria® GX devices incorporate up to 12 high-speed serial transceiver channels that build on the success of the Stratix® II GX device family. Arria GX transceivers are structured into full-duplex (transmitter and receiver) four-channel groups called transceiver blocks located on the right side of the device. You can configure the transceiver blocks to support the following serial connectivity protocols (functional modes):

- PCI Express (PIPE)

- Gigabit Ethernet (GIGE)

- XAUI

- Basic (600 Mbps to 3.125 Gbps)

- SDI (HD, 3G)

- Serial RapidIO (1.25 Gbps, 2.5 Gbps, 3.125 Gbps)

Transceivers within each block are independent and have their own set of dividers. Therefore, each transceiver can operate at different frequencies. Each block can select from two reference clocks to provide two clock domains that each transceiver can select from.

Table 2–1 lists the number of transceiver channels for each member of the Arria GX family.

**Table 2–1.** Arria GX Transceiver Channels

| Device    | Number of Transceiver Channels |

|-----------|--------------------------------|

| EP1AGX20C | 4                              |

| EP1AGX35C | 4                              |

| EP1AGX35D | 8                              |

| EP1AGX50C | 4                              |

| EP1AGX50D | 8                              |

| EP1AGX60C | 4                              |

| EP1AGX60D | 8                              |

| EP1AGX60E | 12                             |

| EP1AGX90E | 12                             |

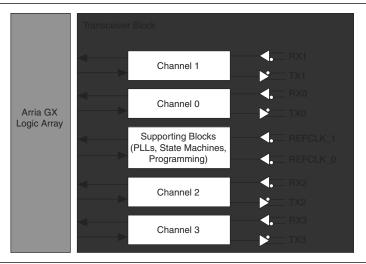

Figure 2–1 shows a high-level diagram of the transceiver block architecture divided into four channels.

Figure 2–1. Transceiver Block

Each transceiver block has:

- Four transceiver channels with dedicated physical coding sublayer (PCS) and physical media attachment (PMA) circuitry

- One transmitter PLL that takes in a reference clock and generates high-speed serial clock depending on the functional mode

- Four receiver PLLs and clock recovery unit (CRU) to recover clock and data from the received serial data stream

- State machines and other logic to implement special features required to support each protocol

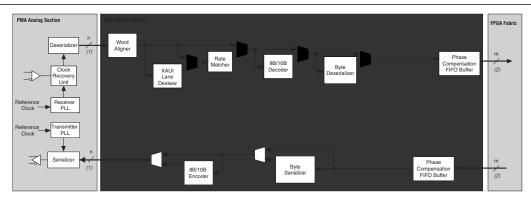

Figure 2–2 shows functional blocks that make up a transceiver channel.

Figure 2-2. Arria GX Transceiver Channel Block Diagram

#### Notes to Figure 2-2:

- "n" represents the number of bits in each word that must be serialized by the transmitter portion of the PMA. n = 8 or 10.

- (2) "m" represents the number of bits in the word that passes between the FPGA logic and the PCS portion of the transceiver. m = 8, 10, 16, or 20.

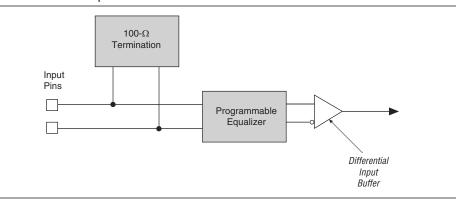

The receiver has  $100-\Omega$  on-chip differential termination ( $R_D$  OCT) for different protocols, as shown in Figure 2–11. You can disable the receiver's internal termination if external terminations and biasing are provided. The receiver and transmitter differential termination method can be set independently of each other.

Figure 2-11. Receiver Input Buffer

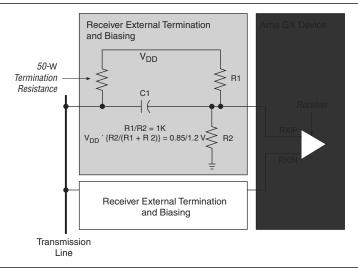

If a design uses external termination, the receiver must be externally terminated and biased to 0.85 V or 1.2 V. Figure 2–12 shows an example of an external termination and biasing circuit.

Figure 2-12. External Termination and Biasing Circuit

#### **Programmable Equalizer**

The Arria GX receivers provide a programmable receiver equalization feature to compensate for the effects of channel attenuation for high-speed signaling. PCB traces carrying these high-speed signals have low-pass filter characteristics. Impedance mismatch boundaries can also cause signal degradation. Equalization in the receiver diminishes the lossy attenuation effects of the PCB at high frequencies.

## **Reverse Serial Pre-CDR Loopback**

Reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received because the signal goes through the output buffer and the  $\rm V_{\rm OD}$  is changed to the  $\rm V_{\rm OD}$  setting level. Pre-emphasis settings have no effect.

Figure 2–20 shows the Arria GX block in reverse serial pre-CDR loopback mode.

Transmitter Digital Logic **Analog Receiver and** Transmitter Logic PRBS Incrementa 8R/10R Compensation Encode FPGA Logic Array Reverse Serial Pre-CDR Loopback Verify **Receiver Digital Logic**

Figure 2-20. Arria GX Block in Reverse Serial Pre-CDR Loopback Mode

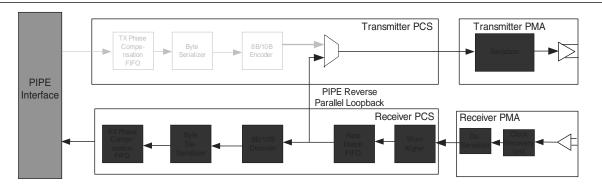

#### **PCI Express (PIPE) Reverse Parallel Loopback**

Figure 2–21 shows the data path for PCI Express (PIPE) reverse parallel loopback. The reverse parallel loopback configuration is compliant with the PCI Express (PIPE) specification and is available only on PCI Express (PIPE) mode.

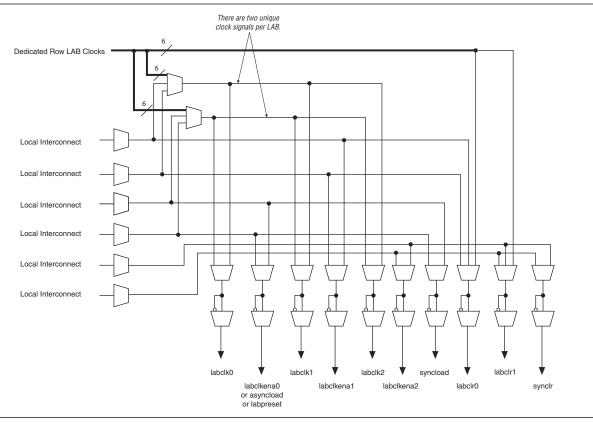

Figure 2–27 shows the LAB control signal generation circuit.

Figure 2–27. LAB-Wide Control Signals

## **Adaptive Logic Modules**

The basic building block of logic in the Arria GX architecture is the ALM. The ALM provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–28 shows a high-level block diagram of the Arria GX ALM while Figure 2–29 shows a detailed view of all the connections in the ALM.

## **PLLs and Clock Networks**

Arria GX devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

## **Global and Hierarchical Clocking**

Arria GX devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Arria GX devices.

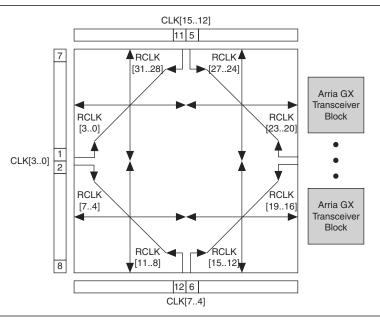

There are 12 dedicated clock pins (CLK [15..12] and CLK [7..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device except the right side, as shown in Figure 2–54 and Figure 2–55. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables or disables the clock to reduce power consumption. Table 2–16 lists the global and regional clock features.

Table 2-16. Global and Regional Clock Features

| Feature                        | Global Clocks                                                    | Regional Clocks                                                  |

|--------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| Number per device              | 16                                                               | 32                                                               |

| Number available per quadrant  | 16                                                               | 8                                                                |

| Sources                        | Clock pins, PLL outputs, core routings, inter-transceiver clocks | Clock pins, PLL outputs, core routings, inter-transceiver clocks |

| Dynamic clock source selection | ~                                                                | _                                                                |

| Dynamic enable/disable         | <b>✓</b>                                                         | ~                                                                |

#### **Global Clock Network**

These clocks drive throughout the entire device, feeding all device quadrants. GCLK networks can be used as clock sources for all resources in the device IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–54 shows the 12 dedicated CLK pins driving global clock networks.

Figure 2-55. Regional Clocks

#### **Dual-Regional Clock Network**

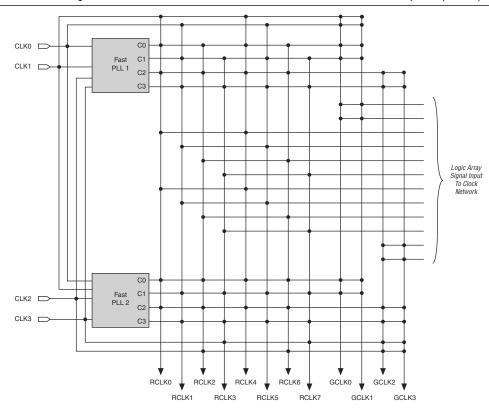

A single source (CLK pin or PLL output) can generate a dual-RCLK by driving two RCLK network lines in adjacent quadrants (one from each quadrant), which allows logic that spans multiple quadrants to use the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–56. Corner PLLs cannot drive dual-regional clocks.

Figure 2–62. Global and Regional Clock Connections from Center Clock Pins and Fast PLL Outputs (Note 1)

#### Note to Figure 2-62:

(1) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. A dedicated clock input pin or other PLL must drive the global or regional source. The source cannot be driven by internally generated logic before driving the fast PLL.

Table 2–21. Global and Regional Clock Connections from Bottom Clock Pins and Enhanced PLL Outputs

| Bottom Side Global and<br>Regional Clock Network<br>Connectivity | DILCIK   | CLK4     | CLK5     | СЦК      | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15 |

|------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------|

| Clock pins                                                       |          |          |          |          |          |          |          |          |          |          |          |          |        |

| CLK4p                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _        | _      |

| CLK5p                                                            | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        | _        | ✓        | _        | _        | _        | <b>✓</b> | _        | _      |

| CLK6p                                                            | ~        | _        | _        | <b>✓</b> | ✓        | _        |          | <b>✓</b> | _        | _        | _        | <b>✓</b> |        |

| CLK7p                                                            | <b>✓</b> | _        | _        | <b>✓</b> | ✓        | _        |          | _        | <b>✓</b> | _        | _        | _        | ✓      |

| CLK4n                                                            | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> |          | _        | _        | <b>✓</b> | _        | _        |        |

| CLK5n                                                            | _        | _        | ~        | _        | _        | _        | <b>✓</b> | _        | _        | _        | ~        | _        |        |

| CLK6n                                                            | _        | _        | _        | <b>✓</b> | _        | _        |          | <b>✓</b> | _        | _        | _        | <b>✓</b> | _      |

| CLK7n                                                            | _        | _        | _        | _        | ✓        | _        |          | _        | <b>✓</b> | _        | _        | _        | ✓      |

| Drivers from internal logic                                      | ;        |          |          |          |          |          |          |          | 1        |          | •        |          |        |

| GCLKDRV0                                                         | _        | <b>✓</b> | _        | _        | _        | _        | _        | _        | _        | _        | _        | _        |        |

| GCLKDRV1                                                         | _        | _        | ~        | _        | _        | _        |          | _        | _        | _        | _        | _        | _      |

| GCLKDRV2                                                         | _        | _        | _        | <b>✓</b> | _        | _        |          | _        | _        | _        | _        | _        | _      |

| GCLKDRV3                                                         | _        | _        | _        | _        | <b>✓</b> | _        |          | _        | _        | _        | _        | _        | _      |

| RCLKDRV0                                                         | _        | _        | _        | _        | _        | <b>✓</b> |          | _        | _        | <b>✓</b> | _        | _        | _      |

| RCLKDRV1                                                         | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _      |

| RCLKDRV2                                                         | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _      |

| RCLKDRV3                                                         | _        | _        | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | _        | ✓      |

| RCLKDRV4                                                         | _        | _        | _        | _        | _        | <b>✓</b> |          | _        | _        | <b>✓</b> | _        | _        | _      |

| RCLKDRV5                                                         | _        | _        | _        | _        | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _      |

| RCLKDRV6                                                         | _        | _        | _        | _        | _        | _        |          | ✓        | _        | _        | _        | ✓        | _      |

| RCLKDRV7                                                         | _        | _        | _        | _        | _        | _        |          | _        | <b>✓</b> | _        | _        | _        | ✓      |

| Enhanced PLL 6 outputs                                           | •        |          |          |          | •        |          |          |          |          |          | •        |          |        |

| c0                                                               | <b>✓</b> | <b>✓</b> | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _        | _      |

| c1                                                               | ~        | <b>✓</b> | ~        | _        | _        | _        | <b>~</b> | _        | _        | _        | ~        | _        |        |

| c2                                                               | <b>✓</b> | _        | _        | <b>✓</b> | ✓        | _        |          | ✓        | _        | _        |          | <b>✓</b> |        |

| c3                                                               | <b>✓</b> | _        | _        | <b>✓</b> | ✓        | _        |          | _        | <b>✓</b> | _        | _        | _        | ✓      |

| c4                                                               | <b>✓</b> | _        | _        | _        | _        | <b>✓</b> |          | <b>✓</b> | _        | ~        | _        | <b>✓</b> | _      |

| c5                                                               | ~        | _        | _        | _        | _        | _        | <b>\</b> | _        | <b>✓</b> | _        | ~        | _        | ✓      |

| Enhanced PLL 12 outputs                                          |          |          |          |          |          |          |          |          | 1        |          | •        |          |        |

| c0                                                               | _        | <b>✓</b> | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _        | _      |

| c1                                                               | _        | <b>✓</b> | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        |        |

| c2                                                               | _        | _        | _        | <b>✓</b> | <b>✓</b> | _        | _        | <b>✓</b> | _        | _        | _        | <b>✓</b> | _      |

| c3                                                               | _        | _        | _        | <b>✓</b> | <b>✓</b> | _        | _        | _        | <b>✓</b> | _        | _        | _        | ✓      |

| c4                                                               | _        | _        | _        | _        | _        | <b>✓</b> | _        | <b>✓</b> | _        | ~        | _        | <b>✓</b> | _      |

| c5                                                               | _        | _        | _        | _        | _        | _        | ✓        | _        | <b>✓</b> | _        | <b>✓</b> | _        | ✓      |

For the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level, refer to the *DC & Switching Characteristics* chapter.

## **Programmable Pull-Up Resistor**

Each Arria GX device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the  $V_{CCIO}$  level of the output pin's bank.

## **Advanced I/O Standard Support**

Arria GX device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- Differential 1.5-V HSTL class I and II

- Differential 1.8-V HSTL class I and II

- Differential SSTL-18 class I and II

- Differential SSTL-2 class I and II

- 1.2-V HSTL class I and II

- 1.5-V HSTL class I and II

- 1.8-V HSTL class I and II

- SSTL-2 class I and II

- SSTL-18 class I and II

device, PLL 1 can drive a maximum of 16 transmitter channels in I/O Bank 2 or a maximum of 29 transmitter channels in I/O Banks 1 and 2. The Quartus II software can also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

For more information, refer to the "Differential Pin Placement Guidelines" section in the *High-Speed Differential I/O Interfaces with DPA in Arria GX Devices* chapter.

**Table 2–30.** EP1AGX20 Device Differential Channels (Note 1)

| Package               | Transmitter/Desciver | Total Channels | Center Fast PLLs |      |  |  |

|-----------------------|----------------------|----------------|------------------|------|--|--|

|                       | Transmitter/Receiver | Total Channels | PLL1             | PLL2 |  |  |

| 484-pin FineLine BGA  | Transmitter          | 29             | 16               | 13   |  |  |

|                       | II alistilittei      | 29             | 13               | 16   |  |  |

|                       | Receiver             | 31 -           | 17               | 14   |  |  |

|                       | neceivei             | 31             | 14               | 17   |  |  |

|                       | Transmitter          | 20             | 16               | 13   |  |  |

| 790 nin Einal ina CRA | II alistillitti      | 29             |                  | 16   |  |  |

| 780-pin FineLine GBA  | Receiver             | 31 -           | 17               | 14   |  |  |

|                       | Leceivei             | ٥١<br>-        | 14               | 17   |  |  |

#### Note to Table 2-30:

Table 2–31.

EP1AGX35 Device Differential Channels (Note 1)

| Package               | Transmitter/Deceiver | Total Ohamada  | Center Fast PLLs |      |  |

|-----------------------|----------------------|----------------|------------------|------|--|

|                       | Transmitter/Receiver | Total Channels | PLL1             | PLL2 |  |

| 484-pin FineLine BGA  | Transmitter          | 29             | 16               | 13   |  |

|                       |                      |                | 13               | 16   |  |

|                       | Receiver             | 31             | 17               | 14   |  |

|                       |                      |                | 14               | 17   |  |

|                       | Transmitter          | 29             | 16               | 13   |  |

| 700 nin Einal ina DCA |                      |                | 13               | 16   |  |

| 780-pin FineLine BGA  | Receiver             | 31             | 17               | 14   |  |

|                       |                      |                | 14               | 17   |  |

#### Note to Table 2-31:

<sup>(1)</sup> The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

<sup>(1)</sup> The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

In addition to the number of configuration methods supported, Arria GX devices also offer decompression and remote system upgrade features. The decompression feature allows Arria GX FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of Arria GX designs. For more information, refer to "Configuration Schemes" on page 3–5.

## **Operating Modes**

The Arria GX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow you to reconfigure Arria GX devices in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, re-initializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select power-on reset (POR) delay times of 12 ms or 100 ms during power up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 12 ms.

The nio\_pullup pin is a dedicated input that chooses whether the internal pull-up resistors on the user I/O pins and dual-purpose configuration I/O pins (ncso, Asdo, Data[7..0], nws, nrs, rdynbsy, ncs, cs, runlu, pgm[2..0], clkusr, Init\_done, dev\_oe, dev\_clr) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-up resistors, while a logic low turns them on.

Arria GX devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the following configuration pins: nCONFIG, DCLK (when used as an input), nIO\_PULLUP, DATA [7 . . 0] , RUnLU, nCE, nWS, nRS, CS, nCS, and CLKUSR. The  $V_{CCSEL}$  pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$  voltage, you do not have to take the VIL and VIH levels driven to the configuration inputs into consideration. The configuration input pins, nCONFIG, DCLK (when used as an input), nIO\_PULLUP, RUnLU, nCE, nWS, nRS, CS, nCS, and CLKUSR, have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The  $V_{CCSEL}$  input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCIO}$ .

Table 4-6. Arria GX Transceiver Block AC Specification (Part 1 of 3)

| Symbol / Description                                                          | Conditions                 | –6 Speed   | Units         |               |      |

|-------------------------------------------------------------------------------|----------------------------|------------|---------------|---------------|------|

| •                                                                             |                            | Min        | Тур           | Max           |      |

| Reference clock                                                               |                            | •          |               | ·             |      |

| Input reference clock frequency                                               | _                          | 50         | _             | 622.08        | MHz  |

| Absolute $V_{MAX}$ for a REFCLK Pin                                           | _                          | _          | _             | 3.3           | V    |

| Absolute $V_{MIN}$ for a REFCLK Pin                                           | _                          | -0.3       | _             | _             | V    |

| Rise/Fall time                                                                | _                          | _          | 0.2           | _             | UI   |

| Duty cycle                                                                    | _                          | 45         | _             | 55            | %    |

| Peak to peak differential input voltage V <sub>ID</sub> (diff p-p)            | _                          | 200        | _             | 2000          | mV   |

| Spread spectrum clocking (1)                                                  | 0 to -0.5%                 | 30         | _             | 33            | kHz  |

| On-chip termination resistors                                                 | _                          |            | 115 ± 20%     | <u> </u>      | Ω    |

| V <sub>ICM</sub> (AC coupled)                                                 | _                          |            | 1200 ± 5%     |               | mV   |

| V <sub>ICM</sub> (DC coupled) <i>(2)</i>                                      | PCI Express<br>(PIPE) mode | 0.25       | _             | 0.55          | V    |

| RREFB                                                                         | _                          |            | 2000 +/-1%    |               |      |

| Transceiver Clocks                                                            |                            |            |               |               |      |

| Calibration block clock frequency                                             | _                          | 10         | _             | 125           | MHz  |

| Calibration block minimum power-down pulse width                              | _                          | 30         | _             | _             | ns   |

| fixedclk clock frequency (3)                                                  | _                          |            | 125 ±10%      |               | MHz  |

| reconfig clock frequency                                                      | SDI mode                   | 2.5        | _             | 50            | MHz  |

| Transceiver block minimum power-down pulse width                              | _                          | 100 —      |               | _             | ns   |

| Receiver                                                                      |                            |            |               |               |      |

| Data rate                                                                     | _                          | 600        | _             | 3125          | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin (4)                              | _                          | _          | _             | 2.0           | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                  | _                          | -0.4       | _             | _             | V    |

| Maximum peak-to-peak differential input voltage $V_{ID}$ (diff p-p)           | Vicm = 0.85 V              | _          | _             | 3.3           | V    |

| Minimum peak-to-peak differential input<br>voltage V <sub>ID</sub> (diff p-p) | DC Gain = 3 dB             | 160        | _             | _             | mV   |

| On-chip termination resistors                                                 | _                          |            | 100±15%       | ·             | Ω    |

| V (15)                                                                        | Vicm = 0.85 V<br>setting   | 850 ± 10%  | 850 ± 10%     | 850 ± 10%     | mV   |

| V <sub>ICM</sub> (15)                                                         | Vicm = 1.2 V<br>setting    | 1200 ± 10% | 1200 ±<br>10% | 1200 ±<br>10% | mV   |

|                                                                               | BW = Low                   | _          | 30            | _             |      |

| Bandwidth at 3.125 Gbps                                                       | BW = Med                   | _          | 40            | _             | MHz  |

|                                                                               | BW = High                  | _          | 50            | _             |      |

Table 4–36. 1.8-V HSTL Class I Specifications

| Symbol               | Parameter                   | Conditions                         | Minimum                 | Typical | Maximum                | Units |

|----------------------|-----------------------------|------------------------------------|-------------------------|---------|------------------------|-------|

| V <sub>CCIO</sub>    | Output supply voltage       | _                                  | 1.71                    | 1.80    | 1.89                   | V     |

| $V_{REF}$            | Input reference voltage     | _                                  | 0.85                    | 0.90    | 0.95                   | V     |

| V <sub>TT</sub>      | Termination voltage         | _                                  | 0.85                    | 0.90    | 0.95                   | V     |

| V <sub>IH</sub> (DC) | DC high-level input voltage | _                                  | V <sub>REF</sub> + 0.1  | _       | _                      | V     |

| V <sub>IL</sub> (DC) | DC low-level input voltage  | _                                  | -0.3                    | _       | V <sub>REF</sub> - 0.1 | V     |

| V <sub>IH</sub> (AC) | AC high-level input voltage | _                                  | V <sub>REF</sub> + 0.2  | _       | _                      | V     |

| V <sub>IL</sub> (AC) | AC low-level input voltage  | _                                  | _                       | _       | V <sub>REF</sub> - 0.2 | V     |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 8 mA <i>(1)</i>  | V <sub>CCIO</sub> - 0.4 | _       | _                      | V     |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OH</sub> = -8 mA <i>(1)</i> | _                       | _       | 0.4                    | V     |

#### Note to Table 4-36:

**Table 4–37.** 1.8-V HSTL Class II Specifications

| Symbol               | Parameter                   | Conditions                         | Minimum                 | Typical | Maximum                | Units |

|----------------------|-----------------------------|------------------------------------|-------------------------|---------|------------------------|-------|

| V <sub>CCIO</sub>    | Output supply voltage       | _                                  | 1.71                    | 1.80    | 1.89                   | V     |

| V <sub>REF</sub>     | Input reference voltage     | _                                  | 0.85                    | 0.90    | 0.95                   | V     |

| V <sub>TT</sub>      | Termination voltage         | _                                  | 0.85                    | 0.90    | 0.95                   | V     |

| V <sub>IH</sub> (DC) | DC high-level input voltage | _                                  | V <sub>REF</sub> + 0.1  | _       | _                      | V     |

| V <sub>IL</sub> (DC) | DC low-level input voltage  | _                                  | -0.3                    | _       | V <sub>REF</sub> - 0.1 | ٧     |

| V <sub>IH</sub> (AC) | AC high-level input voltage | _                                  | V <sub>REF</sub> + 0.2  | _       | _                      | V     |

| V <sub>IL</sub> (AC) | AC low-level input voltage  | _                                  | _                       | _       | V <sub>REF</sub> - 0.2 | V     |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 16 mA <i>(1)</i> | V <sub>CCIO</sub> - 0.4 | _       | _                      | V     |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -16 \text{ mA } (1)$     | _                       | _       | 0.4                    | V     |

#### Note to Table 4-37:

Table 4-38. 1.8-V HSTL Class I & II Differential Specifications

| Symbol                | Parameter                           | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------------------|---------|---------|---------|-------|

| V <sub>CCIO</sub>     | I/O supply voltage                  | 1.71    | 1.80    | 1.89    | V     |

| V <sub>DIF</sub> (DC) | DC input differential voltage       | 0.2     | _       | _       | V     |

| V <sub>CM</sub> (DC)  | DC common mode input voltage        | 0.78    | _       | 1.12    | V     |

| V <sub>DIF</sub> (AC) | AC differential input voltage       | 0.4     | _       | _       | V     |

| V <sub>ox</sub> (AC)  | AC differential cross point voltage | 0.68    | _       | 0.9     | V     |

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard, as shown in the Arria GX Architecture chapter.

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard, as shown in the Arria GX Architecture chapter in volume 1 of the Arria GX Device Handbook.

For more information about PowerPlay tools, refer to the *PowerPlay Early Power Estimator and PowerPlay Power Analyzer* page and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

For typical I<sub>CC</sub> standby specifications, refer to Table 4–14 on page 4–14.

## I/O Timing Model

The DirectDrive technology and MultiTrack interconnect ensures predictable performance, accurate simulation, and accurate timing analysis across all Arria GX device densities and speed grades. This section describes and specifies the performance of I/Os.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

The timing numbers listed in the tables of this section are extracted from the Quartus II software version 7.1.

### **Preliminary, Correlated, and Final Timing**

Timing models can have either preliminary, correlated, or final status. The Quartus II software issues an informational message during design compilation if the timing models are preliminary. Table 4–43 lists the status of the Arria GX device timing models.

- Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

- Correlated numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

- Final timing numbers are based on complete correlation to actual devices and addressing any minor deviations from the correlated timing model. When the timing models are final, all or most of the Arria GX family devices have been completely characterized and no further changes to the timing model are expected.

**Table 4–43.** Arria GX Device Timing Model Status

| Device   | Preliminary | Correlated | Final    |

|----------|-------------|------------|----------|

| EP1AGX20 | _           | _          | <b>✓</b> |

| EP1AGX35 | _           | _          | <b>✓</b> |

| EP1AGX50 | _           | _          | <b>✓</b> |

| EP1AGX60 | _           | _          | <b>✓</b> |

| EP1AGX90 | _           | _          | ~        |

Table 4–55.

EP1AGX35 Column Pins Input Timing Parameters (Part 3 of 3)

| I/O Chandard        | Olook       | Davamatav       | Fast       | Corner     | –6 Speed | II.u.i.t.a |

|---------------------|-------------|-----------------|------------|------------|----------|------------|

| I/O Standard        | Clock       | Parameter       | Industrial | Commercial | Grade    | Units      |

|                     | CCT IZ      | t <sub>su</sub> | 1.131      | 1.131      | 2.607    | ns         |

| 1.5-V HSTL CLASS I  | GCLK        | t <sub>H</sub>  | -1.026     | -1.026     | -2.330   | ns         |

| 1.3-V HOTE GLASS I  | GCLK PLL    | t <sub>su</sub> | 2.573      | 2.573      | 5.713    | ns         |

|                     | GCLK PLL    | t <sub>H</sub>  | -2.468     | -2.468     | -5.436   | ns         |

|                     | GCLK        | t <sub>su</sub> | 1.132      | 1.132      | 2.607    | ns         |

| 1.5-V HSTL CLASS II | GCLK        | t <sub>H</sub>  | -1.027     | -1.027     | -2.330   | ns         |

| 1.5-V HOTE GLASS II | GCLK PLL    | t <sub>su</sub> | 2.574      | 2.574      | 5.715    | ns         |

|                     | GCLK PLL    | t <sub>H</sub>  | -2.469     | -2.469     | -5.438   | ns         |

|                     | CCLIV       | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns         |

| 3.3-V PCI           | GCLK        | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns         |

| 3.3-V FUI           | GCLK PLL    | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns         |

|                     |             | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns         |

|                     | COT IZ      | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns         |

| 3.3-V PCI-X         | GCLK        | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns         |

| J.J-V FUI-A         | GCLK PLL    | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns         |

|                     | GCTV STT    | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns         |

|                     | COL V       | t <sub>su</sub> | 1.106      | 1.106      | 2.489    | ns         |

| LVDC                | GCLK        | t <sub>H</sub>  | -1.001     | -1.001     | -2.212   | ns         |

| LVDS                | CCL IV DI I | t <sub>su</sub> | 2.530      | 2.530      | 5.564    | ns         |

|                     | GCLK PLL    | t <sub>H</sub>  | -2.425     | -2.425     | -5.287   | ns         |

|                     |             |                 |            |            |          |            |

Table 4–56 lists I/O timing specifications.

Table 4-56. EP1AGX35 Row Pins Output Timing Parameters (Part 1 of 3)

| I/O Standard    | Drive<br>Strength | Clock    | Parameter       | Fast Model |            | –6 Speed |       |

|-----------------|-------------------|----------|-----------------|------------|------------|----------|-------|

|                 |                   |          |                 | Industrial | Commercial | Grade    | Units |

| 3.3-V LVTTL     | 4 mA              | GCLK     | t <sub>co</sub> | 2.904      | 2.904      | 6.699    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.485      | 1.485      | 3.627    | ns    |

| 3.3-V LVTTL     | 8 mA              | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns    |

| 3.3-V LVTTL     | 12 mA             | GCLK     | t <sub>co</sub> | 2.720      | 2.720      | 6.022    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.301      | 1.301      | 2.950    | ns    |

| 3.3-V<br>LVCMOS | 4 mA              | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns    |

| 3.3-V<br>LVCMOS | 8 mA              | GCLK     | t <sub>co</sub> | 2.670      | 2.670      | 5.753    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.251      | 1.251      | 2.681    | ns    |

| 2.5 V           | 4 mA              | GCLK     | t <sub>co</sub> | 2.759      | 2.759      | 6.033    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.340      | 1.340      | 2.961    | ns    |

Table 4-57. EP1AGX35 Column Pins Output Timing Parameters (Part 2 of 4)

| I/O Standard    | Drive<br>Strength | Clock    | Parameter       | Fast Corner |            | –6 Speed | 11    |

|-----------------|-------------------|----------|-----------------|-------------|------------|----------|-------|

|                 |                   |          |                 | Industrial  | Commercial | Grade    | Units |

| 3.3-V<br>LVCMOS | 24 mA             | GCLK     | t <sub>co</sub> | 2.627       | 2.627      | 5.724    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.185       | 1.185      | 2.618    | ns    |

| 2.5 V           | 4 mA              | GCLK     | t <sub>co</sub> | 2.726       | 2.726      | 6.201    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.284       | 1.284      | 3.095    | ns    |

| 2.5 V           | 8 mA              | GCLK     | t <sub>co</sub> | 2.674       | 2.674      | 5.939    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.232       | 1.232      | 2.833    | ns    |

| 2.5 V           | 12 mA             | GCLK     | t <sub>co</sub> | 2.653       | 2.653      | 5.822    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.211       | 1.211      | 2.716    | ns    |

| 2.5 V           | 16 mA             | GCLK     | t <sub>co</sub> | 2.635       | 2.635      | 5.748    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.193       | 1.193      | 2.642    | ns    |

| 1.8 V           | 2 mA              | GCLK     | t <sub>co</sub> | 2.766       | 2.766      | 7.193    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.324       | 1.324      | 4.087    | ns    |

| 1.8 V           | 4 mA              | GCLK     | t <sub>co</sub> | 2.771       | 2.771      | 6.419    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.329       | 1.329      | 3.313    | ns    |

| 1.8 V           | 6 mA              | GCLK     | t <sub>co</sub> | 2.695       | 2.695      | 6.155    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.253       | 1.253      | 3.049    | ns    |

| 1.8 V           | 8 mA              | GCLK     | t <sub>co</sub> | 2.697       | 2.697      | 6.064    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.255       | 1.255      | 2.958    | ns    |

| 1.8 V           | 10 mA             | GCLK     | t <sub>co</sub> | 2.651       | 2.651      | 5.987    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.209       | 1.209      | 2.881    | ns    |

| 1.8 V           | 12 mA             | GCLK     | t <sub>co</sub> | 2.652       | 2.652      | 5.930    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.210       | 1.210      | 2.824    | ns    |

| 1.5 V           | 2 mA              | GCLK     | t <sub>co</sub> | 2.746       | 2.746      | 6.723    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.304       | 1.304      | 3.617    | ns    |

| 1.5 V           | 4 mA              | GCLK     | t <sub>co</sub> | 2.682       | 2.682      | 6.154    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.240       | 1.240      | 3.048    | ns    |

| 1.5 V           | 6 mA              | GCLK     | t <sub>co</sub> | 2.685       | 2.685      | 6.036    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.243       | 1.243      | 2.930    | ns    |

| 1.5 V           | 8 mA              | GCLK     | t <sub>co</sub> | 2.644       | 2.644      | 5.983    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.202       | 1.202      | 2.877    | ns    |

| SSTL-2          | 8 mA              | GCLK     | t <sub>co</sub> | 2.629       | 2.629      | 5.762    | ns    |

| CLASS I         |                   | GCLK PLL | t <sub>co</sub> | 1.184       | 1.184      | 2.650    | ns    |

| SSTL-2          | 12 mA             | GCLK     | t <sub>co</sub> | 2.612       | 2.612      | 5.712    | ns    |

| CLASS I         |                   | GCLK PLL | t <sub>co</sub> | 1.167       | 1.167      | 2.600    | ns    |

| SSTL-2          | 16 mA             | GCLK     | t <sub>co</sub> | 2.590       | 2.590      | 5.639    | ns    |

| CLASS II        |                   | GCLK PLL | t <sub>co</sub> | 1.145       | 1.145      | 2.527    | ns    |

| SSTL-2          | 20 mA             | GCLK     | t <sub>co</sub> | 2.591       | 2.591      | 5.626    | ns    |

| CLASS II        |                   | GCLK PLL | t <sub>co</sub> | 1.146       | 1.146      | 2.514    | ns    |

Table 4–90 lists clock timing specifications.

**Table 4–90.** EP1AGX50 Row Pins Regional Clock Timing Parameters

| Parameter            | Fast       | Model      | 6 Speed Crede    | Units |  |

|----------------------|------------|------------|------------------|-------|--|

|                      | Industrial | Commercial | – –6 Speed Grade |       |  |

| t <sub>CIN</sub>     | 1.653      | 1.653      | 3.841            | ns    |  |

| t <sub>cour</sub>    | 1.651      | 1.651      | 3.839            | ns    |  |

| t <sub>PLLCIN</sub>  | 0.245      | 0.245      | 0.755            | ns    |  |

| t <sub>PLLCOUT</sub> | 0.245      | 0.245      | 0.755            | ns    |  |

### **EP1AGX60 Clock Timing Parameters**

Table 4–91 to Table 4–92 on page 4–82 list the GCLK clock timing parameters for EP1AGX60 devices.

Table 4–91 lists clock timing specifications.

**Table 4–91.** EP1AGX60 Row Pins Global Clock Timing Parameters

| Parameter            | Fast       | Model      | -6 Speed Grade | Units |  |

|----------------------|------------|------------|----------------|-------|--|

|                      | Industrial | Commercial | -o speeu draue | Units |  |

| t <sub>CIN</sub>     | 1.531      | 1.531      | 3.593          | ns    |  |

| t <sub>cour</sub>    | 1.536      | 1.536      | 3.587          | ns    |  |

| t <sub>PLLCIN</sub>  | -0.023     | -0.023     | 0.188          | ns    |  |

| t <sub>PLLCOUT</sub> | -0.018     | -0.018     | 0.182          | ns    |  |

Table 4–92 lists clock timing specifications.

**Table 4–92.** EP1AGX60 Row Pins Global Clock Timing Parameters

| Parameter            | Fast       | Model      | C Cross d Orresdo | Units |  |

|----------------------|------------|------------|-------------------|-------|--|

|                      | Industrial | Commercial | -6 Speed Grade    |       |  |

| t <sub>CIN</sub>     | 1.792      | 1.792      | 4.165             | ns    |  |

| t <sub>cour</sub>    | 1.792      | 1.792      | 4.165             | ns    |  |

| t <sub>PLLCIN</sub>  | 0.238      | 0.238      | 0.758             | ns    |  |

| t <sub>PLLCOUT</sub> | 0.238      | 0.238      | 0.758             | ns    |  |

**Table 4–105.** Arria GX Maximum Output Toggle Rate for Column I/O Pins (Part 3 of 3)

| I/O Standards       | Drive Strength | -6 Speed Grade | Units |

|---------------------|----------------|----------------|-------|

|                     | 16 mA          | 420            | MHz   |

| 1.8-V HSTL CLASS II | 18 mA          | 467            | MHz   |

|                     | 20 mA          | 514            | MHz   |

|                     | 4 mA           | 280            | MHz   |

|                     | 6 mA           | 420            | MHz   |

| 1.5-V HSTL CLASS I  | 8 mA           | 561            | MHz   |

|                     | 10 mA          | 607            | MHz   |

|                     | 12 mA          | 654            | MHz   |

|                     | 16 mA          | 514            | MHz   |

| 1.5-V HSTL CLASS II | 18 mA          | 561            | MHz   |

|                     | 20 mA          | 561            | MHz   |

| 3.3-V PCI           | _              | 626            | MHz   |

| 3.3-V PCI-X         | _              | 626            | MHz   |

Table 4–106 shows the maximum output clock toggle rates for Arria GX device row I/O pins.

Table 4–106. Arria GX Maximum Output Toggle Rate for Row I/O Pins

| I/O Standards   | Drive Strength | -6 Speed Grade | Units |

|-----------------|----------------|----------------|-------|

|                 | 4 mA           | 196            | MHz   |

| 3.3-V LVTTL     | 8 mA           | 303            | MHz   |

|                 | 12 mA          | 393            | MHz   |

| 3.3-V LVCMOS    | 4 mA           | 215            | MHz   |

| 3.3-V LVOIVIOS  | 8 mA           | 411            | MHz   |

|                 | 4 mA           | 168            | MHz   |

| 2.5 V           | 8 mA           | 355            | MHz   |

|                 | 12 mA          | 514            | MHz   |

|                 | 2 mA           | 97             | MHz   |

| 1.8 V           | 4 mA           | 215            | MHz   |

| 1.0 V           | 6 mA           | 336            | MHz   |

|                 | 8 mA           | 486            | MHz   |

| 1.5 V           | 2 mA           | 168            | MHz   |

| 1.5 V           | 4 mA           | 303            | MHz   |

| SSTL-2 CLASS I  | 8 mA           | 280            | MHz   |

| 331L-2 ULA331   | 12 mA          | 327            | MHz   |

| SSTL-2 CLASS II | 16 mA          | 280            | MHz   |

|                 | 4 mA           | 140            | MHz   |

| SSTL-18 CLASS I | 6 mA           | 186            | MHz   |

| 331L-10 0LA331  | 8 mA           | 280            | MHz   |

|                 | 10 mA          | 373            | MHz   |