Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1079                                                       |

| Number of Logic Elements/Cells | 21580                                                      |

| Total RAM Bits                 | 1229184                                                    |

| Number of I/O                  | 341                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1agx20cf780c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each transceiver channel is full-duplex and consists of a transmitter channel and a receiver channel.

The transmitter channel contains the following sub-blocks:

- Transmitter phase compensation first-in first-out (FIFO) buffer

- Byte serializer (optional)

- 8B/10B encoder (optional)

- Serializer (parallel-to-serial converter)

- Transmitter differential output buffer

The receiver channel contains the following:

- Receiver differential input buffer

- Receiver lock detector and run length checker

- CRU

- Deserializer

- Pattern detector

- Word aligner

- Lane deskew

- Rate matcher (optional)

- 8B/10B decoder (optional)

- Byte deserializer (optional)

- Receiver phase compensation FIFO buffer

You can configure the transceiver channels to the desired functional modes using the ALT2GXB MegaCore instance in the Quartus<sup>®</sup> II MegaWizard<sup>™</sup> Plug-in Manager for the Arria GX device family. Depending on the selected functional mode, the Quartus II software automatically configures the transceiver channels to employ a subset of the sub-blocks listed above.

#### **Transmitter Path**

This section describes the data path through the Arria GX transmitter. The sub-blocks are described in order from the PLD-transmitter parallel interface to the serial transmitter buffer.

#### **Clock Multiplier Unit**

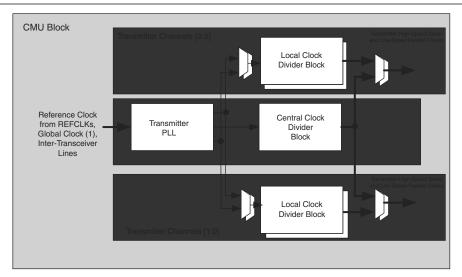

Each transceiver block has a clock multiplier unit (CMU) that takes in a reference clock and synthesizes two clocks: a high-speed serial clock to serialize the data and a low-speed parallel clock to clock the transmitter digital logic (PCS).

The CMU is further divided into three sub-blocks:

- One transmitter PLL

- One central clock divider block

- Four local clock divider blocks (one per channel)

Figure 2–3 shows the block diagram of the clock multiplier unit.

Figure 2-3. Clock Multiplier Unit

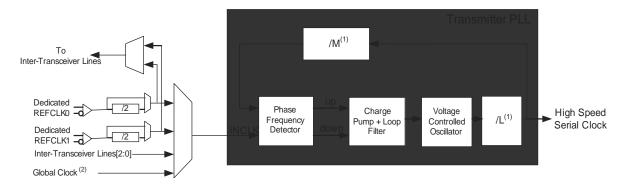

The transmitter PLL multiplies the input reference clock to generate the high-speed serial clock required to support the intended protocol. It implements a half-rate voltage controlled oscillator (VCO) that generates a clock at half the frequency of the serial data rate for which it is configured.

Figure 2–4 shows the block diagram of the transmitter PLL.

Figure 2-4. Transmitter PLL

#### Notes to Figure 2-4:

- (1) You only need to select the protocol and the available input reference clock frequency in the ALTGXB MegaWizard Plug-In Manager. Based on your selections, the MegaWizard Plug-In Manager automatically selects the necessary /M and /L dividers (clock multiplication factors).

- (2) The global clock line must be driven from an input pin only.

The reference clock input to the transmitter PLL can be derived from:

- One of two available dedicated reference clock input pins (REFCLK0 or REFCLK1) of the associated transceiver block

- PLD global clock network (must be driven directly from an input clock pin and cannot be driven by user logic or enhanced PLL)

#### **Transmit State Machine**

The transmit state machine operates in either PCI Express (PIPE) mode, XAUI mode, or GIGE mode, depending on the protocol used.

#### **GIGE Mode**

In GIGE mode, the transmit state machine converts all idle ordered sets (/K28.5/, /Dx.y/) to either /I1/ or /I2/ ordered sets. The /I1/ set consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-), followed by a neutral /D5.6/. The /I2/ set consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by [/K28.5/, /D21.5/] and [/K28.5/, /D2.2/], respectively). Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set.

#### **XAUI Mode**

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–3 lists the code conversion.

**Table 2–3.** On-Chip Termination Support by I/O Banks

| XGMII TXC | XGMII TXD                                | PCS Code-Group                           | Description             |

|-----------|------------------------------------------|------------------------------------------|-------------------------|

| 0         | 00 through FF                            | Dxx.y                                    | Normal data             |

| 1         | 07                                       | K28.0 or K28.3 or K28.5                  | Idle in   I             |

| 1         | 07                                       | K28.5                                    | Idle in   T             |

| 1         | 90                                       | K28.4                                    | Sequence                |

| 1         | FB                                       | K27.7                                    | Start                   |

| 1         | FD                                       | K29.7                                    | Terminate               |

| 1         | FE                                       | K30.7                                    | Error                   |

| 1         | Refer to IEEE 802.3 reserved code groups | Refer to IEEE 802.3 reserved code groups | Reserved code groups    |

| 1         | Other value                              | K30.7                                    | Invalid XGMII character |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $\times$ 7 +  $\times$ 6 + 1 polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups is automatically done by the transmit state machine.

#### **Serializer (Parallel-to-Serial Converter)**

The serializer block clocks in 8- or 10-bit encoded data from the 8B/10B encoder using the low-speed parallel clock and clocks out serial data using the high-speed serial clock from the central or local clock divider blocks. The serializer feeds the data LSB to MSB to the transmitter output buffer.

#### **Programmable Pre-Emphasis**

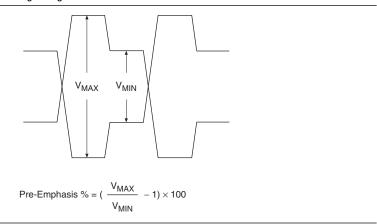

The programmable pre-emphasis module controls the output driver to boost high frequency components and compensate for losses in the transmission medium, as shown in Figure 2–10. Pre-emphasis is set statically using the ALTGXB megafunction.

Figure 2-10. Pre-Emphasis Signaling

Pre-emphasis percentage is defined as  $(V_{MAX}/V_{MIN}-1) \times 100$ , where  $V_{MAX}$  is the differential emphasized voltage (peak-to-peak) and  $V_{MIN}$  is the differential steady-state voltage (peak-to-peak).

#### PCI Express (PIPE) Receiver Detect

The Arria GX transmitter buffer has a built-in receiver detection circuit for use in PCI Express (PIPE) mode. This circuit provides the ability to detect if there is a receiver downstream by sending out a pulse on the channel and monitoring the reflection. This mode requires a tri-stated transmitter buffer (in electrical idle mode).

#### PCI Express (PIPE) Electric Idles (or Individual Transmitter Tri-State)

The Arria GX transmitter buffer supports PCI Express (PIPE) electrical idles. This feature is only active in PCI Express (PIPE) mode. The tx\_forceelecidle port puts the transmitter buffer in electrical idle mode. This port is available in all PCI Express (PIPE) power-down modes and has specific usage in each mode.

#### **Receiver Path**

This section describes the data path through the Arria GX receiver. The sub-blocks are described in order from the receiver buffer to the PLD-receiver parallel interface.

#### **Receiver Buffer**

The Arria GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standards at rates up to 3.125 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and 1.2 V common mode voltage for DC-coupled LVDS links.

- The voltage-controlled oscillator  $(V_{CO})$  operates at half rate.

- Programmable frequency multiplication W of 1, 4, 5, 8, 10, 16, 20, and 25. Not all settings are supported for any particular frequency.

- Two lock indication signals are provided. They are found in PFD mode (lock-to-reference clock), and PD (lock-to-data).

The CRU controls whether the receiver PLL locks to the input reference clock (lock-to-reference mode) or the incoming serial data (lock-to data mode). You can set the CRU to switch between lock-to-data and lock-to-reference modes automatically or manually. In automatic lock mode, the phase detector and dedicated parts per million (PPM) detector within each receiver channel control the switch between lock-to-data and lock-to-reference modes based on some pre-set conditions. In manual lock mode, you can control the switch manually using the rx\_locktorefclk and rx locktodata signals.

For more information, refer to the "Clock Recovery Unit" section in the *Arria GX Transceiver Protocol Support and Additional Features* chapter.

Table 2–4 lists the behavior of the CRU block with respect to the rx\_locktorefclk and rx locktodata signals.

Table 2-4. CRU Manual Lock Signals

| rx_locktorefclk | rx_locktodata CRU Mode |                         |  |  |

|-----------------|------------------------|-------------------------|--|--|

| 1               | 0                      | Lock-to-reference clock |  |  |

| Х               | 1                      | Lock-to-data            |  |  |

| 0               | 0                      | Automatic               |  |  |

If the rx\_locktorefclk and rx\_locktodata ports are not used, the default setting is automatic lock mode.

#### **Deserializer**

The deserializer block clocks in serial input data from the receiver buffer using the high-speed serial recovered clock and deserializes into 8- or 10-bit parallel data using the low-speed parallel recovered clock. The serial data is assumed to be received with LSB first, followed by MSB. It feeds the deserialized 8- or 10-bit data to the word aligner, as shown in Figure 2–14.

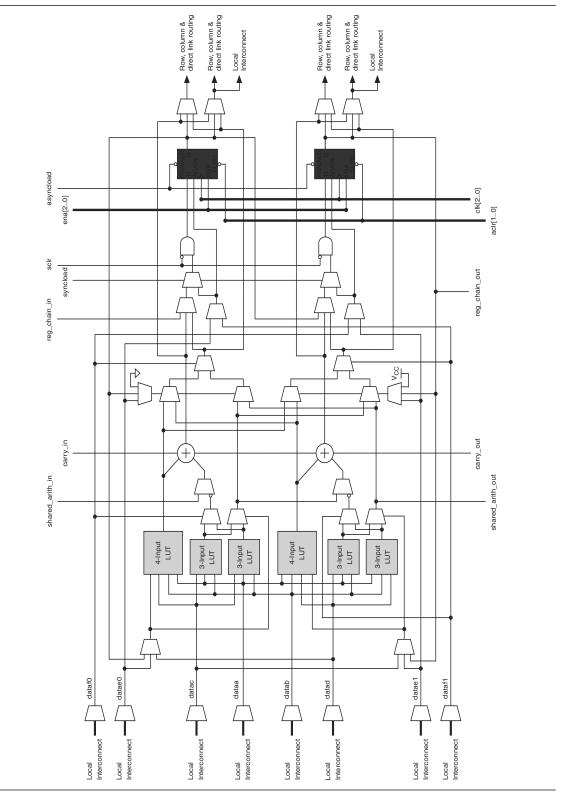

Figure 2-29. Arria GX ALM Details

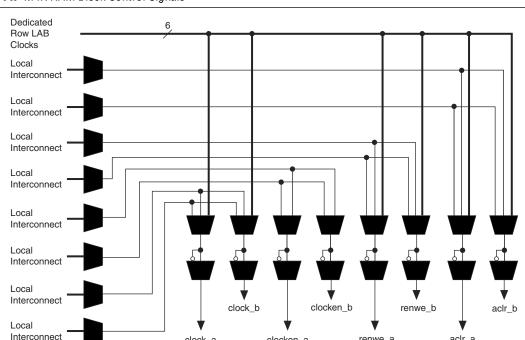

clock\_a

Figure 2-44. M4K RAM Block Control Signals

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM block are possible from the left adjacent LABs and another 16 are possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–45 shows the M4K RAM block to logic array interface.

clocken\_a

renwe\_a

aclr\_a

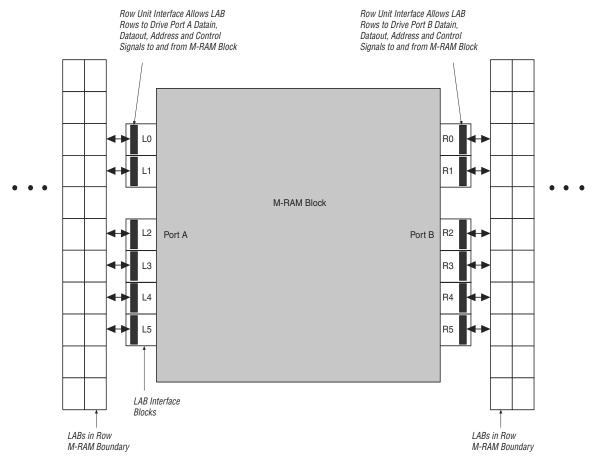

Figure 2–48. M-RAM Block LAB Row Interface (Note 1)

#### Note to Figure 2-48:

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

C4 Interconnect R4 and R24 Interconnects M-RAM Block LAB Up to 16 dataout\_a[] 16 datain\_a[] addressa[] addr\_ena\_a Up to 28 Direct Link renwe\_a Interconnects byteena<sub>A</sub>[] clocken\_a clock\_a aclr\_a Row Interface Block M-RAM Block to LAB Row Interface

Figure 2-49. M-RAM Row Unit Interface to Interconnect

Table 2–12 lists the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

**Table 2–12.** M-RAM Row Interface Unit Signals (Part 1 of 2)

Block Interconnect Region

| Unit Interface Block | Input Signals  | Output Signals  |

|----------------------|----------------|-----------------|

| LO                   | datain_a[140]  | dataout_a[110]  |

| LU                   | byteena_a[10]  |                 |

| L1                   | datain_a[2915] | dataout_a[2312] |

| LI                   | byteena_a[32]  |                 |

|                      | datain_a[3530] | dataout_a[3524] |

|                      | addressa[40]   |                 |

|                      | addr_ena_a     |                 |

| L2                   | clock_a        |                 |

|                      | clocken_a      |                 |

|                      | renwe_a        |                 |

|                      | aclr_a         |                 |

| L3                   | addressa[155]  | dataout_a[4736] |

| LJ                   | datain_a[4136] |                 |

For the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level, refer to the *DC & Switching Characteristics* chapter.

### **Programmable Pull-Up Resistor**

Each Arria GX device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) holds the output to the  $V_{CCIO}$  level of the output pin's bank.

### **Advanced I/O Standard Support**

Arria GX device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- Differential 1.5-V HSTL class I and II

- Differential 1.8-V HSTL class I and II

- Differential SSTL-18 class I and II

- Differential SSTL-2 class I and II

- 1.2-V HSTL class I and II

- 1.5-V HSTL class I and II

- 1.8-V HSTL class I and II

- SSTL-2 class I and II

- SSTL-18 class I and II

Table 2–25 describes the I/O standards supported by Arria GX devices.

Table 2-25. Arria GX Devices Supported I/O Standards

| I/O Standard                               | Туре               | Input Reference<br>Voltage<br>(V <sub>REF</sub> ) (V) | Output Supply<br>Voltage<br>(V <sub>ccio</sub> ) (V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) (V) |

|--------------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------|

| LVTTL                                      | Single-ended       | _                                                     | 3.3                                                  | _                                                      |

| LVCMOS                                     | Single-ended       | _                                                     | 3.3                                                  | _                                                      |

| 2.5 V                                      | Single-ended       | _                                                     | 2.5                                                  | _                                                      |

| 1.8 V                                      | Single-ended       | _                                                     | 1.8                                                  | _                                                      |

| 1.5-V LVCMOS                               | Single-ended       | _                                                     | 1.5                                                  | _                                                      |

| 3.3-V PCI                                  | Single-ended       | _                                                     | 3.3                                                  | _                                                      |

| 3.3-V PCI-X mode 1                         | Single-ended       | _                                                     | 3.3                                                  | _                                                      |

| LVDS                                       | Differential       | _                                                     | 2.5 (3)                                              | _                                                      |

| LVPECL (1)                                 | Differential       | _                                                     | 3.3                                                  | _                                                      |

| HyperTransport technology                  | Differential       | _                                                     | 2.5 (3)                                              | _                                                      |

| Differential 1.5-V HSTL class I and II (2) | Differential       | 0.75                                                  | 1.5                                                  | 0.75                                                   |

| Differential 1.8-V HSTL class I and II (2) | Differential       | 0.90                                                  | 1.8                                                  | 0.90                                                   |

| Differential SSTL-18 class I and II (2)    | Differential       | 0.90                                                  | 1.8                                                  | 0.90                                                   |

| Differential SSTL-2 class I and II (2)     | Differential       | 1.25                                                  | 2.5                                                  | 1.25                                                   |

| 1.2-V HSTL <i>(4)</i>                      | Voltage-referenced | 0.6                                                   | 1.2                                                  | 0.6                                                    |

| 1.5-V HSTL class I and II                  | Voltage-referenced | 0.75                                                  | 1.5                                                  | 0.75                                                   |

| 1.8-V HSTL class I and II                  | Voltage-referenced | 0.9                                                   | 1.8                                                  | 0.9                                                    |

| SSTL-18 class I and II                     | Voltage-referenced | 0.90                                                  | 1.8                                                  | 0.90                                                   |

| SSTL-2 class I and II                      | Voltage-referenced | 1.25                                                  | 2.5                                                  | 1.25                                                   |

#### Notes to Table 2-25:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9, 10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 3, 4, 7, 8, 9, 10, 11, and 12).

- (4) 1.2-V HSTL is only supported in I/O banks 4, 7, and 8.

For more information about the I/O standards supported by Arria GX I/O banks, refer to the *Selectable I/O Standards in Arria GX Devices* chapter.

Arria GX devices contain six I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–78. The two I/O banks on the left of the device contain circuitry to support source-synchronous, high-speed differential I/O for LVDS inputs and outputs. These banks support all Arria GX I/O standards except PCI or PCI-X I/O pins, and SSTL-18 class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

The Arria GX device instruction register length is 10 bits and the USERCODE register length is 32 bits. Table 3–2 and Table 3–3 show the boundary-scan register length and device IDCODE information for Arria GX devices.

Table 3-2. Arria GX Boundary-Scan Register Length

| Device   | Boundary-Scan Register Length |

|----------|-------------------------------|

| EP1AGX20 | 1320                          |

| EP1AGX35 | 1320                          |

| EP1AGX50 | 1668                          |

| EP1AGX60 | 1668                          |

| EP1AGX90 | 2016                          |

Table 3-3. 2-Bit Arria GX Device IDCODE

|          | IDCODE (32 Bits) |                       |                                    |             |  |  |

|----------|------------------|-----------------------|------------------------------------|-------------|--|--|

| Device   | Version (4 Bits) | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) |  |  |

| EP1AGX20 | 0000             | 0010 0001 0010 0001   | 000 0110 1110                      | 1           |  |  |

| EP1AGX35 | 0000             | 0010 0001 0010 0001   | 000 0110 1110                      | 1           |  |  |

| EP1AGX50 | 0000             | 0010 0001 0010 0010   | 000 0110 1110                      | 1           |  |  |

| EP1AGX60 | 0000             | 0010 0001 0010 0010   | 000 0110 1110                      | 1           |  |  |

| EP1AGX90 | 0000             | 0010 0001 0010 0011   | 000 0110 1110                      | 1           |  |  |

# SignalTap II Embedded Logic Analyzer

Arria GX devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA (FBGA) packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

# **Configuration**

The logic, circuitry, and interconnects in the Arria GX architecture are configured with CMOS SRAM elements. Altera® FPGAs are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.

Arria GX devices are configured at system power up with data stored in an Altera configuration device or provided by an external controller (for example, a MAX® II device or microprocessor). You can configure Arria GX devices using the fast passive parallel (FPP), active serial (AS), passive serial (PS), passive parallel asynchronous (PPA), and JTAG configuration schemes. Each Arria GX device has an optimized interface that allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Arria GX devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy.

# **Configuring Arria GX FPGAs with JRunner**

The JRunner software driver configures Altera FPGAs, including Arria GX FPGAs, through the ByteBlaster™ II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information about the JRunner software driver, refer to the *AN414: JRunner Software Driver: An Embedded Solution for PLD JTAG Configuration* and the source files on the Altera website.

### **Programming Serial Configuration Devices with SRunner**

You can program a serial configuration device in-system by an external microprocessor using SRunner<sup>TM</sup>. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit into different embedded systems. SRunner software driver reads a raw programming data file (.rpd) and writes to serial configuration devices. The serial configuration device programming time using SRunner software driver is comparable to the programming time when using the Quartus II software.

- For more information about SRunner, refer to the *AN418: SRunner: An Embedded Solution for Serial Configuration Device Programming* and the source code on the Altera website.

- For more information about programming serial configuration devices, refer to the *Serial Configuration Devices (EPCS1, EPCS4, EPCS64, and EPCS128) Data Sheet* in the *Configuration Handbook*.

## **Configuring Arria GX FPGAs with the MicroBlaster Driver**

The MicroBlaster™ software driver supports a raw binary file (RBF) programming input file and is ideal for embedded FPP or PS configuration. The source code is developed for the Windows NT operating system, although it can be customized to run on other operating systems.

For more information about the MicroBlaster software driver, refer to the *Configuring* the MicroBlaster Fast Passive Parallel Software Driver White Paper or the AN423: Configuring the MicroBlaster Passive Serial Software Driver.

# PLL Reconfiguration

The phase-locked loops (PLLs) in the Arria GX device family support reconfiguration of their multiply, divide, VCO-phase selection, and bandwidth selection settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency synthesis, allowing real-time variation of the PLL frequency and delay. The rest of the device is functional while reconfiguring the PLL.

For more information about Arria GX PLLs, refer to the *PLLs in Arria GX Devices* chapter.

# **Automated Single Event Upset (SEU) Detection**

Arria GX devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole requires periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by the **Device and Pin Options** dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Arria GX devices, eliminating the need for external logic. Arria GX devices compute CRC during configuration. The Arria GX device checks the computed-CRC against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built into Arria GX devices to automatically perform error detection. This circuitry constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a reconfiguration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

Beginning with version 7.1 of the Quartus II software, you can turn on the automated error detection CRC feature in the **Device and Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the Arria GX FPGA.

**Table 4–12.** Typical Pre-Emphasis (First Post-Tap), (Note 1)

| V <sub>cc</sub> HTX = 1.5 V  | First Post Tap Pre-Emphasis Level |           |     |     |     |  |  |

|------------------------------|-----------------------------------|-----------|-----|-----|-----|--|--|

| V <sub>op</sub> Setting (mV) | 1                                 | 1 2 3 4 5 |     |     |     |  |  |

| 1000                         | _                                 | _         | 23% | 36% | 49% |  |  |

| 1200                         | _                                 | _         | 17% | 25% | 35% |  |  |

#### Note to Table 4-12:

(1) Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

**Table 4–13.** Typical Pre-Emphasis (First Post-Tap), (Note 1)

| V <sub>cc</sub> HTX = 1.2 V  |     | First Post Tap Pre-Emphasis Level |      |     |      |  |  |

|------------------------------|-----|-----------------------------------|------|-----|------|--|--|

| V <sub>op</sub> Setting (mV) | 1   | 1 2 3 4                           |      |     |      |  |  |

|                              |     | TX Term = 100 $\Omega$            |      |     |      |  |  |

| 320                          | 24% | 61%                               | 114% | _   | _    |  |  |

| 480                          | _   | 31%                               | 55%  | 86% | 121% |  |  |

| 640                          | _   | 20%                               | 35%  | 54% | 72%  |  |  |

| 800                          | _   | _                                 | 23%  | 36% | 49%  |  |  |

| 960                          | _   | _                                 | 18%  | 25% | 35%  |  |  |

#### Note to Table 4-13:

(1) Applicable to data rates from 600 Mbps to 3.125 Gbps. Specification is for measurement at the package ball.

### **DC Electrical Characteristics**

Table 4–14 lists the Arria GX device family DC electrical characteristics.

**Table 4–14.** Arria GX Device DC Operating Conditions (Part 1 of 2) (Note 1)

| Symbol              | Parameter                                   | Conditions                                                      | Device      | Min | Тур  | Max | Units |

|---------------------|---------------------------------------------|-----------------------------------------------------------------|-------------|-----|------|-----|-------|

| I <sub>I</sub>      | Input pin leakage current                   | $V_I = V_{CCIOmax}$ to 0 V (2)                                  | All         | -10 | _    | 10  | μΑ    |

| I <sub>oz</sub>     | Tri-stated I/O pin leakage current          | $V_0 = V_{CCIOmax}$ to 0 V (2)                                  | All         | -10 | _    | 10  | μΑ    |

|                     |                                             | V <sub>I</sub> = ground, no load, no                            | EP1AGX20/35 | _   | 0.30 | (3) | Α     |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current (standby) | toggling inputs                                                 | EP1AGX50/60 | _   | 0.50 | (3) | Α     |

|                     | (dunaby)                                    | T <sub>J</sub> = 25 °C                                          | EP1AGX90    |     | 0.62 | (3) | Α     |

|                     |                                             | V <sub>I</sub> = ground, no load, no                            | EP1AGX20/35 | _   | 2.7  | (3) | mA    |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current            | toggling inputs                                                 | EP1AGX50/60 | _   | 3.6  | (3) | mA    |

| 001 20              | (standby)                                   | $T_J = 25 ^{\circ}\text{C},$<br>$V_{\text{CCPD}} = 3.3\text{V}$ | EP1AGX90    | _   | 4.3  | (3) | mA    |

|                     | V                                           | V <sub>I</sub> = ground, no load, no                            | EP1AGX20/35 | _   | 4.0  | (3) | mA    |

| I <sub>CC100</sub>  | V <sub>ccio</sub> supply current (standby)  | toggling inputs                                                 | EP1AGX50/60 | _   | 4.0  | (3) | mA    |

|                     | (dundby)                                    | T <sub>J</sub> = 25 °C                                          | EP1AGX90    |     | 4.0  | (3) | mA    |

Table 4-24. 3.3-V PCI Specifications

| Symbol            | Parameter                 | Conditions              | Minimum               | Typical | Maximum                 | Units |

|-------------------|---------------------------|-------------------------|-----------------------|---------|-------------------------|-------|

| V <sub>CCIO</sub> | Output supply voltage     | _                       | 3.0                   | 3.3     | 3.6                     | V     |

| V <sub>IH</sub>   | High-level input voltage  | _                       | 0.5 V <sub>ccio</sub> | _       | V <sub>CCIO</sub> + 0.5 | V     |

| V <sub>IL</sub>   | Low-level input voltage   | _                       | -0.3                  | _       | 0.3 V <sub>CCIO</sub>   | V     |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu A$  | 0.9 V <sub>CCIO</sub> | _       | _                       | V     |

| V <sub>OL</sub>   | Low-level output voltage  | $I_{OUT} = 1,500 \mu A$ | _                     | _       | 0.1 V <sub>ccio</sub>   | V     |

Table 4–25. PCI-X Mode 1 Specifications

| Symbol            | Parameter                 | Conditions                    | Minimum               | Maximum                 | Units |

|-------------------|---------------------------|-------------------------------|-----------------------|-------------------------|-------|

| V <sub>CCIO</sub> | Output supply voltage     | _                             | 3.0                   | 3.6                     | V     |

| V <sub>IH</sub>   | High-level input voltage  | _                             | 0.5 V <sub>CC10</sub> | V <sub>CCIO</sub> + 0.5 | V     |

| V <sub>IL</sub>   | Low-level input voltage   | _                             | -0.3                  | 0.35 V <sub>CCIO</sub>  | V     |

| V <sub>IPU</sub>  | Input pull-up voltage     | _                             | 0.7 V <sub>CC10</sub> | _                       | V     |

| V <sub>OH</sub>   | High-level output voltage | $I_{OUT} = -500 \mu\text{A}$  | 0.9 V <sub>CC10</sub> | _                       | V     |

| V <sub>oL</sub>   | Low-level output voltage  | $I_{OUT} = 1,500 \mu\text{A}$ | _                     | 0.1 V <sub>CCIO</sub>   | ٧     |

Table 4-26. SSTL-18 Class I Specifications

| Symbol               | Parameter                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Units |

|----------------------|-----------------------------|---------------------------------|--------------------------|-----------|--------------------------|-------|

| V <sub>CCIO</sub>    | Output supply voltage       | _                               | 1.71                     | 1.8       | 1.89                     | V     |

| V <sub>REF</sub>     | Reference voltage           | _                               | 0.855                    | 0.9       | 0.945                    | V     |

| V <sub>TT</sub>      | Termination voltage         | _                               | $V_{REF} - 0.04$         | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V     |

| V <sub>IH</sub> (DC) | High-level DC input voltage | _                               | V <sub>REF</sub> + 0.125 | _         | _                        | V     |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  | _                               | _                        | _         | V <sub>REF</sub> - 0.125 | V     |

| V <sub>IH</sub> (AC) | High-level AC input voltage | _                               | V <sub>REF</sub> + 0.25  | _         | _                        | V     |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  | _                               | _                        | _         | V <sub>REF</sub> - 0.25  | V     |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  | _         | _                        | V     |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OL</sub> = 6.7 mA (1)    | _                        | _         | V <sub>π</sub> – 0.475   | V     |

#### Note to Table 4-26:

Table 4-27. SSTL-18 Class II Specifications

| Symbol               | Parameter                   | Conditions | Minimum                  | Typical   | Maximum                  | Units |

|----------------------|-----------------------------|------------|--------------------------|-----------|--------------------------|-------|

| V <sub>ccio</sub>    | Output supply voltage       | _          | 1.71                     | 1.8       | 1.89                     | V     |

| $V_{REF}$            | Reference voltage           | _          | 0.855                    | 0.9       | 0.945                    | V     |

| V <sub>TT</sub>      | Termination voltage         | _          | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V     |

| V <sub>IH</sub> (DC) | High-level DC input voltage | _          | V <sub>REF</sub> + 0.125 | _         | _                        | V     |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  | _          | _                        | _         | V <sub>REF</sub> - 0.125 | V     |

| V <sub>IH</sub> (AC) | High-level AC input voltage | _          | V <sub>REF</sub> + 0.25  | _         | _                        | V     |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  | _          | _                        | _         | V <sub>REF</sub> - 0.25  | V     |

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Arria GX Architecture* chapter.

**Table 4–74.** EP1AGX90 Row Pins Output Timing Parameters (Part 3 of 3)

| I/O Standard | Drive<br>Strength | Clock    | Parameter         | Fast Model |            | –6 Speed | Units  |

|--------------|-------------------|----------|-------------------|------------|------------|----------|--------|

|              |                   |          | raiailletei       | Industrial | Commercial | Grade    | UIIILS |

| 1.5-V HSTL   | 6 mA              | GCLK     | $t_{\mathtt{co}}$ | 2.857      | 2.857      | 6.106    | ns     |

| CLASS I      |                   | GCLK PLL | t <sub>co</sub>   | 0.779      | 0.779      | 1.950    | ns     |

| 1.5-V HSTL   | 8 mA              | GCLK     | t <sub>co</sub>   | 2.842      | 2.842      | 6.098    | ns     |

| CLASS I      |                   | GCLK PLL | t <sub>co</sub>   | 0.764      | 0.764      | 1.942    | ns     |

| LVDS         | _                 | GCLK     | t <sub>co</sub>   | 2.898      | 2.898      | 6.265    | ns     |

| LVDO         |                   | GCLK PLL | t <sub>co</sub>   | 0.831      | 0.831      | 2.129    | ns     |

Table 4–75 lists I/O timing specifications.

Table 4-75. EP1AGX90 Column Pins Output Timing Parameters (Part 1 of 4)

| I/O Ctondoud | Drive<br>Strength | Clock    | Dovometov       | Fast       | Fast Corner |                   | lluite. |

|--------------|-------------------|----------|-----------------|------------|-------------|-------------------|---------|

| I/O Standard |                   | GIUCK    | Parameter       | Industrial | Commercial  | -6 Speed<br>Grade | Units   |

| 3.3-V LVTTL  | 4 mA              | GCLK     | t <sub>co</sub> | 3.141      | 3.141       | 7.164             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 1.077      | 1.077       | 3.029             | ns      |

| 3.3-V LVTTL  | 8 mA              | GCLK     | t <sub>co</sub> | 2.996      | 2.996       | 6.792             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.932      | 0.932       | 2.657             | ns      |

| 3.3-V LVTTL  | 12 mA             | GCLK     | t <sub>co</sub> | 2.929      | 2.929       | 6.792             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.865      | 0.865       | 2.657             | ns      |

| 3.3-V LVTTL  | 16 mA             | GCLK     | t <sub>co</sub> | 2.903      | 2.903       | 6.623             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.839      | 0.839       | 2.488             | ns      |

| 3.3-V LVTTL  | 20 mA             | GCLK     | t <sub>co</sub> | 2.881      | 2.881       | 6.498             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.817      | 0.817       | 2.363             | ns      |

| 3.3-V LVTTL  | 24 mA             | GCLK     | t <sub>co</sub> | 2.874      | 2.874       | 6.500             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.810      | 0.810       | 2.365             | ns      |

| 3.3-V        | 4 mA              | GCLK     | t <sub>co</sub> | 2.996      | 2.996       | 6.792             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.932      | 0.932       | 2.657             | ns      |

| 3.3-V        | 8 mA              | GCLK     | t <sub>co</sub> | 2.904      | 2.904       | 6.497             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.840      | 0.840       | 2.362             | ns      |

| 3.3-V        | 12 mA             | GCLK     | t <sub>co</sub> | 2.876      | 2.876       | 6.419             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.812      | 0.812       | 2.284             | ns      |

| 3.3-V        | 16 mA             | GCLK     | t <sub>co</sub> | 2.883      | 2.883       | 6.387             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.819      | 0.819       | 2.252             | ns      |

| 3.3-V        | 20 mA             | GCLK     | t <sub>co</sub> | 2.870      | 2.870       | 6.369             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.806      | 0.806       | 2.234             | ns      |

| 3.3-V        | 24 mA             | GCLK     | t <sub>co</sub> | 2.859      | 2.859       | 6.347             | ns      |

| LVCMOS       |                   | GCLK PLL | t <sub>co</sub> | 0.795      | 0.795       | 2.212             | ns      |

| 2.5 V        | 4 mA              | GCLK     | t <sub>co</sub> | 2.958      | 2.958       | 6.824             | ns      |

|              |                   | GCLK PLL | t <sub>co</sub> | 0.894      | 0.894       | 2.689             | ns      |

Table 4-75. EP1AGX90 Column Pins Output Timing Parameters (Part 3 of 4)

| I/O Ctondovd | Drive    | Oleak    | Davamatar       | Fast       | Corner     | –6 Speed | lluita |

|--------------|----------|----------|-----------------|------------|------------|----------|--------|

| I/O Standard | Strength | Clock    | Parameter       | Industrial | Commercial | Grade    | Units  |

| SSTL-18      | 6 mA     | GCLK     | t <sub>co</sub> | 2.860      | 2.860      | 6.313    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.798      | 0.798      | 2.182    | ns     |

| SSTL-18      | 8 mA     | GCLK     | t <sub>co</sub> | 2.839      | 2.839      | 6.294    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.777      | 0.777      | 2.163    | ns     |

| SSTL-18      | 10 mA    | GCLK     | t <sub>co</sub> | 2.844      | 2.844      | 6.292    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.782      | 0.782      | 2.161    | ns     |

| SSTL-18      | 12 mA    | GCLK     | t <sub>co</sub> | 2.838      | 2.838      | 6.278    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.776      | 0.776      | 2.147    | ns     |

| SSTL-18      | 8 mA     | GCLK     | t <sub>co</sub> | 2.827      | 2.827      | 6.244    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.765      | 0.765      | 2.113    | ns     |

| SSTL-18      | 16 mA    | GCLK     | t <sub>co</sub> | 2.839      | 2.839      | 6.222    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.777      | 0.777      | 2.091    | ns     |

| SSTL-18      | 18 mA    | GCLK     | t <sub>co</sub> | 2.835      | 2.835      | 6.230    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.773      | 0.773      | 2.099    | ns     |

| SSTL-18      | 20 mA    | GCLK     | t <sub>co</sub> | 2.835      | 2.835      | 6.228    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.773      | 0.773      | 2.097    | ns     |

| 1.8-V HSTL   | 4 mA     | GCLK     | t <sub>co</sub> | 2.861      | 2.861      | 6.287    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.797      | 0.797      | 2.152    | ns     |

| 1.8-V HSTL   | 6 mA     | GCLK     | t <sub>co</sub> | 2.864      | 2.864      | 6.268    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.802      | 0.802      | 2.137    | ns     |

| 1.8-V HSTL   | 8 mA     | GCLK     | t <sub>co</sub> | 2.842      | 2.842      | 6.257    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.780      | 0.780      | 2.126    | ns     |

| 1.8-V HSTL   | 10 mA    | GCLK     | t <sub>co</sub> | 2.846      | 2.846      | 6.263    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.784      | 0.784      | 2.132    | ns     |

| 1.8-V HSTL   | 12 mA    | GCLK     | t <sub>co</sub> | 2.838      | 2.838      | 6.256    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.776      | 0.776      | 2.125    | ns     |

| 1.8-V HSTL   | 16 mA    | GCLK     | t <sub>co</sub> | 2.821      | 2.821      | 6.020    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.759      | 0.759      | 1.889    | ns     |

| 1.8-V HSTL   | 18 mA    | GCLK     | t <sub>co</sub> | 2.823      | 2.823      | 6.031    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.761      | 0.761      | 1.900    | ns     |

| 1.8-V HSTL   | 20 mA    | GCLK     | t <sub>co</sub> | 2.823      | 2.823      | 6.040    | ns     |

| CLASS II     |          | GCLK PLL | t <sub>co</sub> | 0.761      | 0.761      | 1.909    | ns     |

| 1.5-V HSTL   | 4 mA     | GCLK     | t <sub>co</sub> | 2.861      | 2.861      | 6.286    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.797      | 0.797      | 2.151    | ns     |

| 1.5-V HSTL   | 6 mA     | GCLK     | t <sub>co</sub> | 2.863      | 2.863      | 6.260    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.801      | 0.801      | 2.129    | ns     |

| 1.5-V HSTL   | 8 mA     | GCLK     | t <sub>co</sub> | 2.845      | 2.845      | 6.262    | ns     |

| CLASS I      |          | GCLK PLL | t <sub>co</sub> | 0.783      | 0.783      | 2.131    | ns     |

Table 4–99 lists performance notes.

Table 4-99. Arria GX Performance Notes

| Applications                      |                                      |       | Performance                |            |                |

|-----------------------------------|--------------------------------------|-------|----------------------------|------------|----------------|

|                                   |                                      | ALUTs | TriMatrix<br>Memory Blocks | DSP Blocks | -6 Speed Grade |

|                                   | 16-to-1<br>multiplexer               | 5     | 0                          | 0          | 168.41         |

| LE                                | 32-to-1<br>multiplexer               | 11    | 0                          | 0          | 334.11         |

|                                   | 16-bit counter                       | 16    | 0                          | 0          | 374.0          |

|                                   | 64-bit counter                       | 64    | 0                          | 0          | 168.41         |

| TriMatrix Memory<br>M512 block    | Simple dual-port<br>RAM 32 x 18 bit  | 0     | 1                          | 0          | 348.0          |

| IVIOTZ DIOCK                      | FIFO 32 x 18 bit                     | 0     | 1                          | 0          | 333.22         |

| TriMatrix Memory                  | Simple dual-port<br>RAM 128 x 36 bit | 0     | 1                          | 0          | 344.71         |

| M4K block                         | True dual-port<br>RAM 128 x 18 bit   | 0     | 1                          | 0          | 348.0          |

|                                   | Single port RAM<br>4K x 144 bit      | 0     | 2                          | 0          | 244.0          |

|                                   | Simple dual-port<br>RAM 4K x 144 bit | 0     | 1                          | 0          | 292.0          |

|                                   | True dual-port<br>RAM 4K x 144 bit   | 0     | 2                          | 0          | 244.0          |

|                                   | Single port RAM<br>8K x 72 bit       | 0     | 1                          | 0          | 247.0          |

| TriMatrix Memory<br>MegaRAM block | Simple dual-port<br>RAM 8K x 72 bit  | 0     | 1                          | 0          | 292.0          |

|                                   | Single port RAM<br>16K x 36 bit      | 0     | 1                          | 0          | 254.0          |

|                                   | Simple dual-port<br>RAM 16K x 36 bit | 0     | 1                          | 0          | 292.0          |

|                                   | True dual-port<br>RAM 16K x 36 bit   | 0     | 1                          | 0          | 251.0          |

|                                   | Single port RAM<br>32K x 18 bit      | 0     | 1                          | 0          | 317.36         |

|                                   | Simple dual-port<br>RAM 32K x 18 bit | 0     | 1                          | 0          | 292.0          |

|                                   | True dual-port<br>RAM 32K x 18 bit   | 0     | 1                          | 0          | 251.0          |

|                                   | Single port RAM<br>64K x 9 bit       | 0     | 1                          | 0          | 254.0          |

|                                   | Simple dual-port<br>RAM 64K x 9 bit  | 0     | 1                          | 0          | 292.0          |

|                                   | True dual-port<br>RAM 64K x 9 bit    | 0     | 1                          | 0          | 251.0          |

Table 4-115. High-Speed I/O Specifications (Part 2 of 2) Note (1), (2)

| Sumbol        | Conditions     |                          |                       | -6 Speed Grade |     |     | Units       |

|---------------|----------------|--------------------------|-----------------------|----------------|-----|-----|-------------|

| Symbol        |                |                          |                       | Min            | Тур | Max | Units       |

|               | Standard       | Training Pattern         | Transition<br>Density |                | _   | _   |             |

|               | SPI-4          | 000000000011<br>11111111 | 10%                   | 256            | _   | _   | Number of   |

| DPA lock time | Parallel Rapid | 00001111                 | 25%                   | 256            | _   | _   | repetitions |

|               | I/O            | 10010000                 | 50%                   | 256            | _   | _   |             |

|               | Miscellaneous  | 10101010                 | 100%                  | 256            | _   | _   |             |

|               |                | 01010101                 | _                     | 256            | _   | _   |             |

#### Notes to Table 4-115:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le \text{input clock frequency} \times \text{W} \le 1,040$ .

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) used. The I/O differential buffer and input register do not have a minimum toggle rate.