Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1676                                                       |

| Number of Logic Elements/Cells | 33520                                                      |

| Total RAM Bits                 | 1348416                                                    |

| Number of I/O                  | 230                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 484-BBGA                                                   |

| Supplier Device Package        | 484-FBGA (23x23)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1agx35cf484c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

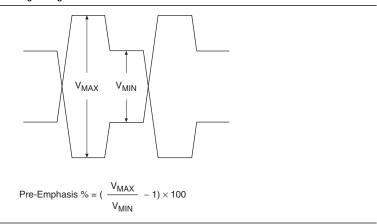

### **Programmable Pre-Emphasis**

The programmable pre-emphasis module controls the output driver to boost high frequency components and compensate for losses in the transmission medium, as shown in Figure 2–10. Pre-emphasis is set statically using the ALTGXB megafunction.

Figure 2-10. Pre-Emphasis Signaling

Pre-emphasis percentage is defined as  $(V_{MAX}/V_{MIN}-1) \times 100$ , where  $V_{MAX}$  is the differential emphasized voltage (peak-to-peak) and  $V_{MIN}$  is the differential steady-state voltage (peak-to-peak).

### PCI Express (PIPE) Receiver Detect

The Arria GX transmitter buffer has a built-in receiver detection circuit for use in PCI Express (PIPE) mode. This circuit provides the ability to detect if there is a receiver downstream by sending out a pulse on the channel and monitoring the reflection. This mode requires a tri-stated transmitter buffer (in electrical idle mode).

### PCI Express (PIPE) Electric Idles (or Individual Transmitter Tri-State)

The Arria GX transmitter buffer supports PCI Express (PIPE) electrical idles. This feature is only active in PCI Express (PIPE) mode. The tx\_forceelecidle port puts the transmitter buffer in electrical idle mode. This port is available in all PCI Express (PIPE) power-down modes and has specific usage in each mode.

### **Receiver Path**

This section describes the data path through the Arria GX receiver. The sub-blocks are described in order from the receiver buffer to the PLD-receiver parallel interface.

### **Receiver Buffer**

The Arria GX receiver input buffer supports the 1.2-V and 1.5-V PCML I/O standards at rates up to 3.125 Gbps. The common mode voltage of the receiver input buffer is programmable between 0.85 V and 1.2 V. You must select the 0.85 V common mode voltage for AC- and DC-coupled PCML links and 1.2 V common mode voltage for DC-coupled LVDS links.

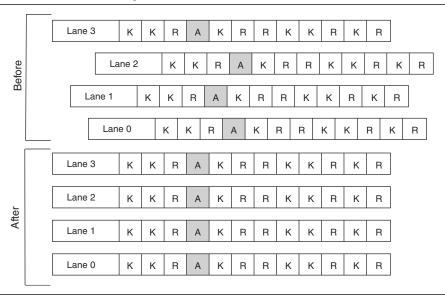

Figure 2–16 shows misaligned channels before the channel aligner and the aligned channels after the channel aligner.

Figure 2-16. Before and After the Channel Aligner

### **Rate Matcher**

In asynchronous systems, the upstream transmitter and local receiver can be clocked with independent reference clock sources. Frequency differences in the order of a few hundred PPM can potentially corrupt the data at the receiver.

The rate matcher compensates for small clock frequency differences between the upstream transmitter and the local receiver clocks by inserting or removing skip characters from the inter packet gap (IPG) or idle streams. It inserts a skip character if the local receiver is running a faster clock than the upstream transmitter. It deletes a skip character if the local receiver is running a slower clock than the upstream transmitter. The Quartus II software automatically configures the appropriate skip character as specified in the IEEE 802.3 for GIGE mode and PCI-Express Base Specification for PCI Express (PIPE) mode. The rate matcher is bypassed in Serial RapidIO and must be implemented in the PLD logic array or external circuits depending on your system design.

Table 2–5 lists the maximum frequency difference that the rate matcher can tolerate in XAUI, PCI Express (PIPE), GIGE, and Basic functional modes.

**Table 2–5.** Rate Matcher PPM Tolerance

| Function Mode      | PPM   |  |  |

|--------------------|-------|--|--|

| XAUI               | ± 100 |  |  |

| PCI Express (PIPE) | ± 300 |  |  |

| GIGE               | ± 100 |  |  |

| Basic              | ± 300 |  |  |

#### **XAUI Mode**

In XAUI mode, the rate matcher adheres to clause 48 of the IEEE 802.3ae specification for clock rate compensation. The rate matcher performs clock compensation on columns of /R/(K28.0/), denoted by //R//. An //R// is added or deleted automatically based on the number of words in the FIFO buffer.

### PCI Express (PIPE) Mode Rate Matcher

In PCI Express (PIPE) mode, the rate matcher can compensate up to  $\pm$  300 PPM (600 PPM total) frequency difference between the upstream transmitter and the receiver. The rate matcher logic looks for skip ordered sets (SOS), which contains a /K28.5/ comma followed by three /K28.0/ skip characters. The rate matcher logic deletes or inserts /K28.0/ skip characters as necessary from/to the rate matcher FIFO.

The rate matcher in PCI Express (PIPE) mode has a FIFO buffer overflow and underflow protection. In the event of a FIFO buffer overflow, the rate matcher deletes any data after detecting the overflow condition to prevent FIFO pointer corruption until the rate matcher is not full. In an underflow condition, the rate matcher inserts 9'h1FE (/K30.7/) until the FIFO buffer is not empty. These measures ensure that the FIFO buffer can gracefully exit the overflow and underflow condition without requiring a FIFO reset. The rate matcher FIFO overflow and underflow condition is indicated on the pipestatus port.

You can bypass the rate matcher in PCI Express (PIPE) mode if you have a synchronous system where the upstream transmitter and local receiver derive their reference clocks from the same source.

### **GIGE Mode Rate Matcher**

In GIGE mode, the rate matcher can compensate up to  $\pm$  100 PPM (200 PPM total) frequency difference between the upstream transmitter and the receiver. The rate matcher logic inserts or deletes /I2/ idle ordered sets to/from the rate matcher FIFO during the inter-frame or inter-packet gap (IFG or IPG). /I2/ is selected as the rate matching ordered set because it maintains the running disparity, unlike /I1/ that alters the running disparity. Because the /I2/ ordered-set contains two 10-bit code groups (/K28.5/, /D16.2/), 20 bits are inserted or deleted at a time for rate matching.

The rate matcher logic has the capability to insert or delete /C1/ or /C2/ configuration ordered sets when 'GIGE Enhanced' mode is chosen as the sub-protocol in the MegaWizard Plug-In Manager.

If the frequency PPM difference between the upstream transmitter and the local receiver is high, or if the packet size is too large, the rate matcher FIFO buffer can face an overflow or underflow situation.

### **Basic Mode**

In basic mode, you can program the skip and control pattern for rate matching. There is no restriction on the deletion of a skip character in a cluster. The rate matcher deletes the skip characters as long as they are available. For insertion, the rate matcher inserts skip characters such that the number of skip characters at the output of rate matcher does not exceed five.

In GIGE and Serial RapidIO modes, you can dynamically put each transceiver channel individually in serial loopback by controlling the rx\_seriallpbken port. A high on the rx\_seriallpbken port puts the transceiver into serial loopback and a low takes the transceiver out of serial loopback.

As seen in Figure 2–18, the serial data output from the transmitter serializer is looped back to the receiver CRU in serial loopback. The transmitter data path from the PLD interface to the serializer in serial loopback is the same as in non-loopback mode. The receiver data path from the clock recovery unit to the PLD interface in serial loopback is the same as in non-loopback mode. Because the entire transceiver data path is available in serial loopback, this option is often used to diagnose the data path as a probable cause of link errors.

When serial loopback is enabled, the transmitter output buffer is still active and drives the serial data out on the tx dataout port.

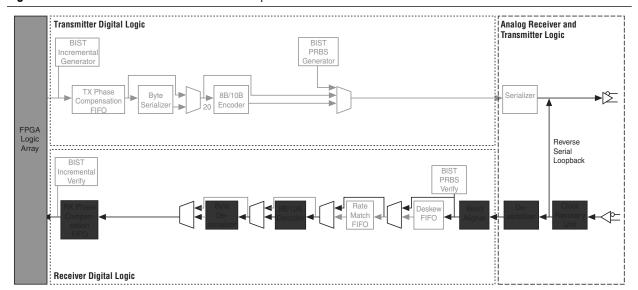

### **Reverse Serial Loopback**

Reverse serial loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, passes through the CRU unit and the retimed serial data is looped back, and is transmitted though the high-speed differential transmitter output buffer.

Figure 2–19 shows the data path in reverse serial loopback mode.

Figure 2–19. Arria GX Block in Reverse Serial Loopback Mode

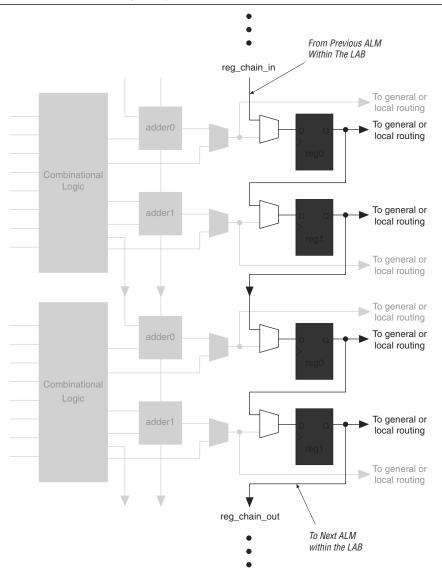

**Figure 2–38.** Register Chain within a LAB (Note 1)

### Note to Figure 2-38:

(1) The combinational or adder logic can be used to implement an unrelated, unregistered function.

## **Clear and Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT gate push-back technique. Arria GX devices support simultaneous asynchronous load/preset and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

clock\_a

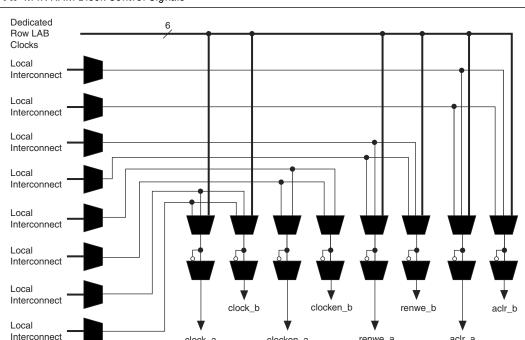

Figure 2-44. M4K RAM Block Control Signals

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM block are possible from the left adjacent LABs and another 16 are possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–45 shows the M4K RAM block to logic array interface.

clocken\_a

renwe\_a

aclr\_a

## **Modes of Operation**

The adder, subtractor, and accumulate functions of a DSP block have four modes of operation:

- Simple multiplier

- Multiply-accumulator

- Two-multipliers adder

- Four-multipliers adder

Table 2–14 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, 2D FIR filters, equalizers, IIR, correlators, matrix multiplication, and many other functions. DSP blocks also support mixed modes and mixed multiplier sizes in the same block. For example, half of one DSP block can implement one  $18 \times 18$ -bit multiplier in multiply-accumulator mode, while the other half of the DSP block implements four  $9 \times 9$ -bit multipliers in simple multiplier mode.

Table 2–14. Multiplier Size and Configurations per DSP Block

| DSP Block Mode         | 9 × 9                                                  | 18 × 18                                                 | 36 × 36                                |

|------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------------------------|

| Multiplier             | Eight multipliers with eight product outputs           | Four multipliers with four product outputs              | One multiplier with one product output |

| Multiply-accumulator   | _                                                      | Two 52-bit multiply-accumulate blocks                   | _                                      |

| Two-multipliers adder  | Four two-multiplier adder (two 9 x 9 complex multiply) | Two two-multiplier adder (one 18 x 18 complex multiply) | _                                      |

| Four-multipliers adder | Two four-multiplier adder                              | One four-multiplier adder                               | _                                      |

### **DSP Block Interface**

The Arria GX device DSP block input registers can generate a shift register that can cascade down in the same DSP block column. Dedicated connections between DSP blocks provide fast connections between shift register inputs to cascade shift register chains. You can cascade registers within multiple DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in ALMs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in ALMs. Each DSP block can route the shift register chain out of the block to cascade multiple columns of DSP blocks.

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete 18 × 18-bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region.

The outputs also work similarly to LAB outputs. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects and 18 can drive to the right LAB though direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing.

Table 2-15. DSP Block Signal Sources and Destinations

| LAB Row at Interface | Control Signals Generated | Data Inputs | Data Outputs |

|----------------------|---------------------------|-------------|--------------|

|                      | clock0                    |             |              |

|                      | aclr0                     |             |              |

|                      | ena0                      |             |              |

|                      | mult01_saturate           |             |              |

| 0                    | addnsub1_round/           | A1[170]     | OA[170]      |

|                      | accum_round               | B1[170]     | OB[170]      |

|                      | addnsub1                  |             |              |

|                      | signa                     |             |              |

|                      | sourcea                   |             |              |

|                      | sourceb clock1            |             |              |

|                      |                           |             |              |

|                      | aclr1<br>ena1             |             |              |

|                      | accum saturate            |             |              |

| 1                    | mult01 round              | A2[170]     | OC[170]      |

| 1                    | accum sload               | B2[170]     | OD[170]      |

|                      | sourcea                   |             |              |

|                      | sourceb                   |             |              |

|                      | mode0                     |             |              |

|                      | clock2                    |             |              |

|                      | aclr2                     |             |              |

|                      | ena2                      |             |              |

|                      | mult23_saturate           |             |              |

| 2                    | addnsub3_round/           | A3[170]     | OE [170]     |

| _                    | accum_round               | B3[170]     | OF[170]      |

|                      | addnsub3                  |             |              |

|                      | sign_b                    |             |              |

|                      | sourcea                   |             |              |

|                      | sourceb                   |             |              |

|                      | clock3                    |             |              |

|                      | aclr3                     |             |              |

|                      | ena3                      |             |              |

| 3                    | accum_saturate            | A4[170]     | OG[170]      |

| S                    | mult23_round              | B4[170]     | OH[170]      |

|                      | accum_sload               |             |              |

|                      | sourcea                   |             |              |

|                      | sourceb                   |             |              |

|                      | mode1                     |             |              |

## **PLLs and Clock Networks**

Arria GX devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

## **Global and Hierarchical Clocking**

Arria GX devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Arria GX devices.

There are 12 dedicated clock pins (CLK [15..12] and CLK [7..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device except the right side, as shown in Figure 2–54 and Figure 2–55. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables or disables the clock to reduce power consumption. Table 2–16 lists the global and regional clock features.

Table 2-16. Global and Regional Clock Features

| Feature                        | Global Clocks                                                    | Regional Clocks                                                  |  |  |

|--------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| Number per device              | 16                                                               | 32                                                               |  |  |

| Number available per quadrant  | 16 8                                                             |                                                                  |  |  |

| Sources                        | Clock pins, PLL outputs, core routings, inter-transceiver clocks | Clock pins, PLL outputs, core routings, inter-transceiver clocks |  |  |

| Dynamic clock source selection | ~                                                                | _                                                                |  |  |

| Dynamic enable/disable         | <b>✓</b>                                                         | ~                                                                |  |  |

### **Global Clock Network**

These clocks drive throughout the entire device, feeding all device quadrants. GCLK networks can be used as clock sources for all resources in the device IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–54 shows the 12 dedicated CLK pins driving global clock networks.

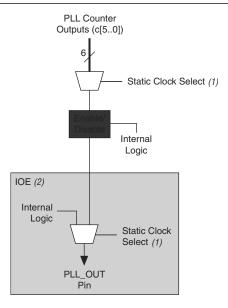

Figure 2–60. External PLL Output Clock Control Blocks

### Notes to Figure 2-60:

- (1) These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) The clock control block feeds to a multiplexer within the PLL\_OUT pin's IOE. The PLL\_OUT pin is a dual-purpose pin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.

For the global clock control block, clock source selection can be controlled either statically or dynamically. You have the option of statically selecting the clock source by using the Quartus II software to set specific configuration bits in the configuration file (.sof or .pof) or controlling the selection dynamically by using internal logic to drive the multiplexer select inputs. When selecting statically, the clock source can be set to any of the inputs to the select multiplexer. When selecting the clock source dynamically, you can either select between two PLL outputs (such as the C0 or C1 outputs from one PLL), between two PLLs (such as the C0/C1 clock output of one PLL or the C0/C1 clock output of the other PLL), between two clock pins (such as CLK0 or CLK1), or between a combination of clock pins or PLL outputs.

For the regional and PLL\_OUT clock control block, clock source selection can only be controlled statically using configuration bits. Any of the inputs to the clock select multiplexer can be set as the clock source.

Arria GX clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device. GCLK and RCLK networks can be powered down statically through a setting in the configuration file (.sof or .pof). Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software. The dynamic clock enable or disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figure 2–58 through Figure 2–60.

ioe\_clk[7..0] VCCIO Column, Row, – PCI Clamp (4) To DQS Logic or Local Block (3) Interconnect DQS Local Bus (2) VCCIO Programmable Pull-Up Resistor On-Chip Input Pin to Termination Input RegisterDelay sclr/spreset Input Register ce\_in Bus-Hold Circuit aclr/apreset Input Register Latch

**Figure 2–73.** Arria GX IOE in DDR Input I/O Configuration (Note 1)

### Notes to Figure 2-73:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- (4) The optional PCI clamp is only available on column I/O pins.

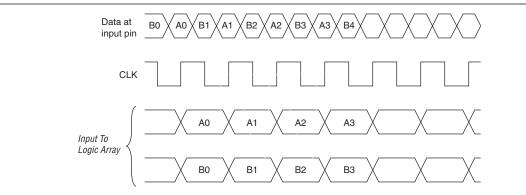

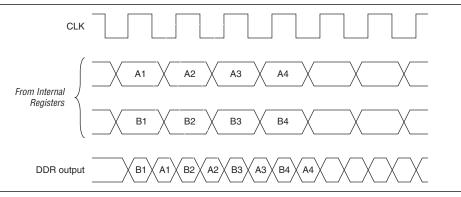

Figure 2-74. Input Timing Diagram in DDR Mode

Figure 2–76. Output Timing Diagram in DDR Mode

The Arria GX IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock to meet DDR SDRAM timing requirements.

## **External RAM Interfacing**

In addition to the six I/O registers in each IOE, Arria GX devices also have dedicated phase-shift circuitry for interfacing with external memory interfaces, including DDR, DDR2 SDRAM, and SDR SDRAM. In every Arria GX device, the I/O banks at the top (Banks 3 and 4) and bottom (Banks 7 and 8) of the device support DQ and DQS signals with DQ bus modes of  $\times 4$ ,  $\times 8/\times 9$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$ . Table 2–23 shows the number of DQ and DQS buses that are supported per device.

**Table 2–23.** DQS and DQ Bus Mode Support (Note 1)

| Device      | Package                   | Number of<br>×4 Groups | Number of<br>×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |

|-------------|---------------------------|------------------------|---------------------------|-----------------------------|-----------------------------|

| EP1AGX20    | 484-pin FineLine BGA      | 2                      | 0                         | 0                           | 0                           |

| EP1AGX35    | 484-pin FineLine BGA      | 2                      | 0                         | 0                           | 0                           |

| LF IAGASS   | 780-pin FineLine BGA      | 18                     | 8                         | 4                           | 0                           |

|             | 484-pin FineLine BGA      | 2                      | 0                         | 0                           | 0                           |

| EP1AGX50/60 | 780-pin FineLine BGA      | 18                     | 8                         | 4                           | 0                           |

| Li maxeeree | 1,152-pin FineLine<br>BGA | 36                     | 18                        | 8                           | 4                           |

| EP1AGX90    | 1,152-pin FineLine<br>BGA | 36                     | 18                        | 8                           | 4                           |

### Note to Table 2-23:

(1) Numbers are preliminary until devices are available.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

Table 4–21. 3.3-V LVDS I/O Specifications

| Symbol                | Parameter                                                                    | Conditions         | Minimum | Typical | Maximum | Units |

|-----------------------|------------------------------------------------------------------------------|--------------------|---------|---------|---------|-------|

| V <sub>ccio</sub> (1) | I/O supply voltage for top and bottom<br>PLL banks (9, 10, 11, and 12)       | _                  | 3.135   | 3.3     | 3.465   | V     |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended)                              | _                  | 100     | 350     | 900     | mV    |

| V <sub>ICM</sub>      | Input common mode voltage                                                    | _                  | 200     | 1,250   | 1,800   | mV    |

| V <sub>od</sub>       | Output differential voltage (single-ended)                                   | $R_L = 100 \Omega$ | 250     | _       | 710     | m۷    |

| V <sub>OCM</sub>      | Output common mode voltage                                                   | $R_L = 100 \Omega$ | 840     | _       | 1,570   | m۷    |

| R <sub>L</sub>        | Receiver differential input discrete resistor (external to Arria GX devices) | _                  | 90      | 100     | 110     | Ω     |

### Note to Table 4-21:

Table 4-22. 3.3-V PCML Specifications

| Symbol            | Parameter                                       | Minimum | Typical           | Maximum | Units |

|-------------------|-------------------------------------------------|---------|-------------------|---------|-------|

| V <sub>CCIO</sub> | I/O supply voltage                              | 3.135   | 3.3               | 3.465   | V     |

| V <sub>ID</sub>   | Input differential voltage swing (single-ended) | 300     | _                 | 600     | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                       | 1.5     | _                 | 3.465   | V     |

| V <sub>oD</sub>   | Output differential voltage (single-ended)      | 300     | 370               | 500     | mV    |

| $\Delta V_{0D}$   | Change in V <sub>O D</sub> between high and low | _       | _                 | 50      | mV    |

| V <sub>OCM</sub>  | Output common mode voltage                      | 2.5     | 2.85              | 3.3     | V     |

| $\Delta V_{OCM}$  | Change in V <sub>OCM</sub> between high and low | _       | _                 | 50      | mV    |

| V <sub>T</sub>    | Output termination voltage                      | _       | V <sub>CCIO</sub> | _       | V     |

| R <sub>1</sub>    | Output external pull-up resistors               | 45      | 50                | 55      | Ω     |

| R <sub>2</sub>    | Output external pull-up resistors               | 45      | 50                | 55      | Ω     |

Table 4-23. LVPECL Specifications

| Parameter             | Conditions                                      | Minimum            | Typical | Maximum | Units | Parameter |

|-----------------------|-------------------------------------------------|--------------------|---------|---------|-------|-----------|

| V <sub>CCIO</sub> (1) | I/O supply voltage                              | _                  | 3.135   | 3.3     | 3.465 | V         |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended) | _                  | 300     | 600     | 1,000 | mV        |

| V <sub>ICM</sub>      | Input common mode voltage                       | _                  | 1.0     | _       | 2.5   | V         |

| V <sub>oD</sub>       | Output differential voltage (single-ended)      | $R_L = 100 \Omega$ | 525     | _       | 970   | mV        |

| V <sub>OCM</sub>      | Output common mode voltage                      | $R_L = 100 \Omega$ | 1,650   | _       | 2,250 | mV        |

| $R_L$                 | Receiver differential input resistor            | T -                | 90      | 100     | 110   | Ω         |

### Note to Table 4-23:

<sup>(1)</sup> The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$  not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by  $VCC\_PLL\_OUT$ . For differential clock output/feedback operation, connect  $VCC\_PLL\_OUT$  to 3.3 V.

<sup>(1)</sup> The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by  $VCC\_PLL\_OUT$ . For differential clock output/feedback operation, connect  $VCC\_PLL\_OUT$  to 3.3 V.

Table 4-51. EP1AGX20 Column Pins Output Timing Parameters (Part 3 of 4)

| 1/0 0111        | Drive                                                                                                                         | 011-              | Parameter -       | Fast       | Corner     | –6 Speed | 11    |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------|------------|----------|-------|

| I/O Standard    | Strength                                                                                                                      | Clock             |                   | Industrial | Commercial | Grade    | Units |

| SSTL-18         | 1C mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.609      | 2.609      | 5.603    | ns    |

| CLASS II        | 16 mA                                                                                                                         | GCLK PLL          | t <sub>co</sub>   | 1.164      | 1.164      | 2.491    | ns    |

| SSTL-18         | 18 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.605      | 2.605      | 5.611    | ns    |

| CLASS II        | 10 IIIA                                                                                                                       | GCLK PLL          | t <sub>co</sub>   | 1.160      | 1.160      | 2.499    | ns    |

| SSTL-18         | 20 m/s                                                                                                                        | GCLK              | t <sub>co</sub>   | 2.605      | 2.605      | 5.609    | ns    |

| CLASS II 20 MA  | GCLK PLL                                                                                                                      | t <sub>co</sub>   | 1.160             | 1.160      | 2.497      | ns       |       |

| 1.8-V HSTL      | 4 mA                                                                                                                          | GCLK              | t <sub>co</sub>   | 2.629      | 2.629      | 5.664    | ns    |

| 1.8-V HSTL 6 mA | GCLK PLL                                                                                                                      | t <sub>co</sub>   | 1.187             | 1.187      | 2.558      | ns       |       |

| 1.8-V HSTL      | 6 m /\                                                                                                                        | GCLK              | t <sub>co</sub>   | 2.634      | 2.634      | 5.649    | ns    |

| CLASS I         | O IIIA                                                                                                                        | GCLK PLL          | t <sub>co</sub>   | 1.189      | 1.189      | 2.537    | ns    |

| 1.8-V HSTL      | 8 mA                                                                                                                          | GCLK              | t <sub>co</sub>   | 2.612      | 2.612      | 5.638    | ns    |

| CLASS I         | O IIIA                                                                                                                        | GCLK PLL          | t <sub>co</sub>   | 1.167      | 1.167      | 2.526    | ns    |

| 1.8-V HSTL      | 10 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.616      | 2.616      | 5.644    | ns    |

| CLASS I         | TO THA                                                                                                                        | GCLK PLL          | t <sub>co</sub>   | 1.171      | 1.171      | 2.532    | ns    |

| 1.8-V HSTL      | 12 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.608      | 2.608      | 5.637    | ns    |

| CLASS I         | 12 IIIA                                                                                                                       | GCLK PLL          | t <sub>co</sub>   | 1.163      | 1.163      | 2.525    | ns    |

| 1.8-V HSTL      | 16 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.591      | 2.591      | 5.401    | ns    |

| CLASS II        | GCLK PLL                                                                                                                      | $t_{co}$          | 1.146             | 1.146      | 2.289      | ns       |       |

| 1.8-V HSTL      | 1 1X MA                                                                                                                       | GCLK              | t <sub>co</sub>   | 2.593      | 2.593      | 5.412    | ns    |

| CLASS II 18 mA  | GCLK PLL                                                                                                                      | $t_{\mathtt{co}}$ | 1.148             | 1.148      | 2.300      | ns       |       |

| 1.8-V HSTL      | 20 m∆                                                                                                                         | GCLK              | $t_{\mathtt{co}}$ | 2.593      | 2.593      | 5.421    | ns    |

| CLASS II        | 20 1117                                                                                                                       | GCLK PLL          | $t_{\mathtt{co}}$ | 1.148      | 1.148      | 2.309    | ns    |

| 1.5-V HSTL      | 4 mΔ                                                                                                                          | GCLK              | $t_{\mathtt{co}}$ | 2.629      | 2.629      | 5.663    | ns    |

| CLASS I         | T IIIA                                                                                                                        | GCLK PLL          | $t_{\mathtt{co}}$ | 1.187      | 1.187      | 2.557    | ns    |

| 1.5-V HSTL      | 6 mΔ                                                                                                                          | GCLK              | $t_{\mathtt{co}}$ | 2.633      | 2.633      | 5.641    | ns    |

| CLASS I         | UIIIA                                                                                                                         | GCLK PLL          | $t_{\mathtt{co}}$ | 1.188      | 1.188      | 2.529    | ns    |

| 1.5-V HSTL      | 8 mΔ                                                                                                                          | GCLK              | $t_{\mathtt{co}}$ | 2.615      | 2.615      | 5.643    | ns    |

| CLASS I         | OTILA                                                                                                                         | GCLK PLL          | $t_{\mathtt{co}}$ | 1.170      | 1.170      | 2.531    | ns    |

| 1.5-V HSTL      | 10 mΔ                                                                                                                         | GCLK              | $t_{\mathtt{co}}$ | 2.615      | 2.615      | 5.645    | ns    |

| CLASS I         | IO IIIA                                                                                                                       | GCLK PLL          | $t_{co}$          | 1.170      | 1.170      | 2.533    | ns    |

| 1.5-V HSTL      | 12 m∆                                                                                                                         | GCLK              | $t_{\mathtt{co}}$ | 2.609      | 2.609      | 5.643    | ns    |

| CLASS I         | 12 1117                                                                                                                       | GCLK PLL          | $t_{\mathtt{co}}$ | 1.164      | 1.164      | 2.531    | ns    |

| 1.5-V HSTL      | ASS II 20 IIIA  5-V HSTL 4 mA  5-V HSTL 6 mA  5-V HSTL 8 mA  5-V HSTL ASS I 10 mA  5-V HSTL ASS I 12 mA  5-V HSTL ASS I 12 mA | GCLK              | t <sub>co</sub>   | 2.596      | 2.596      | 5.455    | ns    |

| CLASS II        | 10 IIIA                                                                                                                       | GCLK PLL          | t <sub>co</sub>   | 1.151      | 1.151      | 2.343    | ns    |

| 1.5-V HSTL      | 18 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.599      | 2.599      | 5.465    | ns    |

| CLASS II        | IO IIIA                                                                                                                       | GCLK PLL          | t <sub>co</sub>   | 1.154      | 1.154      | 2.353    | ns    |

| 1.5-V HSTL      | 20 mA                                                                                                                         | GCLK              | t <sub>co</sub>   | 2.601      | 2.601      | 5.478    | ns    |

| CLASS II        | LUIIIA                                                                                                                        | GCLK PLL          | $t_{\mathtt{co}}$ | 1.156      | 1.156      | 2.366    | ns    |

Table 4–55.

EP1AGX35 Column Pins Input Timing Parameters (Part 3 of 3)

| I/O Chandard        | Olook       | Davamatav       | Fast       | Corner     | –6 Speed | II.u.i.t.a |

|---------------------|-------------|-----------------|------------|------------|----------|------------|

| I/O Standard        | Clock       | Parameter       | Industrial | Commercial | Grade    | Units      |

|                     | CCT IZ      | t <sub>su</sub> | 1.131      | 1.131      | 2.607    | ns         |

| 1.5-V HSTL CLASS I  | GCLK        | t <sub>H</sub>  | -1.026     | -1.026     | -2.330   | ns         |

| 1.3-V HOTE GLASS I  | GCLK PLL    | t <sub>su</sub> | 2.573      | 2.573      | 5.713    | ns         |

|                     | GCLK PLL    | t <sub>H</sub>  | -2.468     | -2.468     | -5.436   | ns         |

|                     | GCLK        | t <sub>su</sub> | 1.132      | 1.132      | 2.607    | ns         |

| 1.5-V HSTL CLASS II | GCTV        | t <sub>H</sub>  | -1.027     | -1.027     | -2.330   | ns         |

| 1.5-V HOTE GLASS II | GCLK PLL    | t <sub>su</sub> | 2.574      | 2.574      | 5.715    | ns         |

|                     |             | t <sub>H</sub>  | -2.469     | -2.469     | -5.438   | ns         |

|                     | GCLK -      | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns         |

| 2 2 V DOI           |             | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns         |

| 3.3-V FUI           | GGT 11 DT 1 | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns         |

| 3.3-V PCI           | GCLK PLL    | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns         |

|                     |             | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns         |

| 3.3-V PCI-X         | GCLK        | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns         |

| J.J-V FUI-A         | GCLK PLL    | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns         |

|                     | GCTV STT    | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns         |

|                     | COL V       | t <sub>su</sub> | 1.106      | 1.106      | 2.489    | ns         |

| LVDS                | GCLK        | t <sub>H</sub>  | -1.001     | -1.001     | -2.212   | ns         |

| LVDO                | CCL IV DI I | t <sub>su</sub> | 2.530      | 2.530      | 5.564    | ns         |

|                     | GCLK PLL    | t <sub>H</sub>  | -2.425     | -2.425     | -5.287   | ns         |

|                     |             |                 |            |            |          |            |

Table 4–56 lists I/O timing specifications.

Table 4-56. EP1AGX35 Row Pins Output Timing Parameters (Part 1 of 3)

| 1/0 011      | Drive    | 011-     |                 | Fast       | Model      | -6 Speed |       |

|--------------|----------|----------|-----------------|------------|------------|----------|-------|

| I/O Standard | Strength | Clock    | Parameter       | Industrial | Commercial | Grade    | Units |

| 3.3-V LVTTL  | 4 mA     | GCLK     | t <sub>co</sub> | 2.904      | 2.904      | 6.699    | ns    |

|              |          | GCLK PLL | t <sub>co</sub> | 1.485      | 1.485      | 3.627    | ns    |

| 3.3-V LVTTL  | 8 mA     | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns    |

|              |          | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns    |

| 3.3-V LVTTL  | 12 mA    | GCLK     | t <sub>co</sub> | 2.720      | 2.720      | 6.022    | ns    |

|              |          | GCLK PLL | t <sub>co</sub> | 1.301      | 1.301      | 2.950    | ns    |

| 3.3-V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns    |

| LVCMOS       |          | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns    |

| 3.3-V        | 8 mA     | GCLK     | t <sub>co</sub> | 2.670      | 2.670      | 5.753    | ns    |

| LVCMOS       |          | GCLK PLL | t <sub>co</sub> | 1.251      | 1.251      | 2.681    | ns    |

| 2.5 V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.759      | 2.759      | 6.033    | ns    |

|              |          | GCLK PLL | t <sub>co</sub> | 1.340      | 1.340      | 2.961    | ns    |

Table 4–59 lists column pin delay adders when using the regional clock in Arria GX devices.

Table 4-59. EP1AGX35 Column Pin Delay Adders for Regional Clock

| Dovomotor             | Fast (     | Corner     | C Canad Crada  | llmito |  |

|-----------------------|------------|------------|----------------|--------|--|

| Parameter             | Industrial | Commercial | -6 Speed Grade | Units  |  |

| RCLK input adder      | 0.099      | 0.099      | 0.254          | ns     |  |

| RCLK PLL input adder  | -0.012     | -0.012     | -0.01          | ns     |  |

| RCLK output adder     | -0.086     | -0.086     | -0.244         | ns     |  |

| RCLK PLL output adder | 1.253      | 1.253      | 3.133          | ns     |  |

### **EP1AGX50 I/O Timing Parameters**

Table 4–60 through Table 4–63 list the maximum I/O timing parameters for EP1AGX50 devices for I/O standards which support general purpose I/O pins.

Table 4–60 lists I/O timing specifications.

**Table 4–60.** EP1AGX50 Row Pins Input Timing Parameters (Part 1 of 2)

| I/O Otomologia | Olask    | Dawamataw       | Fast       | Model      | -6 Speed | Units |

|----------------|----------|-----------------|------------|------------|----------|-------|

| I/O Standard   | Clock    | Parameter       | Industrial | Commercial | Grade    |       |

|                | GCLK     | t <sub>su</sub> | 1.550      | 1.550      | 3.542    | ns    |

| 0.0.1/17/      |          | t <sub>H</sub>  | -1.445     | -1.445     | -3.265   | ns    |

| 3.3-V LVTTL    | GCLK PLL | t <sub>su</sub> | 2.978      | 2.978      | 6.626    | ns    |

|                |          | t <sub>H</sub>  | -2.873     | -2.873     | -6.349   | ns    |

|                | GCLK     | t <sub>su</sub> | 1.550      | 1.550      | 3.542    | ns    |

| 3.3-V LVCMOS   |          | t <sub>H</sub>  | -1.445     | -1.445     | -3.265   | ns    |

| 3.3-V LVGIVIUS | GCLK PLL | t <sub>su</sub> | 2.978      | 2.978      | 6.626    | ns    |

|                |          | t <sub>H</sub>  | -2.873     | -2.873     | -6.349   | ns    |

|                | GCLK     | t <sub>su</sub> | 1.562      | 1.562      | 3.523    | ns    |

| 2.5 V          |          | t <sub>H</sub>  | -1.457     | -1.457     | -3.246   | ns    |

| 2.5 V          | GCLK PLL | t <sub>su</sub> | 2.990      | 2.990      | 6.607    | ns    |

|                |          | t <sub>H</sub>  | -2.885     | -2.885     | -6.330   | ns    |

|                | GCLK     | t <sub>su</sub> | 1.628      | 1.628      | 3.730    | ns    |

| 1.0.1/         |          | t <sub>H</sub>  | -1.523     | -1.523     | -3.453   | ns    |

| 1.8 V          | GCLK PLL | t <sub>su</sub> | 3.056      | 3.056      | 6.814    | ns    |

|                |          | t <sub>H</sub>  | -2.951     | -2.951     | -6.537   | ns    |

| 1.5 V          | GCLK     | t <sub>su</sub> | 1.631      | 1.631      | 3.825    | ns    |

|                |          | t <sub>H</sub>  | -1.526     | -1.526     | -3.548   | ns    |

|                | GCLK PLL | t <sub>su</sub> | 3.059      | 3.059      | 6.909    | ns    |

|                |          | t <sub>H</sub>  | -2.954     | -2.954     | -6.632   | ns    |

Table 4-73.

EP1AGX90 Column Pins Input Timing Parameters (Part 3 of 3)

| I/O Standard        | Clock    | Parameter       | Fast (     | Fast Corner |        | Unito |

|---------------------|----------|-----------------|------------|-------------|--------|-------|

| i/O Stailualu       | GIUUK    | raiailietei     | Industrial | Commercial  | Grade  | Units |

|                     | GCLK     | t <sub>su</sub> | 0.901      | 0.901       | 1.986  | ns    |

| 1.5-V HSTL CLASS II |          | t <sub>H</sub>  | -0.796     | -0.796      | -1.709 | ns    |

| 1.5-V HOTE GLASS II | GCLK PLL | t <sub>su</sub> | 2.965      | 2.965       | 6.121  | ns    |

|                     |          | t <sub>H</sub>  | -2.860     | -2.860      | -5.844 | ns    |

|                     | GCLK     | t <sub>su</sub> | 1.023      | 1.023       | 2.278  | ns    |

| 3.3-V PCI           |          | t <sub>H</sub>  | -0.918     | -0.918      | -2.001 | ns    |

| 3.3-4 FOI           | GCLK PLL | t <sub>su</sub> | 3.087      | 3.087       | 6.413  | ns    |

|                     |          | t <sub>H</sub>  | -2.982     | -2.982      | -6.136 | ns    |

|                     | GCLK     | t <sub>su</sub> | 1.023      | 1.023       | 2.278  | ns    |

| 3.3-V PCI-X         |          | t <sub>H</sub>  | -0.918     | -0.918      | -2.001 | ns    |

| 3.3-V FUI-A         | GCLK PLL | t <sub>su</sub> | 3.087      | 3.087       | 6.413  | ns    |

|                     |          | t <sub>H</sub>  | -2.982     | -2.982      | -6.136 | ns    |

| LVDS                | GCLK     | t <sub>su</sub> | 0.891      | 0.891       | 1.920  | ns    |

|                     |          | t <sub>H</sub>  | -0.786     | -0.786      | -1.643 | ns    |

|                     | GCLK PLL | t <sub>su</sub> | 2.963      | 2.963       | 6.066  | ns    |

|                     |          | t <sub>H</sub>  | -2.858     | -2.858      | -5.789 | ns    |

Table 4–74 lists I/O timing specifications.

Table 4-74. EP1AGX90 Row Pins Output Timing Parameters (Part 1 of 3)

| I/O Otenderal | Drive    | Olevelo  | Davamatav       | Fast Model |            | -6 Speed | 11    |

|---------------|----------|----------|-----------------|------------|------------|----------|-------|

| I/O Standard  | Strength | Clock    | Parameter       | Industrial | Commercial | Grade    | Units |

| 3.3-V LVTTL   | 4 mA     | GCLK     | t <sub>co</sub> | 3.170      | 3.170      | 7.382    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 1.099      | 1.099      | 3.238    | ns    |

| 3.3-V LVTTL   | 8 mA     | GCLK     | t <sub>co</sub> | 3.042      | 3.042      | 6.742    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 0.971      | 0.971      | 2.598    | ns    |

| 3.3-V LVTTL   | 12 mA    | GCLK     | t <sub>co</sub> | 2.986      | 2.986      | 6.705    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 0.915      | 0.915      | 2.561    | ns    |

| 3.3-V         | 4 mA     | GCLK     | t <sub>co</sub> | 3.042      | 3.042      | 6.742    | ns    |

| LVCMOS        |          | GCLK PLL | t <sub>co</sub> | 0.971      | 0.971      | 2.598    | ns    |

| 3.3-V         | 8 mA     | GCLK     | t <sub>co</sub> | 2.936      | 2.936      | 6.436    | ns    |

| LVCMOS        |          | GCLK PLL | t <sub>co</sub> | 0.865      | 0.865      | 2.292    | ns    |

| 2.5 V         | 4 mA     | GCLK     | t <sub>co</sub> | 3.025      | 3.025      | 6.716    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 0.954      | 0.954      | 2.572    | ns    |

| 2.5 V         | 8 mA     | GCLK     | t <sub>co</sub> | 2.922      | 2.922      | 6.458    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 0.851      | 0.851      | 2.314    | ns    |

| 2.5 V         | 12 mA    | GCLK     | t <sub>co</sub> | 2.903      | 2.903      | 6.344    | ns    |

|               |          | GCLK PLL | t <sub>co</sub> | 0.832      | 0.832      | 2.200    | ns    |

**Table 4–74.** EP1AGX90 Row Pins Output Timing Parameters (Part 3 of 3)

| I/II Standard | Drive    | Clock    | Parameter         | Fast Model |            | –6 Speed | Iluito |

|---------------|----------|----------|-------------------|------------|------------|----------|--------|

|               | Strength | GIUCK    |                   | Industrial | Commercial | Grade    | Units  |

| 1.5-V HSTL    | 6 mA     | GCLK     | $t_{\mathtt{co}}$ | 2.857      | 2.857      | 6.106    | ns     |

| CLASS I       |          | GCLK PLL | t <sub>co</sub>   | 0.779      | 0.779      | 1.950    | ns     |

| 1.5-V HSTL    | 8 mA     | GCLK     | t <sub>co</sub>   | 2.842      | 2.842      | 6.098    | ns     |

| CLASS I       |          | GCLK PLL | t <sub>co</sub>   | 0.764      | 0.764      | 1.942    | ns     |

| LVDS          | _        | GCLK     | t <sub>co</sub>   | 2.898      | 2.898      | 6.265    | ns     |

| LVDO          |          | GCLK PLL | t <sub>co</sub>   | 0.831      | 0.831      | 2.129    | ns     |

Table 4–75 lists I/O timing specifications.

Table 4-75. EP1AGX90 Column Pins Output Timing Parameters (Part 1 of 4)

| I/O Standard       | Drive    | Oleak    | D               | Fast       | Corner     | –6 Speed | lluite. |

|--------------------|----------|----------|-----------------|------------|------------|----------|---------|

|                    | Strength | Clock    | Parameter       | Industrial | Commercial | Grade    | Units   |

| 3.3-V LVTTL        | 4 mA     | GCLK     | t <sub>co</sub> | 3.141      | 3.141      | 7.164    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 1.077      | 1.077      | 3.029    | ns      |

| 3.3-V LVTTL        | 8 mA     | GCLK     | t <sub>co</sub> | 2.996      | 2.996      | 6.792    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.932      | 0.932      | 2.657    | ns      |

| 3.3-V LVTTL        | 12 mA    | GCLK     | t <sub>co</sub> | 2.929      | 2.929      | 6.792    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.865      | 0.865      | 2.657    | ns      |

| 3.3-V LVTTL        | 16 mA    | GCLK     | t <sub>co</sub> | 2.903      | 2.903      | 6.623    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.839      | 0.839      | 2.488    | ns      |

| 3.3-V LVTTL        | 20 mA    | GCLK     | t <sub>co</sub> | 2.881      | 2.881      | 6.498    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.817      | 0.817      | 2.363    | ns      |

| 3.3-V LVTTL        | 24 mA    | GCLK     | t <sub>co</sub> | 2.874      | 2.874      | 6.500    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.810      | 0.810      | 2.365    | ns      |

| 3.3-V              | 4 mA     | GCLK     | t <sub>co</sub> | 2.996      | 2.996      | 6.792    | ns      |

| LVCMOS             |          | GCLK PLL | t <sub>co</sub> | 0.932      | 0.932      | 2.657    | ns      |

| 3.3-V              | 8 mA     | GCLK     | t <sub>co</sub> | 2.904      | 2.904      | 6.497    | ns      |

| LVCMOS             |          | GCLK PLL | t <sub>co</sub> | 0.840      | 0.840      | 2.362    | ns      |

| 3.3-V              | 12 mA    | GCLK     | t <sub>co</sub> | 2.876      | 2.876      | 6.419    | ns      |

| LVCMOS             |          | GCLK PLL | t <sub>co</sub> | 0.812      | 0.812      | 2.284    | ns      |

| 3.3-V              | 16 mA    | GCLK     | t <sub>co</sub> | 2.883      | 2.883      | 6.387    | ns      |

| LVCMOS             |          | GCLK PLL | t <sub>co</sub> | 0.819      | 0.819      | 2.252    | ns      |

| 3.3-V              | 20 mA    | GCLK     | t <sub>co</sub> | 2.870      | 2.870      | 6.369    | ns      |

| LVCMOS             |          | GCLK PLL | t <sub>co</sub> | 0.806      | 0.806      | 2.234    | ns      |

| 3.3-V 24 mA LVCMOS | 24 mA    | GCLK     | t <sub>co</sub> | 2.859      | 2.859      | 6.347    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.795      | 0.795      | 2.212    | ns      |

| 2.5 V              | 4 mA     | GCLK     | t <sub>co</sub> | 2.958      | 2.958      | 6.824    | ns      |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.894      | 0.894      | 2.689    | ns      |

Table 4-75.

EP1AGX90 Column Pins Output Timing Parameters (Part 2 of 4)

| I/O Ctondord       | Drive    | Clock    | Parameter ·     | Fast Corner |            | –6 Speed | Units  |

|--------------------|----------|----------|-----------------|-------------|------------|----------|--------|

| I/O Standard       | Strength | Clock    |                 | Industrial  | Commercial | Grade    | UIIICS |

| 2.5 V              | 8 mA     | GCLK     | t <sub>co</sub> | 2.906       | 2.906      | 6.562    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.842       | 0.842      | 2.427    | ns     |

| 2.5 V              | 12 mA    | GCLK     | t <sub>co</sub> | 2.885       | 2.885      | 6.445    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.821       | 0.821      | 2.310    | ns     |

| 2.5 V              | 16 mA    | GCLK     | t <sub>co</sub> | 2.867       | 2.867      | 6.371    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.803       | 0.803      | 2.236    | ns     |

| 1.8 V              | 2 mA     | GCLK     | t <sub>co</sub> | 2.998       | 2.998      | 7.816    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.934       | 0.934      | 3.681    | ns     |

| 1.8 V              | 4 mA     | GCLK     | t <sub>co</sub> | 3.003       | 3.003      | 7.042    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.939       | 0.939      | 2.907    | ns     |

| 1.8 V              | 6 mA     | GCLK     | t <sub>co</sub> | 2.927       | 2.927      | 6.778    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.863       | 0.863      | 2.643    | ns     |

| 1.8 V              | 8 mA     | GCLK     | t <sub>co</sub> | 2.929       | 2.929      | 6.687    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.865       | 0.865      | 2.552    | ns     |

| 1.8 V              | 10 mA    | GCLK     | t <sub>co</sub> | 2.883       | 2.883      | 6.610    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.819       | 0.819      | 2.475    | ns     |

| 1.8 V              | 12 mA    | GCLK     | t <sub>co</sub> | 2.884       | 2.884      | 6.553    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.820       | 0.820      | 2.418    | ns     |

| 1.5 V 2 mA         | 2 mA     | GCLK     | t <sub>co</sub> | 2.978       | 2.978      | 7.346    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.914       | 0.914      | 3.211    | ns     |

| 1.5 V              | 4 mA     | GCLK     | t <sub>co</sub> | 2.914       | 2.914      | 6.777    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.850       | 0.850      | 2.642    | ns     |

| 1.5 V              | 6 mA     | GCLK     | t <sub>co</sub> | 2.917       | 2.917      | 6.659    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.853       | 0.853      | 2.524    | ns     |

| 1.5 V              | 8 mA     | GCLK     | t <sub>co</sub> | 2.876       | 2.876      | 6.606    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.812       | 0.812      | 2.471    | ns     |

| SSTL-2             | 8 mA     | GCLK     | t <sub>co</sub> | 2.859       | 2.859      | 6.381    | ns     |

| CLASS I            |          | GCLK PLL | t <sub>co</sub> | 0.797       | 0.797      | 2.250    | ns     |

| SSTL-2             | 12 mA    | GCLK     | t <sub>co</sub> | 2.842       | 2.842      | 6.331    | ns     |

| CLASS I            |          | GCLK PLL | t <sub>co</sub> | 0.780       | 0.780      | 2.200    | ns     |

| SSTL-2<br>CLASS II | 16 mA    | GCLK     | t <sub>co</sub> | 2.820       | 2.820      | 6.258    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.758       | 0.758      | 2.127    | ns     |

| SSTL-2<br>CLASS II | 20 mA    | GCLK     | t <sub>co</sub> | 2.821       | 2.821      | 6.245    | ns     |

|                    |          | GCLK PLL | t <sub>co</sub> | 0.759       | 0.759      | 2.114    | ns     |

| SSTL-2             | 24 mA    | GCLK     | t <sub>co</sub> | 2.817       | 2.817      | 6.243    | ns     |

| CLASS II           |          | GCLK PLL | t <sub>co</sub> | 0.755       | 0.755      | 2.112    | ns     |

| SSTL-18            | 4 mA     | GCLK     | t <sub>co</sub> | 2.858       | 2.858      | 6.356    | ns     |

| CLASS I            |          | GCLK PLL | t <sub>co</sub> | 0.794       | 0.794      | 2.221    | ns     |

Table 4-107. Arria GX Maximum Output Clock Rate for Dedicated Clock Pins (Part 2 of 4)

| I/O Standards                    | Drive Strength | –6 Speed Grade | Units |

|----------------------------------|----------------|----------------|-------|

| SSTL-2 CLASS I                   | 8 mA           | 280            | MHz   |

| 001L-2 0LA001                    | 12 mA          | 327            | MHz   |

|                                  | 16 mA          | 280            | MHz   |

| SSTL-2 CLASS II                  | 20 mA          | 327            | MHz   |

| Γ                                | 24 mA          | 327            | MHz   |

|                                  | 4 mA           | 140            | MHz   |

|                                  | 6 mA           | 186            | MHz   |

| SSTL-18 CLASS I                  | 8 mA           | 280            | MHz   |

|                                  | 10 mA          | 373            | MHz   |

|                                  | 12 mA          | 373            | MHz   |

|                                  | 8 mA           | 140            | MHz   |

| SSTL-18 CLASS II                 | 16 mA          | 327            | MHz   |

| 331L-10 ULASS II —               | 18 mA          | 373            | MHz   |

|                                  | 20 mA          | 420            | MHz   |

|                                  | 4 mA           | 280            | MHz   |

|                                  | 6 mA           | 420            | MHz   |

| 1.8-V HSTL CLASS I               | 8 mA           | 561            | MHz   |

|                                  | 10 mA          | 561            | MHz   |

|                                  | 12 mA          | 607            | MHz   |

|                                  | 16 mA          | 420            | MHz   |

| 1.8-V HSTL CLASS II              | 18 mA          | 467            | MHz   |

|                                  | 20 mA          | 514            | MHz   |

|                                  | 4 mA           | 280            | MHz   |

|                                  | 6 mA           | 420            | MHz   |

| 1.5-V HSTL CLASS I               | 8 mA           | 561            | MHz   |

|                                  | 10mA           | 607            | MHz   |

|                                  | 12 mA          | 654            | MHz   |

|                                  | 16 mA          | 514            | MHz   |

| 15 V HOTI CLASS II               | 18 mA          | 561            | MHz   |

| 1.5-V HSTL CLASS II –            | 20 mA          | 561            | MHz   |

|                                  | 24 mA          | 278            | MHz   |

| DIFFERENTIAL SSTL-2              | 8 mA           | 280            | MHz   |

| DITTEMENTIAL SSTE-2              | 12 mA          | 327            | MHz   |

| DIFFERENTIAL OF M                | 16 mA          | 280            | MHz   |

| DIFFERENTIAL 2.5-V SSTL CLASS II | 20 mA          | 327            | MHz   |

|                                  | 24 mA          | 327            | MHz   |