Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 2508                                                         |

| Number of Logic Elements/Cells | 50160                                                        |

| Total RAM Bits                 | 2475072                                                      |

| Number of I/O                  | 514                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 1152-BBGA                                                    |

| Supplier Device Package        | 1152-FBGA (35x35)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1agx50df1152i6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ■ Main device features:

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers with performance up to 380 MHz

- Up to 16 global clock networks with up to 32 regional clock networks per device

- High-speed DSP blocks provide dedicated implementation of multipliers, multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to four enhanced phase-locked loops (PLLs) per device provide spread spectrum, programmable bandwidth, clock switch-over, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed source-synchronous differential I/O support on up to 47 channels

- Support for source-synchronous bus standards, including SPI-4 Phase 2 (POS-PHY Level 4), SFI-4.1, XSBI, UTOPIA IV, NPSI, and CSIX-L1

- Support for high-speed external memory including DDR and DDR2 SDRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera® MegaCore® functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>)

- Support for remote configuration updates

Table 1–1 lists Arria GX device features for FineLine BGA (FBGA) with flip chip packages.

Table 1-1. Arria GX Device Features (Part 1 of 2)

| Facture                                       | EP1AGX20C                          | EP1AG                  | X35C/D                 | EP1AG                     | X50C/D                              | E                      | P1AGX60C/D             | )/E                       | EP1AGX90E               |                              |        |

|-----------------------------------------------|------------------------------------|------------------------|------------------------|---------------------------|-------------------------------------|------------------------|------------------------|---------------------------|-------------------------|------------------------------|--------|

| Feature                                       | С                                  | C                      | D                      | C                         | D                                   | C                      | D                      | E                         | E                       |                              |        |

| Package                                       | 484-pin,<br>780-pin<br>(Flip chip) | 484-pin<br>(Flip chip) | 780-pin<br>(Flip chip) | 484-pin<br>(Flip chip)    | 780-pin,<br>1152-pin<br>(Flip chip) | 484-pin<br>(Flip chip) | 780-pin<br>(Flip chip) | 1152-pin<br>(Flip chip)   | 1152-pin<br>(Flip chip) |                              |        |

| ALMs                                          | 8,632                              | 13,                    | 408                    | 20                        | ,064                                |                        | 24,040                 | •                         | 36,088                  |                              |        |

| Equivalent logic elements (LEs)               | 21,580                             | 33,                    | 520                    | 50,160                    |                                     | 60,100                 |                        | 60,100                    |                         |                              | 90,220 |

| Transceiver channels                          | 4                                  | 4                      | 8                      | 4                         | 8                                   | 4                      | 8                      | 12                        | 12                      |                              |        |

| Transceiver data rate                         | 600 Mbps<br>to 3.125<br>Gbps       |                        | s to 3.125<br>ops      | 600 Mbps to 3.125<br>Gbps |                                     | 600 Mbps to 3.125 Gbps |                        | 25 600 Mbps to 3.125 Gbps |                         | 600 Mbps<br>to 3.125<br>Gbps |        |

| Source-<br>synchronous<br>receive<br>channels | 31                                 | 31                     | 31                     | 31                        | 31, 42                              | 31                     | 31                     | 42                        | 47                      |                              |        |

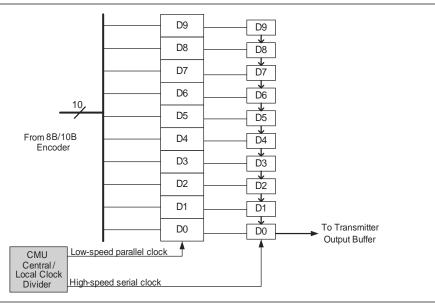

Figure 2–7 shows the serializer block diagram.

Figure 2-7. Serializer

## **Transmitter Buffer**

The Arria GX transceiver buffers support the 1.2- and 1.5-V PCML I/O standard at rates up to 3.125 Gbps. The common mode voltage ( $V_{CM}$ ) of the output driver may be set to 600 or 700 mV.

For more information about the Arria GX transceiver buffers, refer to the *Arria GX Transceiver Architecture* chapter.

The output buffer, as shown in Figure 2–8, is directly driven by the high-speed data serializer and consists of a programmable output driver, a programmable pre-emphasis circuit, and OCT circuitry.

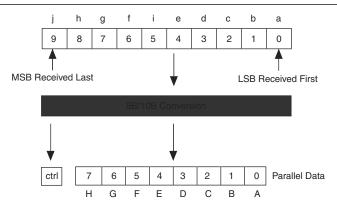

# 8B/10B Decoder

The 8B/10B decoder is used in all supported functional modes. The 8B/10B decoder takes in 10-bit data from the rate matcher and decodes it into 8-bit data + 1-bit control identifier, thereby restoring the original transmitted data at the receiver. The 8B/10B decoder indicates whether the received 10-bit character is a data or control code through the rx\_ctrldetect port. If the received 10-bit code group is a control character (Kx.y), the rx\_ctrldetect signal is driven high and if it is a data character (Dx.y), the rx\_ctrldetect signal is driven low.

Figure 2–17 shows a 10-bit code group decoded to an 8-bit data and a 1-bit control indicator.

Figure 2–17. 10-Bit to 8-Bit Conversion

If the received 10-bit code is not a part of valid Dx.y or Kx.y code groups, the 8B/10B decoder block asserts an error flag on the rx\_errdetect port. If the received 10-bit code is detected with incorrect running disparity, the 8B/10B decoder block asserts an error flag on the rx\_disperr and rx\_errdetect ports. The error flag signals (rx\_errdetect and rx\_disperr) have the same data path delay from the 8B/10B decoder to the PLD-transceiver interface as the bad code group.

#### **Receiver State Machine**

The receiver state machine operates in Basic, GIGE, PCI Express (PIPE), and XAUI modes. In GIGE mode, the receiver state machine replaces invalid code groups with K30.7. In XAUI mode, the receiver state machine translates the XAUI PCS code group to the XAUI XGMII code group.

# **Reverse Serial Pre-CDR Loopback**

Reverse serial pre-CDR loopback mode uses the analog portion of the transceiver. An external source (pattern generator or transceiver) generates the source data. The high-speed serial source data arrives at the high-speed differential receiver input buffer, loops back before the CRU unit, and is transmitted though the high-speed differential transmitter output buffer. It is for test or verification use only to verify the signal being received after the gain and equalization improvements of the input buffer. The signal at the output is not exactly what is received because the signal goes through the output buffer and the  $\rm V_{\rm OD}$  is changed to the  $\rm V_{\rm OD}$  setting level. Pre-emphasis settings have no effect.

Figure 2–20 shows the Arria GX block in reverse serial pre-CDR loopback mode.

Transmitter Digital Logic **Analog Receiver and** Transmitter Logic PRBS Incrementa 8R/10R Compensation Encode FPGA Logic Array Reverse Serial Pre-CDR Loopback Verify **Receiver Digital Logic**

Figure 2-20. Arria GX Block in Reverse Serial Pre-CDR Loopback Mode

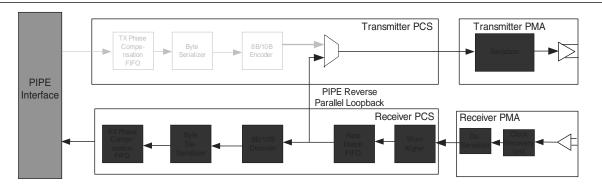

# **PCI Express (PIPE) Reverse Parallel Loopback**

Figure 2–21 shows the data path for PCI Express (PIPE) reverse parallel loopback. The reverse parallel loopback configuration is compliant with the PCI Express (PIPE) specification and is available only on PCI Express (PIPE) mode.

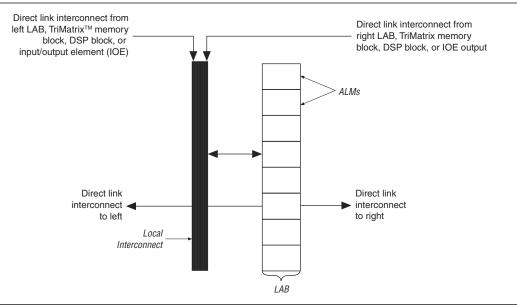

Figure 2–26 shows the direct link connection.

Figure 2–26. Direct Link Connection

# **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset or load, and synchronous load control signals, providing a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–27. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock. Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack interconnects have inherently low skew. This low skew allows the MultiTrack interconnects to distribute clock and control signals in addition to data.

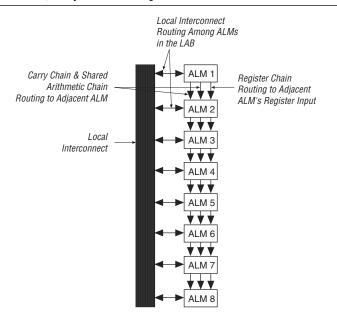

Figure 2–40. Shared Arithmetic Chain, Carry Chain and Register Chain Interconnects

C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–41 shows the C4 interconnect connections from a LAB in a column. C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

**Table 2–13.** DSP Blocks in Arria GX Devices (Note 1)

| Device   | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |

|----------|------------|----------------------------|------------------------------|------------------------------|

| EP1AGX20 | 10         | 80                         | 40                           | 10                           |

| EP1AGX35 | 14         | 112                        | 56                           | 14                           |

| EP1AGX50 | 26         | 208                        | 104                          | 26                           |

| EP1AGX60 | 32         | 256                        | 128                          | 32                           |

| EP1AGX90 | 44         | 352                        | 176                          | 44                           |

## Note to Table 2-13:

Additionally, DSP block input registers can efficiently implement shift registers for FIR filter applications. DSP blocks support Q1.15 format rounding and saturation. Figure 2–51 shows a top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode.

<sup>(1)</sup> This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

# **Enhanced PLLs**

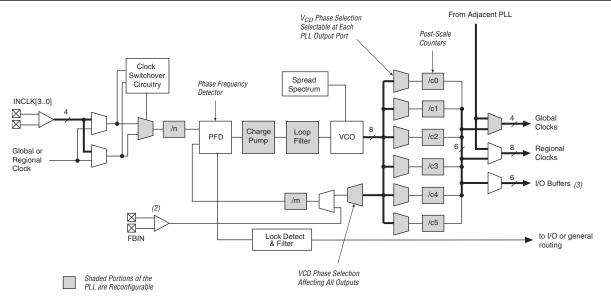

Arria GX devices contain up to four enhanced PLLs with advanced clock management features. These features include support for external clock feedback mode, spread-spectrum clocking, and counter cascading. Figure 2–65 shows a diagram of the enhanced PLL.

Figure 2–65. Arria GX Enhanced PLL (Note 1)

# Notes to Figure 2-65:

- (1) Each clock source can come from any of the four clock pins that are physically located on the same side of the device as the PLL.

- (2) If the feedback input is used, you will lose one (or two, if FBIN is differential) external clock output pin.

- (3) Each enhanced PLL has three differential external clock outputs or six single-ended external clock outputs.

- (4) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

## **Fast PLLs**

Arria GX devices contain up to four fast PLLs with high-speed serial interfacing ability. Fast PLLs offer high-speed outputs to manage the high-speed differential I/O interfaces. Figure 2–66 shows a diagram of the fast PLL.

Table 4-6. Arria GX Transceiver Block AC Specification (Part 3 of 3)

| Symbol / Description                                       | Conditions   | –6 Speed | ercial and                         | Units  |     |

|------------------------------------------------------------|--------------|----------|------------------------------------|--------|-----|

|                                                            |              | Min      | Тур                                | Max    |     |

| Transmitter PLL                                            |              |          |                                    |        |     |

| VCO frequency range                                        | _            | 500      | _                                  | 1562.5 | MHz |

|                                                            | BW = Low     | _        | 3                                  | _      |     |

| Bandwidth at 3.125 Gbps                                    | BW = Med     | _        | 5                                  | _      | MHz |

|                                                            | BW = High    | _        | 9                                  | _      |     |

|                                                            | BW = Low     | _        | 1                                  | _      |     |

| Bandwidth at 2.5 Gbps                                      | BW = Med     | _        | 2                                  | _      | MHz |

|                                                            | BW = High    | _        | 4                                  | _      |     |

| TX PLL lock time from gxb_powerdown de-assertion (9), (14) | _            | _        | _                                  | 100    | us  |

| PCS                                                        |              |          |                                    |        |     |

| Interface speed per mode                                   | <del>_</del> | 25       | _                                  | 156.25 | MHz |

| Digital Reset Pulse Width                                  | _            | Minimum  | Minimum is 2 parallel clock cycles |        |     |

#### Notes to Table 4-6:

- (1) Spread spectrum clocking is allowed only in PCI Express (PIPE) mode if the upstream transmitter and the receiver share the same clock source.

- (2) The reference clock DC coupling option is only available in PCI Express (PIPE) mode for the HCSL I/O standard.

- (3) The fixedclk is used in PIPE mode receiver detect circuitry.

- (4) The device cannot tolerate prolonged operation at this absolute maximum.

- (5) The rate matcher supports only up to  $\pm$  300 PPM for PIPE mode and  $\pm$  100 PPM for GIGE mode.

- (6) This parameter is measured by embedding the run length data in a PRBS sequence.

- (7) Signal detect threshold detector circuitry is available only in PCI Express (PIPE mode).

- (8) Time taken for  $rx_pll_locked$  to go high from  $rx_analogreset$  deassertion. Refer to Figure 4–1.

- (9) For lock times specific to the protocols, refer to protocol characterization documents.

- (10) Time for which the CDR needs to stay in LTR mode after rx\_pll\_locked is asserted and before rx\_locktodata is asserted in manual mode. Refer to Figure 4–1.

- (11) Time taken to recover valid data from GXB after the rx\_locktodata signal is asserted in manual mode. Measurement results are based on PRBS31, for native data rates only. Refer to Figure 4–1.

- (12) Time taken to recover valid data from GXB after the rx\_freqlocked signal goes high in automatic mode. Measurement results are based on PRBS31, for native data rates only. Refer to Figure 4–2.

- (13) This is applicable only to PCI Express (PIPE) ×4 and XAUI ×4 mode.

- (14) Time taken to lock TX PLL from gxb\_powerdown deassertion.

- (15) The 1.2 V RX VICM settings is intended for DC-coupled LVDS links.

Figure 4–1 shows the lock time parameters in manual mode. Figure 4–2 shows the lock time parameters in automatic mode.

LTD = Lock to data

LTR = Lock to reference clock

Table 4–8 and Table 4–9 list the transmitter and receiver PCS latency for each mode, respectively.

**Table 4–8.** PCS Latency (Note 1)

|                 |                                    | Transmitter PCS Latency |                       |                    |                     |                             |                |  |  |

|-----------------|------------------------------------|-------------------------|-----------------------|--------------------|---------------------|-----------------------------|----------------|--|--|

| Functional Mode | Configuration                      | TX PIPE                 | TX Phase<br>Comp FIFO | Byte<br>Serializer | TX State<br>Machine | 8B/10B<br>Encoder           | <b>Sum</b> (2) |  |  |

| XAUI            | _                                  | _                       | 2–3                   | 1                  | 0.5                 | 0.5                         | 4–5            |  |  |

| PIPE            | ×1, ×4, ×8<br>8-bit channel width  | 1                       | 3–4                   | 1                  | _                   | 1                           | 6–7            |  |  |

| FIFL            | ×1, ×4, ×8<br>16-bit channel width | 1                       | 3–4                   | 1                  | _                   | 0.5                         | 6–7            |  |  |

| GIGE            | _                                  | _                       | 2–3                   | 1                  | _                   | 1                           | 4–5            |  |  |

| Serial RapidIO  | 1.25 Gbps, 2.5 Gbps,<br>3.125 Gbps | _                       | 2–3                   | 1                  | _                   | 0.5                         | 4–5            |  |  |

| SDI             | HD10-bit channel width             | _                       | 2–3                   | 1                  | _                   | 1                           | 4–5            |  |  |

| ועט             | HD, 3G 20-bit channel width        | _                       | 2–3                   | 1                  | _                   | 0.5<br>1<br>0.5<br>1<br>0.5 | 4–5            |  |  |

| BASIC Single    | 8-bit/10-bit channel width         | _                       | 2–3                   | 1                  | _                   | 1                           | 4–5            |  |  |

| Width           | 16-bit/20-bit channel width        | _                       | 2–3                   | 1                  | _                   | 0.5                         | 4–5            |  |  |

#### Notes to Table 4-8:

- (1) The latency numbers are with respect to the PLD-transceiver interface clock cycles.

- (2) The total latency number is rounded off in the Sum column.

**Table 4–9.** PCS Latency (Part 1 of 2) (Part 1 of 2)

|                   |                                    |              |             |                  | Rece           | eiver PCS              | Latenc            | у          |                          |               |         |

|-------------------|------------------------------------|--------------|-------------|------------------|----------------|------------------------|-------------------|------------|--------------------------|---------------|---------|

| Functional Mode   | Configuration                      | Word Aligner | Deskew FIFO | Rate Matcher (3) | 8B/10B Decoder | Receiver State Machine | Byte Deserializer | Byte Order | Receiver Phase Comp FIFO | Receiver PIPE | Sum (2) |

| XAUI              | _                                  | 2-2.5        | 2-2.5       | 5.5-6.5          | 0.5            | 1                      | 1                 | 1          | 1–2                      | _             | 14–17   |

| PIPE              | ×1, ×4<br>8-bit channel width      | 4–5          | _           | 11–13            | 1              | _                      | 1                 | 1          | 2–3                      | 1             | 21–25   |

|                   | ×1, ×4<br>16-bit channel width     | 2–2.5        | _           | 5.5–6.5          | 0.5            | _                      | 1                 | 1          | 2–3                      | 1             | 13–16   |

| GIGE              | _                                  | 4–5          |             | 11–13            | 1              | _                      | 1                 | 1          | 1–2                      | _             | 19–23   |

| Serial<br>RapidIO | 1.25 Gbps, 2.5 Gbps,<br>3.125 Gbps | 2–2.5        | _           | _                | 0.5            | _                      | 1                 | 1          | 1–2                      | _             | 6–7     |

|                   | HD 10-bit channel width            | 5            | _           | _                | 1              | _                      | 1                 | 1          | 1–2                      | _             | 9–10    |

| SDI               | HD, 3G 20-bit channel width        | 2.5          | _           | _                | 0.5            | _                      | 1                 | 1          | 1–2                      |               | 6–7     |

**Table 4–14.** Arria GX Device DC Operating Conditions (Part 2 of 2) (Note 1)

| Symbol                | Parameter                                                                                | Conditions                             | Device | Min | Тур | Max | Units |

|-----------------------|------------------------------------------------------------------------------------------|----------------------------------------|--------|-----|-----|-----|-------|

|                       |                                                                                          | $V_i = 0$ , $V_{CCIO} = 3.3 \text{ V}$ | _      | 10  | 25  | 50  | kΩ    |

|                       | Value of I/O pin pull-up                                                                 | $V_i = 0$ , $V_{CCIO} = 2.5 \text{ V}$ | _      | 15  | 35  | 70  | kΩ    |

|                       | resistor before and during                                                               | $V_i = 0, V_{CCIO} = 1.8 \text{ V}$    | _      | 30  | 50  | 100 | kΩ    |

| D (4)                 | configuration                                                                            | $V_i = 0, V_{CCIO} = 1.5 \text{ V}$    | _      | 40  | 75  | 150 | kΩ    |

| R <sub>CONF</sub> (4) |                                                                                          | $V_i = 0, V_{CCIO} = 1.2 \text{ V}$    | _      | 50  | 90  | 170 | kΩ    |

|                       | Recommended value of I/O pin external pull-down resistor before and during configuration | _                                      | _      | _   | 1   | 2   | kΩ    |

## Notes to Table 4-14:

- (1) Typical values are for  $T_A$  = 25 °C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, 1.5, and 1.2 V).

- (3) Maximum values depend on the actual TJ and design utilization. For maximum values, refer to the Excel-based PowerPlay Early Power Estimator (available at PowerPlay Early Power Estimators (EPE) and Power Analyzer) or the Quartus<sup>®</sup> II PowerPlay Power Analyzer feature for maximum values. For more information, refer to "Power Consumption" on page 4–25.

- (4) Pin pull-up resistance values will be lower if an external source drives the pin higher than  $V_{CCIO}$ .

# I/O Standard Specifications

Table 4–15 through Table 4–38 show the Arria GX device family I/O standard specifications.

Table 4-15. LVTTL Specifications

| Symbol                | Parameter                 | Conditions                         | Minimum | Maximum | Units |

|-----------------------|---------------------------|------------------------------------|---------|---------|-------|

| V <sub>CCIO</sub> (1) | Output supply voltage     | _                                  | 3.135   | 3.465   | V     |

| V <sub>IH</sub>       | High-level input voltage  | _                                  | 1.7     | 4.0     | V     |

| V <sub>IL</sub>       | Low-level input voltage   | _                                  | -0.3    | 0.8     | V     |

| V <sub>OH</sub>       | High-level output voltage | I <sub>OH</sub> = -4 mA <i>(2)</i> | 2.4     | _       | V     |

| V <sub>OL</sub>       | Low-level output voltage  | I <sub>OL</sub> = 4 mA <i>(2)</i>  | _       | 0.45    | V     |

#### Notes to Table 4-15:

- (1) Arria GX devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- (2) This specification is supported across all the programmable drive strength settings available for this I/O standard.

Table 4–16. LVCMOS Specifications

| Symbol                | Parameter                 | Conditions                                      | Minimum                 | Maximum | Units |

|-----------------------|---------------------------|-------------------------------------------------|-------------------------|---------|-------|

| V <sub>CCIO</sub> (1) | Output supply voltage     | _                                               | 3.135                   | 3.465   | V     |

| V <sub>IH</sub>       | High-level input voltage  | _                                               | 1.7                     | 4.0     | ٧     |

| V <sub>IL</sub>       | Low-level input voltage   | _                                               | -0.3                    | 0.8     | V     |

| V <sub>OH</sub>       | High-level output voltage | $V_{CCIO} = 3.0, I_{OH} = -0.1 \text{ mA } (2)$ | V <sub>CC10</sub> - 0.2 | _       | V     |

| V <sub>OL</sub>       | Low-level output voltage  | $V_{CCIO} = 3.0, I_{OL} = 0.1 \text{ mA } (2)$  | _                       | 0.2     | V     |

#### Notes to Table 4-16:

- (1) Arria GX devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- $(2) \quad \text{This specification is supported across all the programmable drive strength available for this I/O standard.}$

Table 4-30. SSTL-2 Class II Specifications (Part 2 of 2)

| Symbol               | Parameter                   | Conditions                           | Minimum                 | Typical | Maximum                 | Units |

|----------------------|-----------------------------|--------------------------------------|-------------------------|---------|-------------------------|-------|

| V <sub>IL</sub> (DC) | Low-level DC input voltage  | _                                    | -0.3                    | _       | V <sub>REF</sub> - 0.18 | V     |

| V <sub>IH</sub> (AC) | High-level AC input voltage | _                                    | V <sub>REF</sub> + 0.35 | _       | _                       | V     |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  | _                                    | _                       | _       | V <sub>REF</sub> - 0.35 | V     |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -16.4 \text{ mA } (1)$     | V <sub>⊤⊤</sub> + 0.76  | _       | _                       | V     |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OL</sub> = 16.4 mA <i>(1)</i> | _                       | _       | V <sub>π</sub> − 0.76   | V     |

#### Note to Table 4-30:

**Table 4–31.** SSTL-2 Class I & II Differential Specifications (Note 1)

| Symbol                  | Parameter                                   | Minimum              | Typical               | Maximum              | Units |

|-------------------------|---------------------------------------------|----------------------|-----------------------|----------------------|-------|

| V <sub>CCIO</sub>       | Output supply voltage                       | 2.375                | 2.5                   | 2.625                | V     |

| V <sub>SWING</sub> (DC) | DC differential input voltage               | 0.36                 | _                     | _                    | V     |

| V <sub>x</sub> (AC)     | AC differential input cross point voltage   | $(V_{CCIO}/2) - 0.2$ | _                     | $(V_{CCIO}/2) + 0.2$ | V     |

| V <sub>SWING</sub> (AC) | AC differential input voltage               | 0.7                  | _                     | _                    | V     |

| V <sub>ISO</sub>        | Input clock signal offset voltage           | _                    | 0.5 V <sub>ccio</sub> | _                    | V     |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation | <del></del>          | 200                   | _                    | mV    |

| V <sub>ox</sub> (AC)    | AC differential output cross point voltage  | $(V_{CCIO}/2) - 0.2$ | _                     | $(V_{CC10}/2) + 0.2$ | V     |

#### Note to Table 4-31:

Table 4-32. 1.2-V HSTL Specifications

| Symbol               | Parameter                   | Minimum                 | Typical               | Maximum                  | Units |

|----------------------|-----------------------------|-------------------------|-----------------------|--------------------------|-------|

| V <sub>CCIO</sub>    | Output supply voltage       | 1.14                    | 1.2                   | 1.26                     | V     |

| $V_{REF}$            | Reference voltage           | 0.48 V <sub>ccio</sub>  | 0.5 V <sub>CCIO</sub> | 0.52 V <sub>ccio</sub>   | V     |

| V <sub>IH</sub> (DC) | High-level DC input voltage | V <sub>REF</sub> + 0.08 | _                     | V <sub>CCIO</sub> + 0.15 | V     |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  | -0.15                   | _                     | V <sub>REF</sub> - 0.08  | V     |

| V <sub>IH</sub> (AC) | High-level AC input voltage | V <sub>REF</sub> + 0.15 | _                     | V <sub>CCIO</sub> + 0.24 | V     |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  | -0.24                   | _                     | V <sub>REF</sub> - 0.15  | V     |

| V <sub>OH</sub>      | High-level output voltage   | V <sub>REF</sub> + 0.15 | _                     | V <sub>CCIO</sub> + 0.15 | V     |

| V <sub>0L</sub>      | Low-level output voltage    | -0.15                   | _                     | V <sub>REF</sub> - 0.15  | V     |

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the Arria GX Architecture chapter.

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the Arria GX Architecture chapter.

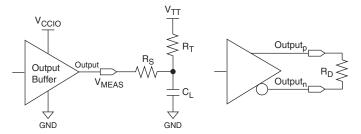

Figure 4-7. Output Delay Timing Reporting Setup Modeled by Quartus II

# Notes to Figure 4-7:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2)  $V_{\text{CCPD}}$  is 3.085 V unless otherwise specified.

- (3) V<sub>CCINT</sub> is 1.12 V unless otherwise specified.

**Table 4–44.** Output Timing Measurement Methodology for Output Pins (Note 1), (2), (3)

| I/O Standard                     |                           | Loading and Termination   |                           |                          |                     |                     |                       |

|----------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|---------------------|---------------------|-----------------------|

| I/O Standard                     | <b>R</b> <sub>S</sub> (Ω) | <b>R</b> <sub>D</sub> (Ω) | <b>R</b> <sub>T</sub> (Ω) | V <sub>CC10</sub><br>(V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |

| LVTTL (4)                        | _                         | _                         | _                         | 3.135                    | _                   | 0                   | 1.5675                |

| LVCMOS (4)                       |                           | _                         | _                         | 3.135                    | _                   | 0                   | 1.5675                |

| 2.5 V (4)                        | _                         | _                         | _                         | 2.375                    | _                   | 0                   | 1.1875                |

| 1.8 V <i>(4)</i>                 |                           | _                         | _                         | 1.710                    | _                   | 0                   | 0.855                 |

| 1.5 V <i>(4)</i>                 | _                         | _                         | _                         | 1.425                    | _                   | 0                   | 0.7125                |

| PCI (5)                          | _                         | _                         | _                         | 2.970                    | _                   | 10                  | 1.485                 |

| PCI-X (5)                        |                           | _                         | _                         | 2.970                    | _                   | 10                  | 1.485                 |

| SSTL-2 Class I                   | 25                        | _                         | 50                        | 2.325                    | 1.123               | 0                   | 1.1625                |

| SSTL-2 Class II                  | 25                        | _                         | 25                        | 2.325                    | 1.123               | 0                   | 1.1625                |

| SSTL-18 Class I                  | 25                        | _                         | 50                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| SSTL-18 Class II                 | 25                        | _                         | 25                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class I               |                           | _                         | 50                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class II              |                           | _                         | 25                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| 1.5-V HSTL Class I               | _                         | _                         | 50                        | 1.375                    | 0.648               | 0                   | 0.6875                |

| 1.5-V HSTL Class II              | _                         | _                         | 25                        | 1.375                    | 0.648               | 0                   | 0.6875                |

| 1.2-V HSTL with OCT              | _                         | _                         | _                         | 1.140                    | _                   | 0                   | 0.570                 |

| Differential SSTL-2 Class I      | 25                        | _                         | 50                        | 2.325                    | 1.123               | 0                   | 1.1625                |

| Differential SSTL-2 Class II     | 25                        | _                         | 25                        | 2.325                    | 1.123               | 0                   | 1.1625                |

| Differential SSTL-18 Class I     | 50                        | _                         | 50                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| Differential SSTL-18 Class II    | 25                        | _                         | 25                        | 1.660                    | 0.790               | 0                   | 0.83                  |

| 1.5-V differential HSTL Class I  | _                         | _                         | 50                        | 1.375                    | 0.648               | 0                   | 0.6875                |

| 1.5-V differential HSTL Class II | _                         | _                         | 25                        | 1.375                    | 0.648               | 0                   | 0.6875                |

| 1.8-V differential HSTL Class I  |                           | _                         | 50                        | 1.660                    | 0.790               | 0                   | 0.83                  |

**Table 4–45.** Timing Measurement Methodology for Input Pins (Note 1), (2), (3), (4) (Part 2 of 2)

| I/O Standard                     | Ме                    | Measurement Point    |                |           |

|----------------------------------|-----------------------|----------------------|----------------|-----------|

| I/O Stanuaru                     | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | VMEAS (V) |

| Differential SSTL-18 Class II    | 1.660                 | 0.830                | 1.660          | 0.83      |

| 1.5-V differential HSTL Class I  | 1.375                 | 0.688                | 1.375          | 0.6875    |

| 1.5-V differential HSTL Class II | 1.375                 | 0.688                | 1.375          | 0.6875    |

| 1.8-V differential HSTL Class I  | 1.660                 | 0.830                | 1.660          | 0.83      |

| 1.8-V differential HSTL Class II | 1.660                 | 0.830                | 1.660          | 0.83      |

| LVDS                             | 2.325                 | _                    | 0.100          | 1.1625    |

| LVPECL                           | 3.135                 | _                    | 0.100          | 1.5675    |

#### Notes to Table 4-45:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is 0.5  $V_{\text{CCIO}}$ .

- (3) Output measuring point is  $0.5 V_{CC}$  at internal node.

- (4) Input edge rate is 1 V/ns.

- (5) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple.

- (6)  $V_{CCPD} = 2.97$  V, less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V.

# **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, the intra-clock network skew adder is not specified. Table 4–46 specifies the intra clock skew between any two clock networks driving any registers in the Arria GX device.

**Table 4–46.** Clock Network Specifications

| Name             | Description                      | Min | Тур | Max   | Units |

|------------------|----------------------------------|-----|-----|-------|-------|

| Clock skew adder | Inter-clock network, same side   | _   | _   | ± 50  | ps    |

| EP1AGX20/35 (1)  | Inter-clock network, entire chip | _   | _   | ± 100 | ps    |

| Clock skew adder | Inter-clock network, same side   | _   | _   | ± 50  | ps    |

| EP1AGX50/60 (1)  | Inter-clock network, entire chip | _   | _   | ± 100 | ps    |

| Clock skew adder | Inter-clock network, same side   |     | _   | ± 55  | ps    |

| EP1AGX90 (1)     | Inter-clock network, entire chip | _   | _   | ± 110 | ps    |

#### Note to Table 4-46:

# **Default Capacitive Loading of Different I/O Standards**

See Table 4–47 for default capacitive loading of different I/O standards.

**Table 4–47.** Default Loading of Different I/O Standards for Arria GX Devices (Part 1 of 2)

| I/O Standard | Capacitive Load | Units |

|--------------|-----------------|-------|

| LVTTL        | 0               | pF    |

| LVCMOS       | 0               | pF    |

| 2.5 V        | 0               | pF    |

<sup>(1)</sup> This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

Table 4-48. EP1AGX20 Row Pin Delay Adders for Regional Clock

| Parameter                | Fast (                | Corner | -6 Speed | Units  |

|--------------------------|-----------------------|--------|----------|--------|

| Parameter                | Industrial Commercial |        | Grade    | UIIILS |

| RCLK input<br>adder      | 0.117                 | 0.117  | 0.273    | ns     |

| RCLK PLL input adder     | 0.011                 | 0.011  | 0.019    | ns     |

| RCLK output adder        | -0.117                | -0.117 | -0.273   | ns     |

| RCLK PLL<br>output adder | -0.011                | -0.011 | -0.019   | ns     |

Table 4–49 describes I/O timing specifications.

**Table 4–49.** EP1AGX20 Column Pins Input Timing Parameters (Part 1 of 3)

| I/O Standard   | Clask    | Downwater       | Fast       | Corner     | –6 Speed | llmita |

|----------------|----------|-----------------|------------|------------|----------|--------|

| i/O Statiuaru  | Clock    | Parameter       | Industrial | Commercial | Grade    | Units  |

|                | GCLK     | t <sub>su</sub> | 1.251      | 1.251      | 2.915    | ns     |

| 0 0 W I WTT I  |          | t <sub>H</sub>  | -1.146     | -1.146     | -2.638   | ns     |

| 3.3-V LVTTL    | GCLK PLL | t <sub>su</sub> | 2.693      | 2.693      | 6.021    | ns     |

|                |          | t <sub>H</sub>  | -2.588     | -2.588     | -5.744   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.251      | 1.251      | 2.915    | ns     |

| 3.3-V LVCMOS   |          | t <sub>H</sub>  | -1.146     | -1.146     | -2.638   | ns     |

| 3.3-V LVGIVIO3 | GCLK PLL | t <sub>su</sub> | 2.693      | 2.693      | 6.021    | ns     |

|                |          | t <sub>H</sub>  | -2.588     | -2.588     | -5.744   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.261      | 1.261      | 2.897    | ns     |

| 2.5 V          |          | t <sub>H</sub>  | -1.156     | -1.156     | -2.620   | ns     |

| 2.5 V          | GCLK PLL | t <sub>su</sub> | 2.703      | 2.703      | 6.003    | ns     |

|                |          | t <sub>H</sub>  | -2.598     | -2.598     | -5.726   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.327      | 1.327      | 3.107    | ns     |

| 1.8 V          |          | t <sub>H</sub>  | -1.222     | -1.222     | -2.830   | ns     |

| 1.0 V          | GCLK PLL | t <sub>su</sub> | 2.769      | 2.769      | 6.213    | ns     |

|                |          | t <sub>H</sub>  | -2.664     | -2.664     | -5.936   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.330      | 1.330      | 3.200    | ns     |

| 1.5 V          |          | t <sub>H</sub>  | -1.225     | -1.225     | -2.923   | ns     |

| 1.0 V          | GCLK PLL | t <sub>su</sub> | 2.772      | 2.772      | 6.306    | ns     |

|                |          | t <sub>H</sub>  | -2.667     | -2.667     | -6.029   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.075      | 1.075      | 2.372    | ns     |

| SSTL-2 CLASS I |          | t <sub>H</sub>  | -0.970     | -0.970     | -2.095   | ns     |

| SSTL-2 CLASST  | GCLK PLL | t <sub>su</sub> | 2.517      | 2.517      | 5.480    | ns     |

|                |          | t <sub>H</sub>  | -2.412     | -2.412     | -5.203   | ns     |

Table 4-49.

EP1AGX20 Column Pins Input Timing Parameters (Part 2 of 3)

| I/O Standard         | Oleak    | Donomoton       | Fast       | Corner     | –6 Speed | lla lla |

|----------------------|----------|-----------------|------------|------------|----------|---------|

| i/O Stanuaru         | Clock    | Parameter -     | Industrial | Commercial | Grade    | Units   |

|                      | GCLK     | t <sub>su</sub> | 1.075      | 1.075      | 2.372    | ns      |

| CCTL O CLACC II      |          | t <sub>H</sub>  | -0.970     | -0.970     | -2.095   | ns      |

| SSTL-2 CLASS II      | GCLK PLL | t <sub>su</sub> | 2.517      | 2.517      | 5.480    | ns      |

|                      |          | t <sub>H</sub>  | -2.412     | -2.412     | -5.203   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.113      | 1.113      | 2.479    | ns      |

| SSTL-18 CLASS I      |          | t <sub>H</sub>  | -1.008     | -1.008     | -2.202   | ns      |

| 221F-10 (FW221       | GCLK PLL | t <sub>su</sub> | 2.555      | 2.555      | 5.585    | ns      |

|                      |          | t <sub>H</sub>  | -2.450     | -2.450     | -5.308   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.114      | 1.114      | 2.479    | ns      |

| CCTL 10 CL ACC II    |          | t <sub>H</sub>  | -1.009     | -1.009     | -2.202   | ns      |

| SSTL-18 CLASS II     | GCLK PLL | t <sub>su</sub> | 2.556      | 2.556      | 5.587    | ns      |

|                      |          | t <sub>H</sub>  | -2.451     | -2.451     | -5.310   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.113      | 1.113      | 2.479    | ns      |

| 4.0.1/11071.01.400.1 |          | t <sub>H</sub>  | -1.008     | -1.008     | -2.202   | ns      |

| 1.8-V HSTL CLASS I   | GCLK PLL | t <sub>su</sub> | 2.555      | 2.555      | 5.585    | ns      |

|                      |          | t <sub>H</sub>  | -2.450     | -2.450     | -5.308   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.114      | 1.114      | 2.479    | ns      |

| 1.0 V HOTE OLACO II  |          | t <sub>H</sub>  | -1.009     | -1.009     | -2.202   | ns      |

| 1.8-V HSTL CLASS II  | GCLK PLL | t <sub>su</sub> | 2.556      | 2.556      | 5.587    | ns      |

|                      |          | t <sub>H</sub>  | -2.451     | -2.451     | -5.310   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.131      | 1.131      | 2.607    | ns      |

| 1 F V HOTE OLACO I   |          | t <sub>H</sub>  | -1.026     | -1.026     | -2.330   | ns      |

| 1.5-V HSTL CLASS I   | GCLK PLL | t <sub>su</sub> | 2.573      | 2.573      | 5.713    | ns      |

|                      |          | t <sub>H</sub>  | -2.468     | -2.468     | -5.436   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.132      | 1.132      | 2.607    | ns      |

| 1 F V HOTH OLACO H   |          | t <sub>H</sub>  | -1.027     | -1.027     | -2.330   | ns      |

| 1.5-V HSTL CLASS II  | GCLK PLL | t <sub>su</sub> | 2.574      | 2.574      | 5.715    | ns      |

|                      |          | t <sub>H</sub>  | -2.469     | -2.469     | -5.438   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns      |

| 2 2 V DOI            |          | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns      |

| 3.3-V PCI            | GCLK PLL | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns      |

|                      |          | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns      |

|                      | GCLK     | t <sub>su</sub> | 1.256      | 1.256      | 2.903    | ns      |

| 0.0 V DOL V          |          | t <sub>H</sub>  | -1.151     | -1.151     | -2.626   | ns      |

| 3.3-V PCI-X          | GCLK PLL | t <sub>su</sub> | 2.698      | 2.698      | 6.009    | ns      |

|                      |          | t <sub>H</sub>  | -2.593     | -2.593     | -5.732   | ns      |

Table 4–49.

EP1AGX20 Column Pins Input Timing Parameters (Part 3 of 3)

| I/O Standard | Clock    | Doromotor       | Fast       | Corner     | -6 Speed          | Units  |

|--------------|----------|-----------------|------------|------------|-------------------|--------|

|              | Clock    | ock Parameter   | Industrial | Commercial | −6 Speed<br>Grade | UIIILS |

|              | GCLK     | t <sub>su</sub> | 1.106      | 1.106      | 2.489             | ns     |

| LVDS         |          | t <sub>H</sub>  | -1.001     | -1.001     | -2.212            | ns     |

| LVDS         | GCLK PLL | t <sub>su</sub> | 2.530      | 2.530      | 5.564             | ns     |

|              |          | t <sub>H</sub>  | -2.425     | -2.425     | -5.287            | ns     |

Table 4–50 describes I/O timing specifications.

**Table 4–50.** EP1AGX20 Row Pins output Timing Parameters (Part 1 of 2)

| I/O Standard | Drive    | Clock    | Parameter       | Fast       | Model      | -6 Speed | Units  |

|--------------|----------|----------|-----------------|------------|------------|----------|--------|

| i/O Otanuaru | Strength | GIUCK    | Parameter       | Industrial | Commercial | Grade    | UIIILS |

| 3.3-V LVTTL  | 4 mA     | GCLK     | t <sub>co</sub> | 2.904      | 2.904      | 6.699    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.485      | 1.485      | 3.627    | ns     |

| 3.3-V LVTTL  | 8 mA     | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns     |

| 3.3-V LVTTL  | 12 mA    | GCLK     | t <sub>co</sub> | 2.720      | 2.720      | 6.022    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.301      | 1.301      | 2.950    | ns     |

| 3.3-V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.776      | 2.776      | 6.059    | ns     |

| LVCMOS       |          | GCLK PLL | t <sub>co</sub> | 1.357      | 1.357      | 2.987    | ns     |

| 3.3-V        | 8 mA     | GCLK     | t <sub>co</sub> | 2.670      | 2.670      | 5.753    | ns     |

| LVCMOS       |          | GCLK PLL | t <sub>co</sub> | 1.251      | 1.251      | 2.681    | ns     |

| 2.5 V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.759      | 2.759      | 6.033    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.340      | 1.340      | 2.961    | ns     |

| 2.5 V        | 8 mA     | GCLK     | t <sub>co</sub> | 2.656      | 2.656      | 5.775    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.237      | 1.237      | 2.703    | ns     |

| 2.5 V        | 12 mA    | GCLK     | t <sub>co</sub> | 2.637      | 2.637      | 5.661    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.218      | 1.218      | 2.589    | ns     |

| 1.8 V        | 2 mA     | GCLK     | t <sub>co</sub> | 2.829      | 2.829      | 7.052    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.410      | 1.410      | 3.980    | ns     |

| 1.8 V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.818      | 2.818      | 6.273    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.399      | 1.399      | 3.201    | ns     |

| 1.8 V        | 6 mA     | GCLK     | t <sub>co</sub> | 2.707      | 2.707      | 5.972    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.288      | 1.288      | 2.900    | ns     |

| 1.8 V        | 8 mA     | GCLK     | t <sub>co</sub> | 2.676      | 2.676      | 5.858    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.257      | 1.257      | 2.786    | ns     |

| 1.5 V        | 2 mA     | GCLK     | t <sub>co</sub> | 2.789      | 2.789      | 6.551    | ns     |

|              |          | GCLK PLL | t <sub>co</sub> | 1.370      | 1.370      | 3.479    | ns     |

| 1.5 V        | 4 mA     | GCLK     | t <sub>co</sub> | 2.682      | 2.682      | 5.950    | ns     |

| 1.0 V        |          |          |                 |            |            |          |        |

Table 4–59 lists column pin delay adders when using the regional clock in Arria GX devices.

Table 4-59. EP1AGX35 Column Pin Delay Adders for Regional Clock

| Parameter             | Fast (     | Corner     | C Canad Crada  | llmito |  |

|-----------------------|------------|------------|----------------|--------|--|

| rarameter             | Industrial | Commercial | -6 Speed Grade | Units  |  |

| RCLK input adder      | 0.099      | 0.099      | 0.254          | ns     |  |

| RCLK PLL input adder  | -0.012     | -0.012     | -0.01          | ns     |  |

| RCLK output adder     | -0.086     | -0.086     | -0.244         | ns     |  |

| RCLK PLL output adder | 1.253      | 1.253      | 3.133          | ns     |  |

# **EP1AGX50 I/O Timing Parameters**

Table 4–60 through Table 4–63 list the maximum I/O timing parameters for EP1AGX50 devices for I/O standards which support general purpose I/O pins.

Table 4–60 lists I/O timing specifications.

**Table 4–60.** EP1AGX50 Row Pins Input Timing Parameters (Part 1 of 2)

| I/O Standard   | Olask    | Dawamataw       | Fast       | Model      | -6 Speed | 11-:4- |

|----------------|----------|-----------------|------------|------------|----------|--------|

| i/o Stanuaru   | Clock    | Parameter       | Industrial | Commercial | Grade    | Units  |

|                | GCLK     | t <sub>su</sub> | 1.550      | 1.550      | 3.542    | ns     |

| 3.3-V LVTTL    |          | t <sub>H</sub>  | -1.445     | -1.445     | -3.265   | ns     |

| 3.3-V LVIIL    | GCLK PLL | t <sub>su</sub> | 2.978      | 2.978      | 6.626    | ns     |

|                |          | t <sub>H</sub>  | -2.873     | -2.873     | -6.349   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.550      | 1.550      | 3.542    | ns     |

| 3.3-V LVCMOS   |          | t <sub>H</sub>  | -1.445     | -1.445     | -3.265   | ns     |

| 3.3-V LVGIVIUS | GCLK PLL | t <sub>su</sub> | 2.978      | 2.978      | 6.626    | ns     |

|                |          | t <sub>H</sub>  | -2.873     | -2.873     | -6.349   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.562      | 1.562      | 3.523    | ns     |

| 2.5 V          |          | t <sub>H</sub>  | -1.457     | -1.457     | -3.246   | ns     |

| 2.5 V          | GCLK PLL | t <sub>su</sub> | 2.990      | 2.990      | 6.607    | ns     |

|                |          | t <sub>H</sub>  | -2.885     | -2.885     | -6.330   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.628      | 1.628      | 3.730    | ns     |

| 1.0.1/         |          | t <sub>H</sub>  | -1.523     | -1.523     | -3.453   | ns     |

| 1.8 V          | GCLK PLL | t <sub>su</sub> | 3.056      | 3.056      | 6.814    | ns     |

|                |          | t <sub>H</sub>  | -2.951     | -2.951     | -6.537   | ns     |

|                | GCLK     | t <sub>su</sub> | 1.631      | 1.631      | 3.825    | ns     |

| 1 E V          |          | t <sub>H</sub>  | -1.526     | -1.526     | -3.548   | ns     |

| 1.5 V          | GCLK PLL | t <sub>su</sub> | 3.059      | 3.059      | 6.909    | ns     |

|                |          | t <sub>H</sub>  | -2.954     | -2.954     | -6.632   | ns     |

Table 4-73.

EP1AGX90 Column Pins Input Timing Parameters (Part 3 of 3)

| I/O Standard        | Clock    | Parameter       | Fast (     | Corner     | –6 Speed | Units  |

|---------------------|----------|-----------------|------------|------------|----------|--------|

| i/O Stanuaru        | Older    | raiailletei     | Industrial | Commercial | Grade    | UIIILS |

|                     | GCLK     | t <sub>su</sub> | 0.901      | 0.901      | 1.986    | ns     |

| 1.5-V HSTL CLASS II |          | t <sub>H</sub>  | -0.796     | -0.796     | -1.709   | ns     |

| 1.5-V HOTE GLASS II | GCLK PLL | t <sub>su</sub> | 2.965      | 2.965      | 6.121    | ns     |

|                     |          | t <sub>H</sub>  | -2.860     | -2.860     | -5.844   | ns     |

|                     | GCLK     | t <sub>su</sub> | 1.023      | 1.023      | 2.278    | ns     |

| 3.3-V PCI           |          | t <sub>H</sub>  | -0.918     | -0.918     | -2.001   | ns     |

| 3.3-4 FOI           | GCLK PLL | t <sub>su</sub> | 3.087      | 3.087      | 6.413    | ns     |

|                     |          | t <sub>H</sub>  | -2.982     | -2.982     | -6.136   | ns     |

|                     | GCLK     | t <sub>su</sub> | 1.023      | 1.023      | 2.278    | ns     |

| 3.3-V PCI-X         |          | t <sub>H</sub>  | -0.918     | -0.918     | -2.001   | ns     |

| 3.3-V FUI-A         | GCLK PLL | t <sub>su</sub> | 3.087      | 3.087      | 6.413    | ns     |

|                     |          | t <sub>H</sub>  | -2.982     | -2.982     | -6.136   | ns     |

|                     | GCLK     | t <sub>su</sub> | 0.891      | 0.891      | 1.920    | ns     |

| LVDS                |          | t <sub>H</sub>  | -0.786     | -0.786     | -1.643   | ns     |

| LVDS                | GCLK PLL | t <sub>su</sub> | 2.963      | 2.963      | 6.066    | ns     |

|                     |          | t <sub>H</sub>  | -2.858     | -2.858     | -5.789   | ns     |

Table 4–74 lists I/O timing specifications.

Table 4-74. EP1AGX90 Row Pins Output Timing Parameters (Part 1 of 3)

| I/O Standard    | Drive<br>Strength | Clock    | Parameter       | Fast Model |            | -6 Speed | 11    |

|-----------------|-------------------|----------|-----------------|------------|------------|----------|-------|

|                 |                   |          |                 | Industrial | Commercial | Grade    | Units |

| 3.3-V LVTTL     | 4 mA              | GCLK     | t <sub>co</sub> | 3.170      | 3.170      | 7.382    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 1.099      | 1.099      | 3.238    | ns    |

| 3.3-V LVTTL     | 8 mA              | GCLK     | t <sub>co</sub> | 3.042      | 3.042      | 6.742    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.971      | 0.971      | 2.598    | ns    |

| 3.3-V LVTTL     | 12 mA             | GCLK     | t <sub>co</sub> | 2.986      | 2.986      | 6.705    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.915      | 0.915      | 2.561    | ns    |

| 3.3-V<br>LVCMOS | 4 mA              | GCLK     | t <sub>co</sub> | 3.042      | 3.042      | 6.742    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.971      | 0.971      | 2.598    | ns    |

| 3.3-V<br>LVCMOS | 8 mA              | GCLK     | t <sub>co</sub> | 2.936      | 2.936      | 6.436    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.865      | 0.865      | 2.292    | ns    |

| 2.5 V           | 4 mA              | GCLK     | t <sub>co</sub> | 3.025      | 3.025      | 6.716    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.954      | 0.954      | 2.572    | ns    |

| 2.5 V           | 8 mA              | GCLK     | t <sub>co</sub> | 2.922      | 2.922      | 6.458    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.851      | 0.851      | 2.314    | ns    |

| 2.5 V           | 12 mA             | GCLK     | t <sub>co</sub> | 2.903      | 2.903      | 6.344    | ns    |

|                 |                   | GCLK PLL | t <sub>co</sub> | 0.832      | 0.832      | 2.200    | ns    |

Table 4–99 lists performance notes.

Table 4-99. Arria GX Performance Notes

|                                   |                                      |       | Performance                |            |                                 |  |

|-----------------------------------|--------------------------------------|-------|----------------------------|------------|---------------------------------|--|

| Applic                            | eations                              | ALUTS | TriMatrix<br>Memory Blocks | DSP Blocks | <b>-6 Speed Grade</b><br>168.41 |  |

|                                   | 16-to-1<br>multiplexer               | 5     | 0                          | 0          |                                 |  |

| LE                                | 32-to-1<br>multiplexer               | 11    | 0                          | 0          | 334.11                          |  |

|                                   | 16-bit counter                       | 16    | 0                          | 0          | 374.0                           |  |

|                                   | 64-bit counter                       | 64    | 0                          | 0          | 168.41                          |  |

| TriMatrix Memory<br>M512 block    | Simple dual-port<br>RAM 32 x 18 bit  | 0     | 1                          | 0          | 348.0                           |  |

|                                   | FIFO 32 x 18 bit                     | 0     | 1                          | 0          | 333.22                          |  |

| TriMatrix Memory<br>M4K block     | Simple dual-port<br>RAM 128 x 36 bit | 0     | 1                          | 0          | 344.71                          |  |

|                                   | True dual-port<br>RAM 128 x 18 bit   | 0     | 1                          | 0          | 348.0                           |  |

|                                   | Single port RAM<br>4K x 144 bit      | 0     | 2                          | 0          | 244.0                           |  |

|                                   | Simple dual-port<br>RAM 4K x 144 bit | 0     | 1                          | 0          | 292.0                           |  |

|                                   | True dual-port<br>RAM 4K x 144 bit   | 0     | 2                          | 0          | 244.0                           |  |

|                                   | Single port RAM<br>8K x 72 bit       | 0     | 1                          | 0          | 247.0                           |  |

| TriMatrix Memory<br>MegaRAM block | Simple dual-port<br>RAM 8K x 72 bit  | 0     | 1                          | 0          | 292.0                           |  |

|                                   | Single port RAM<br>16K x 36 bit      | 0     | 1                          | 0          | 254.0                           |  |

|                                   | Simple dual-port<br>RAM 16K x 36 bit | 0     | 1                          | 0          | 292.0                           |  |

|                                   | True dual-port<br>RAM 16K x 36 bit   | 0     | 1                          | 0          | 251.0                           |  |

|                                   | Single port RAM<br>32K x 18 bit      | 0     | 1                          | 0          | 317.36                          |  |

|                                   | Simple dual-port<br>RAM 32K x 18 bit | 0     | 1                          | 0          | 292.0                           |  |

|                                   | True dual-port<br>RAM 32K x 18 bit   | 0     | 1                          | 0          | 251.0                           |  |

|                                   | Single port RAM<br>64K x 9 bit       | 0     | 1                          | 0          | 254.0                           |  |

|                                   | Simple dual-port<br>RAM 64K x 9 bit  | 0     | 1                          | 0          | 292.0                           |  |

|                                   | True dual-port<br>RAM 64K x 9 bit    | 0     | 1                          | 0          | 251.0                           |  |