Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 196                                                         |

| Number of Logic Elements/Cells | 466                                                         |

| Total RAM Bits                 | 6272                                                        |

| Number of I/O                  | 112                                                         |

| Number of Gates                | 10000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                   |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 144-LQFP                                                    |

| Supplier Device Package        | 144-TQFP (20x20)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcs10xl-4tq144c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan and Spartan-XL devices provide system clock rates exceeding 80 MHz and internal performance in excess of 150 MHz. In addition to the conventional benefit of high volume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.

The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family's features and benefits. Technology advancements have been derived from the XC4000XLA process developments.

# **Logic Functional Description**

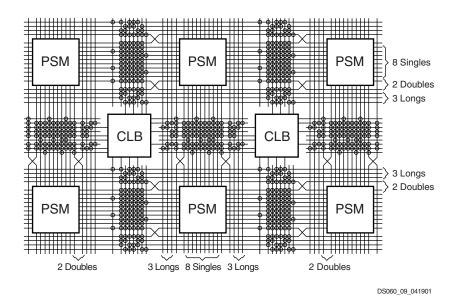

The Spartan series uses a standard FPGA structure as shown in Figure 1, page 2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.

- CLBs provide the functional elements for implementing the user's logic.

- IOBs provide the interface between the package pins and internal signal lines.

- Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.

The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.

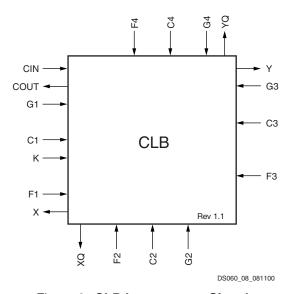

# **Configurable Logic Blocks (CLBs)**

The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simplified block diagram in Figure 2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the **Advanced Features Description**, page 13.

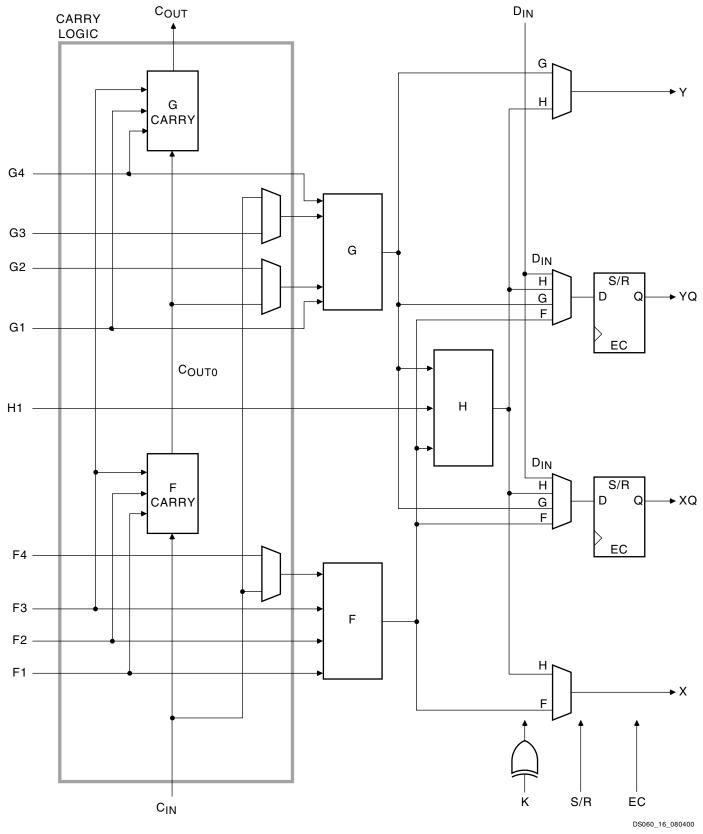

### **Function Generators**

Two 16 x 1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offering unrestricted logic implementation of any Boolean function of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.

A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure 2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement certain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbitrarily defined Boolean function of five inputs.

Table 4: Supported Sources for Spartan/XL Inputs

|                                                             | · · · · · · · · · · · · · · · · · · · |                 |                      |  |  |

|-------------------------------------------------------------|---------------------------------------|-----------------|----------------------|--|--|

|                                                             | -                                     | artan<br>outs   | Spartan-XL<br>Inputs |  |  |

| Source                                                      | 5V,<br>TTL                            | 5V,<br>CMOS     | 3.3V<br>CMOS         |  |  |

| Any device, V <sub>CC</sub> = 3.3V,<br>CMOS outputs         | V                                     | Unreli-<br>able | V                    |  |  |

| Spartan family, V <sub>CC</sub> = 5V,<br>TTL outputs        | <b>V</b>                              | Data            | V                    |  |  |

| Any device, $V_{CC} = 5V$ , TTL outputs $(V_{OH} \le 3.7V)$ | <b>V</b>                              |                 | V                    |  |  |

| Any device, V <sub>CC</sub> = 5V,<br>CMOS outputs           | √                                     | V               | √ (default<br>mode)  |  |  |

### Spartan-XL Family V<sub>CC</sub> Clamping

Spartan-XL FPGAs have an optional clamping diode connected from each I/O to  $V_{CC}$ . When enabled they clampringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications.  $V_{CC}$  clamping is a global option affecting all I/O pins.

Spartan-XL devices are fully 5V TTL I/O compatible if  $V_{CC}$  clamping is not enabled. With  $V_{CC}$  clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above  $V_{CC}$ . If enabled, TTL I/O compatibility is maintained but full 5V I/O tolerance is sacrificed. The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.

Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.

Table 5: I/O Standards Supported by Spartan-XL FPGAs

| Signaling<br>Standard | VCC<br>Clamping | Output<br>Drive | V <sub>IH MAX</sub> | V <sub>IH MIN</sub>    | V <sub>IL MAX</sub>    | V <sub>OH MIN</sub>    | V <sub>OL MAX</sub>    |

|-----------------------|-----------------|-----------------|---------------------|------------------------|------------------------|------------------------|------------------------|

| TTL                   | Not allowed     | 12/24 mA        | 5.5                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| LVTTL                 | OK              | 12/24 mA        | 3.6                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| PCI5V                 | Not allowed     | 24 mA           | 5.5                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| PCI3V                 | Required        | 12 mA           | 3.6                 | 50% of V <sub>CC</sub> | 30% of V <sub>CC</sub> | 90% of V <sub>CC</sub> | 10% of V <sub>CC</sub> |

| LVCMOS 3V             | OK              | 12/24 mA        | 3.6                 | 50% of V <sub>CC</sub> | 30% of V <sub>CC</sub> | 90% of V <sub>CC</sub> | 10% of V <sub>CC</sub> |

# Additional Fast Capture Input Latch (Spartan-XL Family Only)

The Spartan-XL family OB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements. This additional latch allows the fast capture of input data, which is then synchronized to the internal clock by the IOB flip-flop or latch.

To place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a transparent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element, and the inverter is absorbed into the IOB.

### IOB Output Signal Path

Output signals can be optionally inverted within the IOB, and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in Table 6.

Table 6: Output Flip-Flop Functionality

| Mode               | Clock | Clock<br>Enable | Т  | D | Q  |

|--------------------|-------|-----------------|----|---|----|

| Power-Up<br>or GSR | Х     | Х               | 0* | Х | SR |

| Flip-Flop          | Х     | 0               | 0* | Х | Q  |

|                    |       | 1*              | 0* | D | D  |

|                    | Х     | Х               | 1  | Х | Z  |

|                    | 0     | Х               | 0* | Х | Q  |

### Legend:

| V | Don't care |

|---|------------|

|   |            |

\_\_\_ Rising edge (clock not inverted).

SR Set or Reset value. Reset is default.

0\* Input is Low or unconnected (default value)

1\* Input is High or unconnected (default value)

Z 3-state

Figure 8: Spartan/XL CLB Routing Channels and Interface Block Diagram

### **CLB Interface**

A block diagram of the CLB interface signals is shown in Figure 9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algorithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated interconnects which do not interfere with the general routing structure. The output signals from the CLB are available to drive both vertical and horizontal channels.

Figure 9: CLB Interconnect Signals

### **Programmable Switch Matrices**

The horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transistors used to establish connections between the lines (see Figure 10).

For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a double-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.

### **Single-Length Lines**

Single-length lines provide the greatest interconnect flexibility and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the programmable switch matrices, as shown in Figure 10. Routing connectivity is shown in Figure 8.

Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct signals within a localized area and to provide the branching for nets with fanout greater than one.

Figure 16: Fast Carry Logic in Spartan/XL CLB

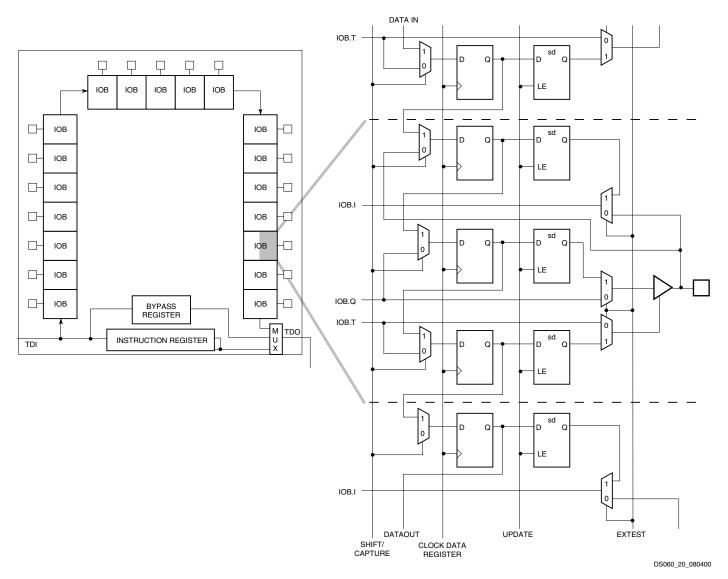

Figure 20: Spartan/XL Boundary Scan Logic

Table 12: Boundary Scan Instructions

| Ins | structi | on | Test                           | TDO                | I/O Data   |

|-----|---------|----|--------------------------------|--------------------|------------|

| 12  | l1      | 10 | Selected                       | Source             | Source     |

| 0   | 0       | 0  | EXTEST                         | DR                 | DR         |

| 0   | 0       | 1  | SAMPLE/<br>PRELOAD             | DR                 | Pin/Logic  |

| 0   | 1       | 0  | USER 1                         | BSCAN.<br>TDO1     | User Logic |

| 0   | 1       | 1  | USER 2                         | BSCAN.<br>TDO2     | User Logic |

| 1   | 0       | 0  | READBACK                       | Readback<br>Data   | Pin/Logic  |

| 1   | 0       | 1  | CONFIGURE                      | DOUT               | Disabled   |

| 1   | 1       | 0  | IDCODE<br>(Spartan-XL<br>only) | IDCODE<br>Register | -          |

| 1   | 1       | 1  | BYPASS                         | Bypass<br>Register | -          |

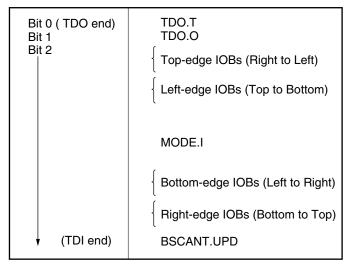

### Bit Sequence

The bit sequence within each IOB is: In, Out, 3-state. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

The first two bits in the I/O data register are TDO.T and TDO.O, which can be used for the capture of internal signals. The final bit is BSCANT.UPD, which can be used to drive an internal net. These locations are primarily used by Xilinx for internal testing.

From a cavity-up view of the chip (as shown in the FPGA Editor), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 21. The device-specific pinout tables for the Spartan/XL devices include the boundary scan locations for each IOB pin.

DS060 21 080400

Figure 21: Boundary Scan Bit Sequence

BSDL (Boundary Scan Description Language) files for Spartan/XL devices are available on the Xilinx website in the File Download area. Note that the 5V Spartan devices and 3V Spartan-XL devices have different BSDL files.

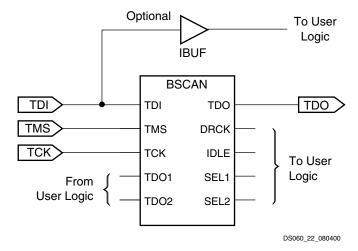

### Including Boundary Scan in a Design

If boundary scan is only to be used during configuration, no special elements need be included in the schematic or HDL code. In this case, the special boundary scan pins TDI, TMS, TCK and TDO can be used for user functions after configuration.

To indicate that boundary scan remain enabled after configuration, place the BSCAN library symbol and connect the TDI, TMS, TCK and TDO pad symbols to the appropriate pins, as shown in Figure 22.

Figure 22: Boundary Scan Example

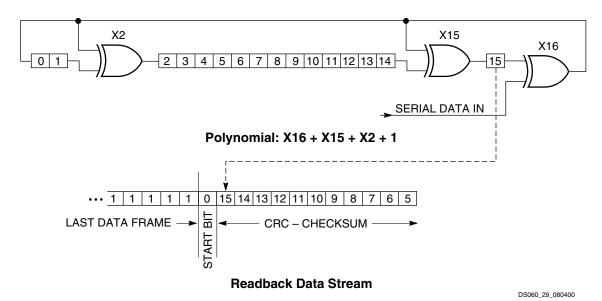

Figure 29: Circuit for Generating CRC-16

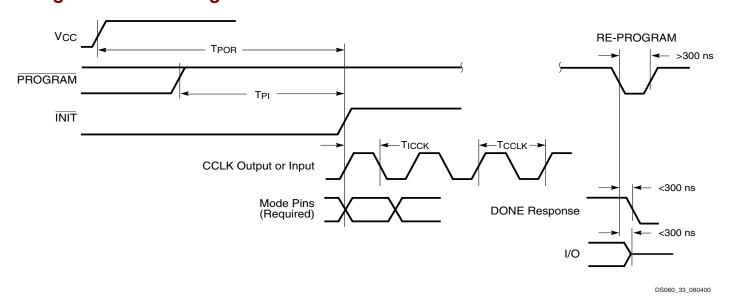

# **Configuration Sequence**

There are four major steps in the Spartan/XL FPGA power-up configuration sequence.

- · Configuration Memory Clear

- Initialization

- Configuration

- Start-up

The full process is illustrated in Figure 30.

## Configuration Memory Clear

When power is first applied or is reapplied to an FPGA, an internal circuit forces initialization of the configuration logic. When  $V_{CC}$  reaches an operational level, and the circuit passes the write and read test of a sample pair of configuration bits, a time delay is started. This time delay is nominally 16 ms. The delay is four times as long when in Master Serial Mode to allow ample time for all slaves to reach a stable  $V_{CC}$ . When all  $\overline{\text{INIT}}$  pins are tied together, as recommended, the longest delay takes precedence. Therefore, devices with different time delays can easily be mixed and matched in a daisy chain.

This delay is applied only on power-up. It is not applied when reconfiguring an FPGA by pulsing the PROGRAM pin

Low. During this time delay, or as long as the PROGRAM input is asserted, the configuration logic is held in a Configuration Memory Clear state. The configuration-memory frames are consecutively initialized, using the internal oscillator.

At the end of each complete pass through the frame addressing, the power-on time-out delay circuitry and the level of the  $\overline{PROGRAM}$  pin are tested. If neither is asserted, the logic initiates one additional clearing of the configuration frames and then tests the  $\overline{INIT}$  input.

### Initialization

During initialization and configuration, user pins HDC,  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE provide status outputs for the system interface. The outputs  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE are held Low and HDC is held High starting at the initial application of power.

The open drain  $\overline{\text{INIT}}$  pin is released after the final initialization pass through the frame addresses. There is a deliberate delay before a Master-mode device recognizes an inactive  $\overline{\text{INIT}}$ . Two internal clocks after the  $\overline{\text{INIT}}$  pin is recognized as High, the device samples the MODE pin to determine the configuration mode. The appropriate interface lines become active and the configuration preamble and data can be loaded.

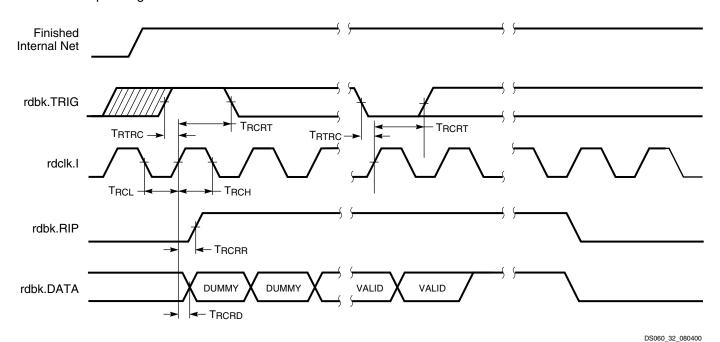

# **Readback Switching Characteristics Guidelines**

The following guidelines reflect worst-case values over the recommended operating conditions.

Figure 33: Spartan and Spartan-XL Readback Timing Diagram

# Spartan and Spartan-XL Readback Switching Characteristics

| Symbol            |           | Description                                    | Min | Max | Units |

|-------------------|-----------|------------------------------------------------|-----|-----|-------|

| T <sub>RTRC</sub> | rdbk.TRIG | rdbk.TRIG setup to initiate and abort Readback | 200 | -   | ns    |

| T <sub>RCRT</sub> |           | rdbk.TRIG hold to initiate and abort Readback  | 50  | -   | ns    |

| T <sub>RCRD</sub> | rdclk.l   | rdbk.DATA delay                                | -   | 250 | ns    |

| T <sub>RCRR</sub> |           | rdbk.RIP delay                                 | -   | 250 | ns    |

| T <sub>RCH</sub>  |           | High time                                      | 250 | 500 | ns    |

| T <sub>RCL</sub>  |           | Low time                                       | 250 | 500 | ns    |

- 1. Timing parameters apply to all speed grades.

- 2. If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

# **Configuration Switching Characteristics**

### **Master Mode**

| Symbol            | Description                | Min | Max  | Units             |

|-------------------|----------------------------|-----|------|-------------------|

| T <sub>POR</sub>  | Power-on reset             | 40  | 130  | ms                |

| T <sub>PI</sub>   | Program Latency            | 30  | 200  | μs per CLB column |

| T <sub>ICCK</sub> | CCLK (output) delay        | 40  | 250  | μs                |

| T <sub>CCLK</sub> | CCLK (output) period, slow | 640 | 2000 | ns                |

| T <sub>CCLK</sub> | CCLK (output) period, fast | 100 | 250  | ns                |

# **Slave Mode**

| Symbol            | Description                    | Min | Max | Units             |

|-------------------|--------------------------------|-----|-----|-------------------|

| T <sub>POR</sub>  | Power-on reset                 | 10  | 33  | ms                |

| T <sub>Pl</sub>   | Program latency                | 30  | 200 | μs per CLB column |

| T <sub>ICCK</sub> | CCLK (input) delay (required)  | 4   | -   | μs                |

| T <sub>CCLK</sub> | CCLK (input) period (required) | 80  | -   | ns                |

# Spartan-XL Family Detailed Specifications

### **Definition of Terms**

In the following tables, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

**Advance:** Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or device families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Specifications not identified as either Advance or Preliminary are to be considered Final.

Notwithstanding the definition of the above terms, all specifications are subject to change without notice.

Except for pin-to-pin input and output parameters, the AC parameter delay specifications included in this document are derived from measuring internal test patterns. All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications.

# Spartan-XL Family Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Descri                            | Value                                     | Units                    |    |

|------------------|-----------------------------------|-------------------------------------------|--------------------------|----|

| V <sub>CC</sub>  | Supply voltage relative to GND    |                                           | -0.5 to 4.0              | V  |

| V <sub>IN</sub>  | Input voltage relative to GND     | 5V Tolerant I/O Checked <sup>(2, 3)</sup> | -0.5 to 5.5              | V  |

|                  |                                   | Not 5V Tolerant I/Os <sup>(4, 5)</sup>    | $-0.5$ to $V_{CC} + 0.5$ | V  |

| V <sub>TS</sub>  | Voltage applied to 3-state output | 5V Tolerant I/O Checked <sup>(2, 3)</sup> | -0.5 to 5.5              | V  |

|                  |                                   | Not 5V Tolerant I/Os <sup>(4, 5)</sup>    | $-0.5$ to $V_{CC} + 0.5$ | V  |

| T <sub>STG</sub> | Storage temperature (ambient)     |                                           | -65 to +150              | °C |

| T <sub>J</sub>   | Junction temperature              | Plastic packages                          | +125                     | °C |

#### Notes:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

- 2. With 5V Tolerant I/Os selected, the Maximum DC overshoot must be limited to either +5.5V or 10 mA and undershoot (below GND) must be limited to either 0.5V or 10 mA, whichever is easier to achieve.

- 3. With 5V Tolerant I/Os selected, the Maximum AC (during transitions) conditions are as follows; the device pins may undershoot to -2.0V or overshoot to + 7.0V, provided this overshoot or undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

- 4. Without 5V Tolerant I/Os selected, the Maximum DC overshoot or undershoot must be limited to either 0.5V or 10 mA, whichever is easier to achieve.

- 5. Without 5V Tolerant I/Os selected, the Maximum AC conditions are as follows; the device pins may undershoot to –2.0V or overshoot to V<sub>CC</sub> + 2.0V, provided this overshoot or undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

- 6. For soldering guidelines, see the Package Information on the Xilinx website.

# **Spartan-XL Family Recommended Operating Conditions**

| Symbol          | Description                                                                   |            | Min                    | Max                    | Units |

|-----------------|-------------------------------------------------------------------------------|------------|------------------------|------------------------|-------|

| $V_{CC}$        | Supply voltage relative to GND, T <sub>J</sub> = 0°C to +85°C                 | Commercial | 3.0                    | 3.6                    | V     |

|                 | Supply voltage relative to GND, $T_J = -40^{\circ}C$ to $+100^{\circ}C^{(1)}$ | Industrial | 3.0                    | 3.6                    | V     |

| V <sub>IH</sub> | High-level input voltage <sup>(2)</sup>                                       |            | 50% of V <sub>CC</sub> | 5.5                    | V     |

| V <sub>IL</sub> | Low-level input voltage <sup>(2)</sup>                                        |            | 0                      | 30% of V <sub>CC</sub> | V     |

| T <sub>IN</sub> | Input signal transition time                                                  |            | -                      | 250                    | ns    |

- At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per °C.

- Input and output measurement threshold is ~50% of V<sub>CC</sub>.

# **Spartan-XL Family DC Characteristics Over Operating Conditions**

| Symbol            | Description                                                                | Min                                                        | Тур. | Max | Units               |    |

|-------------------|----------------------------------------------------------------------------|------------------------------------------------------------|------|-----|---------------------|----|

| V <sub>OH</sub>   | High-level output voltage @ $I_{OH} = -4.0 \text{ mA}, V_{C}$              | <sub>C</sub> min (LVTTL)                                   | 2.4  | -   | -                   | V  |

|                   | High-level output voltage @ $I_{OH} = -500 \mu A$ , (LV                    | gh-level output voltage @ $I_{OH} = -500 \mu A$ , (LVCMOS) |      | -   | -                   | V  |

| V <sub>OL</sub>   | Low-level output voltage @ I <sub>OL</sub> = 12.0 mA, V <sub>CO</sub>      | ; min (LVTTL) <sup>(1)</sup>                               | -    | -   | 0.4                 | V  |

|                   | Low-level output voltage @ I <sub>OL</sub> = 24.0 mA, V <sub>CO</sub>      | ; min (LVTTL) <sup>(2)</sup>                               | -    | -   | 0.4                 | V  |

|                   | Low-level output voltage @ I <sub>OL</sub> = 1500 μA, (LV                  | CMOS)                                                      | -    | -   | 10% V <sub>CC</sub> | V  |

| V <sub>DR</sub>   | Data retention supply voltage (below which configuration data may be lost) |                                                            | 2.5  | -   | -                   | V  |

| I <sub>CCO</sub>  | Quiescent FPGA supply current <sup>(3,4)</sup>                             | Commercial                                                 | -    | 0.1 | 2.5                 | mA |

|                   |                                                                            | Industrial                                                 | -    | 0.1 | 5                   | mA |

| I <sub>CCPD</sub> | Power Down FPGA supply current <sup>(3,5)</sup>                            | Commercial                                                 | -    | 0.1 | 2.5                 | mA |

|                   |                                                                            | Industrial                                                 | -    | 0.1 | 5                   | mA |

| IL                | Input or output leakage current                                            | 1                                                          | -10  | -   | 10                  | μΑ |

| C <sub>IN</sub>   | Input capacitance (sample tested)                                          |                                                            | -    | -   | 10                  | pF |

| I <sub>RPU</sub>  | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V (sample tested)         |                                                            | 0.02 | -   | 0.25                | mA |

| I <sub>RPD</sub>  | Pad pull-down (when selected) @ V <sub>IN</sub> = 3.3V (s                  | sample tested)                                             | 0.02 | -   | -                   | mA |

#### Notes:

- With up to 64 pins simultaneously sinking 12 mA (default mode).

- 2. With up to 64 pins simultaneously sinking 24 mA (with 24 mA option selected).

- 3. With 5V tolerance not selected, no internal oscillators, and the FPGA configured with the Tie option.

- With no output current loads, no active input resistors, and all package pins at V<sub>CC</sub> or GND.

- 5. With PWRDWN active.

# **Supply Current Requirements During Power-On**

Spartan-XL FPGAs require that a minimum supply current  $I_{CCPO}$  be provided to the  $V_{CC}$  lines for a successful power on. If more current is available, the FPGA can consume more than  $I_{CCPO}$  min., though this cannot adversely affect reliability.

A maximum limit for  $I_{CCPO}$  is not specified. Be careful when using foldback/crowbar supplies and fuses. It is possible to control the magnitude of  $I_{CCPO}$  by limiting the supply current available to the FPGA. A current limit below the trip level will avoid inadvertently activating over-current protection circuits.

| Symbol            | Description                                                   | Min | Max | Units |

|-------------------|---------------------------------------------------------------|-----|-----|-------|

| I <sub>CCPO</sub> | Total V <sub>CC</sub> supply current required during power-on | 100 | -   | mA    |

| T <sub>CCPO</sub> | V <sub>CC</sub> ramp time <sup>(2,3)</sup>                    | -   | 50  | ms    |

- 1. The  $I_{CCPO}$  requirement applies for a brief time (commonly only a few milliseconds) when  $V_{CC}$  ramps from 0 to 3.3V.

- 2. The ramp time is measured from GND to V<sub>CC</sub> max on a fully loaded board.

- V<sub>CC</sub> must not dip in the negative direction during power on.

# **Spartan-XL Family Pin-to-Pin Output Parameter Guidelines**

All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case oper-

ating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading.

## Spartan-XL Family Output Flip-Flop, Clock-to-Out

|                    |                            |             | Speed |     |          |

|--------------------|----------------------------|-------------|-------|-----|----------|

|                    |                            |             | -5    | -4  |          |

| Symbol             | Description                | Device      | Max   | Max | Units    |

| Global Cl          | ock to Output using OFF    | '           |       | '   | <u> </u> |

| T <sub>ICKOF</sub> | Fast                       | XCS05XL     | 4.6   | 5.2 | ns       |

|                    |                            | XCS10XL     | 4.9   | 5.5 | ns       |

|                    |                            | XCS20XL     | 5.2   | 5.8 | ns       |

|                    |                            | XCS30XL     | 5.5   | 6.2 | ns       |

|                    |                            | XCS40XL     | 5.8   | 6.5 | ns       |

| Slew Rate          | Adjustment                 | 1           |       | 1   |          |

| $T_{SLOW}$         | For Output SLOW option add | All Devices | 1.5   | 1.7 | ns       |

- Output delays are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- 2. Output timing is measured at ~50% V<sub>CC</sub> threshold with 50 pF external capacitive load.

- 3. OFF = Output Flip Flop

### Spartan-XL Family Pin-to-Pin Input Parameter Guidelines

All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case oper-

ating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading.

### Spartan-XL Family Setup and Hold

|                                                   |             |         | Speed   | Grade   |       |  |  |  |  |

|---------------------------------------------------|-------------|---------|---------|---------|-------|--|--|--|--|

|                                                   |             |         | -5      | -4      |       |  |  |  |  |

| Symbol                                            | Description | Device  | Max     | Max     | Units |  |  |  |  |

| Input Setup/Hold Times Using Global Clock and IFF |             |         |         |         |       |  |  |  |  |

| T <sub>SUF</sub> /T <sub>HF</sub>                 | No Delay    | XCS05XL | 1.1/2.0 | 1.6/2.6 | ns    |  |  |  |  |

|                                                   |             | XCS10XL | 1.0/2.2 | 1.5/2.8 | ns    |  |  |  |  |

|                                                   |             | XCS20XL | 0.9/2.4 | 1.4/3.0 | ns    |  |  |  |  |

|                                                   |             | XCS30XL | 0.8/2.6 | 1.3/3.2 | ns    |  |  |  |  |

|                                                   |             | XCS40XL | 0.7/2.8 | 1.2/3.4 | ns    |  |  |  |  |

| T <sub>SU</sub> /T <sub>H</sub>                   | Full Delay  | XCS05XL | 3.9/0.0 | 5.1/0.0 | ns    |  |  |  |  |

|                                                   |             | XCS10XL | 4.1/0.0 | 5.3/0.0 | ns    |  |  |  |  |

|                                                   |             | XCS20XL | 4.3/0.0 | 5.5/0.0 | ns    |  |  |  |  |

|                                                   |             | XCS30XL | 4.5/0.0 | 5.7/0.0 | ns    |  |  |  |  |

|                                                   |             | XCS40XL | 4.7/0.0 | 5.9/0.0 | ns    |  |  |  |  |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured with the fastest route and the lightest load. Hold time is measured using the furthest distance and a reference load of one clock pin per IOB/CLB.

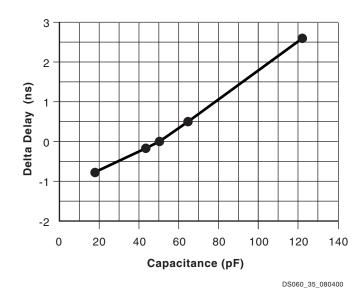

### **Capacitive Load Factor**

Figure 35 shows the relationship between I/O output delay and load capacitance. It allows a user to adjust the specified output delay if the load capacitance is different than 50 pF. For example, if the actual load capacitance is 120 pF, add 2.5 ns to the specified delay. If the load capacitance is 20 pF, subtract 0.8 ns from the specified output delay. Figure 35 is usable over the specified operating conditions of voltage and temperature and is independent of the output slew rate control.

Figure 35: Delay Factor at Various Capacitive Loads

# **Pin Descriptions**

There are three types of pins in the Spartan/XL devices:

- · Permanently dedicated pins

- User I/O pins that can have special functions

- Unrestricted user-programmable I/O pins.

Before and during configuration, all outputs not used for the configuration process are 3-stated with the I/O pull-up resistor network activated. After configuration, if an IOB is unused it is configured as an input with the I/O pull-up resistor network remaining activated.

Any user I/O can be configured to drive the Global Set/Reset net GSR or the global three-state net GTS. See **Global Signals: GSR and GTS**, page 20 for more information.

Device pins for Spartan/XL devices are described in Table 18.

Some Spartan-XL devices are available in Pb-free package options. The Pb-free package options have the same pinouts as the standard package options.

Table 18: Pin Descriptions

| Pin Name               | I/O<br>During<br>Config. | I/O After<br>Config. | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|--------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permanently D          | Dedicated P              | ins                  |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CC</sub>        | Х                        | Х                    | Eight or more (depending on package) connections to the nominal +5V supply voltage (+3.3V for Spartan-XL devices). All must be connected, and each must be decoupled with a 0.01 –0.1 $\mu$ F capacitor to Ground.                                                                                                                                                                                                                        |

| GND                    | Х                        | Х                    | Eight or more (depending on package type) connections to Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                   |

| CCLK                   | I or O                   | I                    | During configuration, Configuration Clock (CCLK) is an output in Master mode and is an input in Slave mode. After configuration, CCLK has a weak pull-up resistor and can be selected as the Readback Clock. There is no CCLK High or Low time restriction on Spartan/XL devices, except during Readback. See Violating the Maximum High and Low Time Specification for the Readback Clock, page 39 for an explanation of this exception. |

| DONE                   | I/O                      | 0                    | DONE is a bidirectional signal with an optional internal pull-up resistor. As an open-drain output, it indicates the completion of the configuration process. As an input, a Low level on DONE can be configured to delay the global logic initialization and the enabling of outputs.                                                                                                                                                    |

|                        |                          |                      | The optional pull-up resistor is selected as an option in the program that creates the configuration bitstream. The resistor is included by default.                                                                                                                                                                                                                                                                                      |

| PROGRAM                | I                        | I                    | PROGRAM is an active Low input that forces the FPGA to clear its configuration memory. It is used to initiate a configuration cycle. When PROGRAM goes High, the FPGA finishes the current clear cycle and executes another complete clear cycle, before it goes into a WAIT state and releases INIT.                                                                                                                                     |

|                        |                          |                      | The PROGRAM pin has a permanent weak pull-up, so it need not be externally pulled up to VCC.                                                                                                                                                                                                                                                                                                                                              |

| MODE<br>(Spartan)      | I                        | Х                    | The Mode input(s) are sampled after INIT goes High to determine the configuration mode to be used.                                                                                                                                                                                                                                                                                                                                        |

| M0, M1<br>(Spartan-XL) |                          |                      | During configuration, these pins have a weak pull-up resistor. For the most popular configuration mode, Slave Serial, the mode pins can be left unconnected. For Master Serial mode, connect the Mode/M0 pin directly to system ground.                                                                                                                                                                                                   |

# **XCS20 and XCS20XL Device Pinouts**

| ACS20 and ACS20XL Device Pinouts              |          |                        |       |       |                    |  |  |  |

|-----------------------------------------------|----------|------------------------|-------|-------|--------------------|--|--|--|

| XCS20/XL<br>Pad Name                          | VQ100    | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |  |  |  |

| PROGRAM                                       | P52      | M13                    | P74   | P106  | -                  |  |  |  |

| I/O (D7 <sup>(2)</sup> )                      | P53      | L12                    | P75   | P107  | 367 <sup>(3)</sup> |  |  |  |

| I/O,                                          | P54      | L13                    | P76   | P108  | 370 <sup>(3)</sup> |  |  |  |

| PGCK3 <sup>(1)</sup> ,<br>GCK5 <sup>(2)</sup> |          |                        |       |       |                    |  |  |  |

| I/O                                           |          | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |  |

| 1/0                                           | -        | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |  |

| I/O (D6 <sup>(2)</sup> )                      | -<br>P55 | K11                    | P79   | P110  | 379 <sup>(3)</sup> |  |  |  |

| I/O (D6(=/)                                   |          | K12                    |       | P112  | 382 (3)            |  |  |  |

|                                               | P56      | NIS                    | P80   |       | 385 (3)            |  |  |  |

| 1/0                                           | -        | -                      | -     | P114  |                    |  |  |  |

| 1/0                                           | -        | -                      | -     | P115  | 388 (3)            |  |  |  |

| 1/0                                           | -        | -                      | -     | P116  | 391 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P117  | 394 <sup>(3)</sup> |  |  |  |

| GND                                           | -        | J10                    | P81   | P118  | - (2)              |  |  |  |

| I/O                                           | -        | J11                    | P82   | P119  | 397 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | J12                    | P83   | P120  | 400 (3)            |  |  |  |

| VCC <sup>(2)</sup>                            | -        | -                      | -     | P121  | - (0)              |  |  |  |

| I/O (D5 <sup>(2)</sup> )                      | P57      | J13                    | P84   | P122  | 403 (3)            |  |  |  |

| I/O                                           | P58      | H10                    | P85   | P123  | 406 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P124  | 409 (3)            |  |  |  |

| I/O                                           | -        | -                      | -     | P125  | 412 <sup>(3)</sup> |  |  |  |

| I/O                                           | P59      | H11                    | P86   | P126  | 415 <sup>(3)</sup> |  |  |  |

| I/O                                           | P60      | H12                    | P87   | P127  | 418 <sup>(3)</sup> |  |  |  |

| I/O (D4 <sup>(2)</sup> )                      | P61      | H13                    | P88   | P128  | 421 <sup>(3)</sup> |  |  |  |

| I/O                                           | P62      | G12                    | P89   | P129  | 424 <sup>(3)</sup> |  |  |  |

| VCC                                           | P63      | G13                    | P90   | P130  | -                  |  |  |  |

| GND                                           | P64      | G11                    | P91   | P131  | -                  |  |  |  |

| I/O (D3 <sup>(2)</sup> )                      | P65      | G10                    | P92   | P132  | 427 <sup>(3)</sup> |  |  |  |

| I/O                                           | P66      | F13                    | P93   | P133  | 430 <sup>(3)</sup> |  |  |  |

| I/O                                           | P67      | F12                    | P94   | P134  | 433 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | F11                    | P95   | P135  | 436 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P136  | 439 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P137  | 442 (3)            |  |  |  |

| I/O (D2 <sup>(2)</sup> )                      | P68      | F10                    | P96   | P138  | 445 <sup>(3)</sup> |  |  |  |

| I/O                                           | P69      | E13                    | P97   | P139  | 448 <sup>(3)</sup> |  |  |  |

| VCC <sup>(2)</sup>                            | -        | -                      | -     | P140  | -                  |  |  |  |

| I/O                                           | _        | E12                    | P98   | P141  | 451 <sup>(3)</sup> |  |  |  |

| I/O                                           | _        | E11                    | P99   | P142  | 454 <sup>(3)</sup> |  |  |  |

| GND                                           | -        | E10                    | P100  | P143  | -                  |  |  |  |

| I/O                                           | -        | -                      | -     | P145  | 457 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P146  | 460 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P147  | 463 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | -                      | -     | P148  | 466 <sup>(3)</sup> |  |  |  |

| I/O (D1 <sup>(2)</sup> )                      | P70      | D13                    | P101  | P149  | 469 <sup>(3)</sup> |  |  |  |

| I/O                                           | P71      | D12                    | P102  | P150  | 472 <sup>(3)</sup> |  |  |  |

| I/O                                           | -        | D11                    | P103  | P151  | 475 <sup>(3)</sup> |  |  |  |

# **XCS20 and XCS20XL Device Pinouts**

| XCS20/XL<br>Pad Name                                            | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |

|-----------------------------------------------------------------|-------|------------------------|-------|-------|--------------------|

| I/O                                                             | -     | C13                    | P104  | P152  | 478 <sup>(3)</sup> |

| I/O<br>(D0 <sup>(2)</sup> , DIN)                                | P72   | C12                    | P105  | P153  | 481 <sup>(3)</sup> |

| I/O,<br>SGCK4 <sup>(1)</sup> ,<br>GCK6 <sup>(2)</sup><br>(DOUT) | P73   | C11                    | P106  | P154  | 484 <sup>(3)</sup> |

| CCLK                                                            | P74   | B13                    | P107  | P155  | -                  |

| VCC                                                             | P75   | B12                    | P108  | P156  | -                  |

| O, TDO                                                          | P76   | A13                    | P109  | P157  | 0                  |

| GND                                                             | P77   | A12                    | P110  | P158  | -                  |

| I/O                                                             | P78   | B11                    | P111  | P159  | 2                  |

| I/O,<br>PGCK4 <sup>(1)</sup> ,<br>GCK7 <sup>(2)</sup>           | P79   | A11                    | P112  | P160  | 5                  |

| I/O                                                             | -     | D10                    | P113  | P161  | 8                  |

| I/O                                                             | -     | C10                    | P114  | P162  | 11                 |

| I/O (CS1 <sup>(2)</sup> )                                       | P80   | B10                    | P115  | P163  | 14                 |

| I/O                                                             | P81   | A10                    | P116  | P164  | 17                 |

| I/O                                                             | -     | D9                     | P117  | P166  | 20                 |

| I/O                                                             | -     | -                      | -     | P167  | 23                 |

| I/O                                                             | -     | -                      | -     | P168  | 26                 |

| I/O                                                             | -     | -                      | -     | P169  | 29                 |

| GND                                                             | -     | C9                     | P118  | P170  | -                  |

| I/O                                                             | -     | B9                     | P119  | P171  | 32                 |

| I/O                                                             | -     | A9                     | P120  | P172  | 35                 |

| VCC <sup>(2)</sup>                                              | -     | -                      | -     | P173  | -                  |

| I/O                                                             | P82   | D8                     | P121  | P174  | 38                 |

| I/O                                                             | P83   | C8                     | P122  | P175  | 41                 |

| I/O                                                             | -     | -                      | -     | P176  | 44                 |

| I/O                                                             | -     | -                      | -     | P177  | 47                 |

| I/O                                                             | P84   | B8                     | P123  | P178  | 50                 |

| I/O                                                             | P85   | A8                     | P124  | P179  | 53                 |

| I/O                                                             | P86   | B7                     | P125  | P180  | 56                 |

| I/O                                                             | P87   | A7                     | P126  | P181  | 59                 |

| GND                                                             | P88   | C7                     | P127  | P182  | -                  |

2/8/00

## Additional XCS20/XL Package Pins

| PQ208              |                                                                      |      |                     |                     |      |  |  |  |  |

|--------------------|----------------------------------------------------------------------|------|---------------------|---------------------|------|--|--|--|--|

|                    | Not Connected Pins                                                   |      |                     |                     |      |  |  |  |  |

| P12                | P12 P18 <sup>(1)</sup> P33 <sup>(1)</sup> P39 P65 P71 <sup>(1)</sup> |      |                     |                     |      |  |  |  |  |

| P86 <sup>(1)</sup> | P92                                                                  | P111 | P121 <sup>(1)</sup> | P140 <sup>(1)</sup> | P144 |  |  |  |  |

| P165               | P165 P173 <sup>(1)</sup> P192 <sup>(1)</sup> P202 P203 -             |      |                     |                     |      |  |  |  |  |

| 9/16/98            |                                                                      |      |                     |                     |      |  |  |  |  |

#### Notes:

- 1. 5V Spartan family only

- 2. 3V Spartan-XL family only

- The "PWRDWN" on the XCS20XL is not part of the Boundary Scan chain. For the XCS20XL, subtract 1 from all Boundary Scan numbers from GCK3 on (247 and higher).

- 4. CS144 package discontinued by PDN2004-01

# XCS30 and XCS30XL Device Pinouts

| XCS30/XL<br>Pad Name                            | VQ100 <sup>(5)</sup> | TQ144 | PQ208 | PQ240 | BG256 <sup>(5)</sup> | CS280 <sup>(2,5)</sup> | Bndry<br>Scan |

|-------------------------------------------------|----------------------|-------|-------|-------|----------------------|------------------------|---------------|

| VCC                                             | P89                  | P128  | P183  | P212  | VCC <sup>(4)</sup>   | C10                    | -             |

| I/O                                             | P90                  | P129  | P184  | P213  | C10                  | D10                    | 74            |

| I/O                                             | P91                  | P130  | P185  | P214  | D10                  | E10                    | 77            |

| I/O                                             | P92                  | P131  | P186  | P215  | A9                   | A9                     | 80            |

| I/O                                             | P93                  | P132  | P187  | P216  | B9                   | В9                     | 83            |

| I/O                                             | -                    | -     | P188  | P217  | C9                   | C9                     | 86            |

| I/O                                             | -                    | -     | P189  | P218  | D9                   | D9                     | 89            |

| I/O                                             | P94                  | P133  | P190  | P220  | A8                   | A8                     | 92            |

| I/O                                             | P95                  | P134  | P191  | P221  | B8                   | B8                     | 95            |

| VCC                                             | -                    | -     | P192  | P222  | VCC <sup>(4)</sup>   | A7                     | -             |

| I/O                                             | -                    | -     | -     | P223  | A6                   | B7                     | 98            |

| I/O                                             | -                    | -     | -     | P224  | C7                   | C7                     | 101           |

| I/O                                             | -                    | P135  | P193  | P225  | B6                   | D7                     | 104           |

| I/O                                             | -                    | P136  | P194  | P226  | A5                   | A6                     | 107           |

| GND                                             | -                    | P137  | P195  | P227  | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -             |

| I/O                                             | -                    | -     | P196  | P228  | C6                   | В6                     | 110           |

| I/O                                             | -                    | -     | P197  | P229  | B5                   | C6                     | 113           |

| I/O                                             | -                    | -     | P198  | P230  | A4                   | D6                     | 116           |

| I/O                                             | -                    | -     | P199  | P231  | C5                   | E6                     | 119           |

| I/O                                             | P96                  | P138  | P200  | P232  | B4                   | <b>A</b> 5             | 122           |

| I/O                                             | P97                  | P139  | P201  | P233  | A3                   | C5                     | 125           |

| I/O                                             | -                    | -     | P202  | P234  | D5                   | B4                     | 128           |

| I/O                                             | -                    | -     | P203  | P235  | C4                   | C4                     | 131           |

| I/O                                             | -                    | P140  | P204  | P236  | В3                   | A3                     | 134           |

| I/O                                             | -                    | P141  | P205  | P237  | B2                   | A2                     | 137           |

| I/O                                             | P98                  | P142  | P206  | P238  | A2                   | В3                     | 140           |

| I/O, SGCK1 <sup>(1)</sup> , GCK8 <sup>(2)</sup> | P99                  | P143  | P207  | P239  | СЗ                   | B2                     | 143           |

| VCC                                             | P100                 | P144  | P208  | P240  | VCC <sup>(4)</sup>   | A1                     | -             |

| GND                                             | P1                   | P1    | P1    | P1    | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -             |

| I/O, PGCK1 <sup>(1)</sup> , GCK1 <sup>(2)</sup> | P2                   | P2    | P2    | P2    | B1                   | C3                     | 146           |

| I/O                                             | P3                   | P3    | P3    | P3    | C2                   | C2                     | 149           |

| I/O                                             | -                    | P4    | P4    | P4    | D2                   | B1                     | 152           |

# XCS30 and XCS30XL Device Pinouts (Continued)

| XCS30/XL<br>Pad Name | VQ100 <sup>(5)</sup> | TQ144 | PQ208 | PQ240 | BG256 <sup>(5)</sup> | CS280 <sup>(2,5)</sup> | Bndry<br>Scan |

|----------------------|----------------------|-------|-------|-------|----------------------|------------------------|---------------|

| I/O                  | -                    | P5    | P5    | P5    | D3                   | C1                     | 155           |

| I/O, TDI             | P4                   | P6    | P6    | P6    | E4                   | D4                     | 158           |

| I/O, TCK             | P5                   | P7    | P7    | P7    | C1                   | D3                     | 161           |

| I/O                  | -                    | -     | P8    | P8    | D1                   | E2                     | 164           |

| I/O                  | -                    | -     | P9    | P9    | E3                   | E4                     | 167           |

| I/O                  | -                    | -     | P10   | P10   | E2                   | E1                     | 170           |

| I/O                  | -                    | -     | P11   | P11   | E1                   | F5                     | 173           |

| I/O                  | -                    | -     | P12   | P12   | F3                   | F3                     | 176           |

| I/O                  | -                    | -     | -     | P13   | F2                   | F2                     | 179           |

| GND                  | -                    | P8    | P13   | P14   | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -             |

| I/O                  | -                    | P9    | P14   | P15   | G3                   | F4                     | 182           |

| I/O                  | -                    | P10   | P15   | P16   | G2                   | F1                     | 185           |

| I/O, TMS             | P6                   | P11   | P16   | P17   | G1                   | G3                     | 188           |

| I/O                  | P7                   | P12   | P17   | P18   | НЗ                   | G2                     | 191           |

| VCC                  | -                    | -     | P18   | P19   | VCC <sup>(4)</sup>   | G1                     | -             |

| I/O                  | -                    | -     | -     | P20   | H2                   | G4                     | 194           |

| I/O                  | -                    | -     | -     | P21   | H1                   | H1                     | 197           |

| I/O                  | -                    | -     | P19   | P23   | J2                   | H4                     | 200           |

| I/O                  | -                    | -     | P20   | P24   | J1                   | J1                     | 203           |

| I/O                  | -                    | P13   | P21   | P25   | K2                   | J2                     | 206           |

| I/O                  | P8                   | P14   | P22   | P26   | КЗ                   | J3                     | 209           |

| I/O                  | P9                   | P15   | P23   | P27   | K1                   | J4                     | 212           |

| I/O                  | P10                  | P16   | P24   | P28   | L1                   | K1                     | 215           |

| GND                  | P11                  | P17   | P25   | P29   | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -             |

| VCC                  | P12                  | P18   | P26   | P30   | VCC <sup>(4)</sup>   | K2                     | -             |

| I/O                  | P13                  | P19   | P27   | P31   | L2                   | K3                     | 218           |

| I/O                  | P14                  | P20   | P28   | P32   | L3                   | K4                     | 221           |

| I/O                  | P15                  | P21   | P29   | P33   | L4                   | K5                     | 224           |

| I/O                  | -                    | P22   | P30   | P34   | M1                   | L1                     | 227           |

| I/O                  | -                    | -     | P31   | P35   | M2                   | L2                     | 230           |

| I/O                  | -                    | -     | P32   | P36   | M3                   | L3                     | 233           |

| I/O                  | -                    | -     | -     | P38   | N1                   | M2                     | 236           |

| I/O                  | -                    | -     | -     | P39   | N2                   | M3                     | 239           |

| VCC                  | -                    | -     | P33   | P40   | VCC <sup>(4)</sup>   | M4                     | -             |

| I/O                  | P16                  | P23   | P34   | P41   | P1                   | N1                     | 242           |

| I/O                  | P17                  | P24   | P35   | P42   | P2                   | N2                     | 245           |

| I/O                  | -                    | P25   | P36   | P43   | R1                   | N3                     | 248           |

| I/O                  | -                    | P26   | P37   | P44   | P3                   | N4                     | 251           |

| GND                  | -                    | P27   | P38   | P45   | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -             |

| I/O                  | -                    | -     | -     | P46   | T1                   | P1                     | 254           |

| I/O                  | -                    | -     | P39   | P47   | R3                   | P2                     | 257           |

| I/O                  | -                    | -     | P40   | P48   | T2                   | P3                     | 260           |

| I/O                  | -                    | -     | P41   | P49   | U1                   | P4                     | 263           |

| I/O                  | -                    | _     | P42   | P50   | T3                   | P5                     | 266           |

| I/O                  | -                    | _     | P43   | P51   | U2                   | R1                     | 269           |

# XCS30 and XCS30XL Device Pinouts (Continued)

| XCS30/XL<br>Pad Name                            | VQ100 <sup>(5)</sup> | TQ144 | PQ208 | PQ240 | BG256 <sup>(5)</sup> | CS280 <sup>(2,5)</sup> | Bndry<br>Scan      |

|-------------------------------------------------|----------------------|-------|-------|-------|----------------------|------------------------|--------------------|

| I/O                                             | -                    | -     | P85   | P97   | U12                  | T11                    | 382 <sup>(3)</sup> |

| I/O                                             | -                    | -     | -     | P99   | V13                  | U12                    | 385 <sup>(3)</sup> |

| I/O                                             | -                    | -     | -     | P100  | Y14                  | T12                    | 388 (3)            |

| VCC                                             | -                    | -     | P86   | P101  | VCC <sup>(4)</sup>   | W13                    | -                  |

| I/O                                             | P43                  | P60   | P87   | P102  | Y15                  | V13                    | 391 <sup>(3)</sup> |

| I/O                                             | P44                  | P61   | P88   | P103  | V14                  | U13                    | 394 <sup>(3)</sup> |

| I/O                                             | -                    | P62   | P89   | P104  | W15                  | T13                    | 397 <sup>(3)</sup> |

| I/O                                             | -                    | P63   | P90   | P105  | Y16                  | W14                    | 400 (3)            |

| GND                                             | -                    | P64   | P91   | P106  | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -                  |

| I/O                                             | -                    | -     | -     | P107  | V15                  | V14                    | 403 (3)            |

| I/O                                             | -                    | -     | P92   | P108  | W16                  | U14                    | 406 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P93   | P109  | Y17                  | T14                    | 409 (3)            |

| I/O                                             | -                    | -     | P94   | P110  | V16                  | R14                    | 412 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P95   | P111  | W17                  | W15                    | 415 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P96   | P112  | Y18                  | U15                    | 418 <sup>(3)</sup> |

| I/O                                             | P45                  | P65   | P97   | P113  | U16                  | V16                    | 421 <sup>(3)</sup> |

| I/O                                             | P46                  | P66   | P98   | P114  | V17                  | U16                    | 424 (3)            |

| I/O                                             | -                    | P67   | P99   | P115  | W18                  | W17                    | 427 (3)            |

| I/O                                             | -                    | P68   | P100  | P116  | Y19                  | W18                    | 430 (3)            |

| I/O                                             | P47                  | P69   | P101  | P117  | V18                  | V17                    | 433 (3)            |

| I/O, SGCK3 <sup>(1)</sup> , GCK4 <sup>(2)</sup> | P48                  | P70   | P102  | P118  | W19                  | V18                    | 436 <sup>(3)</sup> |

| GND                                             | P49                  | P71   | P103  | P119  | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -                  |

| DONE                                            | P50                  | P72   | P104  | P120  | Y20                  | W19                    | -                  |

| VCC                                             | P51                  | P73   | P105  | P121  | VCC <sup>(4)</sup>   | U17                    | -                  |

| PROGRAM                                         | P52                  | P74   | P106  | P122  | V19                  | U18                    | -                  |

| I/O (D7 <sup>(2)</sup> )                        | P53                  | P75   | P107  | P123  | U19                  | V19                    | 439 (3)            |

| I/O, PGCK3 <sup>(1)</sup> , GCK5 <sup>(2)</sup> | P54                  | P76   | P108  | P124  | U18                  | U19                    | 442 (3)            |

| I/O                                             | -                    | P77   | P109  | P125  | T17                  | T16                    | 445 <sup>(3)</sup> |

| I/O                                             | -                    | P78   | P110  | P126  | V20                  | T17                    | 448 (3)            |

| I/O                                             | -                    | -     | -     | P127  | U20                  | T18                    | 451 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P111  | P128  | T18                  | T19                    | 454 <sup>(3)</sup> |

| I/O (D6 <sup>(2)</sup> )                        | P55                  | P79   | P112  | P129  | T19                  | R16                    | 457 <sup>(3)</sup> |

| I/O                                             | P56                  | P80   | P113  | P130  | T20                  | R19                    | 460 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P114  | P131  | R18                  | P15                    | 463 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P115  | P132  | R19                  | P17                    | 466 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P116  | P133  | R20                  | P18                    | 469 <sup>(3)</sup> |

| I/O                                             | -                    | -     | P117  | P134  | P18                  | P16                    | 472 <sup>(3)</sup> |

| GND                                             | -                    | P81   | P118  | P135  | GND <sup>(4)</sup>   | GND <sup>(4)</sup>     | -                  |

| I/O                                             | -                    | -     | -     | P136  | P20                  | P19                    | 475 <sup>(3)</sup> |

| I/O                                             | -                    | -     | -     | P137  | N18                  | N17                    | 478 <sup>(3)</sup> |

| I/O                                             | -                    | P82   | P119  | P138  | N19                  | N18                    | 481 <sup>(3)</sup> |

| I/O                                             | -                    | P83   | P120  | P139  | N20                  | N19                    | 484 (3)            |

| VCC                                             | -                    | -     | P121  | P140  | VCC <sup>(4)</sup>   | N16                    | -                  |

| I/O (D5 <sup>(2)</sup> )                        | P57                  | P84   | P122  | P141  | M17                  | M19                    | 487 <sup>(3)</sup> |

| I/O                                             | P58                  | P85   | P123  | P142  | M18                  | M17                    | 490 (3)            |

# **Product Availability**

Table 19 shows the packages and speed grades for Spartan/XL devices. Table 20 shows the number of user I/Os available for each device/package combination.

Table 19: Component Availability Chart for Spartan/XL FPGAs

|           | Pins | 84                  | 100                  | 144                  | 144             | 208             | 240             | 256                  | 280                  |

|-----------|------|---------------------|----------------------|----------------------|-----------------|-----------------|-----------------|----------------------|----------------------|

|           | Туре | Plastic<br>PLCC     | Plastic<br>VQFP      | Chip<br>Scale        | Plastic<br>TQFP | Plastic<br>PQFP | Plastic<br>PQFP | Plastic<br>BGA       | Chip<br>Scale        |

| Device    | Code | PC84 <sup>(3)</sup> | VQ100 <sup>(3)</sup> | CS144 <sup>(3)</sup> | TQ144           | PQ208           | PQ240           | BG256 <sup>(3)</sup> | CS280 <sup>(3)</sup> |

| XCS05     | -3   | C(3)                | C, I                 | -                    | -               | -               | -               | -                    | -                    |

| AC305     | -4   | C(3)                | С                    | -                    | -               | -               | -               | -                    | -                    |

| XCS10     | -3   | C(3)                | C, I                 | -                    | С               | -               | -               | -                    | -                    |

| AUS10 -   | -4   | C(3)                | С                    | -                    | С               | -               | -               | -                    | -                    |

| XCS20     | -3   | -                   | С                    | -                    | C, I            | C, I            | -               | -                    | -                    |

| ۸0320     | -4   | -                   | С                    | -                    | С               | С               | -               | -                    | -                    |