Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 400                                                         |

| Number of Logic Elements/Cells | 950                                                         |

| Total RAM Bits                 | 12800                                                       |

| Number of I/O                  | 160                                                         |

| Number of Gates                | 20000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                   |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcs20xl-5pq208c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- The 16 x 1 single-port configuration contains a RAM array with 16 locations, each one-bit wide. One 4-bit address decoder determines the RAM location for write and read operations. There is one input for writing data and one output for reading data, all at the selected address.

- The (16 x 1) x 2 single-port configuration combines two 16 x 1 single-port configurations (each according to the preceding description). There is one data input, one data output and one address decoder for each array. These arrays can be addressed independently.

- The 32 x 1 single-port configuration contains a RAM array with 32 locations, each one-bit wide. There is one data input, one data output, and one 5-bit address decoder.

- The dual-port mode 16 x 1 configuration contains a RAM array with 16 locations, each one-bit wide. There are two 4-bit address decoders, one for each port. One port consists of an input for writing and an output for reading, all at a selected address. The other port consists of one output for reading from an independently selected address.

The appropriate choice of RAM configuration mode for a given design should be based on timing and resource requirements, desired functionality, and the simplicity of the design process. Selection criteria include the following: Whereas the 32 x 1 single-port, the (16 x 1) x 2 single-port, and the 16 x 1 dual-port configurations each use one entire CLB, the 16 x 1 single-port configuration uses only one half of a CLB. Due to its simultaneous read/write capability, the dual-port RAM can transfer twice as much data as the single-port RAM, which permits only one data operation at any given time.

CLB memory configuration options are selected by using the appropriate library symbol in the design entry.

#### **Single-Port Mode**

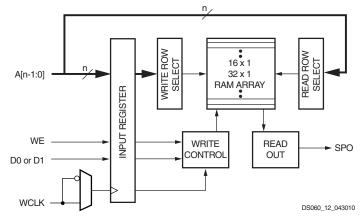

There are three CLB memory configurations for the single-port RAM:  $16 \times 1$ ,  $(16 \times 1) \times 2$ , and  $32 \times 1$ , the functional organization of which is shown in Figure 12.

The single-port RAM signals and the CLB signals (Figure 2, page 4) from which they are originally derived are shown in Table 9.

Table 9: Single-Port RAM Signals

| RAM Signal       | Function                      | CLB Signal                           |

|------------------|-------------------------------|--------------------------------------|

| D0 or D1         | Data In                       | DIN or H1                            |

| A[3:0]           | Address                       | F[4:1] or G[4:1]                     |

| A4 (32 x 1 only) | Address                       | H1                                   |

| WE               | Write Enable                  | SR                                   |

| WCLK             | Clock                         | К                                    |

| SPO              | Single Port Out<br>(Data Out) | F <sub>OUT</sub> or G <sub>OUT</sub> |

#### Notes:

- The (16 x 1) x 2 configuration combines two 16 x 1 single-port RAMs, each with its own independent address bus and data input. The same WE and WCLK signals are connected to both RAMs.

- 2. n = 4 for the 16 x 1 and (16 x 1) x 2 configurations. n = 5 for the 32 x 1 configuration.

Figure 12: Logic Diagram for the Single-Port RAM

Writing data to the single-port RAM is essentially the same as writing to a data register. It is an edge-triggered (synchronous) operation performed by applying an address to the A inputs and data to the D input during the active edge of WCLK while WE is High.

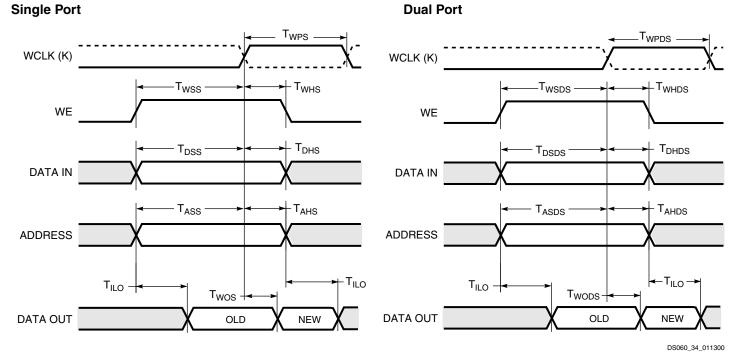

The timing relationships are shown in Figure 13. The High logic level on WE enables the input data register for writing. The active edge of WCLK latches the address, input data, and WE signals. Then, an internal write pulse is generated that loads the data into the memory cell.

CLB signals from which they are originally derived are shown in Table 10.

Table 10: Dual-Port RAM Signals

| RAM Signal | Function                                           | CLB Signal       |

|------------|----------------------------------------------------|------------------|

| D          | Data In                                            | DIN              |

| A[3:0]     | Read Address for<br>Single-Port.                   | F[4:1]           |

|            | Write Address for<br>Single-Port and<br>Dual-Port. |                  |

| DPRA[3:0]  | Read Address for<br>Dual-Port                      | G[4:1]           |

| WE         | Write Enable                                       | SR               |

| WCLK       | Clock                                              | К                |

| SPO        | Single Port Out (addressed by A[3:0])              | F <sub>OUT</sub> |

| DPO        | Dual Port Out<br>(addressed by<br>DPRA[3:0])       | G <sub>OUT</sub> |

The RAM16X1D primitive used to instantiate the dual-port RAM consists of an upper and a lower 16 x 1 memory array. The address port labeled A[3:0] supplies both the read and write addresses for the lower memory array, which behaves the same as the 16 x 1 single-port RAM array described previously. Single Port Out (SPO) serves as the data output for the lower memory. Therefore, SPO reflects the data at address A[3:0].

The other address port, labeled DPRA[3:0] for Dual Port Read Address, supplies the read address for the upper memory. The write address for this memory, however, comes from the address A[3:0]. Dual Port Out (DPO) serves as the data output for the upper memory. Therefore, DPO reflects the data at address DPRA[3:0].

By using A[3:0] for the write address and DPRA[3:0] for the read address, and reading only the DPO output, a FIFO that can read and write simultaneously is easily generated. The simultaneous read/write capability possible with the dual-port RAM can provide twice the effective data throughput of a single-port RAM alternating read and write operations.

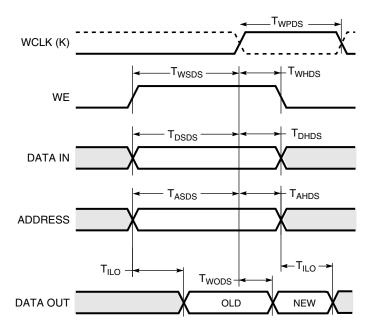

The timing relationships for the dual-port RAM mode are shown in Figure 13.

Note that write operations to RAM are synchronous (edge-triggered); however, data access is asynchronous.

### **Initializing RAM at FPGA Configuration**

Both RAM and ROM implementations in the Spartan/XL families are initialized during device configuration. The initial contents are defined via an INIT attribute or property

attached to the RAM or ROM symbol, as described in the library guide. If not defined, all RAM contents are initialized to zeros, by default.

RAM initialization occurs only during device configuration. The RAM content is not affected by GSR.

#### More Information on Using RAM Inside CLBs

Three application notes are available from Xilinx that discuss synchronous (edge-triggered) RAM: "Xilinx Edge-Triggered and Dual-Port RAM Capability," "Implementing FIFOs in Xilinx RAM," and "Synchronous and Asynchronous FIFO Designs." All three application notes apply to both the Spartan and the Spartan-XL families.

# **Fast Carry Logic**

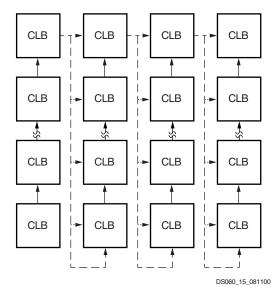

Each CLB F-LUT and G-LUT contains dedicated arithmetic logic for the fast generation of carry and borrow signals. This extra output is passed on to the function generator in the adjacent CLB. The carry chain is independent of normal routing resources. (See Figure 15.)

Dedicated fast carry logic greatly increases the efficiency and performance of adders, subtractors, accumulators, comparators and counters. It also opens the door to many new applications involving arithmetic operation, where the previous generations of FPGAs were not fast enough or too inefficient. High-speed address offset calculations in microprocessor or graphics systems, and high-speed addition in digital signal processing are two typical applications.

The two 4-input function generators can be configured as a 2-bit adder with built-in hidden carry that can be expanded to any length. This dedicated carry circuitry is so fast and efficient that conventional speed-up methods like carry generate/propagate are meaningless even at the 16-bit level, and of marginal benefit at the 32-bit level. This fast carry logic is one of the more significant features of the Spartan

Figure 15: Available Spartan/XL Carry Propagation Paths

and Spartan-XL families, speeding up arithmetic and counting functions.

The carry chain in 5V Spartan devices can run either up or down. At the top and bottom of the columns where there are no CLBs above and below, the carry is propagated to the right. The default is always to propagate up the column, as shown in the figures. The carry chain in Spartan-XL devices can only run up the column, providing even higher speed.

Figure 16, page 18 shows a Spartan/XL FPGA CLB with dedicated fast carry logic. The carry logic shares operand

and control inputs with the function generators. The carry outputs connect to the function generators, where they are combined with the operands to form the sums.

Figure 17, page 19 shows the details of the Spartan/XL FPGA carry logic. This diagram shows the contents of the box labeled "CARRY LOGIC" in Figure 16.

The fast carry logic can be accessed by placing special library symbols, or by using Xilinx Relationally Placed Macros (RPMs) that already include these symbols.

Even if the boundary scan symbol is used in a design, the input pins TMS, TCK, and TDI can still be used as inputs to be routed to internal logic. Care must be taken not to force the chip into an undesired boundary scan state by inadvertently applying boundary scan input patterns to these pins. The simplest way to prevent this is to keep TMS High, and then apply whatever signal is desired to TDI and TCK.

## **Avoiding Inadvertent Boundary Scan**

If TMS or TCK is used as user I/O, care must be taken to ensure that at least one of these pins is held constant during configuration. In some applications, a situation may occur where TMS or TCK is driven during configuration. This may cause the device to go into boundary scan mode and disrupt the configuration process.

To prevent activation of boundary scan during configuration, do either of the following:

- TMS: Tie High to put the Test Access Port controller in a benign RESET state.

- TCK: Tie High or Low—do not toggle this clock input.

For more information regarding boundary scan, refer to the Xilinx Application Note, "Boundary Scan in FPGA Devices."

# Boundary Scan Enhancements (Spartan-XL Family Only)

Spartan-XL devices have improved boundary scan functionality and performance in the following areas:

**IDCODE:** The IDCODE register is supported. By using the IDCODE, the device connected to the JTAG port can be determined. The use of the IDCODE enables selective configuration dependent on the FPGA found.

The IDCODE register has the following binary format:

vvvv:ffff:fffa:aaaa:aaaa:cccc:cccc1

#### where

c = the company code (49h for Xilinx)

a = the array dimension in CLBs (ranges from 0Ah for XCS05XL to 1Ch for XCS40XL)

f = the family code (02h for Spartan-XL family)

v = the die version number

Table 13: IDCODEs Assigned to Spartan-XL FPGAs

| FPGA    | IDCODE    |

|---------|-----------|

| XCS05XL | 0040A093h |

| XCS10XL | 0040E093h |

| XCS20XL | 00414093h |

| XCS30XL | 00418093h |

| XCS40XL | 0041C093h |

**Configuration State:** The configuration state is available to JTAG controllers.

**Configuration Disable:** The JTAG port can be prevented from configuring the FPGA.

**TCK Startup:** TCK can now be used to clock the start-up block in addition to other user clocks.

**CCLK Holdoff:** Changed the requirement for Boundary Scan Configure or EXTEST to be issued prior to the release of INIT pin and CCLK cycling.

**Reissue Configure:** The Boundary Scan Configure can be reissued to recover from an unfinished attempt to configure the device.

**Bypass FF:** Bypass FF and IOB is modified to provide DRCLOCK only during BYPASS for the bypass flip-flop, and during EXTEST or SAMPLE/PRELOAD for the IOB register.

# Power-Down (Spartan-XL Family Only)

All Spartan/XL devices use a combination of efficient segmented routing and advanced process technology to provide low power consumption under all conditions. The 3.3V Spartan-XL family adds a dedicated active Low power-down pin (PWRDWN) to reduce supply current to 100  $\mu A$  typical. The PWRDWN pin takes advantage of one of the unused No Connect locations on the 5V Spartan device. The user must de-select the "5V Tolerant I/Os" option in the Configuration Options to achieve the specified Power Down current. The PWRDWN pin has a default internal pull-up resistor, allowing it to be left unconnected if unused.

$V_{CC}$  must continue to be supplied during Power-down, and configuration data is maintained. When the  $\overline{PWRDWN}$  pin is pulled Low, the input and output buffers are disabled. The inputs are internally forced to a logic Low level, including the MODE pins, DONE, CCLK, and  $\overline{TDO}$ , and all internal pull-up resistors are turned off. The  $\overline{PROGRAM}$  pin is not affected by Power Down. The GSR net is asserted during Power Down, initializing all the flip-flops to their start-up state.

PWRDWN has a minimum pulse width of 50 ns (Figure 23). On entering the Power-down state, the inputs will be disabled and the flip-flops set/reset, and then the outputs are disabled about 10 ns later. The user may prefer to assert the GTS or GSR signals before PWRDWN to affect the order of events. When the PWRDWN signal is returned High, the inputs will be enabled first, followed immediately by the release of the GSR signal initializing the flip-flops. About 10 ns later, the outputs will be enabled. Allow 50 ns after the release of PWRDWN before using the device.

### **Master Serial Mode**

The Master serial mode uses an internal oscillator to generate a Configuration Clock (CCLK) for driving potential slave devices and the Xilinx serial-configuration PROM (SPROM). The CCLK speed is selectable as either 1 MHz (default) or 8 MHz. Configuration always starts at the default slow frequency, then can switch to the higher frequency during the first frame. Frequency tolerance is –50% to +25%.

In Master Serial mode, the CCLK output of the device drives a Xilinx SPROM that feeds the FPGA DIN input. Each rising edge of the CCLK output increments the Serial PROM internal address counter. The next data bit is put on the SPROM data output, connected to the FPGA DIN pin. The FPGA accepts this data on the subsequent rising CCLK edge.

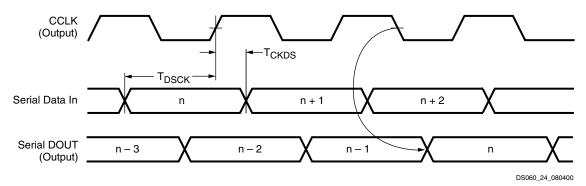

When used in a daisy-chain configuration the Master Serial FPGA is placed as the first device in the chain and is referred to as the lead FPGA. The lead FPGA presents the preamble data, and all data that overflows the lead device, on its DOUT pin. There is an internal pipeline delay of 1.5 CCLK periods, which means that DOUT changes on the

falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge. See the timing diagram in Figure 24.

In the bitstream generation software, the user can specify Fast Configuration Rate, which, starting several bits into the first frame, increases the CCLK frequency by a factor of eight. For actual timing values please refer to the specification section. Be sure that the serial PROM and slaves are fast enough to support this data rate. Earlier families such as the XC3000 series do not support the Fast Configuration Rate option.

The SPROM CE input can be driven from either  $\overline{\text{LDC}}$  or DONE. Using  $\overline{\text{LDC}}$  avoids potential contention on the DIN pin, if this pin is configured as user I/O, but  $\overline{\text{LDC}}$  is then restricted to be a permanently High user output after configuration. Using DONE can also avoid contention on DIN, provided the Early DONE option is invoked.

Figure 25 shows a full master/slave system. The leftmost device is in Master Serial mode, all other devices in the chain are in Slave Serial mode.

|      | Symbol            | Description | Min | Units |

|------|-------------------|-------------|-----|-------|

| CCLK | T <sub>DSCK</sub> | DIN setup   | 20  | ns    |

| COLK | T <sub>CKDS</sub> | DIN hold    | 0   | ns    |

#### Notes:

- 1. At power-up,  $V_{CC}$  must rise from 2.0V to  $V_{CC}$  min in less than 25 ms, otherwise delay configuration by pulling PROGRAM Low until  $V_{CC}$  is valid.

- Master Serial mode timing is based on testing in slave mode.

Figure 24: Master Serial Mode Programming Switching Characteristics

#### Slave Serial Mode

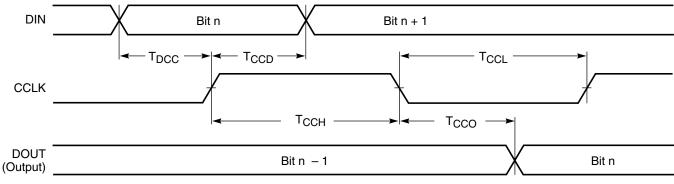

In Slave Serial mode, the FPGA receives serial configuration data on the rising edge of CCLK and, after loading its configuration, passes additional data out, resynchronized on the next falling edge of CCLK.

In this mode, an external signal drives the CCLK input of the FPGA (most often from a Master Serial device). The serial configuration bitstream must be available at the DIN input of the lead FPGA a short setup time before each rising CCLK edge.

The lead FPGA then presents the preamble data—and all data that overflows the lead device—on its DOUT pin. There is an internal delay of 0.5 CCLK periods, which means that DOUT changes on the falling CCLK edge, and the next FPGA in the daisy chain accepts data on the subsequent rising CCLK edge.

Figure 25 shows a full master/slave system. A Spartan/XL device in Slave Serial mode should be connected as shown in the third device from the left.

DS060 26 080400

| Symbol           |      | Description | Min | Max  | Units |

|------------------|------|-------------|-----|------|-------|

| T <sub>DCC</sub> | -    | DIN setup   | 20  | -    | ns    |

| T <sub>CCD</sub> |      | DIN hold    | 0   | -    | ns    |

| T <sub>CCO</sub> | CCLK | DIN to DOUT | -   | 30   | ns    |

| T <sub>CCH</sub> | COLK | High time   | 40  | -    | ns    |

| T <sub>CCL</sub> |      | Low time    | 40  | -    | ns    |

| F <sub>CC</sub>  |      | Frequency   | -   | 12.5 | MHz   |

#### Notes:

Figure 26: Slave Serial Mode Programming Switching Characteristics

# **Express Mode (Spartan-XL Family Only)**

Express mode is similar to Slave Serial mode, except that data is processed one byte per CCLK cycle instead of one bit per CCLK cycle. An external source is used to drive CCLK, while byte-wide data is loaded directly into the configuration data shift registers (Figure 27). A CCLK frequency of 1 MHz is equivalent to a 8 MHz serial rate, because eight bits of configuration data are loaded per CCLK cycle. Express mode does not support CRC error checking, but does support constant-field error checking. A length count is not used in Express mode.

Express mode must be specified as an option to the development system. The Express mode bitstream is not compatible with the other configuration modes (see Table 16, page 32.) Express mode is selected by a <0X> on the Mode pins (M1, M0).

The first byte of parallel configuration data must be available at the D inputs of the FPGA a short setup time before the second rising CCLK edge. Subsequent data bytes are clocked in on each consecutive rising CCLK edge (Figure 28).

### Pseudo Daisy Chain

Multiple devices with different configurations can be configured in a pseudo daisy chain provided that all of the devices

are in Express mode. Concatenated bitstreams are used to configure the chain of Express mode devices so that each device receives a separate header. CCLK pins are tied together and D0-D7 pins are tied together for all devices along the chain. A status signal is passed from DOUT to CS1 of successive devices along the chain. Frame data is accepted only when CS1 is High and the device's configuration memory is not already full. The lead device in the chain has its CS1 input tied High (or floating, since there is an internal pull-up). The status pin DOUT is pulled Low after the header is received, and remains Low until the device's configuration memory is full. DOUT is then pulled High to signal the next device in the chain to accept the next header and configuration data on the D0-D7 bus.

The DONE pins of all devices in the chain should be tied together, with one or more active internal pull-ups. If a large number of devices are included in the chain, deactivate some of the internal pull-ups, since the Low-driving DONE pin of the last device in the chain must sink the current from all pull-ups in the chain. The DONE pull-up is activated by default. It can be deactivated using a development system option.

The requirement that all DONE pins in a daisy chain be wired together applies only to Express mode, and only if all devices in the chain are to become active simultaneously. All Spartan-XL devices in Express mode are synchronized

Configuration must be delayed until the INIT pins of all daisy-chained FPGAs are High.

# **Spartan Family CLB Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan devices and expressed in nanoseconds unless otherwise noted.

|                    |                                                                  | Speed Grade |                           |               |         |       |

|--------------------|------------------------------------------------------------------|-------------|---------------------------|---------------|---------|-------|

|                    | Decesiation -                                                    | -           | 4                         | -3            |         | 1     |

| Symbol             | Description                                                      | Min         | Max                       | Min           | Max     | Units |

| Clocks             |                                                                  |             |                           |               |         |       |

| T <sub>CH</sub>    | Clock High time                                                  | 3.0         | -                         | 4.0           | -       | ns    |

| $T_{CL}$           | Clock Low time                                                   | 3.0         | -                         | 4.0           | -       | ns    |

| Combina            | torial Delays                                                    |             | 1                         | 1             | 1       | 1     |

| T <sub>ILO</sub>   | F/G inputs to X/Y outputs                                        | -           | 1.2                       | -             | 1.6     | ns    |

| T <sub>IHO</sub>   | F/G inputs via H to X/Y outputs                                  | -           | 2.0                       | -             | 2.7     | ns    |

| T <sub>HH1O</sub>  | C inputs via H1 via H to X/Y outputs                             | -           | 1.7                       | -             | 2.2     | ns    |

| CLB Fast           | Carry Logic                                                      |             | 1                         |               | 1       |       |

| T <sub>OPCY</sub>  | Operand inputs (F1, F2, G1, G4) to C <sub>OUT</sub>              | -           | 1.7                       | -             | 2.1     | ns    |

| T <sub>ASCY</sub>  | Add/Subtract input (F3) to C <sub>OUT</sub>                      | -           | 2.8                       | -             | 3.7     | ns    |

| T <sub>INCY</sub>  | Initialization inputs (F1, F3) to C <sub>OUT</sub>               | -           | 1.2                       | -             | 1.4     | ns    |

| T <sub>SUM</sub>   | C <sub>IN</sub> through function generators to X/Y outputs       | -           | 2.0                       | -             | 2.6     | ns    |

| T <sub>BYP</sub>   | C <sub>IN</sub> to C <sub>OUT</sub> , bypass function generators | -           | 0.5                       | -             | 0.6     | ns    |

| Sequentia          | al Delays                                                        |             |                           |               |         |       |

| T <sub>CKO</sub>   | Clock K to Flip-Flop outputs Q                                   | -           | 2.1                       | -             | 2.8     | ns    |

| Setup Tin          | ne before Clock K                                                |             |                           |               |         |       |

| T <sub>ICK</sub>   | F/G inputs                                                       | 1.8         | -                         | 2.4           | -       | ns    |

| T <sub>IHCK</sub>  | F/G inputs via H                                                 | 2.9         | -                         | 3.9           | -       | ns    |

| T <sub>HH1CK</sub> | C inputs via H1 through H                                        | 2.3         | -                         | 3.3           | -       | ns    |

| T <sub>DICK</sub>  | C inputs via DIN                                                 | 1.3         | -                         | 2.0           | -       | ns    |

| T <sub>ECCK</sub>  | C inputs via EC                                                  | 2.0         | -                         | 2.6           | -       | ns    |

| T <sub>RCK</sub>   | C inputs via S/R, going Low (inactive)                           | 2.5         | -                         | 4.0           | -       | ns    |

| Hold Time          | e after Clock K                                                  |             | 1                         |               | 1       |       |

|                    | All Hold times, all devices                                      | 0.0         | -                         | 0.0           | -       | ns    |

| Set/Reset          | Direct                                                           |             |                           |               |         |       |

| T <sub>RPW</sub>   | Width (High)                                                     | 3.0         | -                         | 4.0           | -       | ns    |

| T <sub>RIO</sub>   | Delay from C inputs via S/R, going High to Q                     | -           | 3.0                       | -             | 4.0     | ns    |

| Global Se          | et/Reset                                                         |             |                           |               |         |       |

| $T_{MRW}$          | Minimum GSR pulse width                                          | 11.5        | -                         | 13.5          | -       | ns    |

| $T_{MRQ}$          | Delay from GSR input to any Q                                    | See pa      | ge 50 for T <sub>RI</sub> | RI values per | device. |       |

| F <sub>TOG</sub>   | Toggle Frequency (MHz) (for export control purposes)             | -           | 166                       | -             | 125     | MHz   |

# Spartan Family CLB RAM Synchronous (Edge-Triggered) Write Operation Guidelines (continued)

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan devices and are expressed in nanoseconds unless otherwise noted.

# **Dual-Port RAM Synchronous (Edge-Triggered) Write Operation Characteristics**

|                   |                                           |                     | -   | 4   | -    | 3   |       |

|-------------------|-------------------------------------------|---------------------|-----|-----|------|-----|-------|

| Symbol            | Dual Port RAM                             | Size <sup>(1)</sup> | Min | Max | Min  | Max | Units |

| Write Operati     | ion                                       |                     |     |     |      |     |       |

| T <sub>WCDS</sub> | Address write cycle time (clock K period) | 16x1                | 8.0 | -   | 11.6 | -   | ns    |

| T <sub>WPDS</sub> | Clock K pulse width (active edge)         | 16x1                | 4.0 | -   | 5.8  | -   | ns    |

| T <sub>ASDS</sub> | Address setup time before clock K         | 16x1                | 1.5 | -   | 2.1  | -   | ns    |

| T <sub>AHDS</sub> | Address hold time after clock K           | 16x1                | 0   | -   | 0    | -   | ns    |

| T <sub>DSDS</sub> | DIN setup time before clock K             | 16x1                | 1.5 | -   | 1.6  | -   | ns    |

| T <sub>DHDS</sub> | DIN hold time after clock K               | 16x1                | 0   | -   | 0    | -   | ns    |

| T <sub>WSDS</sub> | WE setup time before clock K              | 16x1                | 1.5 | -   | 1.6  | -   | ns    |

| T <sub>WHDS</sub> | WE hold time after clock K                | 16x1                | 0   | -   | 0    | -   | ns    |

| T <sub>WODS</sub> | Data valid after clock K                  | 16x1                | -   | 6.5 | -    | 7.0 | ns    |

#### Notes:

# Spartan Family CLB RAM Synchronous (Edge-Triggered) Write Timing

<sup>1.</sup> Read Operation timing for 16 x 1 dual-port RAM option is identical to 16 x 2 single-port RAM timing

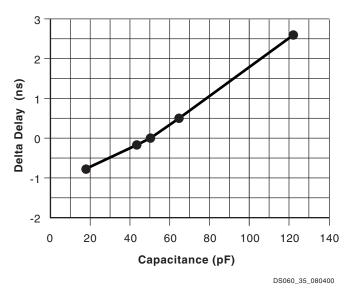

### **Capacitive Load Factor**

Figure 34 shows the relationship between I/O output delay and load capacitance. It allows a user to adjust the specified output delay if the load capacitance is different than 50 pF. For example, if the actual load capacitance is 120 pF, add 2.5 ns to the specified delay. If the load capacitance is 20 pF, subtract 0.8 ns from the specified output delay. Figure 34 is usable over the specified operating conditions of voltage and temperature and is independent of the output slew rate control.

Figure 34: Delay Factor at Various Capacitive Loads

# **Spartan Family IOB Output Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to

the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values are expressed in nanoseconds unless otherwise noted.

|                    |                                                    |             | -4   |      | _    | 3    | 1     |

|--------------------|----------------------------------------------------|-------------|------|------|------|------|-------|

| Symbol             | Description                                        | Device      | Min  | Max  | Min  | Max  | Units |

| Clocks             |                                                    |             |      |      |      |      |       |

| T <sub>CH</sub>    | Clock High                                         | All devices | 3.0  | -    | 4.0  | -    | ns    |

| T <sub>CL</sub>    | Clock Low                                          | All devices | 3.0  | -    | 4.0  | -    | ns    |

| Propagation        | Delays - TTL Outputs <sup>(1,2)</sup>              |             | J.   | .ll  | II.  |      |       |

| T <sub>OKPOF</sub> | Clock (OK) to Pad, fast                            | All devices | -    | 3.3  | -    | 4.5  | ns    |

| T <sub>OKPOS</sub> | Clock (OK to Pad, slew-rate limited                | All devices | -    | 6.9  | -    | 7.0  | ns    |

| T <sub>OPF</sub>   | Output (O) to Pad, fast                            | All devices | -    | 3.6  | -    | 4.8  | ns    |

| T <sub>OPS</sub>   | Output (O) to Pad, slew-rate limited               | All devices | -    | 7.2  | -    | 7.3  | ns    |

| T <sub>TSHZ</sub>  | 3-state to Pad High-Z (slew-rate independent)      | All devices | -    | 3.0  | -    | 3.8  | ns    |

| T <sub>TSONF</sub> | 3-state to Pad active and valid, fast              | All devices | -    | 6.0  | -    | 7.3  | ns    |

| T <sub>TSONS</sub> | 3-state to Pad active and valid, slew-rate limited | All devices | -    | 9.6  | -    | 9.8  | ns    |

| Setup and H        | lold Times                                         |             | +    | !    | ·    | 1    |       |

| T <sub>OOK</sub>   | Output (O) to clock (OK) setup time                | All devices | 2.5  | -    | 3.8  | -    | ns    |

| T <sub>OKO</sub>   | Output (O) to clock (OK) hold time                 | All devices | 0.0  | -    | 0.0  | -    | ns    |

| T <sub>ECOK</sub>  | Clock Enable (EC) to clock (OK) setup time         | All devices | 2.0  | -    | 2.7  | -    | ns    |

| T <sub>OKEC</sub>  | Clock Enable (EC) to clock (OK) hold time          | All devices | 0.0  | -    | 0.5  | -    | ns    |

| Global Set/F       | Reset                                              |             | -11  |      |      |      |       |

| $T_{MRW}$          | Minimum GSR pulse width                            | All devices | 11.5 |      | 13.5 |      | ns    |

| T <sub>RPO</sub>   | Delay from GSR input to any Pad                    | XCS05       | -    | 12.0 | -    | 15.0 | ns    |

|                    |                                                    | XCS10       | -    | 12.5 | -    | 15.7 | ns    |

|                    |                                                    | XCS20       | -    | 13.0 | -    | 16.2 | ns    |

|                    |                                                    | XCS30       | -    | 13.5 | -    | 16.9 | ns    |

|                    |                                                    | XCS40       | -    | 14.0 | -    | 17.5 | ns    |

#### Notes:

- 1. Delay adder for CMOS Outputs option (with fast slew rate option): for -3 speed grade, add 1.0 ns; for -4 speed grade, add 0.8 ns.

- 2. Delay adder for CMOS Outputs option (with slow slew rate option): for -3 speed grade, add 2.0 ns; for -4 speed grade, add 1.5 ns.

- 3. Output timing is measured at ~50% V<sub>CC</sub> threshold, with 50 pF external capacitive loads including test fixture. Slew-rate limited output rise/fall times are approximately two times longer than fast output rise/fall times.

- 4. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **Spartan-XL Family DC Characteristics Over Operating Conditions**

| Symbol            | Description                                                                |                                                                                   | Min                 | Тур. | Max                 | Units |

|-------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------|------|---------------------|-------|

| V <sub>OH</sub>   | High-level output voltage @ $I_{OH} = -4.0 \text{ mA}, V_{C}$              | <sub>C</sub> min (LVTTL)                                                          | 2.4                 | -    | -                   | V     |

|                   | High-level output voltage @ $I_{OH} = -500 \mu A$ , (LV                    | (CMOS)                                                                            | 90% V <sub>CC</sub> | -    | -                   | V     |

| V <sub>OL</sub>   | Low-level output voltage @ I <sub>OL</sub> = 12.0 mA, V <sub>CO</sub>      | ow-level output voltage @ $I_{OL}$ = 12.0 mA, $V_{CC}$ min (LVTTL) <sup>(1)</sup> |                     | -    | 0.4                 | V     |

|                   | Low-level output voltage @ I <sub>OL</sub> = 24.0 mA, V <sub>CO</sub>      | ; min (LVTTL) <sup>(2)</sup>                                                      | -                   | -    | 0.4                 | V     |

|                   | Low-level output voltage @ I <sub>OL</sub> = 1500 μA, (LVCMOS)             |                                                                                   | -                   | -    | 10% V <sub>CC</sub> | V     |

| V <sub>DR</sub>   | Data retention supply voltage (below which configuration data may be lost) |                                                                                   | 2.5                 | -    | -                   | V     |

| I <sub>CCO</sub>  | Quiescent FPGA supply current <sup>(3,4)</sup>                             | Commercial                                                                        | -                   | 0.1  | 2.5                 | mA    |

|                   |                                                                            | Industrial                                                                        | -                   | 0.1  | 5                   | mA    |

| I <sub>CCPD</sub> | Power Down FPGA supply current <sup>(3,5)</sup>                            | Commercial                                                                        | -                   | 0.1  | 2.5                 | mA    |

|                   |                                                                            | Industrial                                                                        | -                   | 0.1  | 5                   | mA    |

| IL                | Input or output leakage current                                            | 1                                                                                 | -10                 | -    | 10                  | μΑ    |

| C <sub>IN</sub>   | Input capacitance (sample tested)                                          |                                                                                   | -                   | -    | 10                  | pF    |

| I <sub>RPU</sub>  | Pad pull-up (when selected) @ V <sub>IN</sub> = 0V (sample tested)         |                                                                                   | 0.02                | -    | 0.25                | mA    |

| I <sub>RPD</sub>  | Pad pull-down (when selected) @ V <sub>IN</sub> = 3.3V (s                  | sample tested)                                                                    | 0.02                | -    | -                   | mA    |

#### Notes:

- With up to 64 pins simultaneously sinking 12 mA (default mode).

- 2. With up to 64 pins simultaneously sinking 24 mA (with 24 mA option selected).

- 3. With 5V tolerance not selected, no internal oscillators, and the FPGA configured with the Tie option.

- With no output current loads, no active input resistors, and all package pins at V<sub>CC</sub> or GND.

- 5. With PWRDWN active.

# **Supply Current Requirements During Power-On**

Spartan-XL FPGAs require that a minimum supply current  $I_{CCPO}$  be provided to the  $V_{CC}$  lines for a successful power on. If more current is available, the FPGA can consume more than  $I_{CCPO}$  min., though this cannot adversely affect reliability.

A maximum limit for  $I_{CCPO}$  is not specified. Be careful when using foldback/crowbar supplies and fuses. It is possible to control the magnitude of  $I_{CCPO}$  by limiting the supply current available to the FPGA. A current limit below the trip level will avoid inadvertently activating over-current protection circuits.

| Symbol            | Description                                                   | Min | Max | Units |

|-------------------|---------------------------------------------------------------|-----|-----|-------|

| I <sub>CCPO</sub> | Total V <sub>CC</sub> supply current required during power-on | 100 | -   | mA    |

| T <sub>CCPO</sub> | V <sub>CC</sub> ramp time <sup>(2,3)</sup>                    | -   | 50  | ms    |

#### Notes:

- 1. The  $I_{CCPO}$  requirement applies for a brief time (commonly only a few milliseconds) when  $V_{CC}$  ramps from 0 to 3.3V.

- 2. The ramp time is measured from GND to V<sub>CC</sub> max on a fully loaded board.

- V<sub>CC</sub> must not dip in the negative direction during power on.

### Spartan-XL Family Global Buffer Switching Characteristic Guidelines

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

When fewer vertical clock lines are connected, the clock distribution is faster; when multiple clock lines per column are driven from the same global clock, the delay is longer. For

more specific, more precise, and worst-case guaranteed data, reflecting the actual routing structure, use the values provided by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature).

| -                |                                         |         | Spee |     |       |

|------------------|-----------------------------------------|---------|------|-----|-------|

|                  |                                         |         | -5   | -4  |       |

| Symbol           | Description                             | Device  | Max  | Max | Units |

| T <sub>GLS</sub> | From pad through buffer, to any clock K | XCS05XL | 1.4  | 1.5 | ns    |

|                  |                                         | XCS10XL | 1.7  | 1.8 | ns    |

|                  |                                         | XCS20XL | 2.0  | 2.1 | ns    |

|                  |                                         | XCS30XL | 2.3  | 2.5 | ns    |

|                  |                                         | XCS40XL | 2.6  | 2.8 | ns    |

# Spartan-XL Family CLB RAM Synchronous (Edge-Triggered) Write Operation Guidelines

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan-XL devices and are expressed in nanoseconds unless otherwise noted.

|                   |                                           |                     |     | Speed Grade |     |     |       |  |

|-------------------|-------------------------------------------|---------------------|-----|-------------|-----|-----|-------|--|

|                   |                                           |                     | •   | -5          | -   | -4  |       |  |

| Symbol            | Single Port RAM                           | Size <sup>(1)</sup> | Min | Max         | Min | Max | Units |  |

| Write Ope         | ration                                    |                     |     |             |     | •   |       |  |

| T <sub>WCS</sub>  | Address write cycle time (clock K period) | 16x2                | 7.7 | -           | 8.4 | -   | ns    |  |

| T <sub>WCTS</sub> |                                           | 32x1                | 7.7 | -           | 8.4 | -   | ns    |  |

| T <sub>WPS</sub>  | Clock K pulse width (active edge)         | 16x2                | 3.1 | -           | 3.6 | -   | ns    |  |

| T <sub>WPTS</sub> |                                           | 32x1                | 3.1 | -           | 3.6 | -   | ns    |  |

| T <sub>ASS</sub>  | Address setup time before clock K         | 16x2                | 1.3 | -           | 1.5 | -   | ns    |  |

| T <sub>ASTS</sub> |                                           | 32x1                | 1.5 | -           | 1.7 | -   | ns    |  |

| T <sub>DSS</sub>  | DIN setup time before clock K             | 16x2                | 1.5 | -           | 1.7 | -   | ns    |  |

| T <sub>DSTS</sub> |                                           | 32x1                | 1.8 | -           | 2.1 | -   | ns    |  |

| T <sub>WSS</sub>  | WE setup time before clock K              | 16x2                | 1.4 | -           | 1.6 | -   | ns    |  |

| T <sub>WSTS</sub> |                                           | 32x1                | 1.3 | -           | 1.5 | -   | ns    |  |

|                   | All hold times after clock K              | 16x2                | 0.0 | -           | 0.0 | -   | ns    |  |

| T <sub>WOS</sub>  | Data valid after clock K                  | 32x1                | -   | 4.5         | -   | 5.3 | ns    |  |

| T <sub>WOTS</sub> |                                           | 16x2                | -   | 5.4         | -   | 6.3 | ns    |  |

| Read Ope          | ration                                    | <u> </u>            |     |             |     |     |       |  |

| T <sub>RC</sub>   | Address read cycle time                   | 16x2                | 2.6 | -           | 3.1 | -   | ns    |  |

| T <sub>RCT</sub>  |                                           | 32x1                | 3.8 | -           | 5.5 | -   | ns    |  |

| T <sub>ILO</sub>  | Data Valid after address change (no Write | 16x2                | -   | 1.0         | -   | 1.1 | ns    |  |

| T <sub>IHO</sub>  | Enable)                                   | 32x1                | -   | 1.7         | -   | 2.0 | ns    |  |

| T <sub>ICK</sub>  | Address setup time before clock K         | 16x2                | 0.6 | -           | 0.7 | -   | ns    |  |

| T <sub>IHCK</sub> |                                           | 32x1                | 1.3 | -           | 1.6 | -   | ns    |  |

| Notes:            |                                           | •                   |     | •           | •   |     |       |  |

#### Notes:

56

<sup>1.</sup> Timing for 16 x 1 RAM option is identical to 16 x 2 RAM timing.

# Spartan-XL Family CLB RAM Synchronous (Edge-Triggered) Write Operation Guidelines (cont.)

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan-XL devices and are expressed in nanoseconds unless otherwise noted.

|                                |                                           |      | -5  |     | -4  |     |       |

|--------------------------------|-------------------------------------------|------|-----|-----|-----|-----|-------|

| Symbol                         | Dual Port RAM                             | Size | Min | Max | Min | Max | Units |

| Write Operation <sup>(1)</sup> |                                           |      |     | •   |     |     |       |

| T <sub>WCDS</sub>              | Address write cycle time (clock K period) | 16x1 | 7.7 | -   | 8.4 | -   | ns    |

| T <sub>WPDS</sub>              | Clock K pulse width (active edge)         | 16x1 | 3.1 | -   | 3.6 | -   | ns    |

| T <sub>ASDS</sub>              | Address setup time before clock K         | 16x1 | 1.3 | -   | 1.5 | -   | ns    |

| T <sub>DSDS</sub>              | DIN setup time before clock K             | 16x1 | 1.7 | -   | 2.0 | -   | ns    |

| T <sub>WSDS</sub>              | WE setup time before clock K              | 16x1 | 1.4 | -   | 1.6 | -   | ns    |

|                                | All hold times after clock K              | 16x1 | 0   | -   | 0   | -   | ns    |

| T <sub>WODS</sub>              | Data valid after clock K                  | 16x1 | -   | 5.2 | -   | 6.1 | ns    |

**Dual Port**

#### Notes:

**Single Port**

# Spartan-XL Family CLB RAM Synchronous (Edge-Triggered) Write Timing

# WCLK (K) T<sub>WHS</sub> T<sub>WSS</sub> WE $\mathsf{T}_{\mathsf{DHS}}$ $T_{DSS}$ DATA IN $T_{ASS}$ TAHS **ADDRESS** TILO T<sub>ILO</sub> $\mathsf{T}_{\mathsf{WOS}}$ **DATA OUT** OLD NEW

DS060\_34\_011300

<sup>1.</sup> Read Operation timing for 16 x 1 dual-port RAM option is identical to 16 x 2 single-port RAM timing

# **Spartan-XL Family IOB Output Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to

the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values are expressed in nanoseconds unless otherwise noted.

|                    |                                               |                           | Speed Grade |      |      |      |       |

|--------------------|-----------------------------------------------|---------------------------|-------------|------|------|------|-------|

|                    |                                               |                           | -           | 5    | -    | 4    |       |

| Symbol             | Description                                   | Description Device Min Ma |             | Max  | Min  | Max  | Units |

| Propagation        | Delays                                        |                           |             |      |      |      |       |

| T <sub>OKPOF</sub> | Clock (OK) to Pad, fast                       | All devices               | -           | 3.2  | -    | 3.7  | ns    |

| T <sub>OPF</sub>   | Output (O) to Pad, fast                       | All devices               | -           | 2.5  | -    | 2.9  | ns    |

| T <sub>TSHZ</sub>  | 3-state to Pad High-Z (slew-rate independent) | All devices               | -           | 2.8  | -    | 3.3  | ns    |

| T <sub>TSONF</sub> | 3-state to Pad active and valid, fast         | All devices               | -           | 2.6  | -    | 3.0  | ns    |

| T <sub>OFPF</sub>  | Output (O) to Pad via Output MUX, fast        | All devices               | -           | 3.7  | -    | 4.4  | ns    |

| T <sub>OKFPF</sub> | Select (OK) to Pad via Output MUX, fast       | All devices               | -           | 3.3  | -    | 3.9  | ns    |

| T <sub>SLOW</sub>  | For Output SLOW option add                    | All devices               | -           | 1.5  | -    | 1.7  | ns    |

| Setup and H        | old Times                                     |                           | ,           |      |      |      |       |

| T <sub>OOK</sub>   | Output (O) to clock (OK) setup time           | All devices               | 0.5         | -    | 0.5  | -    | ns    |

| T <sub>OKO</sub>   | Output (O) to clock (OK) hold time            | All devices               | 0.0         | -    | 0.0  | -    | ns    |

| T <sub>ECOK</sub>  | Clock Enable (EC) to clock (OK) setup time    | All devices               | 0.0         | -    | 0.0  | -    | ns    |

| T <sub>OKEC</sub>  | Clock Enable (EC) to clock (OK) hold time     | All devices               | 0.1         | -    | 0.2  | -    | ns    |

| Global Set/R       | eset                                          |                           |             |      |      |      |       |

| $T_{MRW}$          | Minimum GSR pulse width                       | All devices               | 10.5        | -    | 11.5 | -    | ns    |

| T <sub>RPO</sub>   | Delay from GSR input to any Pad               | XCS05XL                   | -           | 11.9 | -    | 14.0 | ns    |

|                    |                                               | XCS10XL                   | -           | 12.4 | -    | 14.5 | ns    |

|                    |                                               | XCS20XL                   | -           | 12.9 | -    | 15.0 | ns    |

|                    |                                               | XCS30XL                   | -           | 13.9 | -    | 16.0 | ns    |

|                    |                                               | XCS40XL                   | -           | 14.9 | -    | 17.0 | ns    |

#### Notes:

<sup>1.</sup> Output timing is measured at  $\sim$ 50%  $V_{CC}$  threshold, with 50 pF external capacitive loads including test fixture. Slew-rate limited output rise/fall times are approximately two times longer than fast output rise/fall times.

<sup>2.</sup> Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

Table 18: Pin Descriptions (Continued)

| Pin Name                      | I/O<br>During<br>Config. | I/O After<br>Config.  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|--------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDWN                        | I                        | I                     | PWRDWN is an active Low input that forces the FPGA into the Power Down state and reduces power consumption. When PWRDWN is Low, the FPGA disables all I/O and initializes all flip-flops. All inputs are interpreted as Low independent of their actual level. VCC must be maintained, and the configuration data is maintained. PWRDWN halts configuration if asserted before or during configuration, and re-starts configuration when removed. When PWRDWN returns High, the FPGA becomes operational by first enabling the inputs and flip-flops and then enabling the outputs. PWRDWN has a default internal pull-up resistor. |

| User I/O Pins                 | ı                        | -                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TDO                           | Ο                        | 0                     | If boundary scan is used, this pin is the Test Data Output. If boundary scan is not used, this pin is a 3-state output without a register, after configuration is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               |                          |                       | To use this pin, place the library component TDO instead of the usual pad symbol. An output buffer must still be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI, TCK,<br>TMS              | I                        | I/O<br>or I<br>(JTAG) | If boundary scan is used, these pins are Test Data In, Test Clock, and Test Mode Select inputs respectively. They come directly from the pads, bypassing the IOBs. These pins can also be used as inputs to the CLB logic after configuration is completed.                                                                                                                                                                                                                                                                                                                                                                         |

|                               |                          |                       | If the BSCAN symbol is not placed in the design, all boundary scan functions are inhibited once configuration is completed, and these pins become user-programmable I/O. In this case, they must be called out by special library elements. To use these pins, place the library components TDI, TCK, and TMS instead of the usual pad symbols. Input or output buffers must still be used.                                                                                                                                                                                                                                         |

| HDC                           | 0                        | I/O                   | High During Configuration (HDC) is driven High until the I/O go active. It is available as a control output indicating that configuration is not yet completed. After configuration, HDC is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                            |

| LDC                           | 0                        | I/O                   | Low During Configuration (\overline{LDC}) is driven Low until the I/O go active. It is available as a control output indicating that configuration is not yet completed. After configuration, \overline{LDC} is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| ĪNIT                          | I/O                      | I/O                   | Before and during configuration, $\overline{\text{INIT}}$ is a bidirectional signal. A 1 k $\Omega$ to 10 k $\Omega$ external pull-up resistor is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                               |                          |                       | As an active Low open-drain output, $\overline{\text{INIT}}$ is held Low during the power stabilization and internal clearing of the configuration memory. As an active Low input, it can be used to hold the FPGA in the internal WAIT state before the start of configuration. Master mode devices stay in a WAIT state an additional 30 to 300 $\mu$ s after $\overline{\text{INIT}}$ has gone High.                                                                                                                                                                                                                             |

|                               |                          |                       | During configuration, a Low on this output indicates that a configuration data error has occurred. After the I/O go active, $\overline{INIT}$ is a user-programmable I/O pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PGCK1 -<br>PGCK4<br>(Spartan) | Weak<br>Pull-up          | I or I/O              | Four Primary Global inputs each drive a dedicated internal global net with short delay and minimal skew. If not used to drive a global buffer, any of these pins is a user-programmable I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                               |                          |                       | The PGCK1-PGCK4 pins drive the four Primary Global Buffers. Any input pad symbol connected directly to the input of a BUFGP symbol is automatically placed on one of these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **Device-Specific Pinout Tables**

Device-specific tables include all packages for each Spartan and Spartan-XL device. They follow the pad locations around the die, and include boundary scan register locations.

Some Spartan-XL devices are available in Pb-free package options. The Pb-free package options have the same pinouts as the standard package options.

### XCS05 and XCS05XL Device Pinouts

| XCS05/XL                                         | (4)                 |       | Bndry |

|--------------------------------------------------|---------------------|-------|-------|

| Pad Name                                         | PC84 <sup>(4)</sup> | VQ100 | Scan  |

| VCC                                              | P2                  | P89   | -     |

| I/O                                              | P3                  | P90   | 32    |

| I/O                                              | P4                  | P91   | 35    |

| I/O                                              | -                   | P92   | 38    |

| I/O                                              | -                   | P93   | 41    |

| I/O                                              | P5                  | P94   | 44    |

| I/O                                              | P6                  | P95   | 47    |

| I/O                                              | P7                  | P96   | 50    |

| I/O                                              | P8                  | P97   | 53    |

| I/O                                              | P9                  | P98   | 56    |

| I/O, SGCK1 <sup>(1)</sup> , GCK8 <sup>(2)</sup>  | P10                 | P99   | 59    |

| VCC                                              | P11                 | P100  | -     |

| GND                                              | P12                 | P1    | -     |

| I/O, PGCK1 <sup>(1)</sup> , GCK1 <sup>(2)</sup>  | P13                 | P2    | 62    |

| I/O                                              | P14                 | P3    | 65    |

| I/O, TDI                                         | P15                 | P4    | 68    |

| I/O, TCK                                         | P16                 | P5    | 71    |

| I/O, TMS                                         | P17                 | P6    | 74    |

| I/O                                              | P18                 | P7    | 77    |

| I/O                                              | -                   | P8    | 83    |

| I/O                                              | P19                 | P9    | 86    |

| I/O                                              | P20                 | P10   | 89    |

| GND                                              | P21                 | P11   | -     |

| VCC                                              | P22                 | P12   | -     |

| I/O                                              | P23                 | P13   | 92    |

| I/O                                              | P24                 | P14   | 95    |

| I/O                                              | -                   | P15   | 98    |

| I/O                                              | P25                 | P16   | 104   |

| I/O                                              | P26                 | P17   | 107   |

| I/O                                              | P27                 | P18   | 110   |

| I/O                                              | -                   | P19   | 113   |

| I/O                                              | P28                 | P20   | 116   |

| I/O, SGCK2 <sup>(1)</sup> , GCK2 <sup>(2)</sup>  | P29                 | P21   | 119   |

| Not Connected <sup>(1)</sup> , M1 <sup>(2)</sup> | P30                 | P22   | 122   |

| GND                                              | P31                 | P23   | -     |

| MODE <sup>(1)</sup> , M0 <sup>(2)</sup>          | P32                 | P24   | 125   |

| VCC                                              | P33                 | P25   | -     |

| 1                                                | 1                   |       | I.    |

### **XCS05 and XCS05XL Device Pinouts**

| XCS05/XL<br>Pad Name                            | PC84 <sup>(4)</sup> | VQ100 | Bndry<br>Scan      |

|-------------------------------------------------|---------------------|-------|--------------------|

| Not Connected <sup>(1)</sup> ,                  | P34                 | P26   | 126 <sup>(1)</sup> |

| PWRDWN <sup>(2)</sup>                           |                     | F20   |                    |

| I/O, PGCK2 <sup>(1)</sup> , GCK3 <sup>(2)</sup> | P35                 | P27   | 127 <sup>(3)</sup> |

| I/O (HDC)                                       | P36                 | P28   | 130 <sup>(3)</sup> |

| I/O                                             | -                   | P29   | 133 <sup>(3)</sup> |

| I/O (LDC)                                       | P37                 | P30   | 136 <sup>(3)</sup> |

| I/O                                             | P38                 | P31   | 139 <sup>(3)</sup> |

| I/O                                             | P39                 | P32   | 142 <sup>(3)</sup> |

| I/O                                             | -                   | P33   | 145 <sup>(3)</sup> |

| I/O                                             | -                   | P34   | 148 <sup>(3)</sup> |

| I/O                                             | P40                 | P35   | 151 <sup>(3)</sup> |

| I/O (ĪNĪT)                                      | P41                 | P36   | 154 <sup>(3)</sup> |

| VCC                                             | P42                 | P37   | -                  |

| GND                                             | P43                 | P38   | -                  |

| I/O                                             | P44                 | P39   | 157 <sup>(3)</sup> |

| I/O                                             | P45                 | P40   | 160 <sup>(3)</sup> |

| I/O                                             | -                   | P41   | 163 <sup>(3)</sup> |

| I/O                                             | -                   | P42   | 166 <sup>(3)</sup> |

| I/O                                             | P46                 | P43   | 169 <sup>(3)</sup> |

| I/O                                             | P47                 | P44   | 172 <sup>(3)</sup> |

| I/O                                             | P48                 | P45   | 175 <sup>(3)</sup> |

| I/O                                             | P49                 | P46   | 178 <sup>(3)</sup> |

| I/O                                             | P50                 | P47   | 181 <sup>(3)</sup> |

| I/O, SGCK3 <sup>(1)</sup> , GCK4 <sup>(2)</sup> | P51                 | P48   | 184 <sup>(3)</sup> |

| GND                                             | P52                 | P49   | -                  |

| DONE                                            | P53                 | P50   | -                  |

| VCC                                             | P54                 | P51   | -                  |

| PROGRAM                                         | P55                 | P52   | - (0)              |

| I/O (D7 <sup>(2)</sup> )                        | P56                 | P53   | 187 <sup>(3)</sup> |

| I/O, PGCK3 <sup>(1)</sup> , GCK5 <sup>(2)</sup> | P57                 | P54   | 190 <sup>(3)</sup> |

| I/O (D6 <sup>(2)</sup> )                        | P58                 | P55   | 193 <sup>(3)</sup> |

| I/O                                             | -                   | P56   | 196 <sup>(3)</sup> |

| I/O (D5 <sup>(2)</sup> )                        | P59                 | P57   | 199 <sup>(3)</sup> |

| I/O                                             | P60                 | P58   | 202 <sup>(3)</sup> |

| I/O                                             | -                   | P59   | 205 <sup>(3)</sup> |

| I/O                                             | -                   | P60   | 208 <sup>(3)</sup> |

| I/O (D4 <sup>(2)</sup> )                        | P61                 | P61   | 211(3)             |

| 1/0                                             | P62                 | P62   | 214 <sup>(3)</sup> |

| VCC                                             | P63                 | P63   | -                  |

| GND                                             | P64                 | P64   | - (2)              |

| I/O (D3 <sup>(2)</sup> )                        | P65                 | P65   | 217 <sup>(3)</sup> |

| 1/0                                             | P66                 | P66   | 220(3)             |

| 1/0                                             | -                   | P67   | 223 <sup>(3)</sup> |

| I/O (D2 <sup>(2)</sup> )                        | P67                 | P68   | 229(3)             |

| 1/0                                             | P68                 | P69   | 232 <sup>(3)</sup> |

| I/O (D1 <sup>(2)</sup> )                        | P69                 | P70   | 235 <sup>(3)</sup> |

# **XCS20 and XCS20XL Device Pinouts**

| XCS20/XL<br>Pad Name                                     | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |

|----------------------------------------------------------|-------|------------------------|-------|-------|--------------------|

| I/O                                                      | -     | F4                     | P13   | P21   | 170                |

| I/O                                                      | P8    | F3                     | P14   | P22   | 173                |

| I/O                                                      | P9    | F2                     | P15   | P23   | 176                |

| I/O                                                      | P10   | F1                     | P16   | P24   | 179                |

| GND                                                      | P11   | G2                     | P17   | P25   | -                  |

| VCC                                                      | P12   | G1                     | P18   | P26   | -                  |

| I/O                                                      | P13   | G3                     | P19   | P27   | 182                |

| I/O                                                      | P14   | G4                     | P20   | P28   | 185                |

| I/O                                                      | P15   | H1                     | P21   | P29   | 188                |

| I/O                                                      | -     | H2                     | P22   | P30   | 191                |