Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 576                                                          |

| Number of Logic Elements/Cells | 1368                                                         |

| Total RAM Bits                 | 18432                                                        |

| Number of I/O                  | 113                                                          |

| Number of Gates                | 30000                                                        |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 144-LQFP                                                     |

| Supplier Device Package        | 144-TQFP (20x20)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcs30xl-4tqg144c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

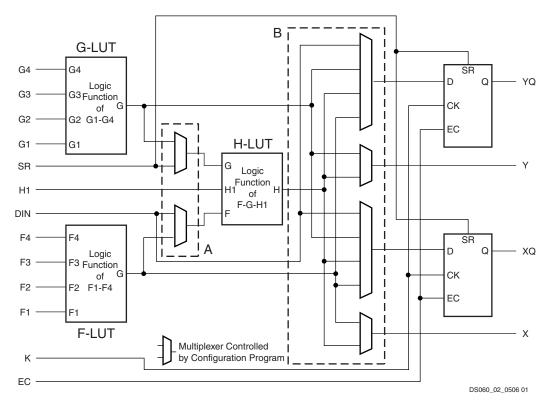

Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)

A CLB can implement any of the following functions:

Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variables

**Note:** When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.

- Any single function of five variables

- Any function of four variables together with some functions of six variables

- · Some functions of up to nine variables.

Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed.

The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently. This flexibility improves cell usage.

#### Flip-Flops

Each CLB contains two flip-flops that can be used to register (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.

The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in **Global Signals: GSR and GTS**, page 20.

#### Latches (Spartan-XL Family Only)

The Spartan-XL family CLB storage elements can also be configured as latches. The two latches have common clock (K) and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.

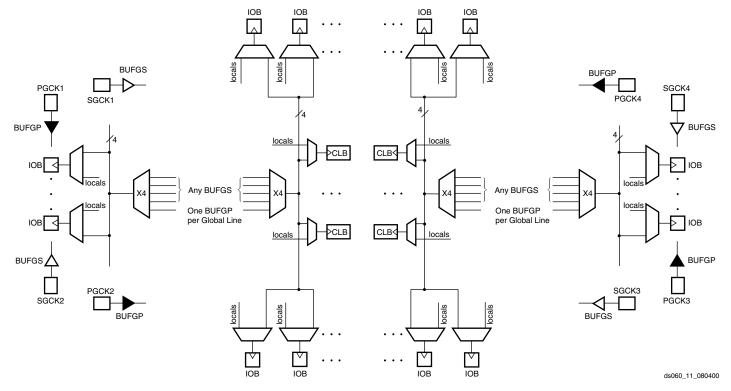

Figure 11: 5V Spartan Family Global Net Distribution

The four Primary Global buffers offer the shortest delay and negligible skew. Four Secondary Global buffers have slightly longer delay and slightly more skew due to potentially heavier loading, but offer greater flexibility when used to drive non-clock CLB inputs. The eight Global Low-Skew buffers in the Spartan-XL devices combine short delay, negligible skew, and flexibility.

The Primary Global buffers must be driven by the semi-dedicated pads (PGCK1-4). The Secondary Global buffers can be sourced by either semi-dedicated pads (SGCK1-4) or internal nets. Each corner of the device has one Primary buffer and one Secondary buffer. The Spartan-XL family has eight global low-skew buffers, two in each corner. All can be sourced by either semi-dedicated pads (GCK1-8) or internal nets.

Using the library symbol called BUFG results in the software choosing the appropriate clock buffer, based on the timing requirements of the design. A global buffer should be specified for all timing-sensitive global signal distribution. To use a global buffer, place a BUFGP (primary buffer), BUFGS (secondary buffer), BUFGLS (Spartan-XL family global low-skew buffer), or BUFG (any buffer type) element in a schematic or in HDL code.

# **Advanced Features Description**

#### **Distributed RAM**

Optional modes for each CLB allow the function generators (F-LUT and G-LUT) to be used as Random Access Memory (RAM).

Read and write operations are significantly faster for this on-chip RAM than for off-chip implementations. This speed advantage is due to the relatively short signal propagation delays within the FPGA.

#### **Memory Configuration Overview**

There are two available memory configuration modes: single-port RAM and dual-port RAM. For both these modes, write operations are synchronous (edge-triggered), while read operations are asynchronous. In the single-port mode, a single CLB can be configured as either a 16 x 1, (16 x 1) x 2, or 32 x 1 RAM array. In the dual-port mode, a single CLB can be configured only as one 16 x 1 RAM array. The different CLB memory configurations are summarized in Table 8. Any of these possibilities can be individually programmed into a Spartan/XL FPGA CLB.

Table 8: CLB Memory Configurations

| Mode        | 16 x 1 | (16 x 1) x 2 | 32 x 1 |

|-------------|--------|--------------|--------|

| Single-Port | √      | √            | V      |

| Dual-Port   | √      | _            | _      |

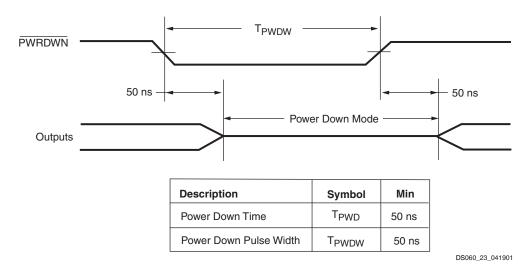

Figure 23: PWRDWN Pulse Timing

Power-down retains the configuration, but loses all data stored in the device flip-flops. All inputs are interpreted as Low, but the internal combinatorial logic is fully functional. Make sure that the combination of all inputs Low and all flip-flops set or reset in your design will not generate internal oscillations, or create permanent bus contention by activating internal bus drivers with conflicting data onto the same long line.

During configuration, the PWRDWN pin must be High. If the Power Down state is entered before or during configuration, the device will restart configuration once the PWRDWN signal is removed. Note that the configuration pins are affected by Power Down and may not reflect their normal function. If there is an external pull-up resistor on the DONE pin, it will be High during Power Down even if the device is not yet configured. Similarly, if PWRDWN is asserted before configuration is completed, the INIT pin will not indicate status information.

Note that the PWRDWN pin is not part of the Boundary Scan chain. Therefore, the Spartan-XL family has a separate set of BSDL files than the 5V Spartan family. Boundary scan logic is not usable during Power Down.

# **Configuration and Test**

Configuration is the process of loading design-specific programming data into one or more FPGAs to define the functional operation of the internal blocks and their interconnections. This is somewhat like loading the command registers of a programmable peripheral chip. Spartan/XL devices use several hundred bits of configuration data per CLB and its associated interconnects. Each configuration bit defines the state of a static memory cell

that controls either a function look-up table bit, a multiplexer input, or an interconnect pass transistor. The Xilinx development system translates the design into a netlist file. It automatically partitions, places and routes the logic and generates the configuration data in PROM format.

## **Configuration Mode Control**

5V Spartan devices have two configuration modes.

- MODE = 1 sets Slave Serial mode

- MODE = 0 sets Master Serial mode

3V Spartan-XL devices have three configuration modes.

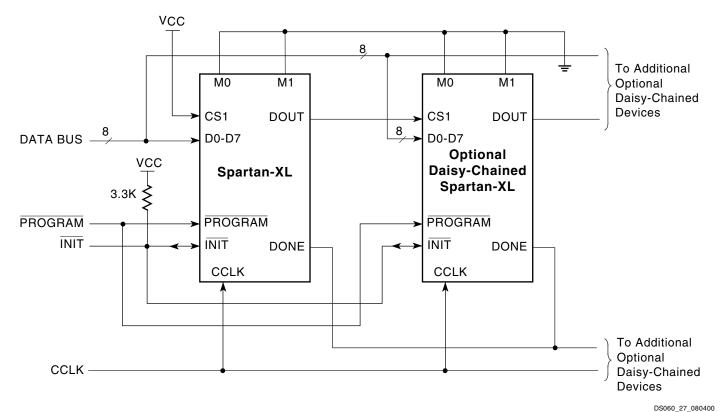

- M1/M0 = 11 sets Slave Serial mode

- M1/M0 = 10 sets Master Serial mode

- M1/M0 = 0X sets Express mode

In addition to these modes, the device can be configured through the Boundary Scan logic (See "Configuration Through the Boundary Scan Pins" on page 37.).

The Mode pins are sampled prior to starting configuration to determine the configuration mode. After configuration, these pin are unused. The Mode pins have a weak pull-up resistor turned on during configuration. With the Mode pins High, Slave Serial mode is selected, which is the most popular configuration mode. Therefore, for the most common configuration mode, the Mode pins can be left unconnected. If the Master Serial mode is desired, the MODE/M0 pin should be connected directly to GND, or through a pull-down resistor of 1 K $\Omega$  or less.

During configuration, some of the I/O pins are used temporarily for the configuration process. All pins used during con-

to the DONE pin. User I/Os for each device become active after the DONE pin for that device goes High. (The exact timing is determined by development system options.) Since the DONE pin is open-drain and does not drive a High value, tying the DONE pins of all devices together prevents all devices in the chain from going High until the last device

in the chain has completed its configuration cycle. If the DONE pin of a device is left unconnected, the device becomes active as soon as that device has been configured. Only devices supporting Express mode can be used to form an Express mode daisy chain.

Figure 27: Express Mode Circuit Diagram

----

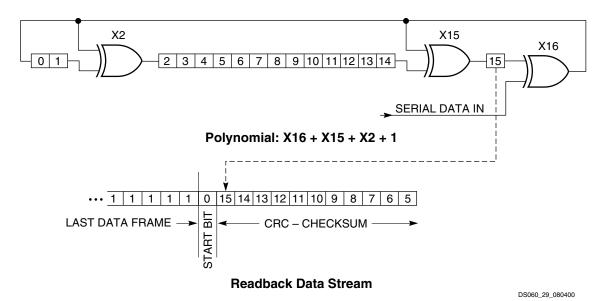

Figure 29: Circuit for Generating CRC-16

## **Configuration Sequence**

There are four major steps in the Spartan/XL FPGA power-up configuration sequence.

- · Configuration Memory Clear

- Initialization

- Configuration

- Start-up

The full process is illustrated in Figure 30.

## Configuration Memory Clear

When power is first applied or is reapplied to an FPGA, an internal circuit forces initialization of the configuration logic. When  $V_{CC}$  reaches an operational level, and the circuit passes the write and read test of a sample pair of configuration bits, a time delay is started. This time delay is nominally 16 ms. The delay is four times as long when in Master Serial Mode to allow ample time for all slaves to reach a stable  $V_{CC}$ . When all  $\overline{\text{INIT}}$  pins are tied together, as recommended, the longest delay takes precedence. Therefore, devices with different time delays can easily be mixed and matched in a daisy chain.

This delay is applied only on power-up. It is not applied when reconfiguring an FPGA by pulsing the PROGRAM pin

Low. During this time delay, or as long as the PROGRAM input is asserted, the configuration logic is held in a Configuration Memory Clear state. The configuration-memory frames are consecutively initialized, using the internal oscillator.

At the end of each complete pass through the frame addressing, the power-on time-out delay circuitry and the level of the  $\overline{PROGRAM}$  pin are tested. If neither is asserted, the logic initiates one additional clearing of the configuration frames and then tests the  $\overline{INIT}$  input.

#### Initialization

During initialization and configuration, user pins HDC,  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE provide status outputs for the system interface. The outputs  $\overline{\text{LDC}}$ ,  $\overline{\text{INIT}}$  and DONE are held Low and HDC is held High starting at the initial application of power.

The open drain  $\overline{\text{INIT}}$  pin is released after the final initialization pass through the frame addresses. There is a deliberate delay before a Master-mode device recognizes an inactive  $\overline{\text{INIT}}$ . Two internal clocks after the  $\overline{\text{INIT}}$  pin is recognized as High, the device samples the MODE pin to determine the configuration mode. The appropriate interface lines become active and the configuration preamble and data can be loaded.

to wait after completing the configuration memory clear operation. When  $\overline{INIT}$  is no longer held Low externally, the device determines its configuration mode by capturing the state of the Mode pins, and is ready to start the configuration process. A master device waits up to an additional 300  $\mu s$  to make sure that any slaves in the optional daisy chain have seen that  $\overline{INIT}$  is High.

For more details on Configuration, refer to the Xilinx Application Note "FPGA Configuration Guidelines" (XAPP090).

#### Start-Up

Start-up is the transition from the configuration process to the intended user operation. This transition involves a change from one clock source to another, and a change from interfacing parallel or serial configuration data where most outputs are 3-stated, to normal operation with I/O pins active in the user system. Start-up must make sure that the user logic 'wakes up' gracefully, that the outputs become active without causing contention with the configuration signals, and that the internal flip-flops are released from the Global Set/Reset (GSR) at the right time.

#### **Start-Up Initiation**

Two conditions have to be met in order for the start-up sequence to begin:

- The chip's internal memory must be full, and

- The configuration length count must be met, exactly.

In all configuration modes except Express mode, Spartan/XL devices read the expected length count from the bitstream and store it in an internal register. The length count varies according to the number of devices and the composition of the daisy chain. Each device also counts the number of CCLKs during configuration.

In Express mode, there is no length count. The start-up sequence for each device begins when the device has received its quota of configuration data. Wiring the DONE pins of several devices together delays start-up of all devices until all are fully configured.

#### **Start-Up Events**

The device can be programmed to control three start-up events.

- The release of the open-drain DONE output

- The termination of the Global Three-State and the change of configuration-related pins to the user function, activating all IOBs.

- The termination of the Global Set/Reset initialization of all CLB and IOB storage elements.

Figure 31 describes start-up timing in detail. The three events — DONE going High, the internal GSR being de-activated, and the user I/O going active — can all occur in any arbitrary sequence. This relative timing is selected by options in the bitstream generation software. Heavy lines in Figure 31 show the default timing. The thin lines indicate all other possible timing options. The start-up logic must be clocked until the "F" (Finished) state is reached.

The default option, and the most practical one, is for DONE to go High first, disconnecting the configuration data source and avoiding any contention when the I/Os become active one clock later. GSR is then released another clock period later to make sure that user operation starts from stable internal conditions. This is the most common sequence, shown with heavy lines in Figure 31, but the designer can modify it to meet particular requirements.

#### Start-Up Clock

Normally, the start-up sequence is controlled by the internal device oscillator (CCLK), which is asynchronous to the system clock. As a configuration option, they can be triggered by an on-chip user net called UCLK. This user net can be accessed by placing the STARTUP library symbol, and the start-up modes are known as UCLK\_NOSYNC or UCLK\_SYNC. This allows the device to wake up in synchronism with the user system.

#### **DONE Pin**

Note that DONE is an open-drain output and does not go High unless an internal pull-up is activated or an external pull-up is attached. The internal pull-up is activated as the default by the bitstream generation software.

The DONE pin can also be wire-ANDed with DONE pins of other FPGAs or with other external signals, and can then be used as input to the start-up control logic. This is called "Start-up Timing Synchronous to Done In" and is selected by either CCLK\_SYNC or UCLK\_SYNC. When DONE is not used as an input, the operation is called "Start-up Timing Not Synchronous to DONE In," and is selected by either CCLK\_NOSYNC or UCLK\_NOSYNC. Express mode configuration always uses either CCLK\_SYNC or UCLK\_SYNC timing, while the other configuration modes can use any of the four timing sequences.

When the UCLK\_SYNC option is enabled, the user can externally hold the open-drain DONE output Low, and thus stall all further progress in the start-up sequence until DONE is released and has gone High. This option can be used to force synchronization of several FPGAs to a common user clock, or to guarantee that all devices are successfully configured before any I/Os go active.

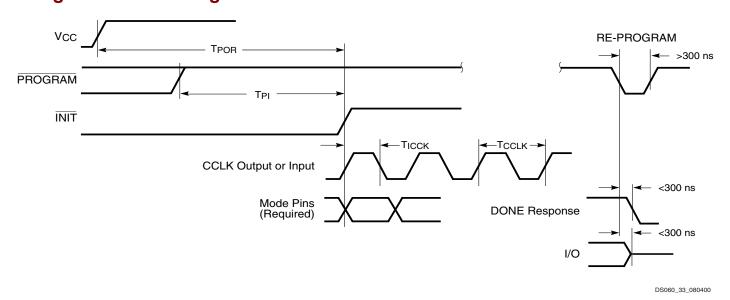

# **Configuration Switching Characteristics**

## **Master Mode**

| Symbol            | Description                | Min | Max  | Units             |

|-------------------|----------------------------|-----|------|-------------------|

| T <sub>POR</sub>  | Power-on reset             | 40  | 130  | ms                |

| T <sub>PI</sub>   | Program Latency            | 30  | 200  | μs per CLB column |

| T <sub>ICCK</sub> | CCLK (output) delay        | 40  | 250  | μs                |

| T <sub>CCLK</sub> | CCLK (output) period, slow | 640 | 2000 | ns                |

| T <sub>CCLK</sub> | CCLK (output) period, fast | 100 | 250  | ns                |

## **Slave Mode**

| Symbol            | Description                    | Min | Max | Units             |

|-------------------|--------------------------------|-----|-----|-------------------|

| T <sub>POR</sub>  | Power-on reset                 | 10  | 33  | ms                |

| T <sub>Pl</sub>   | Program latency                | 30  | 200 | μs per CLB column |

| T <sub>ICCK</sub> | CCLK (input) delay (required)  | 4   | -   | μs                |

| T <sub>CCLK</sub> | CCLK (input) period (required) | 80  | -   | ns                |

# **Spartan Family Detailed Specifications**

#### **Definition of Terms**

In the following tables, some specifications may be designated as Advance or Preliminary. These terms are defined as follows:

**Advance:** Initial estimates based on simulation and/or extrapolation from other speed grades, devices, or families. Values are subject to change. Use as estimates, not for production.

Preliminary: Based on preliminary characterization. Further changes are not expected.

Unmarked: Specifications not identified as either Advance or Preliminary are to be considered Final.

Notwithstanding the definition of the above terms, all specifications are subject to change without notice.

Except for pin-to-pin input and output parameters, the AC parameter delay specifications included in this document are derived from measuring internal test patterns. All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications.

## Spartan Family Absolute Maximum Ratings(1)

| Symbol           | Description                                        | Value                        | Units |    |

|------------------|----------------------------------------------------|------------------------------|-------|----|

| V <sub>CC</sub>  | Supply voltage relative to GND                     | -0.5 to +7.0                 | V     |    |

| V <sub>IN</sub>  | Input voltage relative to GND <sup>(2,3)</sup>     | -0.5 to V <sub>CC</sub> +0.5 | V     |    |

| V <sub>TS</sub>  | Voltage applied to 3-state output <sup>(2,3)</sup> | -0.5 to V <sub>CC</sub> +0.5 | V     |    |

| T <sub>STG</sub> | Storage temperature (ambient)                      | -65 to +150                  | °C    |    |

| T <sub>J</sub>   | Junction temperature                               | Plastic packages             | +125  | °C |

#### Notes:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

- 2. Maximum DC overshoot (above V<sub>CC</sub>) or undershoot (below GND) must be limited to either 0.5V or 10 mA, whichever is easier to achieve.

- 3. Maximum AC (during transitions) conditions are as follows; the device pins may undershoot to -2.0V or overshoot to +7.0V, provided this overshoot or undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

- 4. For soldering guidelines, see the Package Information on the Xilinx website.

## **Spartan Family Recommended Operating Conditions**

| Symbol          | Description                                                                                 | Min         | Max  | Units    |          |

|-----------------|---------------------------------------------------------------------------------------------|-------------|------|----------|----------|

| V <sub>CC</sub> | Supply voltage relative to GND, T <sub>J</sub> = 0°C to +85°C                               | Commercial  | 4.75 | 5.25     | V        |

|                 | Supply voltage relative to GND, $T_J = -40^{\circ}\text{C}$ to $+100^{\circ}\text{C}^{(1)}$ | Industrial  | 4.5  | 5.5      | V        |

| V <sub>IH</sub> | High-level input voltage <sup>(2)</sup>                                                     | TTL inputs  | 2.0  | $V_{CC}$ | V        |

|                 |                                                                                             | CMOS inputs | 70%  | 100%     | $V_{CC}$ |

| V <sub>IL</sub> | Low-level input voltage <sup>(2)</sup>                                                      | TTL inputs  | 0    | 8.0      | V        |

|                 |                                                                                             | CMOS inputs | 0    | 20%      | $V_{CC}$ |

| T <sub>IN</sub> | Input signal transition time                                                                | 1           | -    | 250      | ns       |

#### Notes:

- At junction temperatures above those listed as Recommended Operating Conditions, all delay parameters increase by 0.35% per °C.

- 2. Input and output measurement thresholds are: 1.5V for TTL and 2.5V for CMOS.

## **Spartan Family CLB Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Spartan devices and expressed in nanoseconds unless otherwise noted.

|                    |                                                                  | Speed Grade |                           |               |         |       |

|--------------------|------------------------------------------------------------------|-------------|---------------------------|---------------|---------|-------|

|                    | Decesiation -                                                    | -           | 4                         | -3            |         | 1     |

| Symbol             | Description                                                      | Min         | Max                       | Min           | Max     | Units |

| Clocks             |                                                                  |             |                           |               |         |       |

| T <sub>CH</sub>    | Clock High time                                                  | 3.0         | -                         | 4.0           | -       | ns    |

| $T_{CL}$           | Clock Low time                                                   | 3.0         | -                         | 4.0           | -       | ns    |

| Combina            | torial Delays                                                    |             | 1                         | 1             | 1       | 1     |

| T <sub>ILO</sub>   | F/G inputs to X/Y outputs                                        | -           | 1.2                       | -             | 1.6     | ns    |

| T <sub>IHO</sub>   | F/G inputs via H to X/Y outputs                                  | -           | 2.0                       | -             | 2.7     | ns    |

| T <sub>HH1O</sub>  | C inputs via H1 via H to X/Y outputs                             | -           | 1.7                       | -             | 2.2     | ns    |

| CLB Fast           | Carry Logic                                                      |             | 1                         |               | 1       |       |

| T <sub>OPCY</sub>  | Operand inputs (F1, F2, G1, G4) to C <sub>OUT</sub>              | -           | 1.7                       | -             | 2.1     | ns    |

| T <sub>ASCY</sub>  | Add/Subtract input (F3) to C <sub>OUT</sub>                      | -           | 2.8                       | -             | 3.7     | ns    |

| T <sub>INCY</sub>  | Initialization inputs (F1, F3) to C <sub>OUT</sub>               | -           | 1.2                       | -             | 1.4     | ns    |

| T <sub>SUM</sub>   | C <sub>IN</sub> through function generators to X/Y outputs       | -           | 2.0                       | -             | 2.6     | ns    |

| T <sub>BYP</sub>   | C <sub>IN</sub> to C <sub>OUT</sub> , bypass function generators | -           | 0.5                       | -             | 0.6     | ns    |

| Sequentia          | al Delays                                                        |             |                           |               |         |       |

| T <sub>CKO</sub>   | Clock K to Flip-Flop outputs Q                                   | -           | 2.1                       | -             | 2.8     | ns    |

| Setup Tin          | ne before Clock K                                                |             |                           |               |         |       |

| T <sub>ICK</sub>   | F/G inputs                                                       | 1.8         | -                         | 2.4           | -       | ns    |

| T <sub>IHCK</sub>  | F/G inputs via H                                                 | 2.9         | -                         | 3.9           | -       | ns    |

| T <sub>HH1CK</sub> | C inputs via H1 through H                                        | 2.3         | -                         | 3.3           | -       | ns    |

| T <sub>DICK</sub>  | C inputs via DIN                                                 | 1.3         | -                         | 2.0           | -       | ns    |

| T <sub>ECCK</sub>  | C inputs via EC                                                  | 2.0         | -                         | 2.6           | -       | ns    |

| T <sub>RCK</sub>   | C inputs via S/R, going Low (inactive)                           | 2.5         | -                         | 4.0           | -       | ns    |

| Hold Time          | e after Clock K                                                  |             | 1                         |               |         |       |

|                    | All Hold times, all devices                                      | 0.0         | -                         | 0.0           | -       | ns    |

| Set/Reset          | Direct                                                           |             |                           |               |         |       |

| T <sub>RPW</sub>   | Width (High)                                                     | 3.0         | -                         | 4.0           | -       | ns    |

| T <sub>RIO</sub>   | Delay from C inputs via S/R, going High to Q                     | -           | 3.0                       | -             | 4.0     | ns    |

| Global Se          | et/Reset                                                         |             |                           |               |         |       |

| $T_{MRW}$          | Minimum GSR pulse width                                          | 11.5        | -                         | 13.5          | -       | ns    |

| $T_{MRQ}$          | Delay from GSR input to any Q                                    | See pa      | ge 50 for T <sub>RI</sub> | RI values per | device. |       |

| F <sub>TOG</sub>   | Toggle Frequency (MHz) (for export control purposes)             | -           | 166                       | -             | 125     | MHz   |

## **Spartan Family Pin-to-Pin Output Parameter Guidelines**

All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case operating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading. For more specific, more pre-

cise, and worst-case guaranteed data, reflecting the actual routing structure, use the values provided by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report.

## Spartan Family Output Flip-Flop, Clock-to-Out

|                     |                                       |             | Speed Grade |      |       |

|---------------------|---------------------------------------|-------------|-------------|------|-------|

|                     |                                       |             | -4          | -3   |       |

| Symbol              | Description                           | Device      | Max         | Max  | Units |

| Global Pri          | mary Clock to TTL Output using OFF    |             |             | '    | '     |

| T <sub>ICKOF</sub>  | Fast                                  | XCS05       | 5.3         | 8.7  | ns    |

|                     |                                       | XCS10       | 5.7         | 9.1  | ns    |

|                     |                                       | XCS20       | 6.1         | 9.3  | ns    |

|                     |                                       | XCS30       | 6.5         | 9.4  | ns    |

|                     |                                       | XCS40       | 6.8         | 10.2 | ns    |

| T <sub>ICKO</sub>   | Slew-rate limited                     | XCS05       | 9.0         | 11.5 | ns    |

|                     |                                       | XCS10       | 9.4         | 12.0 | ns    |

|                     |                                       | XCS20       | 9.8         | 12.2 | ns    |

|                     |                                       | XCS30       | 10.2        | 12.8 | ns    |

|                     |                                       | XCS40       | 10.5        | 12.8 | ns    |

| Global Sec          | condary Clock to TTL Output using OFF |             |             |      |       |

| T <sub>ICKSOF</sub> | Fast                                  | XCS05       | 5.8         | 9.2  | ns    |

|                     |                                       | XCS10       | 6.2         | 9.6  | ns    |

|                     |                                       | XCS20       | 6.6         | 9.8  | ns    |

|                     |                                       | XCS30       | 7.0         | 9.9  | ns    |

|                     |                                       | XCS40       | 7.3         | 10.7 | ns    |

| T <sub>ICKSO</sub>  | Slew-rate limited                     | XCS05       | 9.5         | 12.0 | ns    |

|                     |                                       | XCS10       | 9.9         | 12.5 | ns    |

|                     |                                       | XCS20       | 10.3        | 12.7 | ns    |

|                     |                                       | XCS30       | 10.7        | 13.2 | ns    |

|                     |                                       | XCS40       | 11.0        | 14.3 | ns    |

| Delay Add           | er for CMOS Outputs Option            |             |             | 1    | 1     |

| T <sub>CMOSOF</sub> | Fast                                  | All devices | 0.8         | 1.0  | ns    |

| $T_{CMOSO}$         | Slew-rate limited                     | All devices | 1.5         | 2.0  | ns    |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

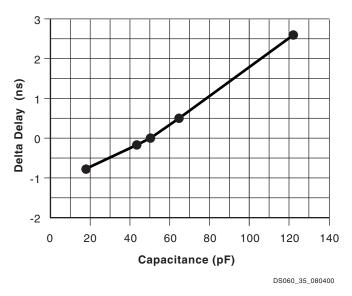

- Output timing is measured at ~50% V<sub>CC</sub> threshold with 50 pF external capacitive load. For different loads, see Figure 34.

- 3. OFF = Output Flip-Flop

#### **Capacitive Load Factor**

Figure 34 shows the relationship between I/O output delay and load capacitance. It allows a user to adjust the specified output delay if the load capacitance is different than 50 pF. For example, if the actual load capacitance is 120 pF, add 2.5 ns to the specified delay. If the load capacitance is 20 pF, subtract 0.8 ns from the specified output delay. Figure 34 is usable over the specified operating conditions of voltage and temperature and is independent of the output slew rate control.

Figure 34: Delay Factor at Various Capacitive Loads

## Spartan-XL Family Pin-to-Pin Input Parameter Guidelines

All devices are 100% functionally tested. Pin-to-pin timing parameters are derived from measuring external and internal test patterns and are guaranteed over worst-case oper-

ating conditions (supply voltage and junction temperature). Listed below are representative values for typical pin locations and normal clock loading.

#### Spartan-XL Family Setup and Hold

|                                                   |             |         | Speed   |         |       |  |  |

|---------------------------------------------------|-------------|---------|---------|---------|-------|--|--|

|                                                   |             |         | -5      | -4      |       |  |  |

| Symbol                                            | Description | Device  | Max     | Max     | Units |  |  |

| Input Setup/Hold Times Using Global Clock and IFF |             |         |         |         |       |  |  |

| T <sub>SUF</sub> /T <sub>HF</sub>                 | No Delay    | XCS05XL | 1.1/2.0 | 1.6/2.6 | ns    |  |  |

|                                                   |             | XCS10XL | 1.0/2.2 | 1.5/2.8 | ns    |  |  |

|                                                   |             | XCS20XL | 0.9/2.4 | 1.4/3.0 | ns    |  |  |

|                                                   |             | XCS30XL | 0.8/2.6 | 1.3/3.2 | ns    |  |  |

|                                                   |             | XCS40XL | 0.7/2.8 | 1.2/3.4 | ns    |  |  |

| T <sub>SU</sub> /T <sub>H</sub>                   | Full Delay  | XCS05XL | 3.9/0.0 | 5.1/0.0 | ns    |  |  |

|                                                   |             | XCS10XL | 4.1/0.0 | 5.3/0.0 | ns    |  |  |

|                                                   |             | XCS20XL | 4.3/0.0 | 5.5/0.0 | ns    |  |  |

|                                                   |             | XCS30XL | 4.5/0.0 | 5.7/0.0 | ns    |  |  |

|                                                   |             | XCS40XL | 4.7/0.0 | 5.9/0.0 | ns    |  |  |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured with the fastest route and the lightest load. Hold time is measured using the furthest distance and a reference load of one clock pin per IOB/CLB.

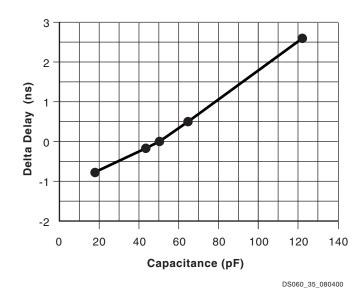

#### **Capacitive Load Factor**

Figure 35 shows the relationship between I/O output delay and load capacitance. It allows a user to adjust the specified output delay if the load capacitance is different than 50 pF. For example, if the actual load capacitance is 120 pF, add 2.5 ns to the specified delay. If the load capacitance is 20 pF, subtract 0.8 ns from the specified output delay. Figure 35 is usable over the specified operating conditions of voltage and temperature and is independent of the output slew rate control.

Figure 35: Delay Factor at Various Capacitive Loads

# **Pin Descriptions**

There are three types of pins in the Spartan/XL devices:

- · Permanently dedicated pins

- User I/O pins that can have special functions

- Unrestricted user-programmable I/O pins.

Before and during configuration, all outputs not used for the configuration process are 3-stated with the I/O pull-up resistor network activated. After configuration, if an IOB is unused it is configured as an input with the I/O pull-up resistor network remaining activated.

Any user I/O can be configured to drive the Global Set/Reset net GSR or the global three-state net GTS. See **Global Signals: GSR and GTS**, page 20 for more information.

Device pins for Spartan/XL devices are described in Table 18.

Some Spartan-XL devices are available in Pb-free package options. The Pb-free package options have the same pinouts as the standard package options.

Table 18: Pin Descriptions

| Pin Name               | I/O<br>During<br>Config. | I/O After<br>Config. | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|--------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permanently D          | Dedicated P              | ins                  |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CC</sub>        | Х                        | Х                    | Eight or more (depending on package) connections to the nominal +5V supply voltage (+3.3V for Spartan-XL devices). All must be connected, and each must be decoupled with a 0.01 –0.1 $\mu$ F capacitor to Ground.                                                                                                                                                                                                                        |

| GND                    | Х                        | Х                    | Eight or more (depending on package type) connections to Ground. All must be connected.                                                                                                                                                                                                                                                                                                                                                   |

| CCLK                   | I or O                   | I                    | During configuration, Configuration Clock (CCLK) is an output in Master mode and is an input in Slave mode. After configuration, CCLK has a weak pull-up resistor and can be selected as the Readback Clock. There is no CCLK High or Low time restriction on Spartan/XL devices, except during Readback. See Violating the Maximum High and Low Time Specification for the Readback Clock, page 39 for an explanation of this exception. |

| DONE                   | I/O                      | 0                    | DONE is a bidirectional signal with an optional internal pull-up resistor. As an open-drain output, it indicates the completion of the configuration process. As an input, a Low level on DONE can be configured to delay the global logic initialization and the enabling of outputs.                                                                                                                                                    |

|                        |                          |                      | The optional pull-up resistor is selected as an option in the program that creates the configuration bitstream. The resistor is included by default.                                                                                                                                                                                                                                                                                      |

| PROGRAM                | I                        | I                    | PROGRAM is an active Low input that forces the FPGA to clear its configuration memory. It is used to initiate a configuration cycle. When PROGRAM goes High, the FPGA finishes the current clear cycle and executes another complete clear cycle, before it goes into a WAIT state and releases INIT.                                                                                                                                     |

|                        |                          |                      | The PROGRAM pin has a permanent weak pull-up, so it need not be externally pulled up to VCC.                                                                                                                                                                                                                                                                                                                                              |

| MODE<br>(Spartan)      | I                        | X                    | The Mode input(s) are sampled after INIT goes High to determine the configuration mode to be used.                                                                                                                                                                                                                                                                                                                                        |

| M0, M1<br>(Spartan-XL) |                          |                      | During configuration, these pins have a weak pull-up resistor. For the most popular configuration mode, Slave Serial, the mode pins can be left unconnected. For Master Serial mode, connect the Mode/M0 pin directly to system ground.                                                                                                                                                                                                   |

Table 18: Pin Descriptions (Continued)

|                                         | I/O                                 |                      |                                                                                                                                                                                                                                                                          |  |  |  |

|-----------------------------------------|-------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                | During<br>Config.                   | I/O After<br>Config. | Pin Description                                                                                                                                                                                                                                                          |  |  |  |

| SGCK1 -<br>SGCK4<br>(Spartan)           | Weak<br>Pull-up<br>(except<br>SGCK4 | I or I/O             | Four Secondary Global inputs each drive a dedicated internal global net with short delay and minimal skew. These internal global nets can also be driven from internal logic. If not used to drive a global net, any of these pins is a user-programmable I/O pin.       |  |  |  |

|                                         | is DOUT)                            |                      | The SGCK1-SGCK4 pins provide the shortest path to the four Secondary Global Buffers. Any input pad symbol connected directly to the input of a BUFGS symbol is automatically placed on one of these pins.                                                                |  |  |  |

| GCK1 -<br>GCK8<br>(Spartan-XL)          | Weak<br>Pull-up<br>(except          | I or I/O             | Eight Global inputs each drive a dedicated internal global net with short delay and minimal skew. These internal global nets can also be driven from internal logic. If not used to drive a global net, any of these pins is a user-programmable I/O pin.                |  |  |  |

|                                         | GCK6 is<br>DOUT)                    |                      | The GCK1-GCK8 pins provide the shortest path to the eight Global Low-Skew Buffers. Any input pad symbol connected directly to the input of a BUFGLS symbol is automatically placed on one of these pins.                                                                 |  |  |  |

| CS1<br>(Spartan-XL)                     | I                                   | I/O                  | During Express configuration, CS1 is used as a serial-enable signal for daisy-chaining.                                                                                                                                                                                  |  |  |  |

| D0-D7<br>(Spartan-XL)                   | I                                   | I/O                  | During Express configuration, these eight input pins receive configuration data. After configuration, they are user-programmable I/O pins.                                                                                                                               |  |  |  |

| DIN                                     | I                                   | I/O                  | During Slave Serial or Master Serial configuration, DIN is the serial configuration data input receiving data on the rising edge of CCLK. After configuration, DIN is a user-programmable I/O pin.                                                                       |  |  |  |

| DOUT                                    | 0                                   | I/O                  | During Slave Serial or Master Serial configuration, DOUT is the serial configuration data output that can drive the DIN of daisy-chained slave FPGAs. DOUT data changes on the falling edge of CCLK, one-and-a-half CCLK periods after it was received at the DIN input. |  |  |  |

|                                         |                                     |                      | In Spartan-XL family Express mode, DOUT is the status output that can drive the CS1 of daisy-chained FPGAs, to enable and disable downstream devices.                                                                                                                    |  |  |  |

|                                         |                                     |                      | After configuration, DOUT is a user-programmable I/O pin.                                                                                                                                                                                                                |  |  |  |

| Unrestricted User-Programmable I/O Pins |                                     |                      |                                                                                                                                                                                                                                                                          |  |  |  |

| I/O                                     | Weak<br>Pull-up                     | I/O                  | These pins can be configured to be input and/or output after configuration is completed. Before configuration is completed, these pins have an internal high-value pull-up resistor network that defines the logic level as High.                                        |  |  |  |

# **XCS10 and XCS10XL Device Pinouts**

| XCS10/XL                 |                     |            |                        |            | Bndry              |

|--------------------------|---------------------|------------|------------------------|------------|--------------------|

| Pad Name                 | PC84 <sup>(4)</sup> | VQ100      | CS144 <sup>(2,4)</sup> | TQ144      | Scan               |

| VCC                      | P33                 | P25        | N1                     | P37        | -                  |

| Not                      | P34                 | P26        | N2                     | P38        | 174 <sup>(1)</sup> |

| Connect-                 |                     |            |                        |            |                    |

| ed <sup>(1)</sup>        |                     |            |                        |            |                    |

| PWRDWN <sup>(2</sup>     |                     |            |                        |            |                    |

| )                        |                     |            |                        |            |                    |

| I/O,                     | P35                 | P27        | М3                     | P39        | 175 <sup>(3)</sup> |

| PGCK2 <sup>(1)</sup>     |                     |            |                        |            |                    |

| GCK3 <sup>(2)</sup>      | D00                 | Doo        | NO                     | D.10       | 470 (3)            |

| I/O (HDC)                | P36                 | P28        | N3                     | P40        | 178 <sup>(3)</sup> |

| 1/0                      | -                   | -          | K4                     | P41        | 181 <sup>(3)</sup> |

| 1/0                      | -                   | -          | L4                     | P42        | 184 <sup>(3)</sup> |

| I/O (I DC)               | -<br>D07            | P29        | M4                     | P43        | 187 <sup>(3)</sup> |

| I/O (LDC)                | P37                 | P30        | N4                     | P44        | 190 <sup>(3)</sup> |

| GND                      | -                   | -          | K5                     | P45        | 193 <sup>(3)</sup> |

| I/O<br>I/O               | -                   | -          | L5<br>M5               | P46<br>P47 | 193 <sup>(3)</sup> |

|                          | -<br>D00            | -<br>D01   | N5                     | P47<br>P48 | 196 <sup>(3)</sup> |

| I/O<br>I/O               | P38                 | P31<br>P32 | K6                     | P46<br>P49 | 202 (3)            |

| I/O                      | P39                 | P32        | L6                     | P49<br>P50 | 205 (3)            |

| I/O                      | -                   | P33        | M6                     | P50<br>P51 | 208 (3)            |

| I/O                      | P40                 | P35        | N6                     | P52        | 211 <sup>(3)</sup> |

|                          | P40<br>P41          | P35        | M7                     | P52        | 211 <sup>(3)</sup> |

| I/O (INIT) VCC           | P42                 | P37        | N7                     | P54        | 214 (9)            |

| GND                      | P43                 | P38        | L7                     | P55        | -                  |

| I/O                      | P44                 | P39        | K7                     | P56        | 217 <sup>(3)</sup> |

| I/O                      | P45                 | P40        | N8                     | P57        | 220 (3)            |

| I/O                      | 1 43                | P41        | M8                     | P58        | 223 (3)            |

| I/O                      | _                   | P42        | L8                     | P59        | 226 <sup>(3)</sup> |

| I/O                      | P46                 | P43        | K8                     | P60        | 229 (3)            |

| I/O                      | P47                 | P44        | N9                     | P61        | 232 (3)            |

| I/O                      | -                   | -          | M9                     | P62        | 235 (3)            |

| I/O                      | _                   | -          | L9                     | P63        | 238 (3)            |

| GND                      | _                   | _          | K9                     | P64        | -                  |

| I/O                      | P48                 | P45        | N10                    | P65        | 241 <sup>(3)</sup> |

| I/O                      | P49                 | P46        | M10                    | P66        | 244 (3)            |

| I/O                      | -                   | -          | L10                    | P67        | 247 <sup>(3)</sup> |

| I/O                      | -                   | -          | N11                    | P68        | 250 <sup>(3)</sup> |

| I/O                      | P50                 | P47        | M11                    | P69        | 253 <sup>(3)</sup> |

| I/O,                     | P51                 | P48        | L11                    | P70        | 256 <sup>(3)</sup> |

| SGCK3 <sup>(1)</sup>     |                     |            |                        |            |                    |

| GCK4 <sup>(2)</sup>      |                     |            |                        |            |                    |

| GND                      | P52                 | P49        | N12                    | P71        | -                  |

| DONE                     | P53                 | P50        | M12                    | P72        | -                  |

| VCC                      | P54                 | P51        | N13                    | P73        | -                  |

| PROGRAM                  | P55                 | P52        | M13                    | P74        | -                  |

| I/O (D7 <sup>(2)</sup> ) | P56                 | P53        | L12                    | P75        | 259 <sup>(3)</sup> |

# **XCS10 and XCS10XL Device Pinouts**

| XCS10/XL                                    | (4)                 |       | (0.4)                  |       | Bndry              |

|---------------------------------------------|---------------------|-------|------------------------|-------|--------------------|

| Pad Name                                    | PC84 <sup>(4)</sup> | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | Scan               |

| I/O,                                        | P57                 | P54   | L13                    | P76   | 262 <sup>(3)</sup> |

| PGCK3 <sup>(1)</sup><br>GCK5 <sup>(2)</sup> |                     |       |                        |       |                    |

| I/O                                         | -                   | -     | K10                    | P77   | 265 <sup>(3)</sup> |

| I/O                                         | -                   | -     | K11                    | P78   | 268 <sup>(3)</sup> |

| I/O (D6 <sup>(2)</sup> )                    | P58                 | P55   | K12                    | P79   | 271 <sup>(3)</sup> |

| I/O                                         | -                   | P56   | K13                    | P80   | 274 (3)            |

| GND                                         | -                   | -     | J10                    | P81   | -                  |

| I/O                                         | -                   | -     | J11                    | P82   | 277 (3)            |

| I/O                                         | -                   | -     | J12                    | P83   | 280 (3)            |

| I/O (D5 <sup>(2)</sup> )                    | P59                 | P57   | J13                    | P84   | 283 <sup>(3)</sup> |

| I/O                                         | P60                 | P58   | H10                    | P85   | 286 <sup>(3)</sup> |

| I/O                                         | -                   | P59   | H11                    | P86   | 289 <sup>(3)</sup> |

| I/O                                         | -                   | P60   | H12                    | P87   | 292 <sup>(3)</sup> |

| I/O (D4 <sup>(2)</sup> )                    | P61                 | P61   | H13                    | P88   | 295 <sup>(3)</sup> |

| I/O                                         | P62                 | P62   | G12                    | P89   | 298 <sup>(3)</sup> |

| VCC                                         | P63                 | P63   | G13                    | P90   | -                  |

| GND                                         | P64                 | P64   | G11                    | P91   | -                  |

| I/O (D3 <sup>(2)</sup> )                    | P65                 | P65   | G10                    | P92   | 301 <sup>(3)</sup> |

| I/O                                         | P66                 | P66   | F13                    | P93   | 304 <sup>(3)</sup> |

| I/O                                         | -                   | P67   | F12                    | P94   | 307 <sup>(3)</sup> |

| I/O                                         | -                   | -     | F11                    | P95   | 310 <sup>(3)</sup> |

| I/O (D2 <sup>(2)</sup> )                    | P67                 | P68   | F10                    | P96   | 313 <sup>(3)</sup> |

| I/O                                         | P68                 | P69   | E13                    | P97   | 316 <sup>(3)</sup> |

| I/O                                         | -                   | -     | E12                    | P98   | 319 <sup>(3)</sup> |

| I/O                                         | -                   | -     | E11                    | P99   | 322 (3)            |

| GND                                         | -                   | -     | E10                    | P100  | -                  |

| I/O (D1 <sup>(2)</sup> )                    | P69                 | P70   | D13                    | P101  | 325 <sup>(3)</sup> |

| I/O                                         | P70                 | P71   | D12                    | P102  | 328 <sup>(3)</sup> |

| I/O                                         | -                   | -     | D11                    | P103  | 331 <sup>(3)</sup> |

| I/O                                         | -                   | -     | C13                    | P104  | 334 <sup>(3)</sup> |

| I/O (D0 <sup>(2)</sup> ,<br>DIN)            | P71                 | P72   | C12                    | P105  | 337 <sup>(3)</sup> |

| I/O,                                        | P72                 | P73   | C11                    | P106  | 340 (3)            |

| SGCK4 <sup>(1)</sup>                        |                     |       |                        |       |                    |

| GCK6 <sup>(2)</sup>                         |                     |       |                        |       |                    |

| (DOUT)                                      |                     |       |                        |       |                    |

| CCLK                                        | P73                 | P74   | B13                    | P107  | -                  |

| VCC                                         | P74                 | P75   | B12                    | P108  | -                  |

| O, TDO                                      | P75                 | P76   | A13                    | P109  | 0                  |

| GND                                         | P76                 | P77   | A12                    | P110  | -                  |

| I/O                                         | P77                 | P78   | B11                    | P111  | 2                  |

| I/O,                                        | P78                 | P79   | A11                    | P112  | 5                  |

| PGCK4 <sup>(1)</sup>                        |                     |       |                        |       |                    |

| GCK7 <sup>(2)</sup>                         |                     |       | D10                    | D110  | 0                  |

| 1/0                                         | -                   | -     | D10                    | P113  | 8                  |

| 1/0                                         | -<br>D70            | -     | C10                    | P114  | 11                 |

| I/O (CS1 <sup>(2)</sup> )                   | P79                 | P80   | B10                    | P115  | 14                 |

## **XCS10 and XCS10XL Device Pinouts**

| XCS10/XL<br>Pad Name | PC84 <sup>(4)</sup> | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | Bndry<br>Scan |

|----------------------|---------------------|-------|------------------------|-------|---------------|

| I/O                  | P80                 | P81   | A10                    | P116  | 17            |

| GND                  | -                   | -     | C9                     | P118  | -             |

| I/O                  | -                   | -     | B9                     | P119  | 20            |

| I/O                  | -                   | -     | A9                     | P120  | 23            |

| I/O                  | P81                 | P82   | D8                     | P121  | 26            |

| I/O                  | P82                 | P83   | C8                     | P122  | 29            |

| I/O                  | -                   | P84   | B8                     | P123  | 32            |

| I/O                  | -                   | P85   | A8                     | P124  | 35            |

| I/O                  | P83                 | P86   | B7                     | P125  | 38            |

| I/O                  | P84                 | P87   | A7                     | P126  | 41            |

| GND                  | P1                  | P88   | C7                     | P127  | -             |

#### Notes:

- 1. 5V Spartan family only

- 2. 3V Spartan-XL family only

- 3. The "PWRDWN" on the XCS10XL is not part of the Boundary Scan chain. For the XCS10XL, subtract 1 from all Boundary Scan numbers from GCK3 on (175 and higher).

- 4. PC84 and CS144 packages discontinued by PDN2004-01

## Additional XCS10/XL Package Pins

| TQ144  |                    |   |   |   |   |  |  |  |  |  |

|--------|--------------------|---|---|---|---|--|--|--|--|--|

|        | Not Connected Pins |   |   |   |   |  |  |  |  |  |

| P117   | -                  | - | - | - | - |  |  |  |  |  |

| 5/5/97 |                    |   |   |   |   |  |  |  |  |  |

| CS144   |                    |   |   |   |   |  |  |  |  |  |

|---------|--------------------|---|---|---|---|--|--|--|--|--|

|         | Not Connected Pins |   |   |   |   |  |  |  |  |  |

| D9      | -                  | - | - | - | - |  |  |  |  |  |

| 4/28/99 |                    |   |   |   |   |  |  |  |  |  |

## XCS20 and XCS20XL Device Pinouts

| XCS20/XL           |       |                        |       |       | Bndry |

|--------------------|-------|------------------------|-------|-------|-------|

| Pad Name           | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Scan  |

| VCC                | P89   | D7                     | P128  | P183  | -     |

| I/O                | P90   | A6                     | P129  | P184  | 62    |

| I/O                | P91   | B6                     | P130  | P185  | 65    |

| I/O                | P92   | C6                     | P131  | P186  | 68    |

| I/O                | P93   | D6                     | P132  | P187  | 71    |

| I/O                | -     | -                      | -     | P188  | 74    |

| I/O                | -     | -                      | -     | P189  | 77    |

| I/O                | P94   | A5                     | P133  | P190  | 80    |

| I/O                | P95   | B5                     | P134  | P191  | 83    |

| VCC <sup>(2)</sup> | -     | -                      | -     | P192  | -     |

| I/O                | -     | C5                     | P135  | P193  | 86    |

| I/O                | -     | D5                     | P136  | P194  | 89    |

| GND                | -     | A4                     | P137  | P195  | -     |

| I/O                | -     | -                      | -     | P196  | 92    |

| I/O                | -     | -                      | -     | P197  | 95    |

| I/O                | -     | -                      | -     | P198  | 98    |

| I/O                | -     | -                      | -     | P199  | 101   |

| I/O                | P96   | B4                     | P138  | P200  | 104   |

| I/O                | P97   | C4                     | P139  | P201  | 107   |

| I/O                | -     | А3                     | P140  | P204  | 110   |

| I/O                | -     | B3                     | P141  | P205  | 113   |

| I/O                | P98   | C3                     | P142  | P206  | 116   |

## **XCS20 and XCS20XL Device Pinouts**

| XCS20/XL                                              | V0400 | CS144 <sup>(2,4)</sup> | TO444 | DOGGG | Bndry |

|-------------------------------------------------------|-------|------------------------|-------|-------|-------|

| Pad Name                                              | VQ100 |                        | TQ144 | PQ208 | Scan  |

| I/O,<br>SGCK1 <sup>(1)</sup> ,<br>GCK8 <sup>(2)</sup> | P99   | A2                     | P143  | P207  | 119   |

| VCC                                                   | P100  | B2                     | P144  | P208  | -     |

| GND                                                   | P1    | A1                     | P1    | P1    | -     |

| I/O,<br>PGCK1 <sup>(1)</sup> ,<br>GCK1 <sup>(2)</sup> | P2    | B1                     | P2    | P2    | 122   |

| I/O                                                   | P3    | C2                     | P3    | P3    | 125   |

| I/O                                                   | -     | C1                     | P4    | P4    | 128   |

| I/O                                                   | -     | D4                     | P5    | P5    | 131   |

| I/O, TDI                                              | P4    | D3                     | P6    | P6    | 134   |

| I/O, TCK                                              | P5    | D2                     | P7    | P7    | 137   |

| I/O                                                   | -     | -                      | -     | P8    | 140   |

| I/O                                                   | -     | -                      | -     | P9    | 143   |

| I/O                                                   | -     | -                      | -     | P10   | 146   |

| I/O                                                   | -     | -                      | -     | P11   | 149   |

| GND                                                   | -     | D1                     | P8    | P13   | -     |

| I/O                                                   | -     | E4                     | P9    | P14   | 152   |

| I/O                                                   | -     | E3                     | P10   | P15   | 155   |

| I/O, TMS                                              | P6    | E2                     | P11   | P16   | 158   |

| I/O                                                   | P7    | E1                     | P12   | P17   | 161   |

| VCC <sup>(2)</sup>                                    | -     | -                      | -     | P18   | -     |

| I/O                                                   | -     | -                      | -     | P19   | 164   |

| I/O                                                   | -     | -                      | -     | P20   | 167   |

# **XCS20 and XCS20XL Device Pinouts**

|                                               | d XCS20XL Device Pinouts |                        |       |       |                    |  |  |  |

|-----------------------------------------------|--------------------------|------------------------|-------|-------|--------------------|--|--|--|

| XCS20/XL<br>Pad Name                          | VQ100                    | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |  |  |  |

| PROGRAM                                       | P52                      | M13                    | P74   | P106  | -                  |  |  |  |

| I/O (D7 <sup>(2)</sup> )                      | P53                      | L12                    | P75   | P107  | 367 <sup>(3)</sup> |  |  |  |

| I/O,                                          | P54                      | L13                    | P76   | P108  | 370 <sup>(3)</sup> |  |  |  |

| PGCK3 <sup>(1)</sup> ,<br>GCK5 <sup>(2)</sup> |                          |                        |       |       |                    |  |  |  |

| I/O                                           |                          | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |  |

| 1/0                                           | -                        | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |  |

| I/O (D6 <sup>(2)</sup> )                      | -<br>P55                 | K11                    | P79   | P110  | 379 <sup>(3)</sup> |  |  |  |

| I/O (D6(=/)                                   |                          | K12                    |       | P112  | 382 (3)            |  |  |  |

|                                               | P56                      | NIS                    | P80   |       | 385 (3)            |  |  |  |

| 1/0                                           | -                        | -                      | -     | P114  |                    |  |  |  |

| 1/0                                           | -                        | -                      | -     | P115  | 388 (3)            |  |  |  |

| 1/0                                           | -                        | -                      | -     | P116  | 391 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P117  | 394 <sup>(3)</sup> |  |  |  |

| GND                                           | -                        | J10                    | P81   | P118  | - (2)              |  |  |  |

| I/O                                           | -                        | J11                    | P82   | P119  | 397 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | J12                    | P83   | P120  | 400 (3)            |  |  |  |

| VCC <sup>(2)</sup>                            | -                        | -                      | -     | P121  | - (0)              |  |  |  |

| I/O (D5 <sup>(2)</sup> )                      | P57                      | J13                    | P84   | P122  | 403 (3)            |  |  |  |

| I/O                                           | P58                      | H10                    | P85   | P123  | 406 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P124  | 409 (3)            |  |  |  |

| I/O                                           | -                        | -                      | -     | P125  | 412 <sup>(3)</sup> |  |  |  |

| I/O                                           | P59                      | H11                    | P86   | P126  | 415 <sup>(3)</sup> |  |  |  |

| I/O                                           | P60                      | H12                    | P87   | P127  | 418 <sup>(3)</sup> |  |  |  |

| I/O (D4 <sup>(2)</sup> )                      | P61                      | H13                    | P88   | P128  | 421 <sup>(3)</sup> |  |  |  |

| I/O                                           | P62                      | G12                    | P89   | P129  | 424 <sup>(3)</sup> |  |  |  |

| VCC                                           | P63                      | G13                    | P90   | P130  | -                  |  |  |  |

| GND                                           | P64                      | G11                    | P91   | P131  | -                  |  |  |  |

| I/O (D3 <sup>(2)</sup> )                      | P65                      | G10                    | P92   | P132  | 427 <sup>(3)</sup> |  |  |  |

| I/O                                           | P66                      | F13                    | P93   | P133  | 430 <sup>(3)</sup> |  |  |  |

| I/O                                           | P67                      | F12                    | P94   | P134  | 433 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | F11                    | P95   | P135  | 436 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P136  | 439 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P137  | 442 (3)            |  |  |  |

| I/O (D2 <sup>(2)</sup> )                      | P68                      | F10                    | P96   | P138  | 445 <sup>(3)</sup> |  |  |  |

| I/O                                           | P69                      | E13                    | P97   | P139  | 448 <sup>(3)</sup> |  |  |  |

| VCC <sup>(2)</sup>                            | -                        | -                      | -     | P140  | -                  |  |  |  |

| I/O                                           | _                        | E12                    | P98   | P141  | 451 <sup>(3)</sup> |  |  |  |

| I/O                                           | _                        | E11                    | P99   | P142  | 454 <sup>(3)</sup> |  |  |  |

| GND                                           | -                        | E10                    | P100  | P143  | -                  |  |  |  |

| I/O                                           | -                        | -                      | -     | P145  | 457 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P146  | 460 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P147  | 463 <sup>(3)</sup> |  |  |  |

| I/O                                           | -                        | -                      | -     | P148  | 466 <sup>(3)</sup> |  |  |  |