Welcome to **E-XFL.COM**

Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 784                                                          |

| Number of Logic Elements/Cells | 1862                                                         |

| Total RAM Bits                 | 25088                                                        |

| Number of I/O                  | 205                                                          |

| Number of Gates                | 40000                                                        |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 256-BBGA                                                     |

| Supplier Device Package        | 256-PBGA (27x27)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xillinx/xcs40xl-4bg256c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Spartan and Spartan-XL devices provide system clock rates exceeding 80 MHz and internal performance in excess of 150 MHz. In addition to the conventional benefit of high volume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.

The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family's features and benefits. Technology advancements have been derived from the XC4000XLA process developments.

# **Logic Functional Description**

The Spartan series uses a standard FPGA structure as shown in Figure 1, page 2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.

- CLBs provide the functional elements for implementing the user's logic.

- IOBs provide the interface between the package pins and internal signal lines.

- Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.

The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.

# **Configurable Logic Blocks (CLBs)**

The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simplified block diagram in Figure 2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the **Advanced Features Description**, page 13.

#### **Function Generators**

Two 16 x 1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offering unrestricted logic implementation of any Boolean function of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.

A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure 2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement certain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbitrarily defined Boolean function of five inputs.

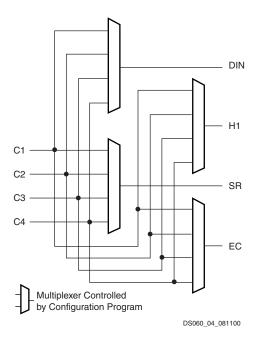

Figure 4: CLB Control Signal Interface

The four internal control signals are:

- EC: Enable Clock

- SR: Asynchronous Set/Reset or H function generator Input 0

- DIN: Direct In or H function generator Input 2

- H1: H function generator Input 1.

# Input/Output Blocks (IOBs)

User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be configured for input, output, or bidirectional signals. Figure 6 shows a simplified functional block diagram of the Spartan/XL FPGA IOB.

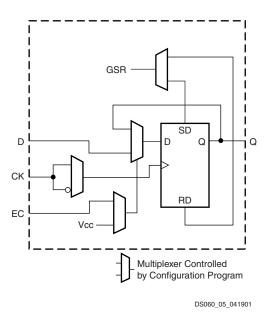

Figure 5: IOB Flip-Flop/Latch Functional Block

Diagram

# IOB Input Signal Path

The input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3, and a simplified block diagram of the register can be seen in Figure 5.

Table 3: Input Register Functionality

| Mode               | CK | EC | D | Q  |

|--------------------|----|----|---|----|

| Power-Up or<br>GSR | Х  | Х  | Х | SR |

| Flip-Flop          |    | 1* | D | D  |

|                    | 0  | Х  | Х | Q  |

| Latch              | 1  | 1* | Х | Q  |

|                    | 0  | 1* | D | D  |

| Both               | Х  | 0  | Х | Q  |

#### Legend:

| X  | Don't care.                                  |

|----|----------------------------------------------|

| ^  |                                              |

|    | Rising edge (clock not inverted).            |

| SR | Set or Reset value. Reset is default.        |

| 0* | Input is Low or unconnected (default value)  |

| 1* | Input is High or unconnected (default value) |

Table 4: Supported Sources for Spartan/XL Inputs

|                                                             | -          | artan<br>outs   | Spartan-XL<br>Inputs |

|-------------------------------------------------------------|------------|-----------------|----------------------|

| Source                                                      | 5V,<br>TTL | 5V,<br>CMOS     | 3.3V<br>CMOS         |

| Any device, V <sub>CC</sub> = 3.3V,<br>CMOS outputs         | √          | Unreli-<br>able | V                    |

| Spartan family, V <sub>CC</sub> = 5V,<br>TTL outputs        | <b>V</b>   | Data            | V                    |

| Any device, $V_{CC} = 5V$ , TTL outputs $(V_{OH} \le 3.7V)$ | <b>V</b>   |                 | V                    |

| Any device, V <sub>CC</sub> = 5V,<br>CMOS outputs           | √          | V               | √ (default<br>mode)  |

### Spartan-XL Family V<sub>CC</sub> Clamping

Spartan-XL FPGAs have an optional clamping diode connected from each I/O to  $V_{CC}$ . When enabled they clampringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications.  $V_{CC}$  clamping is a global option affecting all I/O pins.

Spartan-XL devices are fully 5V TTL I/O compatible if  $V_{CC}$  clamping is not enabled. With  $V_{CC}$  clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above  $V_{CC}$ . If enabled, TTL I/O compatibility is maintained but full 5V I/O tolerance is sacrificed. The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.

Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.

Table 5: I/O Standards Supported by Spartan-XL FPGAs

| Signaling<br>Standard | VCC<br>Clamping | Output<br>Drive | V <sub>IH MAX</sub> | V <sub>IH MIN</sub>    | V <sub>IL MAX</sub>    | V <sub>OH MIN</sub>    | V <sub>OL MAX</sub>    |

|-----------------------|-----------------|-----------------|---------------------|------------------------|------------------------|------------------------|------------------------|

| TTL                   | Not allowed     | 12/24 mA        | 5.5                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| LVTTL                 | OK              | 12/24 mA        | 3.6                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| PCI5V                 | Not allowed     | 24 mA           | 5.5                 | 2.0                    | 0.8                    | 2.4                    | 0.4                    |

| PCI3V                 | Required        | 12 mA           | 3.6                 | 50% of V <sub>CC</sub> | 30% of V <sub>CC</sub> | 90% of V <sub>CC</sub> | 10% of V <sub>CC</sub> |

| LVCMOS 3V             | OK              | 12/24 mA        | 3.6                 | 50% of V <sub>CC</sub> | 30% of V <sub>CC</sub> | 90% of V <sub>CC</sub> | 10% of V <sub>CC</sub> |

# Additional Fast Capture Input Latch (Spartan-XL Family Only)

The Spartan-XL family OB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements. This additional latch allows the fast capture of input data, which is then synchronized to the internal clock by the IOB flip-flop or latch.

To place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a transparent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element, and the inverter is absorbed into the IOB.

#### IOB Output Signal Path

Output signals can be optionally inverted within the IOB, and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in Table 6.

Table 6: Output Flip-Flop Functionality

| Mode               | Clock | Clock<br>Enable | Т  | D | Q  |

|--------------------|-------|-----------------|----|---|----|

| Power-Up<br>or GSR | Х     | Х               | 0* | Х | SR |

| Flip-Flop          | Х     | 0               | 0* | Х | Q  |

|                    |       | 1*              | 0* | D | D  |

|                    | Х     | Х               | 1  | Х | Z  |

|                    | 0     | Х               | 0* | Х | Q  |

#### Legend:

| V | Don't care |

|---|------------|

|   |            |

\_\_\_ Rising edge (clock not inverted).

SR Set or Reset value. Reset is default.

0\* Input is Low or unconnected (default value)

1\* Input is High or unconnected (default value)

Z 3-state

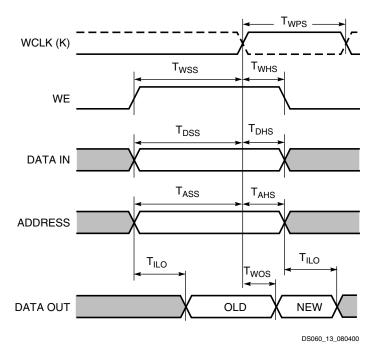

Figure 13: Data Write and Access Timing for RAM

WCLK can be configured as active on either the rising edge (default) or the falling edge. While the WCLK input to the RAM accepts the same signal as the clock input to the associated CLB's flip-flops, the sense of this WCLK input can be

inverted with respect to the sense of the flip-flop clock inputs. Consequently, within the same CLB, data at the RAM SPO line can be stored in a flip-flop with either the same or the inverse clock polarity used to write data to the RAM.

The WE input is active High and cannot be inverted within the CLB.

Allowing for settling time, the data on the SPO output reflects the contents of the RAM location currently addressed. When the address changes, following the asynchronous delay  $T_{ILO}$ , the data stored at the new address location will appear on SPO. If the data at a particular RAM address is overwritten, after the delay  $T_{WOS}$ , the new data will appear on SPO.

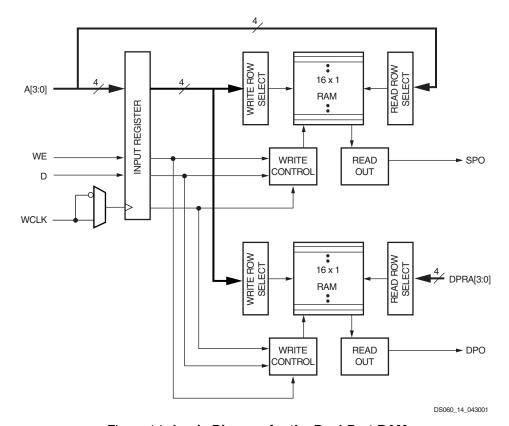

# **Dual-Port Mode**

In dual-port mode, the function generators (F-LUT and G-LUT) are used to create a 16 x 1 dual-port memory. Of the two data ports available, one permits read and write operations at the address specified by A[3:0] while the second provides only for read operations at the address specified independently by DPRA[3:0]. As a result, simultaneous read/write operations at different addresses (or even at the same address) are supported.

The functional organization of the 16  $\times$  1 dual-port RAM is shown in Figure 14. The dual-port RAM signals and the

Figure 14: Logic Diagram for the Dual-Port RAM

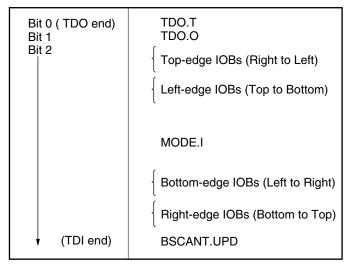

Figure 20 is a diagram of the Spartan/XL FPGA boundary scan logic. It includes three bits of Data Register per IOB, the IEEE 1149.1 Test Access Port controller, and the Instruction Register with decodes.

Spartan/XL devices can also be configured through the boundary scan logic. See **Configuration Through the Boundary Scan Pins**, page 37.

# Data Registers

The primary data register is the boundary scan register. For each IOB pin in the FPGA, bonded or not, it includes three bits for In, Out and 3-state Control. Non-IOB pins have appropriate partial bit population for In or Out only. PROGRAM, CCLK and DONE are not included in the boundary scan register. Each EXTEST CAPTURE-DR state captures all In, Out, and 3-state pins.

The data register also includes the following non-pin bits: TDO.T, and TDO.O, which are always bits 0 and 1 of the data register, respectively, and BSCANT.UPD, which is always the last bit of the data register. These three boundary scan bits are special-purpose Xilinx test signals.

The other standard data register is the single flip-flop BYPASS register. It synchronizes data being passed through the FPGA to the next downstream boundary scan device.

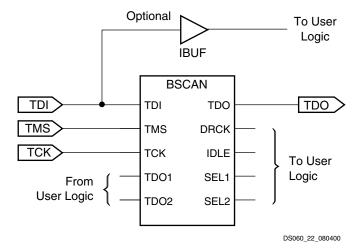

The FPGA provides two additional data registers that can be specified using the BSCAN macro. The FPGA provides two user pins (BSCAN.SEL1 and BSCAN.SEL2) which are the decodes of two user instructions. For these instructions, two corresponding pins (BSCAN.TDO1 and BSCAN.TDO2) allow user scan data to be shifted out on TDO. The data register clock (BSCAN.DRCK) is available for control of test logic which the user may wish to implement with CLBs. The NAND of TCK and RUN-TEST-IDLE is also provided (BSCAN.IDLE).

#### Instruction Set

The Spartan/XL FPGA boundary scan instruction set also includes instructions to configure the device and read back the configuration data. The instruction set is coded as shown in Table 12.

Table 12: Boundary Scan Instructions

| Ins | structi | on | Test                           | TDO                | I/O Data   |

|-----|---------|----|--------------------------------|--------------------|------------|

| 12  | l1      | 10 | Selected                       | Source             | Source     |

| 0   | 0       | 0  | EXTEST                         | DR                 | DR         |

| 0   | 0       | 1  | SAMPLE/<br>PRELOAD             | DR                 | Pin/Logic  |

| 0   | 1       | 0  | USER 1                         | BSCAN.<br>TDO1     | User Logic |

| 0   | 1       | 1  | USER 2                         | BSCAN.<br>TDO2     | User Logic |

| 1   | 0       | 0  | READBACK                       | Readback<br>Data   | Pin/Logic  |

| 1   | 0       | 1  | CONFIGURE                      | DOUT               | Disabled   |

| 1   | 1       | 0  | IDCODE<br>(Spartan-XL<br>only) | IDCODE<br>Register | -          |

| 1   | 1       | 1  | BYPASS                         | Bypass<br>Register | -          |

#### Bit Sequence

The bit sequence within each IOB is: In, Out, 3-state. The input-only pins contribute only the In bit to the boundary scan I/O data register, while the output-only pins contributes all three bits.

The first two bits in the I/O data register are TDO.T and TDO.O, which can be used for the capture of internal signals. The final bit is BSCANT.UPD, which can be used to drive an internal net. These locations are primarily used by Xilinx for internal testing.

From a cavity-up view of the chip (as shown in the FPGA Editor), starting in the upper right chip corner, the boundary scan data-register bits are ordered as shown in Figure 21. The device-specific pinout tables for the Spartan/XL devices include the boundary scan locations for each IOB pin.

DS060 21 080400

Figure 21: Boundary Scan Bit Sequence

BSDL (Boundary Scan Description Language) files for Spartan/XL devices are available on the Xilinx website in the File Download area. Note that the 5V Spartan devices and 3V Spartan-XL devices have different BSDL files.

### Including Boundary Scan in a Design

If boundary scan is only to be used during configuration, no special elements need be included in the schematic or HDL code. In this case, the special boundary scan pins TDI, TMS, TCK and TDO can be used for user functions after configuration.

To indicate that boundary scan remain enabled after configuration, place the BSCAN library symbol and connect the TDI, TMS, TCK and TDO pad symbols to the appropriate pins, as shown in Figure 22.

Figure 22: Boundary Scan Example

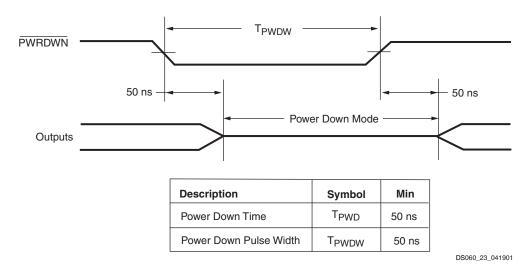

Figure 23: PWRDWN Pulse Timing

Power-down retains the configuration, but loses all data stored in the device flip-flops. All inputs are interpreted as Low, but the internal combinatorial logic is fully functional. Make sure that the combination of all inputs Low and all flip-flops set or reset in your design will not generate internal oscillations, or create permanent bus contention by activating internal bus drivers with conflicting data onto the same long line.

During configuration, the PWRDWN pin must be High. If the Power Down state is entered before or during configuration, the device will restart configuration once the PWRDWN signal is removed. Note that the configuration pins are affected by Power Down and may not reflect their normal function. If there is an external pull-up resistor on the DONE pin, it will be High during Power Down even if the device is not yet configured. Similarly, if PWRDWN is asserted before configuration is completed, the INIT pin will not indicate status information.

Note that the PWRDWN pin is not part of the Boundary Scan chain. Therefore, the Spartan-XL family has a separate set of BSDL files than the 5V Spartan family. Boundary scan logic is not usable during Power Down.

# **Configuration and Test**

Configuration is the process of loading design-specific programming data into one or more FPGAs to define the functional operation of the internal blocks and their interconnections. This is somewhat like loading the command registers of a programmable peripheral chip. Spartan/XL devices use several hundred bits of configuration data per CLB and its associated interconnects. Each configuration bit defines the state of a static memory cell

that controls either a function look-up table bit, a multiplexer input, or an interconnect pass transistor. The Xilinx development system translates the design into a netlist file. It automatically partitions, places and routes the logic and generates the configuration data in PROM format.

# **Configuration Mode Control**

5V Spartan devices have two configuration modes.

- MODE = 1 sets Slave Serial mode

- MODE = 0 sets Master Serial mode

3V Spartan-XL devices have three configuration modes.

- M1/M0 = 11 sets Slave Serial mode

- M1/M0 = 10 sets Master Serial mode

- M1/M0 = 0X sets Express mode

In addition to these modes, the device can be configured through the Boundary Scan logic (See "Configuration Through the Boundary Scan Pins" on page 37.).

The Mode pins are sampled prior to starting configuration to determine the configuration mode. After configuration, these pin are unused. The Mode pins have a weak pull-up resistor turned on during configuration. With the Mode pins High, Slave Serial mode is selected, which is the most popular configuration mode. Therefore, for the most common configuration mode, the Mode pins can be left unconnected. If the Master Serial mode is desired, the MODE/M0 pin should be connected directly to GND, or through a pull-down resistor of 1 K $\Omega$  or less.

During configuration, some of the I/O pins are used temporarily for the configuration process. All pins used during con-

Slave Serial is the default mode if the Mode pins are left unconnected, as they have weak pull-up resistors during configuration.

Multiple slave devices with identical configurations can be wired with parallel DIN inputs. In this way, multiple devices can be configured simultaneously.

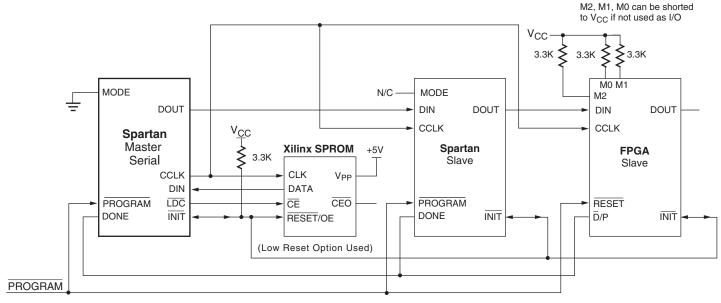

# **Serial Daisy Chain**

Multiple devices with different configurations can be connected together in a "daisy chain," and a single combined bitstream used to configure the chain of slave devices.

To configure a daisy chain of devices, wire the CCLK pins of all devices in parallel, as shown in Figure 25. Connect the DOUT of each device to the DIN of the next. The lead or master FPGA and following slaves each passes resynchronized configuration data coming from a single source. The header data, including the length count, is passed through

and is captured by each FPGA when it recognizes the 0010 preamble. Following the length-count data, each FPGA outputs a High on DOUT until it has received its required number of data frames.

After an FPGA has received its configuration data, it passes on any additional frame start bits and configuration data on DOUT. When the total number of configuration clocks applied after memory initialization equals the value of the 24-bit length count, the FPGAs begin the start-up sequence and become operational together. FPGA I/O are normally released two CCLK cycles after the last configuration bit is received.

The daisy-chained bitstream is not simply a concatenation of the individual bitstreams. The PROM File Formatter must be used to combine the bitstreams for a daisy-chained configuration.

Note:

Figure 25: Master/Slave Serial Mode Circuit Diagram

DS060\_25\_061301

DS060\_39\_082801

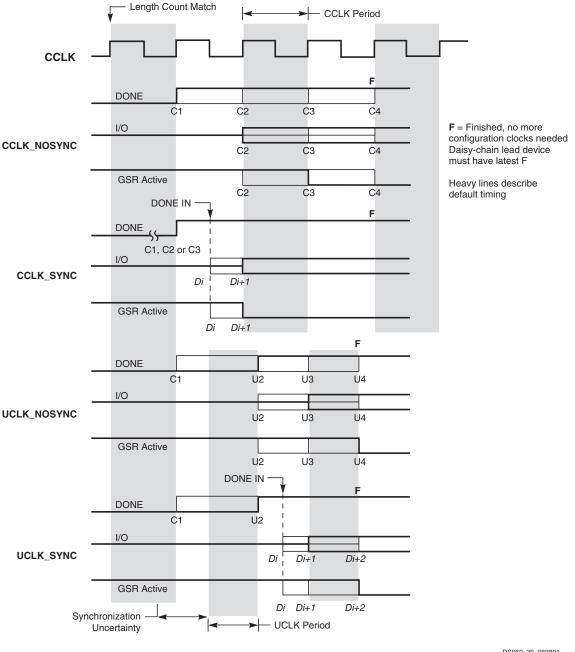

Figure 31: Start-up Timing

# **Configuration Through the Boundary Scan Pins**

Spartan/XL devices can be configured through the boundary scan pins. The basic procedure is as follows:

- Power up the FPGA with INIT held Low (or drive the PROGRAM pin Low for more than 300 ns followed by a High while holding INIT Low). Holding INIT Low allows enough time to issue the CONFIG command to the FPGA. The pin can be used as I/O after configuration if a resistor is used to hold INIT Low.

- Issue the CONFIG command to the TMS input.

- Wait for INIT to go High.

- Sequence the boundary scan Test Access Port to the SHIFT-DR state.

- Toggle TCK to clock data into TDI pin.

The user must account for all TCK clock cycles after INIT goes High, as all of these cycles affect the Length Count compare.

For more detailed information, refer to the Xilinx application note, "Boundary Scan in FPGA Devices." This application note applies to Spartan and Spartan-XL devices.

#### **Readback Abort**

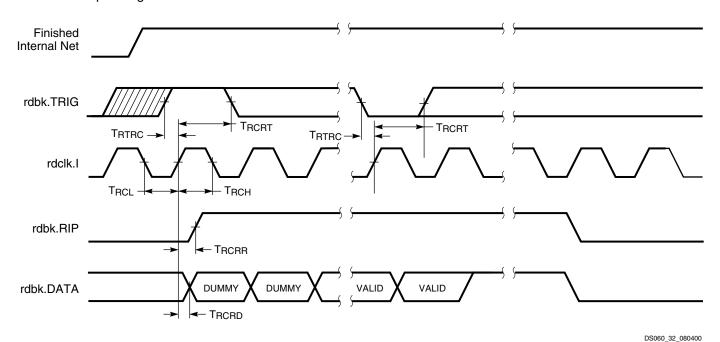

When the Readback Abort option is selected, a High-to-Low transition on RDBK.TRIG terminates the Readback operation and prepares the logic to accept another trigger.

After an aborted Readback, additional clocks (up to one Readback clock per configuration frame) may be required to re-initialize the control logic. The status of Readback is indicated by the output control net RDBK.RIP. RDBK.RIP is High whenever a readback is in progress.

#### **Clock Select**

CCLK is the default clock. However, the user can insert another clock on RDBK.CLK. Readback control and data are clocked on rising edges of RDBK.CLK. If Readback must be inhibited for security reasons, the Readback control nets are simply not connected. RDBK.CLK is located in the lower right chip corner.

# Violating the Maximum High and Low Time Specification for the Readback Clock

The Readback clock has a maximum High and Low time specification. In some cases, this specification cannot be

met. For example, if a processor is controlling Readback, an interrupt may force it to stop in the middle of a readback. This necessitates stopping the clock, and thus violating the specification.

The specification is mandatory only on clocking data at the end of a frame prior to the next start bit. The transfer mechanism will load the data to a shift register during the last six clock cycles of the frame, prior to the start bit of the following frame. This loading process is dynamic, and is the source of the maximum High and Low time requirements.

Therefore, the specification only applies to the six clock cycles prior to and including any start bit, including the clocks before the first start bit in the Readback data stream. At other times, the frame data is already in the register and the register is not dynamic. Thus, it can be shifted out just like a regular shift register.

The user must precisely calculate the location of the Readback data relative to the frame. The system must keep track of the position within a data frame, and disable interrupts before frame boundaries. Frame lengths and data formats are listed in Table 16 and Table 17.

# **Readback Switching Characteristics Guidelines**

The following guidelines reflect worst-case values over the recommended operating conditions.

Figure 33: Spartan and Spartan-XL Readback Timing Diagram

# Spartan and Spartan-XL Readback Switching Characteristics

| Symbol            |           | Description                                    | Min | Max | Units |

|-------------------|-----------|------------------------------------------------|-----|-----|-------|

| T <sub>RTRC</sub> | rdbk.TRIG | rdbk.TRIG setup to initiate and abort Readback | 200 | -   | ns    |

| T <sub>RCRT</sub> |           | rdbk.TRIG hold to initiate and abort Readback  | 50  | -   | ns    |

| T <sub>RCRD</sub> | rdclk.l   | rdbk.DATA delay                                | -   | 250 | ns    |

| T <sub>RCRR</sub> |           | rdbk.RIP delay                                 | -   | 250 | ns    |

| T <sub>RCH</sub>  |           | High time                                      | 250 | 500 | ns    |

| T <sub>RCL</sub>  |           | Low time                                       | 250 | 500 | ns    |

- 1. Timing parameters apply to all speed grades.

- 2. If rdbk.TRIG is High prior to Finished, Finished will trigger the first Readback.

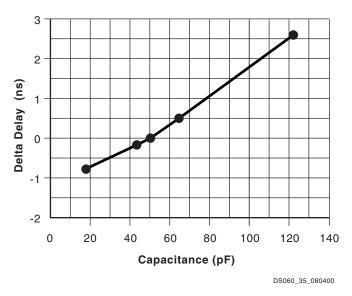

#### **Capacitive Load Factor**

Figure 34 shows the relationship between I/O output delay and load capacitance. It allows a user to adjust the specified output delay if the load capacitance is different than 50 pF. For example, if the actual load capacitance is 120 pF, add 2.5 ns to the specified delay. If the load capacitance is 20 pF, subtract 0.8 ns from the specified output delay. Figure 34 is usable over the specified operating conditions of voltage and temperature and is independent of the output slew rate control.

Figure 34: Delay Factor at Various Capacitive Loads

# **Spartan Family IOB Input Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature).

|                    |                                                         |             | -4   |      | -3   |      |       |

|--------------------|---------------------------------------------------------|-------------|------|------|------|------|-------|

| Symbol             | Description                                             | Device      | Min  | Max  | Min  | Max  | Units |

| Setup Tin          | nes - TTL Inputs <sup>(1)</sup>                         |             |      | •    | •    |      |       |

| T <sub>ECIK</sub>  | Clock Enable (EC) to Clock (IK), no delay               | All devices | 1.6  | -    | 2.1  | -    | ns    |

| T <sub>PICK</sub>  | Pad to Clock (IK), no delay                             | All devices | 1.5  | -    | 2.0  | -    | ns    |

| Hold Time          | es                                                      | ·           |      |      |      |      |       |

| T <sub>IKEC</sub>  | Clock Enable (EC) to Clock (IK), no delay               | All devices | 0.0  | -    | 0.9  | -    | ns    |

|                    | All Other Hold Times                                    | All devices | 0.0  | -    | 0.0  | -    | ns    |

| Propagat           | ion Delays - TTL Inputs <sup>(1)</sup>                  | ,           |      |      |      |      |       |

| T <sub>PID</sub>   | Pad to I1, I2                                           | All devices | -    | 1.5  | -    | 2.0  | ns    |

| T <sub>PLI</sub>   | Pad to I1, I2 via transparent input latch, no delay     | All devices | -    | 2.8  | -    | 3.6  | ns    |

| T <sub>IKRI</sub>  | Clock (IK) to I1, I2 (flip-flop)                        | All devices | -    | 2.7  | -    | 2.8  | ns    |

| T <sub>IKLI</sub>  | Clock (IK) to I1, I2 (latch enable, active Low)         | All devices | -    | 3.2  | -    | 3.9  | ns    |

| Delay Ad           | der for Input with Delay Option                         |             |      | I    | I    | II.  |       |

| T <sub>Delay</sub> | $T_{\text{ECIKD}} = T_{\text{ECIK}} + T_{\text{Delay}}$ | XCS05       | 3.6  | -    | 4.0  | -    | ns    |

|                    | $T_{PICKD} = T_{PICK} + T_{Delay}$                      | XCS10       | 3.7  | -    | 4.1  | -    | ns    |

|                    | $T_{PDLI} = T_{PLI} + T_{Delay}$                        | XCS20       | 3.8  | -    | 4.2  | -    | ns    |

|                    |                                                         | XCS30       | 4.5  | -    | 5.0  | -    | ns    |

|                    |                                                         | XCS40       | 5.5  | -    | 5.5  | -    | ns    |

| Global Se          | et/Reset                                                |             |      | I    | I    | II.  |       |

| $T_{MRW}$          | Minimum GSR pulse width                                 | All devices | 11.5 | -    | 13.5 | -    | ns    |

| T <sub>RRI</sub>   | Delay from GSR input to any Q                           | XCS05       |      | 9.0  | -    | 11.3 | ns    |

|                    |                                                         | XCS10       | -    | 9.5  | -    | 11.9 | ns    |

|                    |                                                         | XCS20       | -    | 10.0 | -    | 12.5 | ns    |

|                    |                                                         | XCS30       | -    | 10.5 | -    | 13.1 | ns    |

|                    |                                                         | XCS40       | -    | 11.0 | -    | 13.8 | ns    |

- 1. Delay adder for CMOS Inputs option: for -3 speed grade, add 0.4 ns; for -4 speed grade, add 0.2 ns.

- 2. Input pad setup and hold times are specified with respect to the internal clock (IK). For setup and hold times with respect to the clock input, see the pin-to-pin parameters in the Pin-to-Pin Input Parameters table.

- 3. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **Spartan Family IOB Output Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to

the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values are expressed in nanoseconds unless otherwise noted.

|                    |                                                    |             | -    | 4    | -    | 3    |       |

|--------------------|----------------------------------------------------|-------------|------|------|------|------|-------|

| Symbol             | Description                                        | Device      | Min  | Max  | Min  | Max  | Units |

| Clocks             |                                                    |             |      |      |      |      |       |

| T <sub>CH</sub>    | Clock High                                         | All devices | 3.0  | -    | 4.0  | -    | ns    |

| T <sub>CL</sub>    | Clock Low                                          | All devices | 3.0  | -    | 4.0  | -    | ns    |

| Propagation        | Delays - TTL Outputs <sup>(1,2)</sup>              |             |      |      |      |      |       |

| T <sub>OKPOF</sub> | Clock (OK) to Pad, fast                            | All devices | -    | 3.3  | -    | 4.5  | ns    |

| T <sub>OKPOS</sub> | Clock (OK to Pad, slew-rate limited                | All devices | -    | 6.9  | -    | 7.0  | ns    |

| T <sub>OPF</sub>   | Output (O) to Pad, fast                            | All devices | -    | 3.6  | -    | 4.8  | ns    |

| T <sub>OPS</sub>   | Output (O) to Pad, slew-rate limited               | All devices | -    | 7.2  | -    | 7.3  | ns    |

| T <sub>TSHZ</sub>  | 3-state to Pad High-Z (slew-rate independent)      | All devices | -    | 3.0  | -    | 3.8  | ns    |

| T <sub>TSONF</sub> | 3-state to Pad active and valid, fast              | All devices | -    | 6.0  | -    | 7.3  | ns    |

| T <sub>TSONS</sub> | 3-state to Pad active and valid, slew-rate limited | All devices | -    | 9.6  | -    | 9.8  | ns    |

| Setup and H        | old Times                                          |             | +    | +    | !    | -    |       |

| T <sub>OOK</sub>   | Output (O) to clock (OK) setup time                | All devices | 2.5  | -    | 3.8  | -    | ns    |

| T <sub>OKO</sub>   | Output (O) to clock (OK) hold time                 | All devices | 0.0  | -    | 0.0  | -    | ns    |

| T <sub>ECOK</sub>  | Clock Enable (EC) to clock (OK) setup time         | All devices | 2.0  | -    | 2.7  | -    | ns    |

| T <sub>OKEC</sub>  | Clock Enable (EC) to clock (OK) hold time          | All devices | 0.0  | -    | 0.5  | -    | ns    |

| Global Set/F       | Reset                                              | l           | 1    |      |      |      |       |

| $T_{MRW}$          | Minimum GSR pulse width                            | All devices | 11.5 |      | 13.5 |      | ns    |

| T <sub>RPO</sub>   | Delay from GSR input to any Pad                    | XCS05       | -    | 12.0 | -    | 15.0 | ns    |

|                    |                                                    | XCS10       | -    | 12.5 | -    | 15.7 | ns    |

|                    |                                                    | XCS20       | -    | 13.0 | -    | 16.2 | ns    |

|                    |                                                    | XCS30       | -    | 13.5 | -    | 16.9 | ns    |

|                    |                                                    | XCS40       | -    | 14.0 | -    | 17.5 | ns    |

- 1. Delay adder for CMOS Outputs option (with fast slew rate option): for -3 speed grade, add 1.0 ns; for -4 speed grade, add 0.8 ns.

- 2. Delay adder for CMOS Outputs option (with slow slew rate option): for -3 speed grade, add 2.0 ns; for -4 speed grade, add 1.5 ns.

- 3. Output timing is measured at ~50% V<sub>CC</sub> threshold, with 50 pF external capacitive loads including test fixture. Slew-rate limited output rise/fall times are approximately two times longer than fast output rise/fall times.

- 4. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **Spartan-XL Family IOB Input Switching Characteristic Guidelines**

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to the simulation netlist. These path delays, provided as a guideline, have been extracted from the static timing analyzer report. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature).

|                    |                                                     |             |      | Speed | Grade |      |       |

|--------------------|-----------------------------------------------------|-------------|------|-------|-------|------|-------|

|                    |                                                     |             | -    | 5     | -     | 4    |       |

| Symbol             | Description                                         | Device      | Min  | Max   | Min   | Max  | Units |

| Setup Tim          | es                                                  |             |      |       |       |      |       |

| T <sub>ECIK</sub>  | Clock Enable (EC) to Clock (IK)                     | All devices | 0.0  | -     | 0.0   | -    | ns    |

| T <sub>PICK</sub>  | Pad to Clock (IK), no delay                         | All devices | 1.0  | -     | 1.2   | -    | ns    |

| T <sub>POCK</sub>  | Pad to Fast Capture Latch Enable (OK), no delay     | All devices | 0.7  | -     | 0.8   | -    | ns    |

| Hold Time          | es                                                  |             |      |       | •     |      |       |

|                    | All Hold Times                                      | All devices | 0.0  | -     | 0.0   | -    | ns    |

| Propagati          | on Delays                                           |             |      |       | •     |      |       |

| T <sub>PID</sub>   | Pad to I1, I2                                       | All devices | -    | 0.9   | -     | 1.1  | ns    |

| T <sub>PLI</sub>   | Pad to I1, I2 via transparent input latch, no delay | All devices | -    | 2.1   | -     | 2.5  | ns    |

| T <sub>IKRI</sub>  | Clock (IK) to I1, I2 (flip-flop)                    | All devices | -    | 1.0   | -     | 1.1  | ns    |

| T <sub>IKLI</sub>  | Clock (IK) to I1, I2 (latch enable, active Low)     | All devices | -    | 1.1   | -     | 1.2  | ns    |

| Delay Add          | ler for Input with Full Delay Option                |             |      |       | •     |      |       |

| T <sub>Delay</sub> | $T_{PICKD} = T_{PICK} + T_{Delay}$                  | XCS05XL     | 4.0  | -     | 4.7   | -    | ns    |

|                    | $T_{PDLI} = T_{PLI} + T_{Delay}$                    | XCS10XL     | 4.8  | -     | 5.6   | -    | ns    |

|                    |                                                     | XCS20XL     | 5.0  | -     | 5.9   | -    | ns    |

|                    |                                                     | XCS30XL     | 5.5  | -     | 6.5   | -    | ns    |

|                    |                                                     | XCS40XL     | 6.5  | -     | 7.6   | -    | ns    |

| Global Se          | t/Reset                                             | "           |      | ı     | 1     | ı    | i.    |

| T <sub>MRW</sub>   | Minimum GSR pulse width                             | All devices | 10.5 | -     | 11.5  | -    | ns    |

| T <sub>RRI</sub>   | Delay from GSR input to any Q                       | XCS05XL     | -    | 9.0   | -     | 10.5 | ns    |

|                    |                                                     | XCS10XL     | -    | 9.5   | -     | 11.0 | ns    |

|                    |                                                     | XCS20XL     | -    | 10.0  | -     | 11.5 | ns    |

|                    |                                                     | XCS30XL     | -    | 11.0  | -     | 12.5 | ns    |

|                    |                                                     | XCS40XL     | -    | 12.0  | -     | 13.5 | ns    |

- 1. Input pad setup and hold times are specified with respect to the internal clock (IK). For setup and hold times with respect to the clock input, see the pin-to-pin parameters in the Pin-to-Pin Input Parameters table.

- 2. Voltage levels of unused pads, bonded or unbonded, must be valid logic levels. Each can be configured with the internal pull-up (default) or pull-down resistor, or configured as a driven output, or can be driven from an external source.

# **Device-Specific Pinout Tables**

Device-specific tables include all packages for each Spartan and Spartan-XL device. They follow the pad locations around the die, and include boundary scan register locations.

Some Spartan-XL devices are available in Pb-free package options. The Pb-free package options have the same pinouts as the standard package options.

# XCS05 and XCS05XL Device Pinouts

| XCS05/XL                                         | (A)                 |       | Bndry |

|--------------------------------------------------|---------------------|-------|-------|

| Pad Name                                         | PC84 <sup>(4)</sup> | VQ100 | Scan  |

| VCC                                              | P2                  | P89   | -     |

| I/O                                              | P3                  | P90   | 32    |

| I/O                                              | P4                  | P91   | 35    |

| I/O                                              | -                   | P92   | 38    |

| I/O                                              | -                   | P93   | 41    |

| I/O                                              | P5                  | P94   | 44    |

| I/O                                              | P6                  | P95   | 47    |

| I/O                                              | P7                  | P96   | 50    |

| I/O                                              | P8                  | P97   | 53    |

| I/O                                              | P9                  | P98   | 56    |

| I/O, SGCK1 <sup>(1)</sup> , GCK8 <sup>(2)</sup>  | P10                 | P99   | 59    |

| VCC                                              | P11                 | P100  | -     |

| GND                                              | P12                 | P1    | -     |

| I/O, PGCK1 <sup>(1)</sup> , GCK1 <sup>(2)</sup>  | P13                 | P2    | 62    |

| I/O                                              | P14                 | P3    | 65    |

| I/O, TDI                                         | P15                 | P4    | 68    |

| I/O, TCK                                         | P16                 | P5    | 71    |

| I/O, TMS                                         | P17                 | P6    | 74    |

| I/O                                              | P18                 | P7    | 77    |

| I/O                                              | -                   | P8    | 83    |

| I/O                                              | P19                 | P9    | 86    |

| I/O                                              | P20                 | P10   | 89    |

| GND                                              | P21                 | P11   | -     |

| VCC                                              | P22                 | P12   | -     |

| I/O                                              | P23                 | P13   | 92    |

| I/O                                              | P24                 | P14   | 95    |

| I/O                                              | -                   | P15   | 98    |

| I/O                                              | P25                 | P16   | 104   |

| I/O                                              | P26                 | P17   | 107   |

| I/O                                              | P27                 | P18   | 110   |

| I/O                                              | -                   | P19   | 113   |

| I/O                                              | P28                 | P20   | 116   |

| I/O, SGCK2 <sup>(1)</sup> , GCK2 <sup>(2)</sup>  | P29                 | P21   | 119   |

| Not Connected <sup>(1)</sup> , M1 <sup>(2)</sup> | P30                 | P22   | 122   |

| GND                                              | P31                 | P23   | -     |

| MODE <sup>(1)</sup> , M0 <sup>(2)</sup>          | P32                 | P24   | 125   |

| VCC                                              | P33                 | P25   | -     |

| 1                                                | 1                   |       | I.    |

# **XCS05 and XCS05XL Device Pinouts**

| XCS05/XL<br>Pad Name                            | PC84 <sup>(4)</sup> | VQ100 | Bndry<br>Scan      |

|-------------------------------------------------|---------------------|-------|--------------------|

| Not Connected <sup>(1)</sup> ,                  | P34                 | P26   | 126 <sup>(1)</sup> |

| PWRDWN <sup>(2)</sup>                           |                     | F20   |                    |

| I/O, PGCK2 <sup>(1)</sup> , GCK3 <sup>(2)</sup> | P35                 | P27   | 127 <sup>(3)</sup> |

| I/O (HDC)                                       | P36                 | P28   | 130 <sup>(3)</sup> |

| I/O                                             | -                   | P29   | 133 <sup>(3)</sup> |

| I/O (LDC)                                       | P37                 | P30   | 136 <sup>(3)</sup> |

| I/O                                             | P38                 | P31   | 139 <sup>(3)</sup> |

| I/O                                             | P39                 | P32   | 142 <sup>(3)</sup> |

| I/O                                             | -                   | P33   | 145 <sup>(3)</sup> |

| I/O                                             | -                   | P34   | 148 <sup>(3)</sup> |

| I/O                                             | P40                 | P35   | 151 <sup>(3)</sup> |

| I/O (ĪNĪT)                                      | P41                 | P36   | 154 <sup>(3)</sup> |

| VCC                                             | P42                 | P37   | -                  |

| GND                                             | P43                 | P38   | -                  |

| I/O                                             | P44                 | P39   | 157 <sup>(3)</sup> |

| I/O                                             | P45                 | P40   | 160 <sup>(3)</sup> |

| I/O                                             | -                   | P41   | 163 <sup>(3)</sup> |

| I/O                                             | -                   | P42   | 166 <sup>(3)</sup> |

| I/O                                             | P46                 | P43   | 169 <sup>(3)</sup> |

| I/O                                             | P47                 | P44   | 172 <sup>(3)</sup> |

| I/O                                             | P48                 | P45   | 175 <sup>(3)</sup> |

| I/O                                             | P49                 | P46   | 178 <sup>(3)</sup> |

| I/O                                             | P50                 | P47   | 181 <sup>(3)</sup> |

| I/O, SGCK3 <sup>(1)</sup> , GCK4 <sup>(2)</sup> | P51                 | P48   | 184 <sup>(3)</sup> |

| GND                                             | P52                 | P49   | -                  |

| DONE                                            | P53                 | P50   | -                  |

| VCC                                             | P54                 | P51   | -                  |

| PROGRAM                                         | P55                 | P52   | - (0)              |

| I/O (D7 <sup>(2)</sup> )                        | P56                 | P53   | 187 <sup>(3)</sup> |

| I/O, PGCK3 <sup>(1)</sup> , GCK5 <sup>(2)</sup> | P57                 | P54   | 190 <sup>(3)</sup> |

| I/O (D6 <sup>(2)</sup> )                        | P58                 | P55   | 193 <sup>(3)</sup> |

| I/O                                             | -                   | P56   | 196 <sup>(3)</sup> |

| I/O (D5 <sup>(2)</sup> )                        | P59                 | P57   | 199 <sup>(3)</sup> |

| I/O                                             | P60                 | P58   | 202 <sup>(3)</sup> |

| I/O                                             | -                   | P59   | 205 <sup>(3)</sup> |

| I/O                                             | -                   | P60   | 208 <sup>(3)</sup> |

| I/O (D4 <sup>(2)</sup> )                        | P61                 | P61   | 211(3)             |

| 1/0                                             | P62                 | P62   | 214 <sup>(3)</sup> |

| VCC                                             | P63                 | P63   | -                  |

| GND                                             | P64                 | P64   | -                  |

| I/O (D3 <sup>(2)</sup> )                        | P65                 | P65   | 217 <sup>(3)</sup> |

| 1/0                                             | P66                 | P66   | 220(3)             |

| 1/0                                             | -                   | P67   | 223 <sup>(3)</sup> |

| I/O (D2 <sup>(2)</sup> )                        | P67                 | P68   | 229 <sup>(3)</sup> |

| 1/0                                             | P68                 | P69   | 232 <sup>(3)</sup> |

| I/O (D1 <sup>(2)</sup> )                        | P69                 | P70   | 235 <sup>(3)</sup> |

# XCS05 and XCS05XL Device Pinouts

| XCS05/XL                                                  |                     |       | Bndry              |

|-----------------------------------------------------------|---------------------|-------|--------------------|

| Pad Name                                                  | PC84 <sup>(4)</sup> | VQ100 | Scan               |

| I/O                                                       | P70                 | P71   | 238 <sup>(3)</sup> |

| I/O (D0 <sup>(2)</sup> , DIN)                             | P71                 | P72   | 241 <sup>(3)</sup> |

| I/O, SGCK4 <sup>(1)</sup> , GCK6 <sup>(2)</sup><br>(DOUT) | P72                 | P73   | 244 <sup>(3)</sup> |

| CCLK                                                      | P73                 | P74   | -                  |

| VCC                                                       | P74                 | P75   | -                  |

| O, TDO                                                    | P75                 | P76   | 0                  |

| GND                                                       | P76                 | P77   | -                  |

| I/O                                                       | P77                 | P78   | 2                  |

| I/O, PGCK4 <sup>(1)</sup> , GCK7 <sup>(2)</sup>           | P78                 | P79   | 5                  |

| I/O (CS1 <sup>(2)</sup> )                                 | P79                 | P80   | 8                  |

| I/O                                                       | P80                 | P81   | 11                 |

| I/O                                                       | P81                 | P82   | 14                 |

| I/O                                                       | P82                 | P83   | 17                 |

| I/O                                                       | -                   | P84   | 20                 |

| I/O                                                       | -                   | P85   | 23                 |

| I/O                                                       | P83                 | P86   | 26                 |

| I/O                                                       | P84                 | P87   | 29                 |

| GND                                                       | P1                  | P88   | -                  |

#### Notes:

- 1. 5V Spartan family only

- 2. 3V Spartan-XL family only

- 3. The "PWRDWN" on the XCS05XL is not part of the Boundary Scan chain. For the XCS05XL, subtract 1 from all Boundary Scan numbers from GCK3 on (127 and higher).

- 4. PC84 package discontinued by PDN2004-01

# **XCS10 and XCS10XL Device Pinouts**

| XCS10/XL<br>Pad Name | PC84 <sup>(4)</sup> | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | Bndry<br>Scan |

|----------------------|---------------------|-------|------------------------|-------|---------------|

| VCC                  | P2                  | P89   | D7                     | P128  | -             |

| I/O                  | P3                  | P90   | A6                     | P129  | 44            |

| I/O                  | P4                  | P91   | В6                     | P130  | 47            |

| I/O                  | -                   | P92   | C6                     | P131  | 50            |

| I/O                  | -                   | P93   | D6                     | P132  | 53            |

| I/O                  | P5                  | P94   | A5                     | P133  | 56            |

| I/O                  | P6                  | P95   | B5                     | P134  | 59            |

| I/O                  | -                   | -     | C5                     | P135  | 62            |

| I/O                  | -                   | -     | D5                     | P136  | 65            |

| GND                  | -                   | -     | A4                     | P137  | -             |

| I/O                  | P7                  | P96   | B4                     | P138  | 68            |

| I/O                  | P8                  | P97   | C4                     | P139  | 71            |

| I/O                  | -                   | -     | A3                     | P140  | 74            |

| I/O                  | -                   | -     | В3                     | P141  | 77            |

| I/O                  | P9                  | P98   | C3                     | P142  | 80            |

# **XCS10 and XCS10XL Device Pinouts**

|                      |                     |       | vice Pino              |       | D             |

|----------------------|---------------------|-------|------------------------|-------|---------------|

| XCS10/XL<br>Pad Name | PC84 <sup>(4)</sup> | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | Bndry<br>Scan |

| I/O,                 | P10                 | P99   | A2                     | P143  | 83            |

| SGCK1 <sup>(1)</sup> |                     |       |                        |       |               |

| GCK8 <sup>(2)</sup>  |                     |       |                        |       |               |

| VCC                  | P11                 | P100  | B2                     | P144  | -             |

| GND                  | P12                 | P1    | A1                     | P1    | -             |

| I/O,                 | P13                 | P2    | B1                     | P2    | 86            |

| PGCK1 <sup>(1)</sup> |                     |       |                        |       |               |

| GCK1 <sup>(2)</sup>  |                     |       |                        |       |               |

| I/O                  | P14                 | P3    | C2                     | P3    | 89            |

| I/O                  | -                   | -     | C1                     | P4    | 92            |

| I/O                  | -                   | -     | D4                     | P5    | 95            |

| I/O, TDI             | P15                 | P4    | D3                     | P6    | 98            |

| I/O, TCK             | P16                 | P5    | D2                     | P7    | 101           |

| GND                  | -                   | -     | D1                     | P8    | ı             |

| I/O                  | -                   | _     | E4                     | P9    | 104           |

| I/O                  | -                   | -     | E3                     | P10   | 107           |

| I/O, TMS             | P17                 | P6    | E2                     | P11   | 110           |

| I/O                  | P18                 | P7    | E1                     | P12   | 113           |

| I/O                  | -                   | -     | F4                     | P13   | 116           |

| I/O                  | -                   | P8    | F3                     | P14   | 119           |

| I/O                  | P19                 | P9    | F2                     | P15   | 122           |

| I/O                  | P20                 | P10   | F1                     | P16   | 125           |

| GND                  | P21                 | P11   | G2                     | P17   | -             |

| VCC                  | P22                 | P12   | G1                     | P18   | -             |

| I/O                  | P23                 | P13   | G3                     | P19   | 128           |

| I/O                  | P24                 | P14   | G4                     | P20   | 131           |

| I/O                  | -                   | P15   | H1                     | P21   | 134           |

| I/O                  | -                   | -     | H2                     | P22   | 137           |

| I/O                  | P25                 | P16   | H3                     | P23   | 140           |

| I/O                  | P26                 | P17   | H4                     | P24   | 143           |

| I/O                  | -                   | -     | J1                     | P25   | 146           |

| I/O                  | -                   | -     | J2                     | P26   | 149           |

| GND                  | -                   | -     | J3                     | P27   | -             |

| I/O                  | P27                 | P18   | J4                     | P28   | 152           |

| I/O                  | -                   | P19   | K1                     | P29   | 155           |

| I/O                  | _                   | -     | K2                     | P30   | 158           |

| I/O                  | _                   | _     | K3                     | P31   | 161           |

| I/O                  | P28                 | P20   | L1                     | P32   | 164           |

| I/O,                 | P29                 | P21   | L2                     | P33   | 167           |

| SGCK2 <sup>(1)</sup> | 1 23                | 1 - 1 | L                      | . 00  | 107           |

| GCK2 <sup>(2)</sup>  |                     |       |                        |       |               |

| Not                  | P30                 | P22   | L3                     | P34   | 170           |

| Connect-             |                     |       |                        |       |               |

| ed <sup>(1)</sup>    |                     |       |                        |       |               |

| M1 <sup>(2)</sup>    |                     |       |                        |       |               |

| GND                  | P31                 | P23   | M1                     | P35   | -             |

| $MODE^{(1)}$ ,       | P32                 | P24   | M2                     | P36   | 173           |

| M0 <sup>(2)</sup>    |                     |       |                        |       |               |

# **XCS10 and XCS10XL Device Pinouts**

| XCS10/XL<br>Pad Name | PC84 <sup>(4)</sup> | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | Bndry<br>Scan |

|----------------------|---------------------|-------|------------------------|-------|---------------|

| I/O                  | P80                 | P81   | A10                    | P116  | 17            |

| GND                  | -                   | -     | C9                     | P118  | -             |

| I/O                  | -                   | -     | B9                     | P119  | 20            |

| I/O                  | -                   | -     | A9                     | P120  | 23            |

| I/O                  | P81                 | P82   | D8                     | P121  | 26            |

| I/O                  | P82                 | P83   | C8                     | P122  | 29            |

| I/O                  | -                   | P84   | B8                     | P123  | 32            |

| I/O                  | -                   | P85   | A8                     | P124  | 35            |

| I/O                  | P83                 | P86   | B7                     | P125  | 38            |

| I/O                  | P84                 | P87   | A7                     | P126  | 41            |

| GND                  | P1                  | P88   | C7                     | P127  | -             |

#### Notes:

- 1. 5V Spartan family only

- 2. 3V Spartan-XL family only

- 3. The "PWRDWN" on the XCS10XL is not part of the Boundary Scan chain. For the XCS10XL, subtract 1 from all Boundary Scan numbers from GCK3 on (175 and higher).

- 4. PC84 and CS144 packages discontinued by PDN2004-01

# Additional XCS10/XL Package Pins

| TQ144              |   |   |   |   |   |  |

|--------------------|---|---|---|---|---|--|

| Not Connected Pins |   |   |   |   |   |  |

| P117               | - | - | - | - | - |  |

| 5/5/97             |   |   |   |   |   |  |

| CS144              |   |   |   |   |   |  |  |

|--------------------|---|---|---|---|---|--|--|

| Not Connected Pins |   |   |   |   |   |  |  |

| D9                 | - | - | - | - | - |  |  |

| 4/28/99            |   |   |   |   |   |  |  |

# XCS20 and XCS20XL Device Pinouts

| XCS20/XL           |       |                        |       |       | Bndry |

|--------------------|-------|------------------------|-------|-------|-------|

| Pad Name           | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Scan  |

| VCC                | P89   | D7                     | P128  | P183  | -     |

| I/O                | P90   | A6                     | P129  | P184  | 62    |

| I/O                | P91   | B6                     | P130  | P185  | 65    |

| I/O                | P92   | C6                     | P131  | P186  | 68    |

| I/O                | P93   | D6                     | P132  | P187  | 71    |

| I/O                | -     | -                      | -     | P188  | 74    |

| I/O                | -     | -                      | -     | P189  | 77    |

| I/O                | P94   | A5                     | P133  | P190  | 80    |

| I/O                | P95   | B5                     | P134  | P191  | 83    |

| VCC <sup>(2)</sup> | -     | -                      | -     | P192  | -     |

| I/O                | -     | C5                     | P135  | P193  | 86    |

| I/O                | -     | D5                     | P136  | P194  | 89    |

| GND                | -     | A4                     | P137  | P195  | -     |

| I/O                | -     | -                      | -     | P196  | 92    |

| I/O                | -     | -                      | -     | P197  | 95    |

| I/O                | -     | -                      | -     | P198  | 98    |

| I/O                | -     | -                      | -     | P199  | 101   |

| I/O                | P96   | B4                     | P138  | P200  | 104   |

| I/O                | P97   | C4                     | P139  | P201  | 107   |

| I/O                | -     | А3                     | P140  | P204  | 110   |

| I/O                | -     | B3                     | P141  | P205  | 113   |

| I/O                | P98   | C3                     | P142  | P206  | 116   |

# **XCS20 and XCS20XL Device Pinouts**

| XCS20/XL                                              | V0400 | CS144 <sup>(2,4)</sup> | TO444 | DOGGG | Bndry |

|-------------------------------------------------------|-------|------------------------|-------|-------|-------|

| Pad Name                                              | VQ100 |                        | TQ144 | PQ208 | Scan  |

| I/O,<br>SGCK1 <sup>(1)</sup> ,<br>GCK8 <sup>(2)</sup> | P99   | A2                     | P143  | P207  | 119   |

| VCC                                                   | P100  | B2                     | P144  | P208  | -     |

| GND                                                   | P1    | A1                     | P1    | P1    | -     |

| I/O,<br>PGCK1 <sup>(1)</sup> ,<br>GCK1 <sup>(2)</sup> | P2    | B1                     | P2    | P2    | 122   |

| I/O                                                   | P3    | C2                     | P3    | P3    | 125   |

| I/O                                                   | -     | C1                     | P4    | P4    | 128   |

| I/O                                                   | -     | D4                     | P5    | P5    | 131   |

| I/O, TDI                                              | P4    | D3                     | P6    | P6    | 134   |

| I/O, TCK                                              | P5    | D2                     | P7    | P7    | 137   |

| I/O                                                   | -     | -                      | -     | P8    | 140   |

| I/O                                                   | -     | -                      | -     | P9    | 143   |

| I/O                                                   | -     | -                      | -     | P10   | 146   |

| I/O                                                   | -     | -                      | -     | P11   | 149   |

| GND                                                   | -     | D1                     | P8    | P13   | -     |

| I/O                                                   | -     | E4                     | P9    | P14   | 152   |

| I/O                                                   | -     | E3                     | P10   | P15   | 155   |

| I/O, TMS                                              | P6    | E2                     | P11   | P16   | 158   |

| I/O                                                   | P7    | E1                     | P12   | P17   | 161   |

| VCC <sup>(2)</sup>                                    | -     | -                      | -     | P18   | -     |

| I/O                                                   | -     | -                      | -     | P19   | 164   |

| I/O                                                   | -     | -                      | -     | P20   | 167   |

# **XCS20 and XCS20XL Device Pinouts**

|                                               | 20 and XCS20XL Device Pinouts |                        |       |       |                    |  |  |

|-----------------------------------------------|-------------------------------|------------------------|-------|-------|--------------------|--|--|

| XCS20/XL<br>Pad Name                          | VQ100                         | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |  |  |

| PROGRAM                                       | P52                           | M13                    | P74   | P106  | -                  |  |  |

| I/O (D7 <sup>(2)</sup> )                      | P53                           | L12                    | P75   | P107  | 367 <sup>(3)</sup> |  |  |

| I/O,                                          | P54                           | L13                    | P76   | P108  | 370 <sup>(3)</sup> |  |  |

| PGCK3 <sup>(1)</sup> ,<br>GCK5 <sup>(2)</sup> |                               |                        |       |       |                    |  |  |

| I/O                                           |                               | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |

| 1/0                                           | -                             | K10                    | P77   | P109  | 373 <sup>(3)</sup> |  |  |

| I/O (D6 <sup>(2)</sup> )                      | -<br>P55                      | K11                    | P79   | P110  | 379 <sup>(3)</sup> |  |  |

| I/O (D6(=/)                                   |                               | K12                    |       | P112  | 382 (3)            |  |  |

|                                               | P56                           | NIS                    | P80   |       | 385 (3)            |  |  |

| 1/0                                           | -                             | -                      | -     | P114  |                    |  |  |

| 1/0                                           | -                             | -                      | -     | P115  | 388 (3)            |  |  |

| 1/0                                           | -                             | -                      | -     | P116  | 391 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P117  | 394 <sup>(3)</sup> |  |  |

| GND                                           | -                             | J10                    | P81   | P118  | - (2)              |  |  |

| I/O                                           | -                             | J11                    | P82   | P119  | 397 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | J12                    | P83   | P120  | 400 (3)            |  |  |

| VCC <sup>(2)</sup>                            | -                             | -                      | -     | P121  | - (0)              |  |  |

| I/O (D5 <sup>(2)</sup> )                      | P57                           | J13                    | P84   | P122  | 403 (3)            |  |  |

| I/O                                           | P58                           | H10                    | P85   | P123  | 406 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P124  | 409 (3)            |  |  |

| I/O                                           | -                             | -                      | -     | P125  | 412 <sup>(3)</sup> |  |  |

| I/O                                           | P59                           | H11                    | P86   | P126  | 415 <sup>(3)</sup> |  |  |

| I/O                                           | P60                           | H12                    | P87   | P127  | 418 <sup>(3)</sup> |  |  |

| I/O (D4 <sup>(2)</sup> )                      | P61                           | H13                    | P88   | P128  | 421 <sup>(3)</sup> |  |  |

| I/O                                           | P62                           | G12                    | P89   | P129  | 424 <sup>(3)</sup> |  |  |

| VCC                                           | P63                           | G13                    | P90   | P130  | -                  |  |  |

| GND                                           | P64                           | G11                    | P91   | P131  | -                  |  |  |

| I/O (D3 <sup>(2)</sup> )                      | P65                           | G10                    | P92   | P132  | 427 <sup>(3)</sup> |  |  |

| I/O                                           | P66                           | F13                    | P93   | P133  | 430 <sup>(3)</sup> |  |  |

| I/O                                           | P67                           | F12                    | P94   | P134  | 433 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | F11                    | P95   | P135  | 436 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P136  | 439 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P137  | 442 (3)            |  |  |

| I/O (D2 <sup>(2)</sup> )                      | P68                           | F10                    | P96   | P138  | 445 <sup>(3)</sup> |  |  |

| I/O                                           | P69                           | E13                    | P97   | P139  | 448 <sup>(3)</sup> |  |  |

| VCC <sup>(2)</sup>                            | -                             | -                      | -     | P140  | -                  |  |  |

| I/O                                           | _                             | E12                    | P98   | P141  | 451 <sup>(3)</sup> |  |  |

| I/O                                           | _                             | E11                    | P99   | P142  | 454 <sup>(3)</sup> |  |  |

| GND                                           | -                             | E10                    | P100  | P143  | -                  |  |  |

| I/O                                           | -                             | -                      | -     | P145  | 457 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P146  | 460 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P147  | 463 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | -                      | -     | P148  | 466 <sup>(3)</sup> |  |  |

| I/O (D1 <sup>(2)</sup> )                      | P70                           | D13                    | P101  | P149  | 469 <sup>(3)</sup> |  |  |

| I/O                                           | P71                           | D12                    | P102  | P150  | 472 <sup>(3)</sup> |  |  |

| I/O                                           | -                             | D11                    | P103  | P151  | 475 <sup>(3)</sup> |  |  |

# **XCS20 and XCS20XL Device Pinouts**

| XCS20/XL<br>Pad Name                                            | VQ100 | CS144 <sup>(2,4)</sup> | TQ144 | PQ208 | Bndry<br>Scan      |

|-----------------------------------------------------------------|-------|------------------------|-------|-------|--------------------|

| I/O                                                             | -     | C13                    | P104  | P152  | 478 <sup>(3)</sup> |

| I/O<br>(D0 <sup>(2)</sup> , DIN)                                | P72   | C12                    | P105  | P153  | 481 <sup>(3)</sup> |

| I/O,<br>SGCK4 <sup>(1)</sup> ,<br>GCK6 <sup>(2)</sup><br>(DOUT) | P73   | C11                    | P106  | P154  | 484 <sup>(3)</sup> |

| CCLK                                                            | P74   | B13                    | P107  | P155  | -                  |

| VCC                                                             | P75   | B12                    | P108  | P156  | -                  |