Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details |

|---------|

|---------|

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | 768                                                            |

| Number of Logic Elements/Cells | ·                                                              |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 69                                                             |

| Number of Gates                | 12000                                                          |

| Voltage - Supply               | 3V ~ 3.6V, 4.75V ~ 5.25V                                       |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 85°C (TA)                                              |

| Package / Case                 | 84-LCC (J-Lead)                                                |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a54sx08-2plg84i |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DirectConnect is a horizontal routing resource that provides connections from a C-cell to its neighboring Rcell in a given SuperCluster. DirectConnect uses a hardwired signal path requiring no programmable interconnection to achieve its fast signal propagation time of less than 0.1 ns.

FastConnect enables horizontal routing between any two logic modules within a given SuperCluster and vertical routing with the SuperCluster immediately below it. Only one programmable connection is used in a FastConnect path, delivering maximum pin-to-pin propagation of 0.4 ns.

In addition to DirectConnect and FastConnect, the architecture makes use of two globally oriented routing resources known as segmented routing and high-drive routing. The Actel segmented routing structure provides a variety of track lengths for extremely fast routing between SuperClusters. The exact combination of track lengths and antifuses within each path is chosen by the 100 percent automatic place-and-route software to minimize signal propagation delays.

The Actel high-drive routing structure provides three clock networks. The first clock, called HCLK, is hardwired from the HCLK buffer to the clock select multiplexer (MUX) in each R-cell. This provides a fast propagation path for the clock signal, enabling the 3.7 ns clock-to-out (pin-to-pin) performance of the SX devices. The hardwired clock is tuned to provide clock skew as low as 0.25 ns. The remaining two clocks (CLKA, CLKB) are global clocks that can be sourced from external pins or from internal logic signals within the SX device.

### **Other Architectural Features**

#### Technology

The Actel SX family is implemented on a high-voltage twin-well CMOS process using 0.35  $\mu$  design rules. The metal-to-metal antifuse is made up of a combination of amorphous silicon and dielectric material with barrier metals and has a programmed ("on" state) resistance of 25  $\Omega$  with a capacitance of 1.0 fF for low signal impedance.

#### Performance

The combination of architectural features described above enables SX devices to operate with internal clock frequencies exceeding 300 MHz, enabling very fast execution of even complex logic functions. Thus, the SX family is an optimal platform upon which to integrate the functionality previously contained in multiple CPLDs. In addition, designs that previously would have required a gate array to meet performance goals can now be integrated into an SX device with dramatic improvements in cost and time to market. Using timingdriven place-and-route tools, designers can achieve highly deterministic device performance. With SX devices, designers do not need to use complicated performance-enhancing design techniques such as the use of redundant logic to reduce fanout on critical nets or the instantiation of macros in HDL code to achieve high performance.

#### I/O Modules

Each I/O on an SX device can be configured as an input, an output, a tristate output, or a bidirectional pin.

Even without the inclusion of dedicated I/O registers, these I/Os, in combination with array registers, can achieve clock-to-out (pad-to-pad) timing as fast as 3.7 ns. I/O cells that have embedded latches and flip-flops require instantiation in HDL code; this is a design complication not encountered in SX FPGAs. Fast pin-to-pin timing ensures that the device will have little trouble interfacing with any other device in the system, which in turn enables parallel design of system components and reduces overall design time.

#### **Power Requirements**

The SX family supports 3.3 V operation and is designed to tolerate 5.0 V inputs. (Table 1-1). Power consumption is extremely low due to the very short distances signals are required to travel to complete a circuit. Power requirements are further reduced because of the small number of low-resistance antifuses in the path. The antifuse architecture does not require active circuitry to hold a charge (as do SRAM or EPROM), making it the lowest power architecture on the market.

| Denter                        |                  | V                | V                |                         | Maniana Outrat Daire |

|-------------------------------|------------------|------------------|------------------|-------------------------|----------------------|

| Device                        | V <sub>CCA</sub> | V <sub>CCI</sub> | V <sub>CCR</sub> | Maximum Input Tolerance | Maximum Output Drive |

| A54SX08<br>A54SX16<br>A54SX32 | 3.3 V            | 3.3 V            | 5.0 V            | 5.0 V                   | 3.3 V                |

| A54SX16-P*                    | 3.3 V            | 3.3 V            | 3.3 V            | 3.3 V                   | 3.3 V                |

|                               | 3.3 V            | 3.3 V            | 5.0 V            | 5.0 V                   | 3.3 V                |

|                               | 3.3 V            | 5.0 V            | 5.0 V            | 5.0 V                   | 5.0 V                |

**Note:** \*A54SX16-P has three different entries because it is capable of both a 3.3 V and a 5.0 V drive.

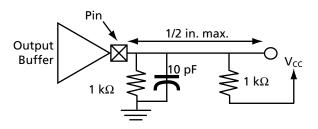

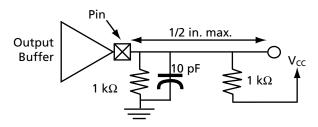

Figure 1-8 • Probe Setup

### Programming

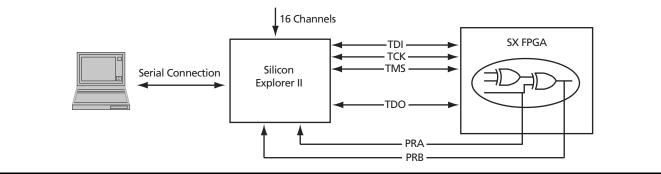

Device programming is supported through Silicon Sculptor series of programmers. In particular, Silicon Sculptor II are compact, robust, single-site and multi-site device programmer for the PC.

With standalone software, Silicon Sculptor II allows concurrent programming of multiple units from the same PC, ensuring the fastest programming times possible. Each fuse is subsequently verified by Silicon Sculptor II to insure correct programming. In addition, integrity tests ensure that no extra fuses are programmed. Silicon Sculptor II also provides extensive hardware self-testing capability. The procedure for programming an SX device using Silicon Sculptor II are as follows:

- 1. Load the .AFM file

- 2. Select the device to be programmed

- 3. Begin programming

When the design is ready to go to production, Actel offers device volume-programming services either through distribution partners or via in-house programming from the factory.

For more details on programming SX devices, refer to the *Programming Antifuse Devices* application note and the *Silicon Sculptor II User's Guide*.

### **3.3 V / 5 V Operating Conditions** *Table 1-3* • Absolute Maximum Ratings<sup>1</sup>

| Symbol                        | Parameter                                     | Limits        | Units |

|-------------------------------|-----------------------------------------------|---------------|-------|

| V <sub>CCR</sub> <sup>2</sup> | DC Supply Voltage <sup>3</sup>                | -0.3 to + 6.0 | V     |

| V <sub>CCA</sub> <sup>2</sup> | DC Supply Voltage                             | -0.3 to + 4.0 | V     |

| V <sub>CCI</sub> <sup>2</sup> | DC Supply Voltage (A54SX08, A54SX16, A54SX32) | -0.3 to + 4.0 | V     |

| V <sub>CCI</sub> <sup>2</sup> | DC Supply Voltage (A54SX16P)                  | -0.3 to + 6.0 | V     |

| VI                            | Input Voltage                                 | -0.5 to + 5.5 | V     |

| V <sub>O</sub>                | Output Voltage                                | -0.5 to + 3.6 | V     |

| I <sub>IO</sub>               | I/O Source Sink Current <sup>3</sup>          | -30 to + 5.0  | mA    |

| T <sub>STG</sub>              | Storage Temperature                           | -65 to +150   | °C    |

Notes:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

2.  $V_{CCR}$  in the A54SX16P must be greater than or equal to  $V_{CCI}$  during power-up and power-down sequences and during normal operation.

3. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than  $V_{CC}$  + 0.5 V or less than GND – 0.5 V, the internal protection diodes will forward-bias and can draw excessive current.

# A54SX16P AC Specifications for (PCI Operation)

| Symbol              | Parameter              | Condition                        | Min.                                 | Max.                | Units |

|---------------------|------------------------|----------------------------------|--------------------------------------|---------------------|-------|

| I <sub>OH(AC)</sub> | Switching Current High | $0 < V_{OUT} \le 1.4^{1}$        | -44                                  |                     | mA    |

|                     |                        | $1.4 \le V_{OUT} < 2.4^{1, 2}$   | -44 + (V <sub>OUT</sub> - 1.4)/0.024 |                     | mA    |

|                     |                        | $3.1 < V_{OUT} < V_{CC}^{1, 3}$  |                                      | EQ 1-1 on page 1-11 |       |

|                     | (Test Point)           | $V_{OUT} = 3.1^{3}$              |                                      | -142                | mA    |

| I <sub>OL(AC)</sub> | Switching Current High | $V_{OUT} \ge 2.2^{1}$            | 95                                   |                     | mA    |

|                     |                        | $2.2 > V_{OUT} > 0.55^{1}$       | V <sub>OUT</sub> /0.023              |                     |       |

|                     |                        | $0.71 > V_{OUT} > 0^{1, 3}$      |                                      | EQ 1-2 on page 1-11 | mA    |

|                     | (Test Point)           | $V_{OUT} = 0.71^{3}$             |                                      | 206                 | mA    |

| I <sub>CL</sub>     | Low Clamp Current      | $-5 < V_{IN} \leq -1$            | -25 + (V <sub>IN</sub> + 1)/0.015    |                     | mA    |

| slew <sub>R</sub>   | Output Rise Slew Rate  | 0.4 V to 2.4 V load <sup>4</sup> | 1                                    | 5                   | V/ns  |

| slew <sub>F</sub>   | Output Fall Slew Rate  | 2.4 V to 0.4 V load <sup>4</sup> | 1                                    | 5                   | V/ns  |

#### Table 1-7 A54SX16P AC Specifications for (PCI Operation)

#### Notes:

1. Refer to the V/I curves in Figure 1-9 on page 1-11. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here; i.e., half-size output drivers may be used on these signals. This specification does not apply to CLK and RST#, which are system outputs. "Switching Current High" specifications are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD#, which are open drain outputs.

2. Note that this segment of the minimum current curve is drawn from the AC drive point directly to the DC drive point rather than toward the voltage rail (as is done in the pull-down curve). This difference is intended to allow for an optional N-channel pull-up.

3. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (A and B) are provided with the respective diagrams in Figure 1-9 on page 1-11. The equation defined maxima should be met by design. In order to facilitate component testing, a maximum current test point is defined for each side of the output driver.

4. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an unloaded output per revision 2.0 of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is now required (the maximum is no longer simply a guideline). Since adherence to the maximum slew rate was not required prior to revision 2.1 of the specification, there may be components in the market for some time that have faster edge rates; therefore, motherboard designers must bear in mind that rise and fall times faster than this specification could occur, and should ensure that signal integrity modeling accounts for this. Rise slew rate does not apply to open drain outputs.

# A54SX16P DC Specifications (3.3 V PCI Operation)

| Symbol             | Parameter                                    | Condition                  | Min.               | Max.               | Units |

|--------------------|----------------------------------------------|----------------------------|--------------------|--------------------|-------|

| V <sub>CCA</sub>   | Supply Voltage for Array                     |                            | 3.0                | 3.6                | V     |

| V <sub>CCR</sub>   | Supply Voltage required for Internal Biasing |                            | 3.0                | 3.6                | V     |

| V <sub>CCI</sub>   | Supply Voltage for I/Os                      |                            | 3.0                | 3.6                | V     |

| $V_{\text{IH}}$    | Input High Voltage                           |                            | 0.5V <sub>CC</sub> | $V_{CC} + 0.5$     | V     |

| V <sub>IL</sub>    | Input Low Voltage                            |                            | -0.5               | 0.3V <sub>CC</sub> | V     |

| I <sub>IPU</sub>   | Input Pull-up Voltage <sup>1</sup>           |                            | 0.7V <sub>CC</sub> |                    | V     |

| IIL                | Input Leakage Current <sup>2</sup>           | $0 < V_{IN} < V_{CC}$      |                    | ±10                | μA    |

| V <sub>OH</sub>    | Output High Voltage                          | I <sub>OUT</sub> = –500 μA | 0.9V <sub>CC</sub> |                    | V     |

| V <sub>OL</sub>    | Output Low Voltage                           | I <sub>OUT</sub> = 1500 μA |                    | 0.1V <sub>CC</sub> | V     |

| C <sub>IN</sub>    | Input Pin Capacitance <sup>3</sup>           |                            |                    | 10                 | pF    |

| C <sub>CLK</sub>   | CLK Pin Capacitance                          |                            | 5                  | 12                 | pF    |

| C <sub>IDSEL</sub> | IDSEL Pin Capacitance <sup>4</sup>           |                            |                    | 8                  | pF    |

Table 1-8 • A54SX16P DC Specifications (3.3 V PCI Operation)

Notes:

1. This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Applications sensitive to static power utilization should assure that the input buffer is conducting minimum current at this input voltage.

2. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

3. Absolute maximum pin capacitance for a PCI input is 10 pF (except for CLK).

4. Lower capacitance on this input-only pin allows for non-resistive coupling to AD[xx].

# A54SX16P AC Specifications (3.3 V PCI Operation)

| Symbol              | Parameter                          | Condition                                | Min.                                                | Max.                | Units |

|---------------------|------------------------------------|------------------------------------------|-----------------------------------------------------|---------------------|-------|

|                     | Switching Current High             | $0 < V_{OUT} \le 0.3 V_{CC}^{1}$         |                                                     |                     | mA    |

| 1                   |                                    | $0.3V_{CC} \le V_{OUT} < 0.9V_{CC}^{-1}$ | -12V <sub>CC</sub>                                  |                     | mA    |

| IOH(AC)             |                                    | $0.7V_{CC} < V_{OUT} < V_{CC}^{1, 2}$    | –17.1 + (V <sub>CC</sub> – V <sub>OUT</sub> )       | EQ 1-3 on page 1-14 |       |

|                     | (Test Point)                       | $V_{OUT} = 0.7 V_{CC}^2$                 |                                                     | -32V <sub>CC</sub>  | mA    |

|                     | Switching Current High             | $V_{CC} > V_{OUT} \ge 0.6 V_{CC}^{1}$    |                                                     |                     | mA    |

| 1                   |                                    | $0.6V_{CC} > V_{OUT} > 0.1V_{CC}^{1}$    | 16V <sub>CC</sub>                                   |                     | mA    |

| I <sub>OL(AC)</sub> |                                    | $0.18V_{CC} > V_{OUT} > 0^{1, 2}$        | 26.7V <sub>OUT</sub>                                | EQ 1-4 on page 1-14 | mA    |

|                     | (Test Point)                       | $V_{OUT} = 0.18 V_{CC}^2$                |                                                     | 38V <sub>CC</sub>   |       |

| I <sub>CL</sub>     | Low Clamp Current                  | $-3 < V_{IN} \le -1$                     | -25 + (V <sub>IN</sub> + 1)/0.015                   |                     | mA    |

| I <sub>CH</sub>     | High Clamp Current                 | $-3 < V_{IN} \le -1$                     | 25 + (V <sub>IN</sub> – V <sub>OUT</sub> – 1)/0.015 |                     | mA    |

| slew <sub>R</sub>   | Output Rise Slew Rate <sup>3</sup> | $0.2V_{CC}$ to $0.6V_{CC}$ load          | 1                                                   | 4                   | V/ns  |

| slew <sub>F</sub>   | Output Fall Slew Rate <sup>3</sup> | $0.6V_{CC}$ to $0.2V_{CC}$ load          | 1                                                   | 4                   | V/ns  |

#### Table 1-9 • A54SX16P AC Specifications (3.3 V PCI Operation)

Notes:

1. Refer to the V/I curves in Figure 1-10 on page 1-14. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here; i.e., half size output drivers may be used on these signals. This specification does not apply to CLK and RST# which are system outputs. "Switching Current High" specification are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD# which are open drain outputs.

2. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (C and D) are provided with the respective diagrams in Figure 1-10 on page 1-14. The equation defined maxima should be met by design. In order to facilitate component testing, a maximum current test point is defined for each side of the output driver.

3. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an unloaded output per the latest revision of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is required (the maximum is no longer simply a guideline). Rise slew rate does not apply to open drain outputs.

# **Power-Up Sequencing**

Table 1-10Power-Up Sequencing

| V <sub>CCA</sub> | V <sub>CCR</sub> | V <sub>CCI</sub> | Power-Up Sequence           | Comments                     |

|------------------|------------------|------------------|-----------------------------|------------------------------|

| A54SX08, A549    | X16, A54SX32     |                  |                             |                              |

| 3.3 V            | 5.0 V            | 3.3 V            | 5.0 V First<br>3.3 V Second | No possible damage to device |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | Possible damage to device    |

| A54SX16P         |                  |                  |                             |                              |

| 3.3 V            | 3.3 V            | 3.3 V            | 3.3 V Only                  | No possible damage to device |

| 3.3 V            | 5.0 V            | 3.3 V            | 5.0 V First<br>3.3 V Second | No possible damage to device |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | Possible damage to device    |

| 3.3 V            | 5.0 V            | 5.0 V            | 5.0 V First<br>3.3 V Second | No possible damage to device |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | No possible damage to device |

*Note:* No inputs should be driven (high or low) before completion of power-up.

# **Power-Down Sequencing**

#### Table 1-11Power-Down Sequencing

| V <sub>CCA</sub> | V <sub>CCR</sub> | V <sub>CCI</sub> | Power-Down Sequence         | Comments                     |

|------------------|------------------|------------------|-----------------------------|------------------------------|

| A54SX08, A549    | 5X16, A54SX32    |                  |                             |                              |

| 3.3 V            | 5.0 V            | 3.3 V            | 5.0 V First<br>3.3 V Second | Possible damage to device    |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | No possible damage to device |

| A54SX16P         |                  |                  | ·                           |                              |

| 3.3 V            | 3.3 V            | 3.3 V            | 3.3 V Only                  | No possible damage to device |

| 3.3 V            | 5.0 V            | 3.3 V            | 5.0 V First<br>3.3 V Second | Possible damage to device    |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | No possible damage to device |

| 3.3 V            | 5.0 V            | 5.0 V            | 5.0 V First<br>3.3 V Second | No possible damage to device |

|                  |                  |                  | 3.3 V First<br>5.0 V Second | No possible damage to device |

**Note:** No inputs should be driven (high or low) after the beginning of the power-down sequence.

#### **SX Family FPGAs**

#### Step 1: Define Terms Used in Formula

v

22

|                                                                                  | $V_{CCA}$         | 3.3       |

|----------------------------------------------------------------------------------|-------------------|-----------|

| Module                                                                           |                   |           |

| Number of logic modules switching<br>at f <sub>m</sub> (Used 50%)                | m                 | 264       |

| Average logic modules switching rate<br>f <sub>m</sub> (MHz) (Guidelines: f/10)  | f <sub>m</sub>    | 20        |

| Module capacitance C <sub>EQM</sub> (pF)                                         | C <sub>EQM</sub>  | 4.0       |

| Input Buffer                                                                     |                   |           |

| Number of input buffers switching at f <sub>n</sub>                              | n                 | 1         |

| Average input switching rate f <sub>n</sub> (MHz)<br>(Guidelines: f/5)           | f <sub>n</sub>    | 40        |

| Input buffer capacitance C <sub>EQI</sub> (pF)                                   | C <sub>EQI</sub>  | 3.4       |

| Output Buffer                                                                    |                   |           |

| Number of output buffers switching at fp                                         | р                 | 1         |

| Average output buffers switching rate<br>f <sub>p</sub> (MHz) (Guidelines: f/10) | $f_p$             | 20        |

| Output buffers buffer capacitance<br>C <sub>EQO</sub> (pF)                       | C <sub>EQO</sub>  | 4.7       |

| Output Load capacitance C <sub>L</sub> (pF)                                      | CL                | 35        |

| RCLKA                                                                            |                   |           |

| Number of Clock loads q <sub>1</sub>                                             | q <sub>1</sub>    | 528       |

| Capacitance of routed array clock (pF)                                           | C <sub>EQCR</sub> | 1.6       |

| Average clock rate (MHz)                                                         | f <sub>q1</sub>   | 200       |

| Fixed capacitance (pF)                                                           | r <sub>1</sub>    | 138       |

| RCLKB                                                                            |                   |           |

| Number of Clock loads q <sub>2</sub>                                             | q <sub>2</sub>    | 0         |

| Capacitance of routed array clock (pF)                                           | C <sub>EQCR</sub> | 1.6       |

| Average clock rate (MHz)                                                         | f <sub>q2</sub>   | 0         |

| Fixed capacitance (pF)                                                           | r <sub>2</sub>    | 138       |

| HCLK                                                                             |                   |           |

| Number of Clock loads                                                            | s <sub>1</sub>    | 0         |

| Variable capacitance of dedicated<br>array clock (pF)                            | C <sub>EQHV</sub> | 0.61<br>5 |

| Fixed capacitance of dedicated<br>array clock (pF)                               | C <sub>EQHF</sub> | 96        |

| Average clock rate (MHz)                                                         | f <sub>s1</sub>   | 0         |

#### Step 2: Calculate Dynamic Power Consumption

| $V_{CCA} \times V_{CCA}$                                             | 10.89    |

|----------------------------------------------------------------------|----------|

| $m \times f_m \times C_{EQM}$                                        | 0.02112  |

| $n \times f_n \times C_{EQI}$                                        | 0.000136 |

| $p \times f_p \times (C_{EQO}+C_L)$                                  | 0.000794 |

| $0.5 (q_1 \times C_{EQCR} \times f_{q1}) + (r_1 \times f_{q1})$      | 0.11208  |

| $0.5(q_2 \times C_{EQCR} \times f_{q2}) + (r_2 \times f_{q2})$       | 0        |

| $0.5~(s_1 \times C_{EQHV} \times f_{s1}) + (C_{EQHF} \times f_{s1})$ | 0        |

| $P_{AC} = 1.461 \text{ W}$                                           |          |

# Step 3: Calculate DC Power Dissipation DC Power Dissipation

$$\begin{split} P_{DC} &= (I_{standby}) \times V_{CCA} + (I_{standby}) \times V_{CCR} + (I_{standby}) \times V_{CCI} + X \times V_{OL} \times I_{OL} + Y(V_{CCI} - V_{OH}) \times V_{OH} \end{split}$$

EQ 1-12

For a rough estimate of DC Power Dissipation, only use  $P_{DC} = (I_{standby}) \times V_{CCA}$ . The rest of the formula provides a very small number that can be considered negligible.

$$P_{DC} = (I_{standby}) \times V_{CCA}$$

$$P_{DC} = .55 \text{ mA} \times 3.3 \text{ V}$$

$$P_{DC} = 0.001815 \text{ W}$$

#### Step 4: Calculate Total Power Consumption

$P_{Total} = P_{AC} + P_{DC}$  $P_{Total} = 1.461 + 0.001815$  $P_{Total} = 1.4628$  W

# Step 5: Compare Estimated Power Consumption against Characterized Power Consumption

The estimated total power consumption for this design is 1.46 W. The characterized power consumption for this design at 200 MHz is 1.0164 W.

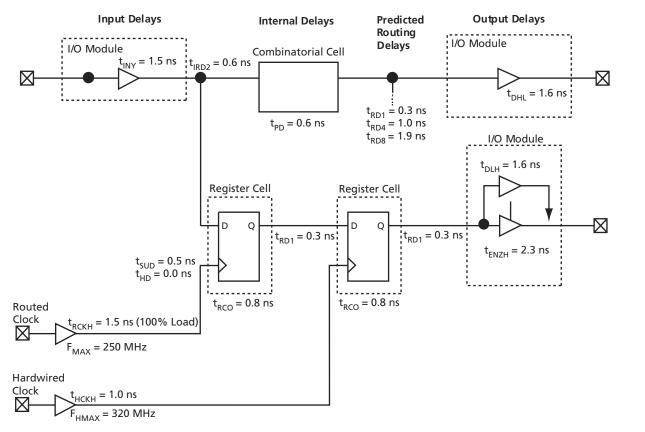

### **SX Timing Model**

### Figure 1-12 • SX Timing Model

#### **Hardwired Clock**

External Setup =  $t_{INY} + t_{IRD1} + t_{SUD} - t_{HCKH}$ = 1.5 + 0.3 + 0.5 - 1.0 = 1.3 ns

Clock-to-Out (Pin-to-Pin)

$$= t_{HCKH} + t_{RCO} + t_{RD1} + t_{DHL}$$

= 1.0 + 0.8 + 0.3 + 1.6 = 3.7 r

EQ 1-16

#### **Routed Clock**

|         | External Setup = $t_{INY} + t_{IRD1} + t_{SUD} - t_{RCKH}$<br>= 1.5 + 0.3 + 0.5 - 1.5 = 0.8 ns |         |

|---------|------------------------------------------------------------------------------------------------|---------|

| EQ 1-15 |                                                                                                | EQ 1-17 |

|         | Clock-to-Out (Pin-to-Pin)                                                                      |         |

|         | $= t_{RCKH} + t_{RCO} + t_{RD1} + t_{DHL}$                                                     |         |

|         | = 1.52+ 0.8 + 0.3 + 1.6 = 4.2 ns                                                               |         |

| EO 1-16 |                                                                                                | EQ 1-18 |

### A54SX08 Timing Characteristics

#### Table 1-17 • A54SX08 Timing Characteristics

(Worst-Case Commercial Conditions, V<sub>CCR</sub> = 4.75 V, V<sub>CCA</sub>, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                     |                                          | '-3' 9 | 5peed | '-2' \$ | Speed | '-1' 9 | Speed | 'Std' |      |       |

|---------------------|------------------------------------------|--------|-------|---------|-------|--------|-------|-------|------|-------|

| Parameter           | Description                              | Min.   | Max.  | Min.    | Max.  | Min.   | Max.  | Min.  | Max. | Units |

| C-Cell Propa        | agation Delays <sup>1</sup>              |        |       |         |       |        |       |       |      |       |

| t <sub>PD</sub>     | Internal Array Module                    |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9  | ns    |

| Predicted R         | outing Delays <sup>2</sup>               |        |       |         |       |        |       |       |      |       |

| t <sub>DC</sub>     | FO = 1 Routing Delay, Direct Connect     |        | 0.1   |         | 0.1   |        | 0.1   |       | 0.1  | ns    |

| t <sub>FC</sub>     | FO = 1 Routing Delay, Fast Connect       |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5  | ns    |

| t <sub>RD1</sub>    | FO = 1 Routing Delay                     |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5  | ns    |

| t <sub>RD2</sub>    | FO = 2 Routing Delay                     |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9  | ns    |

| t <sub>RD3</sub>    | FO = 3 Routing Delay                     |        | 0.8   |         | 0.9   |        | 1.0   |       | 1.2  | ns    |

| t <sub>RD4</sub>    | FO = 4 Routing Delay                     |        | 1.0   |         | 1.2   |        | 1.4   |       | 1.6  | ns    |

| t <sub>RD8</sub>    | FO = 8 Routing Delay                     |        | 1.9   |         | 2.2   |        | 2.5   |       | 2.9  | ns    |

| t <sub>RD12</sub>   | FO = 12 Routing Delay                    |        | 2.8   |         | 3.2   |        | 3.7   |       | 4.3  | ns    |

| R-Cell Timir        | ng                                       |        |       |         |       |        |       |       |      |       |

| t <sub>RCO</sub>    | Sequential Clock-to-Q                    |        | 0.8   |         | 1.1   |        | 1.2   |       | 1.4  | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q                  |        | 0.5   |         | 0.6   |        | 0.7   |       | 0.8  | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q                 |        | 0.7   |         | 0.8   |        | 0.9   |       | 1.0  | ns    |

| t <sub>SUD</sub>    | Flip-Flop Data Input Set-Up              | 0.5    |       | 0.5     |       | 0.7    |       | 0.8   |      | ns    |

| t <sub>HD</sub>     | Flip-Flop Data Input Hold                | 0.0    |       | 0.0     |       | 0.0    |       | 0.0   |      | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width                 | 1.4    |       | 1.6     |       | 1.8    |       | 2.1   |      | ns    |

| Input Modu          | le Propagation Delays                    |        |       |         |       |        |       |       |      |       |

| t <sub>INYH</sub>   | Input Data Pad-to-Y HIGH                 |        | 1.5   |         | 1.7   |        | 1.9   |       | 2.2  | ns    |

| t <sub>INYL</sub>   | Input Data Pad-to-Y LOW                  |        | 1.5   |         | 1.7   |        | 1.9   |       | 2.2  | ns    |

| Input Modu          | le Predicted Routing Delays <sup>2</sup> |        |       |         |       |        |       |       |      |       |

| t <sub>IRD1</sub>   | FO = 1 Routing Delay                     |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5  | ns    |

| t <sub>IRD2</sub>   | FO = 2 Routing Delay                     |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9  | ns    |

| t <sub>IRD3</sub>   | FO = 3 Routing Delay                     |        | 0.8   |         | 0.9   |        | 1.0   |       | 1.2  | ns    |

| t <sub>IRD4</sub>   | FO = 4 Routing Delay                     |        | 1.0   |         | 1.2   |        | 1.4   |       | 1.6  | ns    |

| t <sub>IRD8</sub>   | FO = 8 Routing Delay                     |        | 1.9   |         | 2.2   |        | 2.5   |       | 2.9  | ns    |

| t <sub>IRD12</sub>  | FO = 12 Routing Delay                    |        | 2.8   |         | 3.2   |        | 3.7   |       | 4.3  | ns    |

#### Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn'}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD'}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

#### Table 1-17 A54SX08 Timing Characteristics (Continued)

| (Worst-Case Commercial Conditions, | V <sub>CCR</sub> = 4.75 V, V <sub>CC</sub> | <sub>A,</sub> V <sub>CCI</sub> = 3.0 V, T <sub>J</sub> = 70°C) |

|------------------------------------|--------------------------------------------|----------------------------------------------------------------|

|------------------------------------|--------------------------------------------|----------------------------------------------------------------|

|                    |                                                         | '-3' \$ | Speed | '-2' \$ | 5peed | '-1' \$ | 5peed | 'Std' |      |       |

|--------------------|---------------------------------------------------------|---------|-------|---------|-------|---------|-------|-------|------|-------|

| Parameter          | Description                                             | Min.    | Max.  | Min.    | Max.  | Min.    | Max.  | Min.  | Max. | Units |

| Dedicated (        | Hardwired) Array Clock Network                          |         |       |         |       |         |       |       |      |       |

| t <sub>HCKH</sub>  | Input LOW to HIGH (pad to R-Cell input)                 |         | 1.0   |         | 1.1   |         | 1.3   |       | 1.5  | ns    |

| t <sub>HCKL</sub>  | Input HIGH to LOW (pad to R-Cell input)                 |         | 1.0   |         | 1.2   |         | 1.4   |       | 1.6  | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width HIGH                                | 1.4     |       | 1.6     |       | 1.8     |       | 2.1   |      | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width LOW                                 | 1.4     |       | 1.6     |       | 1.8     |       | 2.1   |      | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |         | 0.1   |         | 0.2   |         | 0.2   |       | 0.2  | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.7     |       | 3.1     |       | 3.6     |       | 4.2   |      | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |         | 350   |         | 320   |         | 280   |       | 240  | MHz   |

| Routed Arra        | ay Clock Networks                                       |         |       |         |       |         |       |       |      |       |

| t <sub>RCKH</sub>  | Input LOW to HIGH (light load)<br>(pad to R-Cell input) |         | 1.3   |         | 1.5   |         | 1.7   |       | 2.0  | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (light load)<br>(pad to R-Cell Input) |         | 1.4   |         | 1.6   |         | 1.8   |       | 2.1  | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (50% load)<br>(pad to R-Cell input)   |         | 1.4   |         | 1.7   |         | 1.9   |       | 2.2  | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (50% load)<br>(pad to R-Cell input)   |         | 1.5   |         | 1.7   |         | 2.0   |       | 2.3  | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (100% load)<br>(pad to R-Cell input)  |         | 1.5   |         | 1.7   |         | 1.9   |       | 2.2  | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (100% load)<br>(pad to R-Cell input)  |         | 1.5   |         | 1.8   |         | 2.0   |       | 2.3  | ns    |

| t <sub>RPWH</sub>  | Min. Pulse Width HIGH                                   | 2.1     |       | 2.4     |       | 2.7     |       | 3.2   |      | ns    |

| t <sub>RPWL</sub>  | Min. Pulse Width LOW                                    | 2.1     |       | 2.4     |       | 2.7     |       | 3.2   |      | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (light load)                               |         | 0.1   |         | 0.2   |         | 0.2   |       | 0.2  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% load)                                 |         | 0.3   |         | 0.3   |         | 0.4   |       | 0.4  | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% load)                                |         | 0.3   |         | 0.3   |         | 0.4   |       | 0.4  | ns    |

| TTL Output         | Module Timing1                                          |         |       |         |       |         |       |       |      |       |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                                 |         | 1.6   |         | 1.9   |         | 2.1   |       | 2.5  | ns    |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                                 |         | 1.6   |         | 1.9   |         | 2.1   |       | 2.5  | ns    |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                                   |         | 2.1   |         | 2.4   |         | 2.8   |       | 3.2  | ns    |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                                   |         | 2.3   |         | 2.7   |         | 3.1   |       | 3.6  | ns    |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                                   |         | 1.4   |         | 1.7   |         | 1.9   |       | 2.2  | ns    |

Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

#### SX Family FPGAs

#### Table 1-20 • A54SX32 Timing Characteristics (Continued)

#### (Worst-Case Commercial Conditions, V<sub>CCR</sub>= 4.75 V, V<sub>CCA</sub>, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                         | '-3' \$ | Speed | '-2' ! | 5peed | '-1' \$ | Speed | 'Std' | Speed |       |

|--------------------|---------------------------------------------------------|---------|-------|--------|-------|---------|-------|-------|-------|-------|

| Parameter          | Description                                             | Min.    | Max.  | Min.   | Max.  | Min.    | Max.  | Min.  | Max.  | Units |

| Dedicated (        | Hardwired) Array Clock Network                          |         |       |        |       |         |       |       |       |       |

| t <sub>HCKH</sub>  | Input LOW to HIGH (pad to R-Cell input)                 |         | 1.9   |        | 2.1   |         | 2.4   |       | 2.8   | ns    |

| t <sub>HCKL</sub>  | Input HIGH to LOW (pad to R-Cell input)                 |         | 1.9   |        | 2.1   |         | 2.4   |       | 2.8   | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width HIGH                                | 1.4     |       | 1.6    |       | 1.8     |       | 2.1   |       | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width LOW                                 | 1.4     |       | 1.6    |       | 1.8     |       | 2.1   |       | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |         | 0.3   |        | 0.4   |         | 0.4   |       | 0.5   | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.7     |       | 3.1    |       | 3.6     |       | 4.2   |       | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |         | 350   |        | 320   |         | 280   |       | 240   | MHz   |

| Routed Arra        | ay Clock Networks                                       |         |       |        |       |         |       |       |       |       |

| t <sub>rckh</sub>  | Input LOW to HIGH (light load)<br>(pad to R-Cell input) |         | 2.4   |        | 2.7   |         | 3.0   |       | 3.5   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (light load)<br>(pad to R-Cell input) |         | 2.4   |        | 2.7   |         | 3.1   |       | 3.6   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (50% load)<br>(pad to R-Cell input)   |         | 2.7   |        | 3.0   |         | 3.5   |       | 4.1   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (50% load)<br>(pad to R-Cell input)   |         | 2.7   |        | 3.1   |         | 3.6   |       | 4.2   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (100% load)<br>(pad to R-Cell input)  |         | 2.7   |        | 3.1   |         | 3.5   |       | 4.1   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (100% load)<br>(pad to R-Cell input)  |         | 2.8   |        | 3.2   |         | 3.6   |       | 4.3   | ns    |

| t <sub>RPWH</sub>  | Min. Pulse Width HIGH                                   | 2.1     |       | 2.4    |       | 2.7     |       | 3.2   |       | ns    |

| t <sub>RPWL</sub>  | Min. Pulse Width LOW                                    | 2.1     |       | 2.4    |       | 2.7     |       | 3.2   |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (light load)                               |         | 0.85  |        | 0.98  |         | 1.1   |       | 1.3   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% load)                                 |         | 1.23  |        | 1.4   |         | 1.6   |       | 1.9   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% load)                                |         | 1.30  |        | 1.5   |         | 1.7   |       | 2.0   | ns    |

| TTL Output         | Module Timing <sup>3</sup>                              |         |       |        |       |         |       |       |       |       |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                                 |         | 1.6   |        | 1.9   |         | 2.1   |       | 2.5   | ns    |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                                 |         | 1.6   |        | 1.9   |         | 2.1   |       | 2.5   | ns    |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                                   |         | 2.1   |        | 2.4   |         | 2.8   |       | 3.2   | ns    |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                                   |         | 2.3   |        | 2.7   |         | 3.1   |       | 3.6   | ns    |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                                   |         | 1.4   |        | 1.7   |         | 1.9   |       | 2.2   | ns    |

| t <sub>enhz</sub>  | Enable-to-Pad, H to Z                                   |         | 1.3   |        | 1.5   |         | 1.7   |       | 2.0   | ns    |

#### Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 35 pF loading, except  $t_{ENZL}$  and  $t_{ENZH}$ . For  $t_{ENZL}$  and  $t_{ENZH}$  the loading is 5 pF.

# 208-Pin PQFP

Figure 2-2 • 208-Pin PQFP (Top View)

### Note

|         | Actel      |  |

|---------|------------|--|

| 54SX Fa | mily FPGAs |  |

|            | 208-Pi              | n PQFP                           |                     | 208-Pin PQFP |                     |                                  |                     |  |  |  |  |  |  |

|------------|---------------------|----------------------------------|---------------------|--------------|---------------------|----------------------------------|---------------------|--|--|--|--|--|--|

| Pin Number | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function | A54SX32<br>Function | Pin Number   | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function | A54SX32<br>Function |  |  |  |  |  |  |

| 73         | NC                  | I/O                              | I/O                 | 109          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 74         | I/O                 | I/O                              | I/O                 | 110          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 75         | NC                  | I/O                              | I/O                 | 111          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 76         | PRB, I/O            | PRB, I/O                         | PRB, I/O            | 112          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 77         | GND                 | GND                              | GND                 | 113          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 78         | V <sub>CCA</sub>    | V <sub>CCA</sub>                 | V <sub>CCA</sub>    | 114          | V <sub>CCA</sub>    | V <sub>CCA</sub>                 | V <sub>CCA</sub>    |  |  |  |  |  |  |

| 79         | GND                 | GND                              | GND                 | 115          | V <sub>CCI</sub>    | V <sub>CCI</sub>                 | V <sub>CCI</sub>    |  |  |  |  |  |  |

| 80         | V <sub>CCR</sub>    | V <sub>CCR</sub>                 | V <sub>CCR</sub>    | 116          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 81         | I/O                 | I/O                              | I/O                 | 117          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 82         | HCLK                | HCLK                             | HCLK                | 118          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 83         | I/O                 | I/O                              | I/O                 | 119          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 84         | I/O                 | I/O                              | I/O                 | 120          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 85         | NC                  | I/O                              | I/O                 | 121          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 86         | I/O                 | I/O                              | I/O                 | 122          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 87         | I/O                 | I/O                              | I/O                 | 123          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 88         | NC                  | I/O                              | I/O                 | 124          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 89         | I/O                 | I/O                              | I/O                 | 125          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 90         | I/O                 | I/O                              | I/O                 | 126          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 91         | NC                  | I/O                              | I/O                 | 127          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 92         | I/O                 | I/O                              | I/O                 | 128          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 93         | I/O                 | I/O                              | I/O                 | 129          | GND                 | GND                              | GND                 |  |  |  |  |  |  |

| 94         | NC                  | I/O                              | I/O                 | 130          | V <sub>CCA</sub>    | V <sub>CCA</sub>                 | V <sub>CCA</sub>    |  |  |  |  |  |  |

| 95         | I/O                 | I/O                              | I/O                 | 131          | GND                 | GND                              | GND                 |  |  |  |  |  |  |

| 96         | I/O                 | I/O                              | I/O                 | 132          | V <sub>CCR</sub>    | V <sub>CCR</sub>                 | V <sub>CCR</sub>    |  |  |  |  |  |  |

| 97         | NC                  | I/O                              | I/O                 | 133          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 98         | V <sub>CCI</sub>    | V <sub>CCI</sub>                 | V <sub>CCI</sub>    | 134          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 99         | I/O                 | I/O                              | I/O                 | 135          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 100        | I/O                 | I/O                              | I/O                 | 136          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 101        | I/O                 | I/O                              | I/O                 | 137          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 102        | I/O                 | I/O                              | I/O                 | 138          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 103        | TDO, I/O            | TDO, I/O                         | TDO, I/O            | 139          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 104        | I/O                 | I/O                              | I/O                 | 140          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 105        | GND                 | GND                              | GND                 | 141          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 106        | NC                  | I/O                              | I/O                 | 142          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 107        | I/O                 | I/O                              | I/O                 | 143          | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 108        | NC                  | I/O                              | I/O                 | 144          | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

**Note:** \* Note that Pin 65 in the A54SX32—PQ208 is a no connect (NC).

|            | 176-Pi              | n TQFP                           |                     |

|------------|---------------------|----------------------------------|---------------------|

| Pin Number | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function | A54SX32<br>Function |

| 1          | GND                 | GND                              | GND                 |

| 2          | TDI, I/O            | TDI, I/O                         | TDI, I/O            |

| 3          | NC                  | I/O                              | I/O                 |

| 4          | I/O                 | I/O                              | I/O                 |

| 5          | I/O                 | I/O                              | I/O                 |

| 6          | I/O                 | I/O                              | I/O                 |

| 7          | I/O                 | I/O                              | I/O                 |

| 8          | I/O                 | I/O                              | I/O                 |

| 9          | I/O                 | I/O                              | I/O                 |

| 10         | TMS                 | TMS                              | TMS                 |

| 11         | V <sub>CCI</sub>    | V <sub>CCI</sub>                 | V <sub>CCI</sub>    |

| 12         | NC                  | I/O                              | I/O                 |

| 13         | I/O                 | I/O                              | I/O                 |

| 14         | I/O                 | I/O                              | I/O                 |

| 15         | I/O                 | I/O                              | I/O                 |

| 16         | I/O                 | I/O                              | I/O                 |

| 17         | I/O                 | I/O                              | I/O                 |

| 18         | I/O                 | I/O                              | I/O                 |

| 19         | I/O                 | I/O                              | I/O                 |

| 20         | I/O                 | I/O                              | I/O                 |

| 21         | GND                 | GND                              | GND                 |

| 22         | $V_{CCA}$           | V <sub>CCA</sub>                 | V <sub>CCA</sub>    |

| 23         | GND                 | GND                              | GND                 |

| 24         | I/O                 | I/O                              | I/O                 |

| 25         | I/O                 | I/O                              | I/O                 |

| 26         | I/O                 | I/O                              | I/O                 |

| 27         | I/O                 | I/O                              | I/O                 |

| 28         | I/O                 | I/O                              | I/O                 |

| 29         | I/O                 | I/O                              | I/O                 |

| 30         | I/O                 | I/O                              | I/O                 |

| 31         | I/O                 | I/O                              | I/O                 |

| 32         | V <sub>CCI</sub>    | V <sub>CCI</sub>                 | V <sub>CCI</sub>    |

| 33         | V <sub>CCA</sub>    | V <sub>CCA</sub>                 | V <sub>CCA</sub>    |

| 34         | I/O                 | I/O                              | I/O                 |

| 176-Pin TQFP |                     |                                  |                     |  |  |  |  |  |  |

|--------------|---------------------|----------------------------------|---------------------|--|--|--|--|--|--|

| Pin Number   | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function | A54SX32<br>Function |  |  |  |  |  |  |

| 35           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 36           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 37           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 38           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 39           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 40           | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 41           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 42           | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 43           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 44           | GND                 | GND                              | GND                 |  |  |  |  |  |  |

| 45           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 46           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 47           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 48           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 49           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 50           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 51           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 52           | V <sub>CCI</sub>    | V <sub>CCI</sub>                 | V <sub>CCI</sub>    |  |  |  |  |  |  |

| 53           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 54           | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 55           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 56           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 57           | NC                  | I/O                              | I/O                 |  |  |  |  |  |  |

| 58           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 59           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 60           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 61           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 62           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 63           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

| 64           | PRB, I/O            | PRB, I/O                         | PRB, I/O            |  |  |  |  |  |  |

| 65           | GND                 | GND                              | GND                 |  |  |  |  |  |  |

| 66           | V <sub>CCA</sub>    | V <sub>CCA</sub>                 | V <sub>CCA</sub>    |  |  |  |  |  |  |

| 67           | V <sub>CCR</sub>    | V <sub>CCR</sub>                 | V <sub>CCR</sub>    |  |  |  |  |  |  |

| 68           | I/O                 | I/O                              | I/O                 |  |  |  |  |  |  |

# 100-Pin VQFP

Figure 2-5 • 100-Pin VQFP (Top View)

#### Note

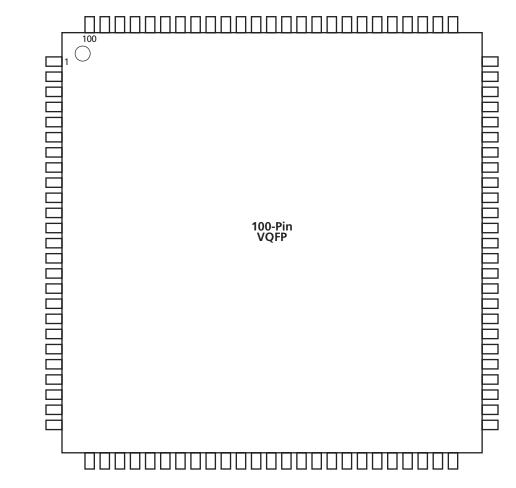

### 313-Pin PBGA

Figure 2-6 • 313-Pin PBGA (Top View)

### Note

| 313-Pi        | n PBGA              | 313-Pi        | n PBGA              | 313-Pi        | n PBGA              | 313-Pin PBGA  |                     |  |  |  |

|---------------|---------------------|---------------|---------------------|---------------|---------------------|---------------|---------------------|--|--|--|

| Pin<br>Number | A54SX32<br>Function | Pin<br>Number | A54SX32<br>Function | Pin<br>Number | A54SX32<br>Function | Pin<br>Number | A54SX32<br>Function |  |  |  |

| A1            | GND                 | AC5           | I/O                 | B10           | I/O                 | E15           | I/O                 |  |  |  |

| A3            | NC                  | AC7           | I/O                 | B12           | I/O                 | E17           | I/O                 |  |  |  |

| A5            | I/O                 | AC9           | I/O                 | B14           | I/O                 | E19           | I/O                 |  |  |  |

| A7            | I/O                 | AC11          | I/O                 | B16           | I/O                 | E21           | I/O                 |  |  |  |

| A9            | I/O                 | AC13          | V <sub>CCR</sub>    | B18           | I/O                 | E23           | I/O                 |  |  |  |

| A11           | I/O                 | AC15          | I/O                 | B20           | I/O                 | E25           | I/O                 |  |  |  |

| A13           | V <sub>CCR</sub>    | AC17          | I/O                 | B22           | I/O                 | F2            | I/O                 |  |  |  |

| A15           | I/O                 | AC19          | I/O                 | B24           | I/O                 | F4            | I/O                 |  |  |  |

| A17           | I/O                 | AC21          | I/O                 | C1            | TDI, I/O            | F6            | NC                  |  |  |  |

| A19           | I/O                 | AC23          | I/O                 | C3            | I/O                 | F8            | I/O                 |  |  |  |

| A21           | I/O                 | AC25          | NC                  | C5            | NC                  | F10           | NC                  |  |  |  |

| A23           | NC                  | AD2           | GND                 | С7            | I/O                 | F12           | I/O                 |  |  |  |

| A25           | GND                 | AD4           | I/O                 | С9            | I/O                 | F14           | I/O                 |  |  |  |

| AA1           | I/O                 | AD6           | V <sub>CCI</sub>    | C11           | I/O                 | F16           | NC                  |  |  |  |

| AA3           | I/O                 | AD8           | I/O                 | C13           | V <sub>CCI</sub>    | F18           | I/O                 |  |  |  |

| AA5           | NC                  | AD10          | I/O                 | C15           | I/O                 | F20           | I/O                 |  |  |  |

| AA7           | I/O                 | AD12          | PRB, I/O            | C17           | I/O                 | F22           | I/O                 |  |  |  |

| AA9           | NC                  | AD14          | I/O                 | C19           | V <sub>CCI</sub>    | F24           | I/O                 |  |  |  |

| AA11          | I/O                 | AD16          | I/O                 | C21           | I/O                 | G1            | I/O                 |  |  |  |

| AA13          | I/O                 | AD18          | I/O                 | C23           | I/O                 | G3            | TMS                 |  |  |  |

| AA15          | I/O                 | AD20          | I/O                 | C25           | NC                  | G5            | I/O                 |  |  |  |

| AA17          | I/O                 | AD22          | NC                  | D2            | I/O                 | G7            | I/O                 |  |  |  |

| AA19          | I/O                 | AD24          | I/O                 | D4            | NC                  | G9            | V <sub>CCI</sub>    |  |  |  |

| AA21          | I/O                 | AE1           | NC                  | D6            | I/O                 | G11           | I/O                 |  |  |  |

| AA23          | NC                  | AE3           | I/O                 | D8            | I/O                 | G13           | CLKB                |  |  |  |

| AA25          | I/O                 | AE5           | I/O                 | D10           | I/O                 | G15           | I/O                 |  |  |  |

| AB2           | NC                  | AE7           | I/O                 | D12           | I/O                 | G17           | I/O                 |  |  |  |

| AB4           | NC                  | AE9           | I/O                 | D14           | I/O                 | G19           | I/O                 |  |  |  |

| AB6           | I/O                 | AE11          | I/O                 | D16           | I/O                 | G21           | I/O                 |  |  |  |

| AB8           | I/O                 | AE13          | V <sub>CCA</sub>    | D18           | I/O                 | G23           | I/O                 |  |  |  |

| AB10          | I/O                 | AE15          | I/O                 | D20           | I/O                 | G25           | I/O                 |  |  |  |

| AB12          | I/O                 | AE17          | I/O                 | D22           | I/O                 | H2            | I/O                 |  |  |  |

| AB14          | I/O                 | AE19          | I/O                 | D24           | NC                  | H4            | I/O                 |  |  |  |

| AB16          | I/O                 | AE21          | I/O                 | E1            | I/O                 | H6            | I/O                 |  |  |  |

| AB18          | V <sub>CCI</sub>    | AE23          | TDO, I/O            | E3            | NC                  | H8            | I/O                 |  |  |  |

| AB20          | NC                  | AE25          | GND                 | E5            | I/O                 | H10           | I/O                 |  |  |  |

| AB22          | I/O                 | B2            | TCK, I/O            | E7            | I/O                 | H12           | PRA, I/O            |  |  |  |

| AB24          | I/O                 | B4            | I/O                 | E9            | I/O                 | H14           | I/O                 |  |  |  |

| AC1           | I/O                 | B6            | I/O                 | E11           | I/O                 | H16           | I/O                 |  |  |  |

| AC3           | I/O                 | B8            | I/O                 | E13           | V <sub>CCA</sub>    | H18           | NC                  |  |  |  |

# 329-Pin PBGA

| _      | 1        | 2              | 3           | 4           | 5      | 6      | 7      | 8      | 9      | 10     | 11     | 12     | 13     | 14     | 15     | 16 | 17     | 18     | 19 | 20            | 21       | 22       | 23                 |   |

|--------|----------|----------------|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----|--------|--------|----|---------------|----------|----------|--------------------|---|

| А      | 0        | 0              | 0           | 0           | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0  | 0      | 0      | 0  | 0             | 0        | 0        | 0                  | ٦ |

| В      | 0        | 0              | Õ           | 0           | ~      | ~      | 0      | ~      | ~      | ž      | ~      | ~      | ~      | ~      | 0      | ~  | ž      | ~      | ~  | $\overline{}$ | 0        | ~        | 0                  |   |

| С      | Ŭ        | č              | ~           | -           | -      | -      | -      | -      | -      | -      | _      | Ξ.     | -      | -      | -      | _  | _      | -      | _  | 0             | -        | -        | -                  |   |

| D      | •        | 0              | ·           | -           | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0  | 0      | 0      | 0  | -             | ~        | 0        | ~                  |   |

| E<br>F | -        | 0              | -           | -           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    | -             | -        | 0        | _                  |   |

| G      | -        |                | ·           | -           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    |               | 0        | 0        | 0                  |   |

| н      | _        | $\overline{0}$ | _           | _           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    |               |          | 0        |                    |   |

| J      | -        | $\tilde{O}$    | Ξ.          | -           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    | -             | -        | õ        | -                  |   |

| к      |          | Õ              | <u> </u>    | -           |        |        |        |        |        | 0      | 0      | 0      | 0      | 0      |        |    |        |        |    | -             | -        | ŏ        | -                  |   |

| L      | 0        | 0              | Ο           | Ο           |        |        |        |        |        | 0      | Ο      | 0      | 0      | Ο      |        |    |        |        |    | 0             | 0        | 0        | Ο                  |   |

| м      | 0        | 0              | Ο           | Ο           |        |        |        |        |        | Ο      | Ο      | Ο      | 0      | Ο      |        |    |        |        |    | 0             | Ο        | Ο        | Ο                  |   |

| N      | <u> </u> | 0              | <u> </u>    | <u> </u>    |        |        |        |        |        |        | Õ      |        |        |        |        |    |        |        |    | $\sim$        | Õ        | $\sim$   | Õ                  |   |

| P      |          | 0              |             |             |        |        |        |        |        | 0      | 0      | Ο      | Ο      | Ο      |        |    |        |        |    | -             | 0        | -        | O                  |   |

| R      | •        | 0              | ·           | -           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    | <u> </u>      | 0        | <u> </u> | 0                  |   |

| T<br>U | -        | 0              | -           | 0           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    | Ŭ             | 0        | Ŭ        | 0                  |   |

| v      | · ·      |                | <u> </u>    | 0           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    | <u> </u>      | 00       | <u> </u> | 0                  |   |

| ŵ      | -        | 0              | -           | -           |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    |               | 0        | -        | $\hat{\mathbf{O}}$ |   |

| Y      | _        | -              | _           | $\tilde{0}$ | $\cap$ | 0  | $\cap$ | $\cap$ | 0  | ~             | <u> </u> | ~        | $\tilde{0}$        |   |

| AA     | č        | $\tilde{O}$    | $\tilde{O}$ | õ           | õ      | õ      | õ      | õ      | _      | õ      | _      | _      | _      | _      | _      | õ  | _      | õ      | õ  | _             | õ        | ~        | õ                  |   |

| AB     | ŏ        | ŏ              | ŏ           | õ           | ŏ      | ŏ      | ŏ      | ŏ      | õ      | ŏ      | ŏ      | õ      | ŏ      | õ      | ŏ      | ŏ  | ŏ      | ŏ      | ŏ  | ŏ             | ŏ        | ŏ        | õ                  |   |

| AC     | , Ō      | 0              | Ο           | 0           | 0      | Ō      | Ō      | Ō      | Ō      | Ō      | 0      | 0      | 0      | 0      | Ō      | 0  | Ō      | Ō      | Ō  | 0             | Ō        | 0        | Ō                  |   |

|        |          |                |             |             |        |        |        |        |        |        |        |        |        |        |        |    |        |        |    |               |          |          |                    |   |

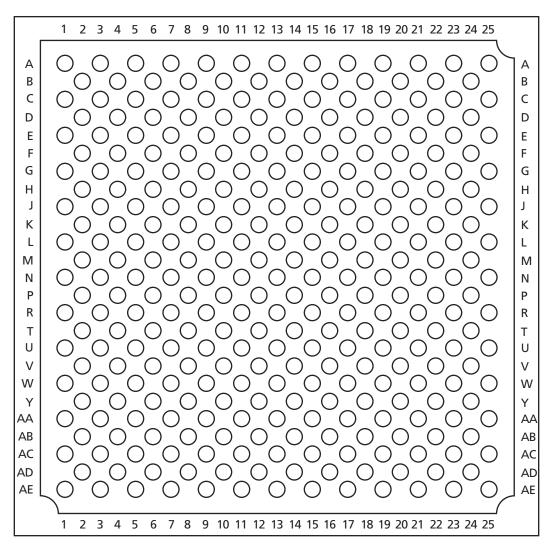

Figure 2-7 • 329-Pin PBGA (Top View)

#### Note

#### 54SX Family FPGAs

| 329-Pir       | n PBGA              |

|---------------|---------------------|

| Pin<br>Number | A54SX32<br>Function |

| T22           | I/O                 |

| T23           | I/O                 |

| U1            | I/O                 |

| U2            | I/O                 |

| U3            | V <sub>CCA</sub>    |

| U4            | I/O                 |

| U20           | I/O                 |

| U21           | V <sub>CCA</sub>    |