# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 768                                                          |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | -                                                            |

| Number of I/O                  | 69                                                           |

| Number of Gates                | 12000                                                        |

| Voltage - Supply               | 3V ~ 3.6V, 4.75V ~ 5.25V                                     |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                            |

| Package / Case                 | 84-LCC (J-Lead)                                              |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a54sx08-pl84i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Routing Resources**

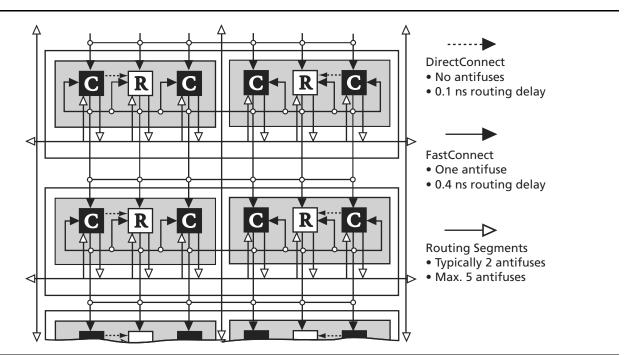

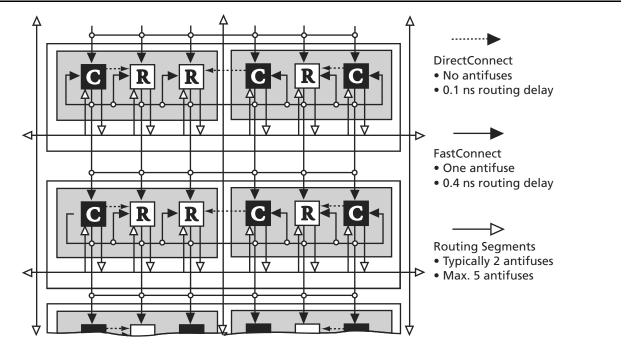

Clusters and SuperClusters can be connected through the use of two innovative local routing resources called *FastConnect* and *DirectConnect*, which enable extremely fast and predictable interconnection of modules within clusters and SuperClusters (Figure 1-5 and Figure 1-6). This routing architecture also dramatically reduces the number of antifuses required to complete a circuit, ensuring the highest possible performance.

Figure 1-5 • DirectConnect and FastConnect for Type 1 SuperClusters

*Figure 1-6* • **DirectConnect and FastConnect for Type 2 SuperClusters**

### Boundary Scan Testing (BST)

All SX devices are IEEE 1149.1 compliant. SX devices offer superior diagnostic and testing capabilities by providing Boundary Scan Testing (BST) and probing capabilities. These functions are controlled through the special test pins in conjunction with the program fuse. The functionality of each pin is described in Table 1-2. In the dedicated test mode, TCK, TDI, and TDO are dedicated pins and cannot be used as regular I/Os. In flexible mode, TMS should be set HIGH through a pull-up resistor of 10 k $\Omega$ . TMS can be pulled LOW to initiate the test sequence.

The program fuse determines whether the device is in dedicated or flexible mode. The default (fuse not blown) is flexible mode.

| Table 1-2 • | Boundary Scan Pin Functionality |

|-------------|---------------------------------|

|-------------|---------------------------------|

| Program Fuse Blown<br>(Dedicated Test Mode) | Program Fuse Not Blown<br>(Flexible Mode)           |  |  |  |  |

|---------------------------------------------|-----------------------------------------------------|--|--|--|--|

| TCK, TDI, TDO are dedicated BST pins.       | TCK, TDI, TDO are flexible and may be used as I/Os. |  |  |  |  |

| No need for pull-up resistor for<br>TMS     | Use a pull-up resistor of 10 $k\Omega$ on TMS.      |  |  |  |  |

# **Dedicated Test Mode**

In Dedicated mode, all JTAG pins are reserved for BST; designers cannot use them as regular I/Os. An internal pull-up resistor is automatically enabled on both TMS and TDI pins, and the TMS pin will function as defined in the IEEE 1149.1 (JTAG) specification.

To select Dedicated mode, users need to reserve the JTAG pins in Actel's Designer software by checking the "Reserve JTAG" box in "Device Selection Wizard" (Figure 1-7). JTAG pins comply with LVTTL/TTL I/O specification regardless of whether they are used as a user I/O or a JTAG I/O. Refer to the Table 1-5 on page 1-8 for detailed specifications.

Figure 1-7 • Device Selection Wizard

### **Development Tool Support**

The SX family of FPGAs is fully supported by both the Actel Libero<sup>®</sup> Integrated Design Environment (IDE) and Designer FPGA Development software. Actel Libero IDE is a design management environment, seamlessly integrating design tools while guiding the user through the design flow, managing all design and log files, and passing necessary design data among tools. Libero IDE allows users to integrate both schematic and HDL synthesis into a single flow and verify the entire design in a single environment. Libero IDE includes Synplify<sup>®</sup> for Actel from Synplicity<sup>®</sup>, ViewDraw<sup>®</sup> for Actel from Mentor Graphics<sup>®</sup>, ModelSim<sup>®</sup> HDL Simulator from Mentor Graphics, WaveFormer Lite™ from SynaptiCAD<sup>™</sup>, and Designer software from Actel. Refer to the Libero IDE flow diagram (located on the Actel website) for more information.

Actel Designer software is a place-and-route tool and provides a comprehensive suite of backend support tools for FPGA development. The Designer software includes timing-driven place-and-route, and a world-class integrated static timing analyzer and constraints editor. With the Designer software, a user can select and lock package pins while only minimally impacting the results of place-and-route. Additionally, the back-annotation flow is compatible with all the major simulators, and the simulation results can be cross-probed with Silicon Explorer II, Actel integrated verification and logic analysis tool. Another tool included in the Designer software is the SmartGen core generator, which easily creates popular and commonly used logic functions for implementation into your schematic or HDL design. Actel Designer software is compatible with the most popular FPGA design entry and verification tools from companies such as Mentor Graphics, Synplicity, Synopsys<sup>®</sup>, and Cadence<sup>®</sup> Design Systems. The Designer software is available for both the Windows® and UNIX® operating systems.

### **Probe Circuit Control Pins**

The Silicon Explorer II tool uses the boundary scan ports (TDI, TCK, TMS, and TDO) to select the desired nets for verification. The selected internal nets are assigned to the PRA/PRB pins for observation. Figure 1-8 on page 1-7 illustrates the interconnection between Silicon Explorer II and the FPGA to perform in-circuit verification.

### **Design Considerations**

The TDI, TCK, TDO, PRA, and PRB pins should not be used as input or bidirectional ports. Because these pins are active during probing, critical signals input through these pins are not available while probing. In addition, the Security Fuse should not be programmed because doing so disables the Probe Circuitry.

# A54SX16P AC Specifications for (PCI Operation)

| Symbol              | Parameter              | Condition                        | Min.                                 | Max.                | Units |  |

|---------------------|------------------------|----------------------------------|--------------------------------------|---------------------|-------|--|

| I <sub>OH(AC)</sub> | Switching Current High | $0 < V_{OUT} \le 1.4^{1}$        | -44                                  |                     | mA    |  |

|                     |                        | $1.4 \le V_{OUT} < 2.4^{1, 2}$   | -44 + (V <sub>OUT</sub> - 1.4)/0.024 |                     | mA    |  |

|                     |                        | $3.1 < V_{OUT} < V_{CC}^{1, 3}$  |                                      | EQ 1-1 on page 1-11 |       |  |

|                     | (Test Point)           | $V_{OUT} = 3.1^{3}$              |                                      | -142                | mA    |  |

| I <sub>OL(AC)</sub> | Switching Current High | $V_{OUT} \ge 2.2^{1}$            | 95                                   |                     | mA    |  |

|                     |                        | $2.2 > V_{OUT} > 0.55^{1}$       | V <sub>OUT</sub> /0.023              |                     |       |  |

|                     |                        | $0.71 > V_{OUT} > 0^{1, 3}$      |                                      | EQ 1-2 on page 1-11 | mA    |  |

|                     | (Test Point)           | $V_{OUT} = 0.71^{3}$             |                                      | 206                 | mA    |  |

| I <sub>CL</sub>     | Low Clamp Current      | $-5 < V_{IN} \leq -1$            | -25 + (V <sub>IN</sub> + 1)/0.015    |                     | mA    |  |

| slew <sub>R</sub>   | Output Rise Slew Rate  | 0.4 V to 2.4 V load <sup>4</sup> | 1                                    | 5                   | V/ns  |  |

| slew <sub>F</sub>   | Output Fall Slew Rate  | 2.4 V to 0.4 V load <sup>4</sup> | 1                                    | 5                   | V/ns  |  |

### Table 1-7 A54SX16P AC Specifications for (PCI Operation)

### Notes:

1. Refer to the V/I curves in Figure 1-9 on page 1-11. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here; i.e., half-size output drivers may be used on these signals. This specification does not apply to CLK and RST#, which are system outputs. "Switching Current High" specifications are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD#, which are open drain outputs.

2. Note that this segment of the minimum current curve is drawn from the AC drive point directly to the DC drive point rather than toward the voltage rail (as is done in the pull-down curve). This difference is intended to allow for an optional N-channel pull-up.

3. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (A and B) are provided with the respective diagrams in Figure 1-9 on page 1-11. The equation defined maxima should be met by design. In order to facilitate component testing, a maximum current test point is defined for each side of the output driver.

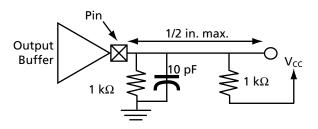

4. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an unloaded output per revision 2.0 of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is now required (the maximum is no longer simply a guideline). Since adherence to the maximum slew rate was not required prior to revision 2.1 of the specification, there may be components in the market for some time that have faster edge rates; therefore, motherboard designers must bear in mind that rise and fall times faster than this specification could occur, and should ensure that signal integrity modeling accounts for this. Rise slew rate does not apply to open drain outputs.

# A54SX16P DC Specifications (3.3 V PCI Operation)

| Symbol             | Parameter                                    | Condition                  | Min.               | Max.               | Units |

|--------------------|----------------------------------------------|----------------------------|--------------------|--------------------|-------|

| V <sub>CCA</sub>   | Supply Voltage for Array                     |                            | 3.0                | 3.6                | V     |

| V <sub>CCR</sub>   | Supply Voltage required for Internal Biasing |                            | 3.0                | 3.6                | V     |

| V <sub>CCI</sub>   | Supply Voltage for I/Os                      |                            | 3.0                | 3.6                | V     |

| $V_{\text{IH}}$    | Input High Voltage                           |                            | 0.5V <sub>CC</sub> | $V_{CC} + 0.5$     | V     |

| V <sub>IL</sub>    | Input Low Voltage                            |                            | -0.5               | 0.3V <sub>CC</sub> | V     |

| I <sub>IPU</sub>   | Input Pull-up Voltage <sup>1</sup>           |                            | 0.7V <sub>CC</sub> |                    | V     |

| IIL                | Input Leakage Current <sup>2</sup>           | $0 < V_{IN} < V_{CC}$      |                    | ±10                | μA    |

| V <sub>OH</sub>    | Output High Voltage                          | I <sub>OUT</sub> = –500 μA | 0.9V <sub>CC</sub> |                    | V     |

| V <sub>OL</sub>    | Output Low Voltage                           | I <sub>OUT</sub> = 1500 μA |                    | 0.1V <sub>CC</sub> | V     |

| C <sub>IN</sub>    | Input Pin Capacitance <sup>3</sup>           |                            |                    | 10                 | pF    |

| C <sub>CLK</sub>   | CLK Pin Capacitance                          |                            | 5                  | 12                 | pF    |

| C <sub>IDSEL</sub> | IDSEL Pin Capacitance <sup>4</sup>           |                            |                    | 8                  | pF    |

Table 1-8 • A54SX16P DC Specifications (3.3 V PCI Operation)

Notes:

1. This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Applications sensitive to static power utilization should assure that the input buffer is conducting minimum current at this input voltage.

2. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

3. Absolute maximum pin capacitance for a PCI input is 10 pF (except for CLK).

4. Lower capacitance on this input-only pin allows for non-resistive coupling to AD[xx].

# A54SX16P AC Specifications (3.3 V PCI Operation)

| Symbol              | Parameter                          | Condition                                | Min.                                                | Max.                | Units |

|---------------------|------------------------------------|------------------------------------------|-----------------------------------------------------|---------------------|-------|

|                     | Switching Current High             | $0 < V_{OUT} \le 0.3 V_{CC}^{1}$         |                                                     |                     | mA    |

| 1                   |                                    | $0.3V_{CC} \le V_{OUT} < 0.9V_{CC}^{-1}$ | -12V <sub>CC</sub>                                  |                     | mA    |

| IOH(AC)             |                                    | $0.7V_{CC} < V_{OUT} < V_{CC}^{1, 2}$    | –17.1 + (V <sub>CC</sub> – V <sub>OUT</sub> )       | EQ 1-3 on page 1-14 |       |

|                     | (Test Point)                       | $V_{OUT} = 0.7 V_{CC}^2$                 |                                                     | -32V <sub>CC</sub>  | mA    |

|                     | Switching Current High             | $V_{CC} > V_{OUT} \ge 0.6 V_{CC}^{1}$    |                                                     |                     | mA    |

| 1                   |                                    | $0.6V_{CC} > V_{OUT} > 0.1V_{CC}^{1}$    | 16V <sub>CC</sub>                                   |                     | mA    |

| I <sub>OL(AC)</sub> |                                    | $0.18V_{CC} > V_{OUT} > 0^{1, 2}$        | 26.7V <sub>OUT</sub>                                | EQ 1-4 on page 1-14 | mA    |

|                     | (Test Point)                       | $V_{OUT} = 0.18 V_{CC}^2$                |                                                     | 38V <sub>CC</sub>   |       |

| I <sub>CL</sub>     | Low Clamp Current                  | $-3 < V_{IN} \le -1$                     | -25 + (V <sub>IN</sub> + 1)/0.015                   |                     | mA    |

| I <sub>CH</sub>     | High Clamp Current                 | $-3 < V_{IN} \le -1$                     | 25 + (V <sub>IN</sub> – V <sub>OUT</sub> – 1)/0.015 |                     | mA    |

| slew <sub>R</sub>   | Output Rise Slew Rate <sup>3</sup> | $0.2V_{CC}$ to $0.6V_{CC}$ load          | 1                                                   | 4                   | V/ns  |

| slew <sub>F</sub>   | Output Fall Slew Rate <sup>3</sup> | $0.6V_{CC}$ to $0.2V_{CC}$ load          | 1                                                   | 4                   | V/ns  |

#### Table 1-9 • A54SX16P AC Specifications (3.3 V PCI Operation)

Notes:

1. Refer to the V/I curves in Figure 1-10 on page 1-14. Switching current characteristics for REQ# and GNT# are permitted to be one half of that specified here; i.e., half size output drivers may be used on these signals. This specification does not apply to CLK and RST# which are system outputs. "Switching Current High" specification are not relevant to SERR#, INTA#, INTB#, INTC#, and INTD# which are open drain outputs.

2. Maximum current requirements must be met as drivers pull beyond the last step voltage. Equations defining these maximums (C and D) are provided with the respective diagrams in Figure 1-10 on page 1-14. The equation defined maxima should be met by design. In order to facilitate component testing, a maximum current test point is defined for each side of the output driver.

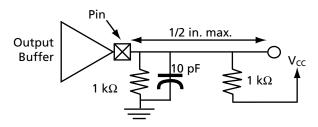

3. This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the instantaneous rate at any point within the transition range. The specified load (diagram below) is optional; i.e., the designer may elect to meet this parameter with an unloaded output per the latest revision of the PCI Local Bus Specification. However, adherence to both maximum and minimum parameters is required (the maximum is no longer simply a guideline). Rise slew rate does not apply to open drain outputs.

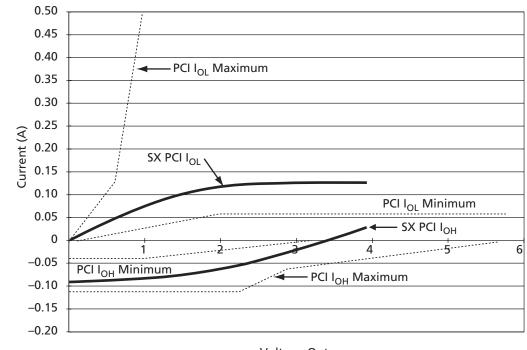

Figure 1-10 shows the 3.3 V PCI V/I curve and the minimum and maximum PCI drive characteristics of the A54SX16P device.

# Voltage Out

### Figure 1-10 • 3.3 V PCI Curve for A54SX16P Device

$I_{OH} = (98.0/V_{CC}) \times (V_{OUT} - V_{CC}) \times (V_{OUT} + 0.4V_{CC})$ for V<sub>CC</sub> > V<sub>OUT</sub> > 0.7 V<sub>CC</sub>  $I_{OL} = (256/V_{CC}) \times V_{OUT} \times (V_{CC} - V_{OUT})$ for 0 V < V<sub>OUT</sub> < 0.18 V<sub>CC</sub>

EQ 1-3

EQ 1-4

# **Evaluating Power in SX Devices**

A critical element of system reliability is the ability of electronic devices to safely dissipate the heat generated during operation. The thermal characteristics of a circuit depend on the device and package used, the operating temperature, the operating current, and the system's ability to dissipate heat.

You should complete a power evaluation early in the design process to help identify potential heat-related problems in the system and to prevent the system from exceeding the device's maximum allowed junction temperature.

The actual power dissipated by most applications is significantly lower than the power the package can dissipate. However, a thermal analysis should be performed for all projects. To perform a power evaluation, follow these steps:

- 1. Estimate the power consumption of the application.

- 2. Calculate the maximum power allowed for the device and package.

- 3. Compare the estimated power and maximum power values.

# **Estimating Power Consumption**

The total power dissipation for the SX family is the sum of the DC power dissipation and the AC power dissipation. Use EQ 1-5 to calculate the estimated power consumption of your application.

$$P_{Total} = P_{DC} + P_{AC}$$

р

х

у

r<sub>1</sub>

fn

fp

f<sub>s1</sub>

### **DC** Power Dissipation

The power due to standby current is typically a small component of the overall power. The Standby power is shown in Table 1-12 for commercial, worst-case conditions (70°C).

| Table 1-12 | • Sta | ndby Pov | ver |

|------------|-------|----------|-----|

|------------|-------|----------|-----|

| I <sub>cc</sub> | V <sub>cc</sub> | Power   |  |  |

|-----------------|-----------------|---------|--|--|

| 4 mA            | 3.6 V           | 14.4 mW |  |  |

The DC power dissipation is defined in EO 1-6.

$P_{DC} = (I_{standby}) \times V_{CCA} + (I_{standby}) \times V_{CCR} +$  $(I_{standbv}) \times V_{CCI} + xV_{OL} \times I_{OL} + y(V_{CCI} - V_{OH}) \times V_{OH}$

EQ 1-6

# **AC Power Dissipation**

The power dissipation of the SX Family is usually dominated by the dynamic power dissipation. Dynamic power dissipation is a function of frequency, equivalent capacitance, and power supply voltage. The AC power dissipation is defined in EQ 1-7 and EQ 1-8.

EQ 1-7

$P_{AC} = V_{CCA}^2 \times [(m \times C_{EOM} \times f_m)_{Module} +$  $(n \times C_{EOI} \times f_n)_{Input Buffer} + (p \times (C_{EOO} + C_L) \times f_p)_{Output Buffer} +$  $(0.5 \times (q_1 \times C_{EQCR} \times f_{q1}) + (r_1 \times f_{q1}))_{RCLKA} +$  $(0.5 \times (q2 \times CEQCR \times f_{q2}) + (r2 \times f_{q2}))RCLKB +$  $(0.5 \times (s_1 \times C_{EOHV} \times f_{s1}) + (C_{EOHF} \times f_{s1}))_{HCLK}]$

EQ 1-8

### **Definition of Terms Used in Formula**

| m | = | Number of logic modules switching at f <sub>m</sub> |

|---|---|-----------------------------------------------------|

| n | = | Number of input buffers switching at f <sub>p</sub> |

- = Number of input buffers switching at f<sub>n</sub>

- Number of output buffers switching at fp =

- Number of clock loads on the first routed array  $q_1$ clock

- Number of clock loads on the second routed array =  $q_2$ clock

- = Number of I/Os at logic low

- Number of I/Os at logic high =

- = Fixed capacitance due to first routed array clock

- Fixed capacitance due to second routed array = r<sub>2</sub> clock

- Number of clock loads on the dedicated array = s<sub>1</sub> clock

$$C_{EQM}$$

= Equivalent capacitance of logic modules in pF

- Equivalent capacitance of input buffers in pF C<sub>EQI</sub> =

- Equivalent capacitance of output buffers in pF  $C_{EOO} =$

- Equivalent capacitance of routed array clock in pF  $C_{EOCR} =$

- Variable capacitance of dedicated array clock  $C_{EOHV} =$

- Fixed capacitance of dedicated array clock  $C_{EOHF} =$

- C = Output lead capacitance in pF

- Average logic module switching rate in MHz fm =

- = Average input buffer switching rate in MHz

- = Average output buffer switching rate in MHz

- = Average first routed array clock rate in MHz f<sub>q1</sub>

- Average second routed array clock rate in MHz f<sub>q2</sub> =

- = Average dedicated array clock rate in MHz

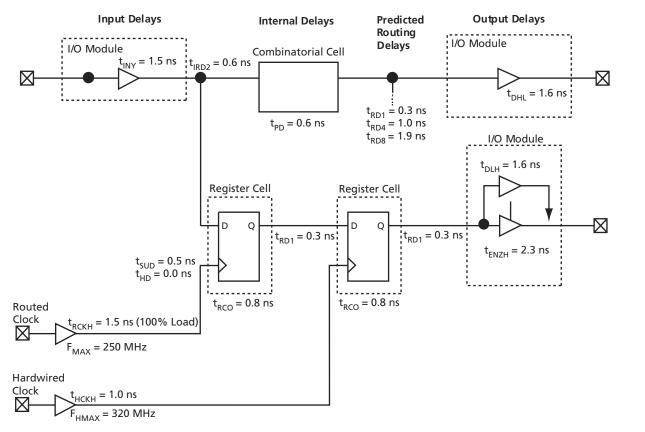

# **SX Timing Model**

### Figure 1-12 • SX Timing Model

### **Hardwired Clock**

External Setup =  $t_{INY} + t_{IRD1} + t_{SUD} - t_{HCKH}$ = 1.5 + 0.3 + 0.5 - 1.0 = 1.3 ns

Clock-to-Out (Pin-to-Pin)

$$= t_{HCKH} + t_{RCO} + t_{RD1} + t_{DHL}$$

= 1.0 + 0.8 + 0.3 + 1.6 = 3.7 r

EQ 1-16

#### **Routed Clock**

|         | External Setup = $t_{INY} + t_{IRD1} + t_{SUD} - t_{RCKH}$<br>= 1.5 + 0.3 + 0.5 - 1.5 = 0.8 ns |         |

|---------|------------------------------------------------------------------------------------------------|---------|

| EQ 1-15 |                                                                                                | EQ 1-17 |

|         | Clock-to-Out (Pin-to-Pin)                                                                      |         |

|         | $= t_{RCKH} + t_{RCO} + t_{RD1} + t_{DHL}$                                                     |         |

|         | = 1.52+ 0.8 + 0.3 + 1.6 = 4.2 ns                                                               |         |

| EO 1-16 |                                                                                                | EQ 1-18 |

### Table 1-17 A54SX08 Timing Characteristics (Continued)

| (Worst-Case Commercial Conditions, | V <sub>CCR</sub> = 4.75 V, V <sub>CC</sub> | <sub>A,</sub> V <sub>CCI</sub> = 3.0 V, T <sub>J</sub> = 70°C) |

|------------------------------------|--------------------------------------------|----------------------------------------------------------------|

|------------------------------------|--------------------------------------------|----------------------------------------------------------------|

|                                           |                                                         | '-3' \$ | Speed | '-2' \$ | 5peed | '-1' \$ | 5peed | 'Std' Speed |      |       |

|-------------------------------------------|---------------------------------------------------------|---------|-------|---------|-------|---------|-------|-------------|------|-------|

| Parameter                                 | Description                                             | Min.    | Max.  | Min.    | Max.  | Min.    | Max.  | Min.        | Max. | Units |

| Dedicated (Hardwired) Array Clock Network |                                                         |         |       |         |       |         |       |             |      |       |

| t <sub>HCKH</sub>                         | Input LOW to HIGH (pad to R-Cell input)                 |         | 1.0   |         | 1.1   |         | 1.3   |             | 1.5  | ns    |

| t <sub>HCKL</sub>                         | Input HIGH to LOW (pad to R-Cell input)                 |         | 1.0   |         | 1.2   |         | 1.4   |             | 1.6  | ns    |

| t <sub>HPWH</sub>                         | Minimum Pulse Width HIGH                                | 1.4     |       | 1.6     |       | 1.8     |       | 2.1         |      | ns    |

| t <sub>HPWL</sub>                         | Minimum Pulse Width LOW                                 | 1.4     |       | 1.6     |       | 1.8     |       | 2.1         |      | ns    |

| t <sub>HCKSW</sub>                        | Maximum Skew                                            |         | 0.1   |         | 0.2   |         | 0.2   |             | 0.2  | ns    |

| t <sub>HP</sub>                           | Minimum Period                                          | 2.7     |       | 3.1     |       | 3.6     |       | 4.2         |      | ns    |

| f <sub>HMAX</sub>                         | Maximum Frequency                                       |         | 350   |         | 320   |         | 280   |             | 240  | MHz   |

| Routed Arra                               | ay Clock Networks                                       |         |       |         |       |         |       |             |      |       |

| t <sub>RCKH</sub>                         | Input LOW to HIGH (light load)<br>(pad to R-Cell input) |         | 1.3   |         | 1.5   |         | 1.7   |             | 2.0  | ns    |

| t <sub>RCKL</sub>                         | Input HIGH to LOW (light load)<br>(pad to R-Cell Input) |         | 1.4   |         | 1.6   |         | 1.8   |             | 2.1  | ns    |

| t <sub>RCKH</sub>                         | Input LOW to HIGH (50% load)<br>(pad to R-Cell input)   |         | 1.4   |         | 1.7   |         | 1.9   |             | 2.2  | ns    |

| t <sub>RCKL</sub>                         | Input HIGH to LOW (50% load)<br>(pad to R-Cell input)   |         | 1.5   |         | 1.7   |         | 2.0   |             | 2.3  | ns    |

| t <sub>RCKH</sub>                         | Input LOW to HIGH (100% load)<br>(pad to R-Cell input)  |         | 1.5   |         | 1.7   |         | 1.9   |             | 2.2  | ns    |

| t <sub>RCKL</sub>                         | Input HIGH to LOW (100% load)<br>(pad to R-Cell input)  |         | 1.5   |         | 1.8   |         | 2.0   |             | 2.3  | ns    |

| t <sub>RPWH</sub>                         | Min. Pulse Width HIGH                                   | 2.1     |       | 2.4     |       | 2.7     |       | 3.2         |      | ns    |

| t <sub>RPWL</sub>                         | Min. Pulse Width LOW                                    | 2.1     |       | 2.4     |       | 2.7     |       | 3.2         |      | ns    |

| t <sub>RCKSW</sub>                        | Maximum Skew (light load)                               |         | 0.1   |         | 0.2   |         | 0.2   |             | 0.2  | ns    |

| t <sub>RCKSW</sub>                        | Maximum Skew (50% load)                                 |         | 0.3   |         | 0.3   |         | 0.4   |             | 0.4  | ns    |

| t <sub>RCKSW</sub>                        | Maximum Skew (100% load)                                |         | 0.3   |         | 0.3   |         | 0.4   |             | 0.4  | ns    |

| TTL Output                                | Module Timing1                                          |         |       |         |       |         |       |             |      |       |

| t <sub>DLH</sub>                          | Data-to-Pad LOW to HIGH                                 |         | 1.6   |         | 1.9   |         | 2.1   |             | 2.5  | ns    |

| t <sub>DHL</sub>                          | Data-to-Pad HIGH to LOW                                 |         | 1.6   |         | 1.9   |         | 2.1   |             | 2.5  | ns    |

| t <sub>ENZL</sub>                         | Enable-to-Pad, Z to L                                   |         | 2.1   |         | 2.4   |         | 2.8   |             | 3.2  | ns    |

| t <sub>ENZH</sub>                         | Enable-to-Pad, Z to H                                   |         | 2.3   |         | 2.7   |         | 3.1   |             | 3.6  | ns    |

| t <sub>ENLZ</sub>                         | Enable-to-Pad, L to Z                                   |         | 1.4   |         | 1.7   |         | 1.9   |             | 2.2  | ns    |

Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

### Table 1-18 A54SX16 Timing Characteristics (Continued)

| (Worst-Case Commercial Conditions, V | / <sub>CCR</sub> = 4.75 V, V <sub>CC</sub> | <sub>CA</sub> ,V <sub>CCI</sub> = 3.0 V, T <sub>J</sub> = 70°C) |

|--------------------------------------|--------------------------------------------|-----------------------------------------------------------------|

|--------------------------------------|--------------------------------------------|-----------------------------------------------------------------|

|                    |                                                         | '-3' ! | Speed | '-2' : | Speed | '-1' : | Speed | 'Std' | Speed |       |

|--------------------|---------------------------------------------------------|--------|-------|--------|-------|--------|-------|-------|-------|-------|

| Parameter          | Description                                             |        | Max.  | Min.   | Max.  | Min.   | Max.  | Min.  | Max.  | Units |

| Dedicated (        | Hardwired) Array Clock Network                          |        |       |        |       |        |       |       |       |       |

| t <sub>HCKH</sub>  | Input LOW to HIGH (pad to R-Cell input)                 |        | 1.2   |        | 1.4   |        | 1.5   |       | 1.8   | ns    |

| t <sub>HCKL</sub>  | Input HIGH to LOW (pad to R-Cell input)                 |        | 1.2   |        | 1.4   |        | 1.6   |       | 1.9   | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width HIGH                                | 1.4    |       | 1.6    |       | 1.8    |       | 2.1   |       | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width LOW                                 | 1.4    |       | 1.6    |       | 1.8    |       | 2.1   |       | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |        | 0.2   |        | 0.2   |        | 0.3   |       | 0.3   | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.7    |       | 3.1    |       | 3.6    |       | 4.2   |       | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |        | 350   |        | 320   |        | 280   |       | 240   | MHz   |

| Routed Arra        | ay Clock Networks                                       |        |       |        |       |        |       |       |       |       |

| t <sub>RCKH</sub>  | Input LOW to HIGH (light load)<br>(pad to R-Cell input) |        | 1.6   |        | 1.8   |        | 2.1   |       | 2.5   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (light load)<br>(pad to R-Cell input) |        | 1.8   |        | 2.0   |        | 2.3   |       | 2.7   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (50% load)<br>(pad to R-Cell input)   |        | 1.8   |        | 2.1   |        | 2.5   |       | 2.8   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (50% load)<br>(pad to R-Cell input)   |        | 2.0   |        | 2.2   |        | 2.5   |       | 3.0   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (100% load)<br>(pad to R-Cell input)  |        | 1.8   |        | 2.1   |        | 2.4   |       | 2.8   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (100% load)<br>(pad to R-Cell input)  |        | 2.0   |        | 2.2   |        | 2.5   |       | 3.0   | ns    |

| t <sub>RPWH</sub>  | Min. Pulse Width HIGH                                   | 2.1    |       | 2.4    |       | 2.7    |       | 3.2   |       | ns    |

| t <sub>RPWL</sub>  | Min. Pulse Width LOW                                    | 2.1    |       | 2.4    |       | 2.7    |       | 3.2   |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (light load)                               |        | 0.5   |        | 0.5   |        | 0.5   |       | 0.7   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% load)                                 |        | 0.5   |        | 0.6   |        | 0.7   |       | 0.8   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% load)                                |        | 0.5   |        | 0.6   |        | 0.7   |       | 0.8   | ns    |

| TTL Output         | Module Timing <sup>3</sup>                              |        |       |        |       |        |       |       |       |       |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                                 |        | 1.6   |        | 1.9   |        | 2.1   |       | 2.5   | ns    |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                                 |        | 1.6   |        | 1.9   |        | 2.1   |       | 2.5   | ns    |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                                   |        | 2.1   |        | 2.4   |        | 2.8   |       | 3.2   | ns    |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                                   |        | 2.3   |        | 2.7   |        | 3.1   |       | 3.6   | ns    |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                                   |        | 1.4   |        | 1.7   |        | 1.9   |       | 2.2   | ns    |

| t <sub>ENHZ</sub>  | Enable-to-Pad, H to Z                                   |        | 1.3   |        | 1.5   |        | 1.7   |       | 2.0   | ns    |

Notes:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 35 pF loading, except  $t_{ENZL}$  and  $t_{ENZH}$ . For  $t_{ENZL}$  and  $t_{ENZH}$ , the loading is 5 pF.

# A54SX16P Timing Characteristics

Table 1-19 • A54SX16P Timing Characteristics

(Worst-Case Commercial Conditions, V<sub>CCR</sub> = 4.75 V, V<sub>CCA</sub>, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                     |                                      | '-3' 9 | 5peed | '-2' \$ | 5peed | '-1' : | 5peed | 'Std' | Speed |       |

|---------------------|--------------------------------------|--------|-------|---------|-------|--------|-------|-------|-------|-------|

| Parameter           | Description                          | Min.   | Max.  | Min.    | Max.  | Min.   | Max.  | Min.  | Max.  | Units |

| C-Cell Propa        | agation Delays <sup>1</sup>          |        |       |         |       |        |       |       |       |       |

| t <sub>PD</sub>     | Internal Array Module                |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9   | ns    |

| Predicted R         | outing Delays <sup>2</sup>           |        |       |         |       |        |       |       |       |       |

| t <sub>DC</sub>     | FO = 1 Routing Delay, Direct Connect |        | 0.1   |         | 0.1   |        | 0.1   |       | 0.1   | ns    |

| t <sub>FC</sub>     | FO = 1 Routing Delay, Fast Connect   |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5   | ns    |

| t <sub>RD1</sub>    | FO = 1 Routing Delay                 |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5   | ns    |

| t <sub>RD2</sub>    | FO = 2 Routing Delay                 |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9   | ns    |

| t <sub>RD3</sub>    | FO = 3 Routing Delay                 |        | 0.8   |         | 0.9   |        | 1.0   |       | 1.2   | ns    |

| t <sub>RD4</sub>    | FO = 4 Routing Delay                 |        | 1.0   |         | 1.2   |        | 1.4   |       | 1.6   | ns    |

| t <sub>RD8</sub>    | FO = 8 Routing Delay                 |        | 1.9   |         | 2.2   |        | 2.5   |       | 2.9   | ns    |

| t <sub>RD12</sub>   | FO = 12 Routing Delay                |        | 2.8   |         | 3.2   |        | 3.7   |       | 4.3   | ns    |

| <b>R-Cell Timir</b> | ng                                   |        |       |         |       |        |       |       |       |       |

| t <sub>RCO</sub>    | Sequential Clock-to-Q                |        | 0.9   |         | 1.1   |        | 1.3   |       | 1.4   | ns    |

| t <sub>CLR</sub>    | Asynchronous Clear-to-Q              |        | 0.5   |         | 0.6   |        | 0.7   |       | 0.8   | ns    |

| t <sub>PRESET</sub> | Asynchronous Preset-to-Q             |        | 0.7   |         | 0.8   |        | 0.9   |       | 1.0   | ns    |

| t <sub>SUD</sub>    | Flip-Flop Data Input Set-Up          | 0.5    |       | 0.5     |       | 0.7    |       | 0.8   |       | ns    |

| t <sub>HD</sub>     | Flip-Flop Data Input Hold            | 0.0    |       | 0.0     |       | 0.0    |       | 0.0   |       | ns    |

| t <sub>WASYN</sub>  | Asynchronous Pulse Width             | 1.4    |       | 1.6     |       | 1.8    |       | 2.1   |       | ns    |

| Input Modu          | le Propagation Delays                |        |       |         |       |        |       |       |       |       |

| t <sub>INYH</sub>   | Input Data Pad-to-Y HIGH             |        | 1.5   |         | 1.7   |        | 1.9   |       | 2.2   | ns    |

| t <sub>INYL</sub>   | Input Data Pad-to-Y LOW              |        | 1.5   |         | 1.7   |        | 1.9   |       | 2.2   | ns    |

| Predicted Ir        | put Routing Delays <sup>2</sup>      |        |       |         |       |        |       |       |       |       |

| t <sub>IRD1</sub>   | FO = 1 Routing Delay                 |        | 0.3   |         | 0.4   |        | 0.4   |       | 0.5   | ns    |

| t <sub>IRD2</sub>   | FO = 2 Routing Delay                 |        | 0.6   |         | 0.7   |        | 0.8   |       | 0.9   | ns    |

| t <sub>IRD3</sub>   | FO = 3 Routing Delay                 |        | 0.8   |         | 0.9   |        | 1.0   |       | 1.2   | ns    |

| t <sub>IRD4</sub>   | FO = 4 Routing Delay                 |        | 1.0   |         | 1.2   |        | 1.4   |       | 1.6   | ns    |

| t <sub>IRD8</sub>   | FO = 8 Routing Delay                 |        | 1.9   |         | 2.2   |        | 2.5   |       | 2.9   | ns    |

| t <sub>IRD12</sub>  | FO = 12 Routing Delay                |        | 2.8   |         | 3.2   |        | 3.7   |       | 4.3   | ns    |

Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 10 pF loading.

### Table 1-19 • A54SX16P Timing Characteristics (Continued)

| (Worst-Case Commercial Conditions | , V <sub>CCR</sub> = 4.75 V, V <sub>C</sub> | <sub>CCA</sub> ,V <sub>CCI</sub> = 3.0 V, T <sub>J</sub> = 70°C) |

|-----------------------------------|---------------------------------------------|------------------------------------------------------------------|

|-----------------------------------|---------------------------------------------|------------------------------------------------------------------|

|                   |                            | '-3' | Speed | '-2' 9 | 5peed | '-1' 9 | 5peed | 'Std' | Speed |       |

|-------------------|----------------------------|------|-------|--------|-------|--------|-------|-------|-------|-------|

| Parameter         | Description                | Min. | Max.  | Min.   | Max.  | Min.   | Max.  | Min.  | Max.  | Units |

| TTL/PCI Out       | put Module Timing          |      |       |        |       |        |       |       |       |       |

| t <sub>DLH</sub>  | Data-to-Pad LOW to HIGH    |      | 1.5   |        | 1.7   |        | 2.0   |       | 2.3   | ns    |

| t <sub>DHL</sub>  | Data-to-Pad HIGH to LOW    |      | 1.9   |        | 2.2   |        | 2.4   |       | 2.9   | ns    |

| t <sub>ENZL</sub> | Enable-to-Pad, Z to L      |      | 2.3   |        | 2.6   |        | 3.0   |       | 3.5   | ns    |

| t <sub>ENZH</sub> | Enable-to-Pad, Z to H      |      | 1.5   |        | 1.7   |        | 1.9   |       | 2.3   | ns    |

| t <sub>ENLZ</sub> | Enable-to-Pad, L to Z      |      | 2.7   |        | 3.1   |        | 3.5   |       | 4.1   | ns    |

| t <sub>ENHZ</sub> | Enable-to-Pad, H to Z      |      | 2.9   |        | 3.3   |        | 3.7   |       | 4.4   | ns    |

| PCI Output        | Module Timing <sup>3</sup> |      |       |        |       |        |       |       |       |       |

| t <sub>DLH</sub>  | Data-to-Pad LOW to HIGH    |      | 1.8   |        | 2.0   |        | 2.3   |       | 2.7   | ns    |

| t <sub>DHL</sub>  | Data-to-Pad HIGH to LOW    |      | 1.7   |        | 2.0   |        | 2.2   |       | 2.6   | ns    |

| t <sub>ENZL</sub> | Enable-to-Pad, Z to L      |      | 0.8   |        | 1.0   |        | 1.1   |       | 1.3   | ns    |

| t <sub>ENZH</sub> | Enable-to-Pad, Z to H      |      | 1.2   |        | 1.2   |        | 1.5   |       | 1.8   | ns    |

| t <sub>ENLZ</sub> | Enable-to-Pad, L to Z      |      | 1.0   |        | 1.1   |        | 1.3   |       | 1.5   | ns    |

| t <sub>ENHZ</sub> | Enable-to-Pad, H to Z      |      | 1.1   |        | 1.3   |        | 1.5   |       | 1.7   | ns    |

| TTL Output        | Module Timing              |      |       |        |       |        |       |       |       |       |

| t <sub>DLH</sub>  | Data-to-Pad LOW to HIGH    |      | 2.1   |        | 2.5   |        | 2.8   |       | 3.3   | ns    |

| t <sub>DHL</sub>  | Data-to-Pad HIGH to LOW    |      | 2.0   |        | 2.3   |        | 2.6   |       | 3.1   | ns    |

| t <sub>ENZL</sub> | Enable-to-Pad, Z to L      |      | 2.5   |        | 2.9   |        | 3.2   |       | 3.8   | ns    |

| t <sub>ENZH</sub> | Enable-to-Pad, Z to H      |      | 3.0   |        | 3.5   |        | 3.9   |       | 4.6   | ns    |

| t <sub>ENLZ</sub> | Enable-to-Pad, L to Z      |      | 2.3   |        | 2.7   |        | 3.1   |       | 3.6   | ns    |

| t <sub>ENHZ</sub> | Enable-to-Pad, H to Z      |      | 2.9   |        | 3.3   |        | 3.7   |       | 4.4   | ns    |

Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 10 pF loading.

### Table 1-20 • A54SX32 Timing Characteristics (Continued)

### (Worst-Case Commercial Conditions, V<sub>CCR</sub>= 4.75 V, V<sub>CCA</sub>, V<sub>CCI</sub> = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                         | '-3' \$ | Speed | '-2' ! | 5peed | '-1' \$ | Speed | 'Std' | Speed |       |

|--------------------|---------------------------------------------------------|---------|-------|--------|-------|---------|-------|-------|-------|-------|

| Parameter          | Description                                             | Min.    | Max.  | Min.   | Max.  | Min.    | Max.  | Min.  | Max.  | Units |

| Dedicated (        | Hardwired) Array Clock Network                          |         |       |        |       |         |       |       |       |       |

| t <sub>HCKH</sub>  | Input LOW to HIGH (pad to R-Cell input)                 |         | 1.9   |        | 2.1   |         | 2.4   |       | 2.8   | ns    |

| t <sub>HCKL</sub>  | Input HIGH to LOW (pad to R-Cell input)                 |         | 1.9   |        | 2.1   |         | 2.4   |       | 2.8   | ns    |

| t <sub>HPWH</sub>  | Minimum Pulse Width HIGH                                | 1.4     |       | 1.6    |       | 1.8     |       | 2.1   |       | ns    |

| t <sub>HPWL</sub>  | Minimum Pulse Width LOW                                 | 1.4     |       | 1.6    |       | 1.8     |       | 2.1   |       | ns    |

| t <sub>HCKSW</sub> | Maximum Skew                                            |         | 0.3   |        | 0.4   |         | 0.4   |       | 0.5   | ns    |

| t <sub>HP</sub>    | Minimum Period                                          | 2.7     |       | 3.1    |       | 3.6     |       | 4.2   |       | ns    |

| f <sub>HMAX</sub>  | Maximum Frequency                                       |         | 350   |        | 320   |         | 280   |       | 240   | MHz   |

| Routed Arra        | ay Clock Networks                                       |         |       |        |       |         |       |       |       |       |

| t <sub>rckh</sub>  | Input LOW to HIGH (light load)<br>(pad to R-Cell input) |         | 2.4   |        | 2.7   |         | 3.0   |       | 3.5   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (light load)<br>(pad to R-Cell input) |         | 2.4   |        | 2.7   |         | 3.1   |       | 3.6   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (50% load)<br>(pad to R-Cell input)   |         | 2.7   |        | 3.0   |         | 3.5   |       | 4.1   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (50% load)<br>(pad to R-Cell input)   |         | 2.7   |        | 3.1   |         | 3.6   |       | 4.2   | ns    |

| t <sub>RCKH</sub>  | Input LOW to HIGH (100% load)<br>(pad to R-Cell input)  |         | 2.7   |        | 3.1   |         | 3.5   |       | 4.1   | ns    |

| t <sub>RCKL</sub>  | Input HIGH to LOW (100% load)<br>(pad to R-Cell input)  |         | 2.8   |        | 3.2   |         | 3.6   |       | 4.3   | ns    |

| t <sub>RPWH</sub>  | Min. Pulse Width HIGH                                   | 2.1     |       | 2.4    |       | 2.7     |       | 3.2   |       | ns    |

| t <sub>RPWL</sub>  | Min. Pulse Width LOW                                    | 2.1     |       | 2.4    |       | 2.7     |       | 3.2   |       | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (light load)                               |         | 0.85  |        | 0.98  |         | 1.1   |       | 1.3   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (50% load)                                 |         | 1.23  |        | 1.4   |         | 1.6   |       | 1.9   | ns    |

| t <sub>RCKSW</sub> | Maximum Skew (100% load)                                |         | 1.30  |        | 1.5   |         | 1.7   |       | 2.0   | ns    |

| TTL Output         | Module Timing <sup>3</sup>                              |         |       |        |       |         |       |       |       |       |

| t <sub>DLH</sub>   | Data-to-Pad LOW to HIGH                                 |         | 1.6   |        | 1.9   |         | 2.1   |       | 2.5   | ns    |

| t <sub>DHL</sub>   | Data-to-Pad HIGH to LOW                                 |         | 1.6   |        | 1.9   |         | 2.1   |       | 2.5   | ns    |

| t <sub>ENZL</sub>  | Enable-to-Pad, Z to L                                   |         | 2.1   |        | 2.4   |         | 2.8   |       | 3.2   | ns    |

| t <sub>ENZH</sub>  | Enable-to-Pad, Z to H                                   |         | 2.3   |        | 2.7   |         | 3.1   |       | 3.6   | ns    |

| t <sub>ENLZ</sub>  | Enable-to-Pad, L to Z                                   |         | 1.4   |        | 1.7   |         | 1.9   |       | 2.2   | ns    |

| t <sub>enhz</sub>  | Enable-to-Pad, H to Z                                   |         | 1.3   |        | 1.5   |         | 1.7   |       | 2.0   | ns    |

#### Note:

1. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn}$ ,  $t_{RCO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

3. Delays based on 35 pF loading, except  $t_{ENZL}$  and  $t_{ENZH}$ . For  $t_{ENZL}$  and  $t_{ENZH}$  the loading is 5 pF.

# Package Pin Assignments

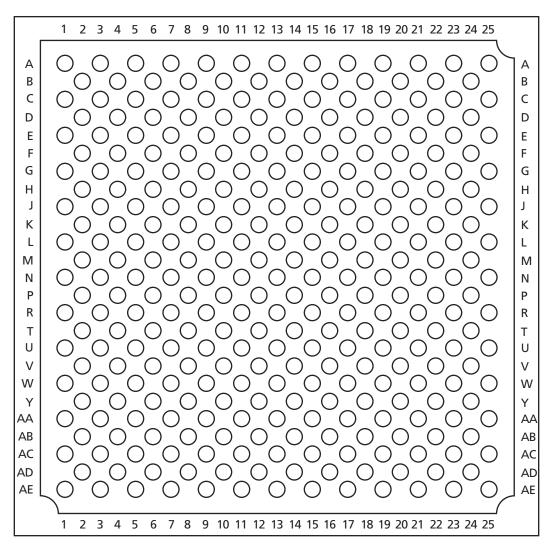

# 84-Pin PLCC

Figure 2-1 • 84-Pin PLCC (Top View)

### Note

For Package Manufacturing and Environmental information, visit the Package Resource center at http://www.actel.com/products/rescenter/package/index.html.

|            | 144-Pi              | n TQFP               |                     | 144-Pin TQFP |                     |                      |                     |  |  |  |

|------------|---------------------|----------------------|---------------------|--------------|---------------------|----------------------|---------------------|--|--|--|

| Pin Number | A54SX08<br>Function | A54SX16P<br>Function | A54SX32<br>Function | Pin Number   | A54SX08<br>Function | A54SX16P<br>Function | A54SX32<br>Function |  |  |  |

| 73         | GND                 | GND                  | GND                 | 109          | GND                 | GND                  | GND                 |  |  |  |

| 74         | I/O                 | I/O                  | I/O                 | 110          | I/O                 | I/O                  | I/O                 |  |  |  |

| 75         | I/O                 | I/O                  | I/O                 | 111          | I/O                 | I/O                  | I/O                 |  |  |  |

| 76         | I/O                 | I/O                  | I/O                 | 112          | I/O                 | I/O                  | I/O                 |  |  |  |

| 77         | I/O                 | I/O                  | I/O                 | 113          | I/O                 | I/O                  | I/O                 |  |  |  |

| 78         | I/O                 | I/O                  | I/O                 | 114          | I/O                 | I/O                  | I/O                 |  |  |  |

| 79         | V <sub>CCA</sub>    | V <sub>CCA</sub>     | V <sub>CCA</sub>    | 115          | V <sub>CCI</sub>    | V <sub>CCI</sub>     | V <sub>CCI</sub>    |  |  |  |

| 80         | V <sub>CCI</sub>    | V <sub>CCI</sub>     | V <sub>CCI</sub>    | 116          | I/O                 | I/O                  | I/O                 |  |  |  |

| 81         | GND                 | GND                  | GND                 | 117          | I/O                 | I/O                  | I/O                 |  |  |  |

| 82         | I/O                 | I/O                  | I/O                 | 118          | I/O                 | I/O                  | I/O                 |  |  |  |

| 83         | I/O                 | I/O                  | I/O                 | 119          | I/O                 | I/O                  | I/O                 |  |  |  |

| 84         | I/O                 | I/O                  | I/O                 | 120          | I/O                 | I/O                  | I/O                 |  |  |  |

| 85         | I/O                 | I/O                  | I/O                 | 121          | I/O                 | I/O                  | I/O                 |  |  |  |

| 86         | I/O                 | I/O                  | I/O                 | 122          | I/O                 | I/O                  | I/O                 |  |  |  |

| 87         | I/O                 | I/O                  | I/O                 | 123          | I/O                 | I/O                  | I/O                 |  |  |  |

| 88         | I/O                 | I/O                  | I/O                 | 124          | I/O                 | I/O                  | I/O                 |  |  |  |

| 89         | V <sub>CCA</sub>    | V <sub>CCA</sub>     | V <sub>CCA</sub>    | 125          | CLKA                | CLKA                 | CLKA                |  |  |  |

| 90         | V <sub>CCR</sub>    | V <sub>CCR</sub>     | V <sub>CCR</sub>    | 126          | CLKB                | CLKB                 | CLKB                |  |  |  |

| 91         | I/O                 | I/O                  | I/O                 | 127          | V <sub>CCR</sub>    | V <sub>CCR</sub>     | V <sub>CCR</sub>    |  |  |  |

| 92         | I/O                 | I/O                  | I/O                 | 128          | GND                 | GND                  | GND                 |  |  |  |

| 93         | I/O                 | I/O                  | I/O                 | 129          | V <sub>CCA</sub>    | V <sub>CCA</sub>     | V <sub>CCA</sub>    |  |  |  |

| 94         | I/O                 | I/O                  | I/O                 | 130          | I/O                 | I/O                  | I/O                 |  |  |  |

| 95         | I/O                 | I/O                  | I/O                 | 131          | PRA, I/O            | PRA, I/O             | PRA, I/O            |  |  |  |

| 96         | I/O                 | I/O                  | I/O                 | 132          | I/O                 | I/O                  | I/O                 |  |  |  |

| 97         | I/O                 | I/O                  | I/O                 | 133          | I/O                 | I/O                  | I/O                 |  |  |  |

| 98         | V <sub>CCA</sub>    | V <sub>CCA</sub>     | V <sub>CCA</sub>    | 134          | I/O                 | I/O                  | I/O                 |  |  |  |

| 99         | GND                 | GND                  | GND                 | 135          | I/O                 | I/O                  | I/O                 |  |  |  |

| 100        | I/O                 | I/O                  | I/O                 | 136          | I/O                 | I/O                  | I/O                 |  |  |  |

| 101        | GND                 | GND                  | GND                 | 137          | I/O                 | I/O                  | I/O                 |  |  |  |

| 102        | V <sub>CCI</sub>    | V <sub>CCI</sub>     | V <sub>CCI</sub>    | 138          | I/O                 | I/O                  | I/O                 |  |  |  |

| 103        | I/O                 | I/O                  | I/O                 | 139          | I/O                 | I/O                  | I/O                 |  |  |  |

| 104        | I/O                 | I/O                  | I/O                 | 140          | V <sub>CCI</sub>    | V <sub>CCI</sub>     | V <sub>CCI</sub>    |  |  |  |

| 105        | I/O                 | I/O                  | I/O                 | 141          | I/O                 | I/O                  | I/O                 |  |  |  |

| 106        | I/O                 | I/O                  | I/O                 | 142          | I/O                 | I/O                  | I/O                 |  |  |  |

| 107        | I/O                 | I/O                  | I/O                 | 143          | I/O                 | I/O                  | I/O                 |  |  |  |

| 108        | I/O                 | I/O                  | I/O                 | 144          | TCK, I/O            | TCK, I/O             | TCK, I/O            |  |  |  |

|               | 100-Pin VQF         | P                                |

|---------------|---------------------|----------------------------------|

| Pin<br>Number | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function |

| 1             | GND                 | GND                              |

| 2             | TDI, I/O            | TDI, I/O                         |

| 3             | I/O                 | I/O                              |

| 4             | I/O                 | I/O                              |

| 5             | I/O                 | I/O                              |

| 6             | I/O                 | I/O                              |

| 7             | TMS                 | TMS                              |

| 8             | V <sub>CCI</sub>    | V <sub>CCI</sub>                 |

| 9             | GND                 | GND                              |

| 10            | I/O                 | I/O                              |

| 11            | I/O                 | I/O                              |

| 12            | I/O                 | I/O                              |

| 13            | I/O                 | I/O                              |

| 14            | I/O                 | I/O                              |

| 15            | I/O                 | I/O                              |

| 16            | I/O                 | I/O                              |

| 17            | I/O                 | I/O                              |

| 18            | I/O                 | I/O                              |

| 19            | I/O                 | I/O                              |

| 20            | V <sub>CCI</sub>    | V <sub>CCI</sub>                 |

| 21            | I/O                 | I/O                              |

| 22            | I/O                 | I/O                              |

| 23            | I/O                 | I/O                              |

| 24            | I/O                 | I/O                              |

| 25            | I/O                 | I/O                              |

| 26            | I/O                 | I/O                              |

| 27            | I/O                 | I/O                              |

| 28            | I/O                 | I/O                              |

| 29            | I/O                 | I/O                              |

| 30            | I/O                 | I/O                              |

| 31            | I/O                 | I/O                              |

| 32            | I/O                 | I/O                              |

| 33            | I/O                 | I/O                              |

| 34            | PRB, I/O            | PRB, I/O                         |

|               | 100-Pin VQF         | P                                |

|---------------|---------------------|----------------------------------|

| Pin<br>Number | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function |

| 35            | V <sub>CCA</sub>    | V <sub>CCA</sub>                 |

| 36            | GND                 | GND                              |

| 37            | V <sub>CCR</sub>    | V <sub>CCR</sub>                 |

| 38            | I/O                 | I/O                              |

| 39            | HCLK                | HCLK                             |

| 40            | I/O                 | I/O                              |

| 41            | I/O                 | I/O                              |

| 42            | I/O                 | I/O                              |

| 43            | I/O                 | I/O                              |

| 44            | V <sub>CCI</sub>    | V <sub>CCI</sub>                 |

| 45            | I/O                 | I/O                              |

| 46            | I/O                 | I/O                              |

| 47            | I/O                 | I/O                              |

| 48            | I/O                 | I/O                              |

| 49            | TDO, I/O            | TDO, I/O                         |

| 50            | I/O                 | I/O                              |

| 51            | GND                 | GND                              |

| 52            | I/O                 | I/O                              |

| 53            | I/O                 | I/O                              |

| 54            | I/O                 | I/O                              |

| 55            | I/O                 | I/O                              |

| 56            | I/O                 | I/O                              |

| 57            | V <sub>CCA</sub>    | V <sub>CCA</sub>                 |

| 58            | V <sub>CCI</sub>    | V <sub>CCI</sub>                 |

| 59            | I/O                 | I/O                              |

| 60            | I/O                 | I/O                              |

| 61            | I/O                 | I/O                              |

| 62            | I/O                 | I/O                              |

| 63            | I/O                 | I/O                              |

| 64            | I/O                 | I/O                              |

| 65            | I/O                 | I/O                              |

| 66            | I/O                 | I/O                              |

| 67            | V <sub>CCA</sub>    | V <sub>CCA</sub>                 |

| 68            | GND                 | GND                              |

|               | 100-Pin VQF         | P                                |

|---------------|---------------------|----------------------------------|

| Pin<br>Number | A54SX08<br>Function | A54SX16,<br>A54SX16P<br>Function |

| 69            | GND                 | GND                              |

| 70            | I/O                 | I/O                              |

| 71            | I/O                 | I/O                              |

| 72            | I/O                 | I/O                              |

| 73            | I/O                 | I/O                              |

| 74            | I/O                 | I/O                              |

| 75            | I/O                 | I/O                              |

| 76            | I/O                 | I/O                              |

| 77            | I/O                 | I/O                              |

| 78            | I/O                 | I/O                              |

| 79            | I/O                 | I/O                              |

| 80            | I/O                 | I/O                              |

| 81            | I/O                 | I/O                              |

| 82            | V <sub>CCI</sub>    | V <sub>CCI</sub>                 |

| 83            | I/O                 | I/O                              |

| 84            | I/O                 | I/O                              |

| 85            | I/O                 | I/O                              |

| 86            | I/O                 | I/O                              |

| 87            | CLKA                | CLKA                             |

| 88            | CLKB                | CLKB                             |

| 89            | V <sub>CCR</sub>    | V <sub>CCR</sub>                 |

| 90            | V <sub>CCA</sub>    | V <sub>CCA</sub>                 |

| 91            | GND                 | GND                              |

| 92            | PRA, I/O            | PRA, I/O                         |

| 93            | I/O                 | I/O                              |

| 94            | I/O                 | I/O                              |

| 95            | I/O                 | I/O                              |

| 96            | I/O                 | I/O                              |

| 97            | I/O                 | I/O                              |

| 98            | I/O                 | I/O                              |

| 99            | I/O                 | I/O                              |

| 100           | TCK, I/O            | TCK, I/O                         |

Actel

54SX Family FPGAs

# 313-Pin PBGA

Figure 2-6 • 313-Pin PBGA (Top View)

### Note

For Package Manufacturing and Environmental information, visit the Package Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 329-Pin PBGA  |                     | 329-Pin PBGA  |                  | 329-Pi | n PBGA              | 329-Pin PBGA  |                     |  |

|---------------|---------------------|---------------|------------------|--------|---------------------|---------------|---------------------|--|

| Pin<br>Number | A54SX32<br>Function | Pin<br>Number |                  |        | A54SX32<br>Function | Pin<br>Number | A54SX32<br>Function |  |

| A1            | GND                 | AA13          | I/O              | AC2    | V <sub>CCI</sub>    | B14           | I/O                 |  |

| A2            | GND                 | AA14          | I/O              | AC3    | NC                  | B15           | I/O                 |  |

| A3            | V <sub>CCI</sub>    | AA15          | I/O              | AC4    | I/O                 | B16           | I/O                 |  |

| A4            | NC                  | AA16          | I/O              | AC5    | I/O                 | B17           | I/O                 |  |

| A5            | I/O                 | AA17          | I/O              | AC6    | I/O                 | B18           | I/O                 |  |

| A6            | I/O                 | AA18          | I/O              | AC7    | I/O                 | B19           | I/O                 |  |

| A7            | V <sub>CCI</sub>    | AA19          | I/O              | AC8    | I/O                 | B20           | I/O                 |  |

| A8            | NC                  | AA20          | TDO, I/O         | AC9    | V <sub>CCI</sub>    | B21           | I/O                 |  |

| A9            | I/O                 | AA21          | V <sub>CCI</sub> | AC10   | I/O                 | B22           | GND                 |  |

| A10           | I/O                 | AA22          | I/O              | AC11   | I/O                 | B23           | V <sub>CCI</sub>    |  |

| A11           | I/O                 | AA23          | V <sub>CCI</sub> | AC12   | I/O                 | C1            | NC                  |  |

| A12           | I/O                 | AB1           | I/O              | AC13   | I/O                 | C2            | TDI, I/O            |  |

| A13           | CLKB                | AB2           | GND              | AC14   | I/O                 | C3            | GND                 |  |

| A14           | I/O                 | AB3           | I/O              | AC15   | NC                  | C4            | I/O                 |  |

| A15           | I/O                 | AB4           | I/O              | AC16   | I/O                 | C5            | I/O                 |  |

| A16           | I/O                 | AB5           | I/O              | AC17   | I/O                 | C6            | I/O                 |  |

| A17           | I/O                 | AB6           | I/O              | AC18   | I/O                 | С7            | I/O                 |  |

| A18           | I/O                 | AB7           | I/O              | AC19   | I/O                 | C8            | I/O                 |  |

| A19           | I/O                 | AB8           | I/O              | AC20   | I/O                 | С9            | I/O                 |  |

| A20           | I/O                 | AB9           | I/O              | AC21   | NC                  | C10           | I/O                 |  |

| A21           | NC                  | AB10          | I/O              | AC22   | V <sub>CCI</sub>    | C11           | I/O                 |  |

| A22           | V <sub>CCI</sub>    | AB11          | PRB, I/O         | AC23   | GND                 | C12           | I/O                 |  |

| A23           | GND                 | AB12          | I/O              | B1     | V <sub>CCI</sub>    | C13           | I/O                 |  |

| AA1           | V <sub>CCI</sub>    | AB13          | HCLK             | B2     | GND                 | C14           | I/O                 |  |

| AA2           | I/O                 | AB14          | I/O              | B3     | I/O                 | C15           | I/O                 |  |

| AA3           | GND                 | AB15          | I/O              | B4     | I/O                 | C16           | I/O                 |  |

| AA4           | I/O                 | AB16          | I/O              | B5     | I/O                 | C17           | I/O                 |  |

| AA5           | I/O                 | AB17          | I/O              | B6     | I/O                 | C18           | I/O                 |  |

| AA6           | I/O                 | AB18          | I/O              | В7     | I/O                 | C19           | I/O                 |  |

| AA7           | I/O                 | AB19          | I/O              | B8     | I/O                 | C20           | I/O                 |  |

| AA8           | I/O                 | AB20          | I/O              | В9     | I/O                 | C21           | V <sub>CCI</sub>    |  |

| AA9           | I/O                 | AB21          | I/O              | B10    | I/O                 | C22           | GND                 |  |

| AA10          | I/O                 | AB22          | GND              | B11    | I/O                 | C23           | NC                  |  |

| AA11          | I/O                 | AB23          | I/O              | B12    | PRA, I/O            | D1            | I/O                 |  |

| AA12          | I/O                 | AC1           | GND              | B13    | CLKA                | D2            | I/O                 |  |

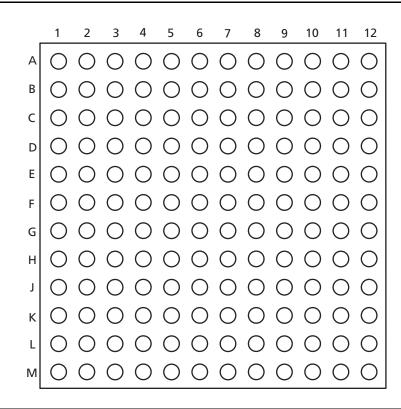

# 144-Pin FBGA

Figure 2-8 • 144-Pin FBGA (Top View)

### Note

For Package Manufacturing and Environmental information, visit the Package Resource center at http://www.actel.com/products/rescenter/package/index.html.

| 144-Pi        | 144-Pin FBGA        |               | 144-Pin FBGA        |               | n FBGA              | 144-Pin FBGA  |                     |  |

|---------------|---------------------|---------------|---------------------|---------------|---------------------|---------------|---------------------|--|

| Pin<br>Number | A54SX08<br>Function | Pin<br>Number | A54SX08<br>Function | Pin<br>Number | A54SX08<br>Function | Pin<br>Number | A54SX08<br>Function |  |

| A1            | I/O                 | D1            | I/O                 | G1            | I/O                 | K1            | I/O                 |  |

| A2            | I/O                 | D2            | V <sub>CCI</sub>    | G2            | GND                 | K2            | I/O                 |  |

| A3            | I/O                 | D3            | TDI, I/O            | G3            | I/O                 | К3            | I/O                 |  |

| A4            | I/O                 | D4            | I/O                 | G4            | I/O                 | К4            | I/O                 |  |

| A5            | V <sub>CCA</sub>    | D5            | I/O                 | G5            | GND                 | K5            | I/O                 |  |

| A6            | GND                 | D6            | I/O                 | G6            | GND                 | К6            | I/O                 |  |

| A7            | CLKA                | D7            | I/O                 | G7            | GND                 | К7            | GND                 |  |

| A8            | I/O                 | D8            | I/O                 | G8            | V <sub>CCI</sub>    | K8            | I/O                 |  |

| A9            | I/O                 | D9            | I/O                 | G9            | I/O                 | К9            | I/O                 |  |

| A10           | I/O                 | D10           | I/O                 | G10           | I/O                 | K10           | GND                 |  |

| A11           | I/O                 | D11           | I/O                 | G11           | I/O                 | K11           | I/O                 |  |

| A12           | I/O                 | D12           | I/O                 | G12           | I/O                 | K12           | I/O                 |  |

| B1            | I/O                 | E1            | I/O                 | H1            | I/O                 | L1            | GND                 |  |

| B2            | GND                 | E2            | I/O                 | H2            | I/O                 | L2            | I/O                 |  |

| B3            | I/O                 | E3            | I/O                 | H3            | I/O                 | L3            | I/O                 |  |

| B4            | I/O                 | E4            | I/O                 | H4            | I/O                 | L4            | I/O                 |  |

| B5            | I/O                 | E5            | TMS                 | H5            | V <sub>CCA</sub>    | L5            | I/O                 |  |

| B6            | I/O                 | E6            | V <sub>CCI</sub>    | H6            | V <sub>CCA</sub>    | L6            | I/O                 |  |

| B7            | CLKB                | E7            | V <sub>CCI</sub>    | H7            | V <sub>CCI</sub>    | L7            | HCLK                |  |

| B8            | I/O                 | E8            | V <sub>CCI</sub>    | H8            | V <sub>CCI</sub>    | L8            | I/O                 |  |

| B9            | I/O                 | E9            | V <sub>CCA</sub>    | H9            | V <sub>CCA</sub>    | L9            | I/O                 |  |

| B10           | I/O                 | E10           | I/O                 | H10           | I/O                 | L10           | I/O                 |  |