Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | IDE/ATAPI, I <sup>2</sup> C, Memory Card, PCM, SPI, UART/USART, USB       |

| Peripherals                | I <sup>2</sup> S, POR, WDT                                                |

| Number of I/O              | 44                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 4K x 8                                                                    |

| RAM Size                   | 2.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.3V                                                               |

| Data Converters            | A/D 2x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-LQFP                                                                   |

| Supplier Device Package    | 80-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5132-rotul |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

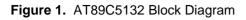

# **Block Diagram**

- Notes: 1. Alternate function of Port 3

- 2. Alternate function of Port 4

- 3. Alternate function of Port 1

# Signals

All the AT89C5132 signals are detailed by functionality in Table 1 to Table 15. **Table 1.** Ports Signal Description

| Signal<br>Name | Туре                                                                    | Description                                                                                                                                                                                                                                                                       | Alternate<br>Function                              |  |  |  |

|----------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| P0.7:0         | I/O                                                                     | Port 0P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1sI/Owritten to them float and can be used as high impedance inputs. To<br>avoid any parasitic current consumption, floating P0 inputs must be<br>polarized to V <sub>DD</sub> or V <sub>SS</sub> . |                                                    |  |  |  |

| P1.7:0         | I/O                                                                     | <b>Port 1</b><br>P1 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                    | KIN3:0<br>SCL<br>SDA                               |  |  |  |

| P2.7:0         | I/O                                                                     | <b>Port 2</b><br>P2 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                    | A15:8                                              |  |  |  |

| P3.7:0         | Port 3<br>P3 is an 8-bit bidirectional I/O port with internal pull-ups. |                                                                                                                                                                                                                                                                                   | RXD<br>TXD<br>INT0<br>INT1<br>T0<br>T1<br>WR<br>RD |  |  |  |

| P4.7:0         | I/O                                                                     | <b>Port 4</b><br>P4 is an 8-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                    | MISO<br>MOSI<br>SCK<br>SS                          |  |  |  |

| P5.3:0         | I/O                                                                     | <b>Port 5</b><br>P5 is a 4-bit bidirectional I/O port with internal pull-ups.                                                                                                                                                                                                     | -                                                  |  |  |  |

#### Table 2. Clock Signal Description

| Signal<br>Name | 5                                                                                                                                                                                                                                                                        |                                                                                       | Alternate<br>Function |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|

| X1             | X1Input to the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to<br>this pin. If an external oscillator is used, its output is connected to this<br>pin. X1 is the clock source for internal timing. |                                                                                       | -                     |

| X2             | 2 O Output of the on-chip inverting oscillator amplifier<br>To use the internal oscillator, a crystal/resonator circuit is connected to<br>this pin. If an external oscillator is used, leave X2 unconnected.                                                            |                                                                                       | -                     |

| FILT           | I                                                                                                                                                                                                                                                                        | PLL Low Pass Filter input<br>FILT receives the RC network of the PLL low pass filter. | -                     |

#### Table 11. A/D Converter Signal Description

| Signal<br>Name | Туре | Description                                                                          | Alternate<br>Function |  |

|----------------|------|--------------------------------------------------------------------------------------|-----------------------|--|

| AIN1:0         | I    | A/D Converter Analog Inputs                                                          | -                     |  |

| AREFP          | I    | Analog Positive Voltage Reference Input                                              | -                     |  |

| AREFN          | I    | Analog Negative Voltage Reference Input<br>This pin is internally connected to AVSS. | -                     |  |

### Table 12. Keypad Interface Signal Description

| Signal<br>Name | Туре | Description                                                                                                                  |        |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------|--------|

| KIN3:0         | I    | <b>Keypad Input Lines</b><br>Holding one of these pins high or low for 24 oscillator periods triggers a<br>keypad interrupt. | P1.3:0 |

Table 13.

External Access Signal Description

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                              | Alternate<br>Function |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A15:8          | I/O  | Address Lines<br>Upper address lines for the external bus.<br>Multiplexed higher address and data lines for the IDE interface.                                                                                                           | P2.7:0                |

| AD7:0          | I/O  | Address/Data Lines<br>Multiplexed lower address and data lines for the external memory or the<br>IDE interface.                                                                                                                          | P0.7:0                |

| ALE            | 0    | Address Latch Enable Output<br>ALE signals the start of an external bus cycle and indicates that valid<br>address information is available on lines A7:0. An external latch is used<br>to demultiplex the address from address/data bus. | -                     |

| ISP            | I/O  | <b>ISP Enable Input</b><br>This signal must be held to GND through a pull-down resistor at the falling reset to force execution of the internal bootloader.                                                                              | -                     |

| RD             | 0    | Read Signal<br>Read signal asserted during external data memory read operation.                                                                                                                                                          | P3.7                  |

| WR             | 0    | Write Signal Write signal asserted during external data memory write operation.                                                                                                                                                          | P3.6                  |

Table 14. System Signal Description

| Signal<br>Name |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Alternate<br>Function |

|----------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| RST            | T | <b>Reset Input</b><br>Holding this pin high for 64 oscillator periods while the oscillator is<br>running resets the device. The Port pins are driven to their reset<br>conditions when a voltage lower than $V_{IL}$ is applied, whether or not the<br>oscillator is running.<br>This pin has an internal pull-down resistor which allows the device to be<br>reset by connecting a capacitor between this pin and $V_{DD}$ .<br>Asserting RST when the chip is in Idle mode or Power-Down mode<br>returns the chip to normal operation. | -                     |

| TST            | Ι | Test Input Test mode entry signal. This pin must be set to $V_{\text{DD}}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                     |

| Table 15.         Power Signal Description | 1 |

|--------------------------------------------|---|

|--------------------------------------------|---|

| Signal<br>Name | Туре | Description                                                                | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------|-----------------------|

| VDD            | PWR  | <b>Digital Supply Voltage</b><br>Connect these pins to +3V supply voltage. | -                     |

| VSS            | GND  | Circuit Ground<br>Connect these pins to ground.                            | -                     |

| AVDD           | PWR  | Analog Supply Voltage<br>Connect this pin to +3V supply voltage.           | -                     |

| AVSS           | GND  | Analog Ground<br>Connect this pin to ground.                               | -                     |

| PVDD           | PWR  | PLL Supply voltage<br>Connect this pin to +3V supply voltage.              | -                     |

| PVSS           | GND  | PLL Circuit Ground<br>Connect this pin to ground.                          | -                     |

| UVDD           | PWR  | USB Supply Voltage<br>Connect this pin to +3V supply voltage.              | -                     |

| UVSS           | GND  | USB Ground<br>Connect this pin to ground.                                  | -                     |

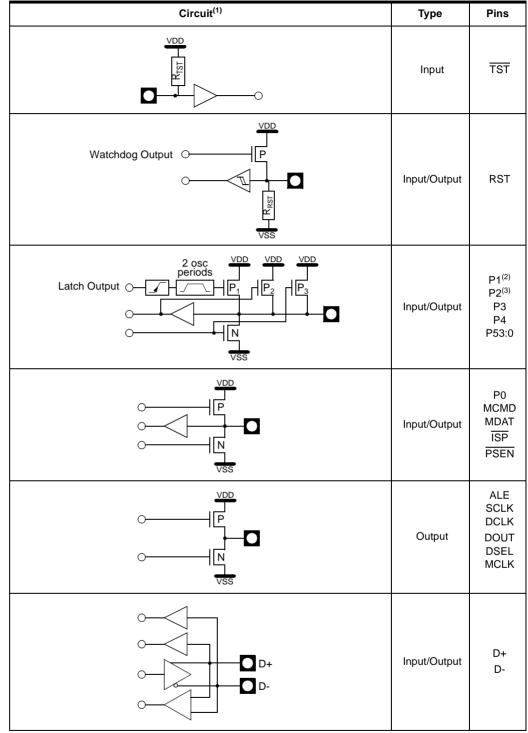

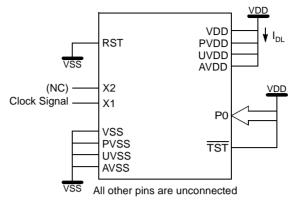

#### **Internal Pin Structure**

Table 16.

Detailed Internal Pin Structure

Notes: 1. For information on resistors value, input/output levels, and drive capability, refer to the Section "DC Characteristics", page 183.

<sup>2.</sup> When the Two Wire controller is enabled, P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub> transistors are disabled allowing pseudo open-drain structure.

<sup>3.</sup> In Port 2, P<sub>1</sub> transistor is continuously driven when outputting a high level bit address (A15:8).

| IIIEL |   |

|-------|---|

|       |   |

| (8    | ) |

## Peripherals

The AT8xC5132 peripherals are briefly described in the following sections. For further details on how to interface (hardware and software) to these peripherals, please refer to the AT8xC5132 complete datasheet.

- **Clock Generator System** The AT8xC5132 internal clocks are extracted from an on-chip PLL fed by an on-chip oscillator. Four clocks are generated respectively for the C51 core, the audio interface, and the other peripherals. The C51 and peripheral clocks are derived from the oscillator clock. The audio interface sample rates are also obtained by dividing the PLL output clock.

- PortsThe AT8xC5132 implement five 8-bit ports (P0 to P4) and one 4-bit port (P5). In addition<br/>to performing general-purpose I/Os, some ports are capable of external data memory<br/>operations; others allow for alternate functions. All I/O Ports are bidirectional. Each Port<br/>contains a latch, an output driver and an input buffer. Port 0 and Port 2 output drivers<br/>and input buffers facilitate external memory operations. Some Port 1, Port 3 and Port 4<br/>pins serve for both general-purpose I/Os and alternate functions.

- **Timers/Counters** The AT8xC5132 implement the two general-purpose, 16-bit Timers/Counters of a standard C51. They are identified as Timer 0, Timer 1, and can independently be configured each to operate in a variety of modes as a Timer or as an event Counter. When operating as a Timer, a Timer/Counter runs for a programmed length of time, then issues an interrupt request. When operating as a Counter, a Timer/Counter counts negative transitions on an external pin. After a preset number of counts, the Counter issues an interrupt request.

- Watchdog TimerThe AT8xC5132 implement a hardware Watchdog Timer that automatically resets the<br/>chip if it is allowed to time out. The WDT provides a means of recovering from routines<br/>that do not complete successfully due to software or hardware malfunctions.

- Audio Output Interface The AT8xC5132 implements an audio output interface allowing the decoded audio bitstream to be output in various formats. They are compatible with right and left justification PCM and I<sub>2</sub>S formats and the on-chip PLL allows connection of almost all commercial audio DAC families available on the market.

Universal Serial BusThe AT8xC5132 implements a full-speed Universal Serial Bus Interface. The USB inter-<br/>face can be used for the following purposes:

- Download of files by supporting the USB mass storage class.

- In-System Programming by supporting the USB firmware upgrade class.

- MultiMedia CardThe AT8xC5132 implements a MultiMedia Card (MMC) interface compliant to the V2.2Interfacespecification in MultiMedia Card mode. The MMC allows storage of files in removable<br/>Flash memory cards that can be easily plugged or removed from the application. It can<br/>also be used for In-System Programming.

- **IDE/ATAPI Interface** The AT8xC5132 provide an IDE/ATAPI interface allowing connection of devices such as CD-ROM reader, CompactFlash™ cards, Hard Disk Drive, etc. It consists of a 16-bit bidirectional bus part of the low-level ANSI ATA/ATAPI specification. It is provided for mass storage interface but could be used for In-System Programming using CD-ROM.

# **Electrical Characteristics**

## Absolute Maximum Ratings

| Storage Temperature                                     | 65°C to +150°C |

|---------------------------------------------------------|----------------|

| Voltage on any other Pin to $V_{\mbox{\scriptsize SS}}$ | -0.3 to +4.0V  |

| I <sub>OL</sub> per I/O Pin                             | 5 mA           |

| Power Dissipation                                       | 1 W            |

| Ambient Temperature Under Bias                          | 40°C to +85°C  |

| V <sub>DD</sub>                                         | 2.7V to 3.3V   |

NOTE: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "operating conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## **DC Characteristics**

#### **Digital Logic**

**Table 1.** Digital DC Characteristics  $V_{DD} = 2.7$  to 3.3V ,  $T_A = -40^{\circ}$  to +85°C

| Symbol           | Parameter                                                                                                 | Min                                | Typ <sup>(1)</sup> | Max                       | Units | Test Conditions           |

|------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|---------------------------|-------|---------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                                                                         | -0.5                               |                    | 0.2·V <sub>DD</sub> - 0.1 | V     |                           |

| V <sub>IH1</sub> | Input High Voltage (except RST, X1)                                                                       | 0.2·V <sub>DD</sub> + 1.1          |                    | V <sub>DD</sub>           | V     |                           |

| $V_{\rm IH2}$    | Input High Voltage (RST, X1)                                                                              | 0.7·V <sub>DD</sub> <sup>(2)</sup> |                    | V <sub>DD</sub> + 0.5     | V     |                           |

| V <sub>OL1</sub> | Output Low Voltage<br>(except P0, ALE, MCMD, MDAT, MCLK,<br>SCLK, DCLK, DSEL, DOUT)                       |                                    |                    | 0.45                      | V     | I <sub>OL</sub> = 1.6 mA  |

| V <sub>OL2</sub> | Output Low Voltage<br>(P0, ALE, MCMD, MDAT, MCLK, SCLK,<br>DCLK, DSEL, DOUT)                              |                                    |                    | 0.45                      | V     | I <sub>OL</sub> = 3.2 mA  |

| V <sub>OH1</sub> | Output High Voltage<br>(P1, P2, P3, P4 and P5)                                                            | V <sub>DD</sub> - 0.7              |                    |                           | V     | I <sub>OH</sub> = -30 μA  |

| V <sub>OH2</sub> | Output High Voltage<br>(P0, P2 address mode, ALE, MCMD,<br>MDAT, MCLK, SCLK, DCLK, DSEL,<br>DOUT, D+, D-) | V <sub>DD</sub> - 0.7              |                    |                           | v     | I <sub>OH</sub> = -3.2 mA |

| I <sub>IL</sub>  | Logical 0 Input Current (P1, P2, P3, P4 and P5)                                                           |                                    |                    | -50                       | μΑ    | Vin = 0.45 V              |

#### Table 1. Digital DC Characteristics $V_{DD} = 2.7 \text{ to } 3.3 \text{V}$ , $T_A = -40^\circ \text{ to } +85^\circ \text{C}$

| Symbol           | Parameter                                                                       | Min | Typ <sup>(1)</sup> | Max                                                 | Units | Test Conditions                                       |

|------------------|---------------------------------------------------------------------------------|-----|--------------------|-----------------------------------------------------|-------|-------------------------------------------------------|

| ILI              | Input Leakage Current (P0, ALE, MCMD,<br>MDAT, MCLK, SCLK, DCLK, DSEL,<br>DOUT) |     |                    | 10                                                  | μA    | 0.45< V <sub>IN</sub> < V <sub>DD</sub>               |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current<br>(P1, P2, P3, P4 and P5)                    |     |                    | -650                                                | μΑ    | Vin = 2.0 V                                           |

| R <sub>RST</sub> | Pull-Down Resistor                                                              | 50  | 90                 | 200                                                 | kΩ    |                                                       |

| CIO              | Pin Capacitance                                                                 |     | 10                 |                                                     | pF    | $T_A = 25^{\circ}C$                                   |

| $V_{RET}$        | V <sub>DD</sub> Data Retention Limit                                            |     |                    | 1.8                                                 | V     |                                                       |

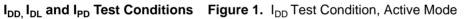

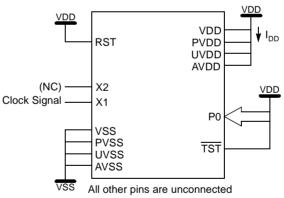

| I <sub>DD</sub>  | Operating Current                                                               |     | (3)                | X1 / X2 mode<br>6.5 / 10.5<br>8 / 13.5<br>9.5 / 17  | mA    | V <sub>DD</sub> < 3.3 V<br>12 MHz<br>16 MHz<br>20 MHz |

| I <sub>DL</sub>  | Idle Mode Current                                                               |     | (3)                | X1 / X2 mode<br>5.3 / 8.1<br>6.4 / 10.3<br>7.5 / 13 | mA    | V <sub>DD</sub> < 3.3 V<br>12 MHz<br>16 MHz<br>20 MHz |

| I <sub>PD</sub>  | Power-Down Mode Current                                                         |     | 20                 | 500                                                 | μA    | V <sub>RET</sub> < V <sub>DD</sub> < 3.3 V            |

Notes: 1. Typical values are obtained using  $V_{DD}$ = 3 V and  $T_A$ = 25°C. They are not tested and there is no guarantee on these values.

2. Flash retention is guaranteed with the same formula for  $V_{DD}$  min down to 0V.

3. See Table 154 for typical consumption in player mode.

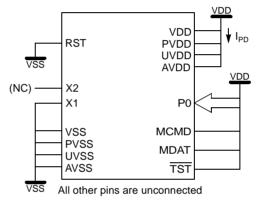

Figure 2.  $I_{DL}$  Test Condition, Idle Mode

Figure 3.  $I_{PD}$  Test Condition, Power-Down Mode

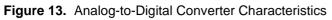

#### A-to-D Converter

# **Table 2.** A-to-D Converter DC Characteristics $V_{DD} = 2.7$ to 3.3V, $T_A = -40^{\circ}$ C to $+85^{\circ}$ C

| Symbol            | Parameter                                                   | Min                     | Тур | Max              | Units  | Test Conditions                               |

|-------------------|-------------------------------------------------------------|-------------------------|-----|------------------|--------|-----------------------------------------------|

| $AV_{DD}$         | Analog Supply Voltage                                       | 2.7                     |     | 3.3              | V      |                                               |

| AI <sub>DD</sub>  | Analog Operating Supply<br>Current                          |                         |     | 600              | μA     | $AV_{DD} = 3.3V$<br>AIN1:0 = 0 to $AV_{DD}$   |

| AI <sub>PD</sub>  | Analog Standby Current                                      |                         |     | 2                | μA     | AV <sub>DD</sub> = 3.3V<br>ADEN = 0 or PD = 1 |

| AV <sub>IN</sub>  | Analog Input Voltage                                        | $AV_{SS}$               |     | $AV_{DD}$        | V      |                                               |

| AV <sub>REF</sub> | Reference Voltage<br>A <sub>REFN</sub><br>A <sub>REFP</sub> | AV <sub>SS</sub><br>2.4 |     | aV <sub>dd</sub> | V<br>V |                                               |

| $R_{REF}$         | AREF Input Resistance                                       | 10                      |     | 30               | kΩ     | $T_A = 25^{\circ}C$                           |

| C <sub>IA</sub>   | Analog Input capacitance                                    |                         |     | 10               | pF     | $T_A = 25^{\circ}C$                           |

#### **Oscillator and Crystal**

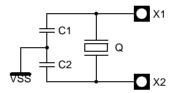

Schematic

Figure 4. Crystal Connection

Note: For operation with most standard crystals, no external components are needed on X1 and X2. It may be necessary to add external capacitors on X1 and X2 to ground in special cases (max 10 pF). X1 and X2 may not be used to drive other circuits.

#### Parameters

## Table 3. Oscillator and Crystal Characteristics V/ 2.7 to 2.2 V/

$V_{DD}$  = 2.7 to 3.3V ,  $T_A$  = -40° to +85°C

| Symbol          | Parameter                                    | Min | Тур | Max | Unit |

|-----------------|----------------------------------------------|-----|-----|-----|------|

| C <sub>X1</sub> | Internal Capacitance (X1 - V <sub>SS</sub> ) |     | 10  |     | pF   |

| C <sub>X2</sub> | Internal Capacitance (X2 - V <sub>SS</sub> ) |     | 10  |     | pF   |

| CL              | Equivalent Load Capacitance (X1 - X2)        |     | 5   |     | pF   |

| DL              | Drive Level                                  |     |     | 50  | μW   |

| F               | Crystal Frequency                            |     |     | 20  | MHz  |

| RS              | Crystal Series Resistance                    |     |     | 40  | Ω    |

| CS              | Crystal Shunt Capacitance                    |     |     | 6   | pF   |

#### Phase Lock Loop

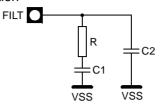

Schematic

#### Figure 5. PLL Filter Connection

#### Parameters

# Table 4. PLL Filter Characteristics $V_{DD}$ = 2.7 to 3.3V , $T_A$ = -40° to +85°C

| Symbol | Parameter            | Min | Тур | Max | Unit |

|--------|----------------------|-----|-----|-----|------|

| R      | Filter Resistor      |     | 100 |     | Ω    |

| C1     | Filter Capacitance 1 |     | 10  |     | nF   |

| C2     | Filter Capacitance 2 |     | 2.2 |     | nF   |

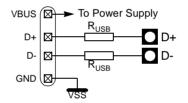

#### **USB** Connection

Schematic

#### Figure 6. USB Connection

#### Parameters

Table 1. USB Termination Characteristics

$V_{DD}$  = 2.7 to 3.3 V,  $T_{A}$  = -40 to +85°C

| Symbol    | Parameter                | Min | Тур | Max | Unit |

|-----------|--------------------------|-----|-----|-----|------|

| $R_{USB}$ | USB Termination Resistor |     | 27  |     | Ω    |

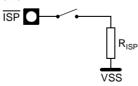

#### **In-system Programming**

#### Schematic

Figure 7. ISP Pull-down Connection

Parameters

Table 5. ISP Pull-Down Characteristics  $V_{DD}$  = 2.7 to 3.3V ,  $T_{A}$  = -40° to +85°C

| Symbol           | Parameter              | Min | Тур | Max | Unit |

|------------------|------------------------|-----|-----|-----|------|

| R <sub>ISP</sub> | ISP Pull-Down Resistor |     | 2.2 |     | kΩ   |

# Table 3. External 8-bit Bus Cycle – Data Write AC Timings $V_{DD}$ = 2.7 to 3.3V, $T_A$ = -40° to +85°C

|                   |                               | Variable<br>Standar     |                       | Variable Clock<br>X2 Mode |                           |      |

|-------------------|-------------------------------|-------------------------|-----------------------|---------------------------|---------------------------|------|

| Symbol            | Parameter                     | Min                     | Max                   | Min                       | Max                       | Unit |

| T <sub>CLCL</sub> | Clock Period                  | 50                      |                       | 50                        |                           | ns   |

| T <sub>LHLL</sub> | ALE Pulse Width               | 2·T <sub>CLCL</sub> -15 |                       | T <sub>CLCL</sub> -15     |                           | ns   |

| T <sub>AVLL</sub> | Address Valid to ALE Low      | T <sub>CLCL</sub> -20   |                       | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |

| T <sub>LLAX</sub> | Address hold after ALE<br>Low | T <sub>CLCL</sub> -20   |                       | 0.5·T <sub>CLCL</sub> -20 |                           | ns   |

| T <sub>LLWL</sub> | ALE Low to WR Low             | 3-T <sub>CLCL</sub> -30 |                       | 1.5·T <sub>CLCL</sub> -30 |                           | ns   |

| T <sub>WLWH</sub> | WR Pulse Width                | 6·T <sub>CLCL</sub> -25 |                       | 3.T <sub>CLCL</sub> -25   |                           | ns   |

| $T_{WHLH}$        | WR High to ALE High           | T <sub>CLCL</sub> -20   | T <sub>CLCL</sub> +20 | 0.5·T <sub>CLCL</sub> -20 | 0.5·T <sub>CLCL</sub> +20 | ns   |

| T <sub>AVWL</sub> | Address Valid to WR Low       | 4.T <sub>CLCL</sub> -30 |                       | 2.T <sub>CLCL</sub> -30   |                           | ns   |

| T <sub>QVWH</sub> | Data Valid to WR High         | 7.T <sub>CLCL</sub> -20 |                       | 3.5·T <sub>CLCL</sub> -20 |                           | ns   |

| T <sub>WHQX</sub> | Data Hold after WR High       | T <sub>CLCL</sub> -15   |                       | 0.5·T <sub>CLCL</sub> -15 |                           | ns   |

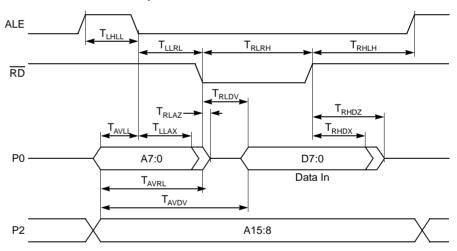

#### Waveforms

#### Figure 1. External 8-bit Bus Cycle - Data Read Waveforms

#### Timings

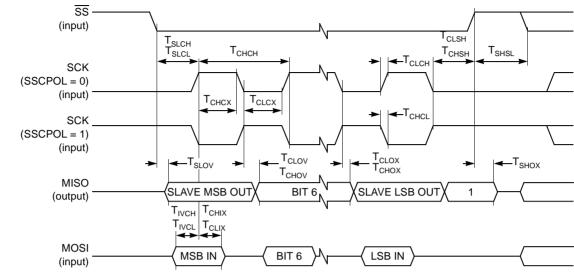

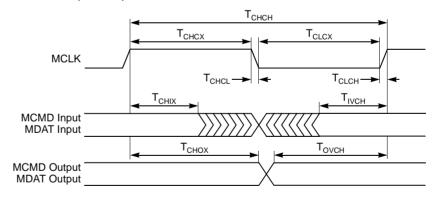

# Table 8. SPI Interface Master AC Timing $V_{DD}$ = 2.7 to 3.3V, $T_A$ = -40° to +85°C

| Symbol                                | Parameter                              | Min | Мах | Unit             |

|---------------------------------------|----------------------------------------|-----|-----|------------------|

|                                       | Slave Mode                             | 1   |     |                  |

| Т <sub>снсн</sub>                     | Clock Period                           | 8   |     | T <sub>osc</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 3.2 |     | T <sub>OSC</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 3.2 |     | T <sub>OSC</sub> |

| T <sub>SLCH</sub> , T <sub>SLCL</sub> | SS Low to Clock edge                   | 200 |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 100 | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>CLSH</sub> , T <sub>CHSH</sub> | SS High after Clock Edge               | 0   |     | ns               |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 100 |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 100 |     | ns               |

| T <sub>SLOV</sub>                     | SS Low to Output Data Valid            |     | 130 | ns               |

| T <sub>SHOX</sub>                     | Output Data Hold after SS High         |     | 130 | ns               |

| T <sub>SHSL</sub>                     | SS High to SS Low                      | (1) |     |                  |

| T <sub>ILIH</sub>                     | Input Rise Time                        |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Fall Time                        |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Rise Time                       |     | 100 | ns               |

| Т <sub>ОНОL</sub>                     | Output Fall Time                       |     | 100 | ns               |

|                                       | Master Mode                            | •   | •   | 1                |

| Т <sub>снсн</sub>                     | Clock Period                           | 4   |     | T <sub>OSC</sub> |

| Т <sub>снсх</sub>                     | Clock High Time                        | 1.6 |     | T <sub>OSC</sub> |

| T <sub>CLCX</sub>                     | Clock Low Time                         | 1.6 |     | T <sub>OSC</sub> |

| T <sub>IVCL</sub> , T <sub>IVCH</sub> | Input Data Valid to Clock Edge         | 50  |     | ns               |

| T <sub>CLIX</sub> , T <sub>CHIX</sub> | Input Data Hold after Clock Edge       | 50  |     | ns               |

| T <sub>CLOV,</sub> T <sub>CHOV</sub>  | Output Data Valid after Clock Edge     |     | 65  | ns               |

| T <sub>CLOX</sub> , T <sub>CHOX</sub> | Output Data Hold Time after Clock Edge | 0   |     | ns               |

| T <sub>ILIH</sub>                     | Input Data Rise Time                   |     | 2   | μs               |

| T <sub>IHIL</sub>                     | Input Data Fall Time                   |     | 2   | μs               |

| Т <sub>оloн</sub>                     | Output Data Rise Time                  |     | 50  | ns               |

| T <sub>OHOL</sub>                     | Output Data Fall Time                  |     | 50  | ns               |

Notes: 1. Value of this parameter depends on software.

2. Test conditions: capacitive load on all pins = 100 pF

#### Waveforms

#### Figure 5. SPI Slave Waveforms (SSCPHA = 0)

#### Figure 6. SPI Slave Waveforms (SSCPHA = 1)

Note: 1. Not Defined but generally the LSB of the character which has just been received.

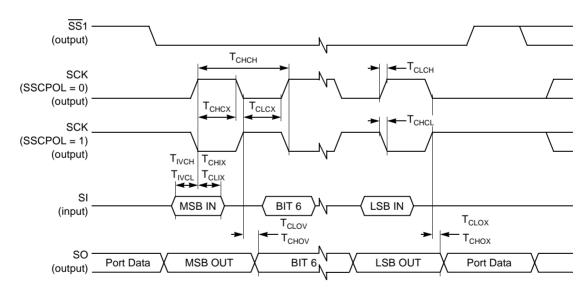

#### **MMC Interface**

#### Definition of Symbols

#### Table 9. MMC Interface Timing Symbol Definitions

| Signals |          |  |  |  |

|---------|----------|--|--|--|

| С       | Clock    |  |  |  |

| D       | Data In  |  |  |  |

| 0       | Data Out |  |  |  |

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| Н          | High            |  |  |  |

| L          | Low             |  |  |  |

| V          | Valid           |  |  |  |

| Х          | No Longer Valid |  |  |  |

#### Timings

#### Table 10. MMC Interface AC Timings

## $V_{DD}$ = 2.7 to 3.3 V, $T_{A}$ = -40 to +85°C, CL $\leq$ 100pF (10 cards)

| Symbol            | Parameter                         | Min | Max | Unit |

|-------------------|-----------------------------------|-----|-----|------|

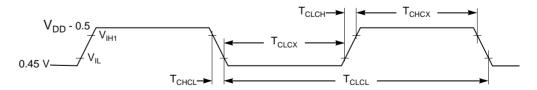

| Т <sub>снсн</sub> | Clock Period                      | 50  |     | ns   |

| T <sub>CHCX</sub> | Clock High Time                   | 10  |     | ns   |

| T <sub>CLCX</sub> | Clock Low Time                    | 10  |     | ns   |

| T <sub>CLCH</sub> | Clock Rise Time                   |     | 10  | ns   |

| T <sub>CHCL</sub> | Clock Fall Time                   |     | 10  | ns   |

| T <sub>DVCH</sub> | Input Data Valid to Clock High    | 3   |     | ns   |

| T <sub>CHDX</sub> | Input Data Hold after Clock High  | 3   |     | ns   |

| T <sub>CHOX</sub> | Output Data Hold after Clock High | 5   |     | ns   |

| T <sub>OVCH</sub> | Output Data Valid to Clock High   | 5   |     | ns   |

#### Waveforms

#### Figure 10. MMC Input Output Waveforms

#### Audio Interface

Definition of Symbols

Table 11.

Audio Interface Timing Symbol Definitions

| Signals |             |  |  |  |

|---------|-------------|--|--|--|

| С       | Clock       |  |  |  |

| 0       | Data Out    |  |  |  |

| S       | Data Select |  |  |  |

| Conditions |                 |  |  |

|------------|-----------------|--|--|

| Н          | High            |  |  |

| L          | Low             |  |  |

| V          | Valid           |  |  |

| х          | No Longer Valid |  |  |

#### Timings

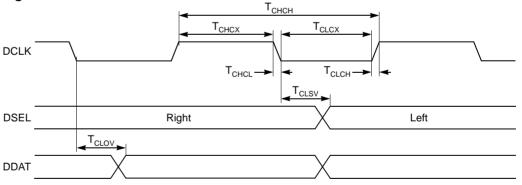

#### Table 12. Audio Interface AC timings

## $V_{DD}$ = 2.7 to 3.3V, $T_A$ = -40 to +85°C, $CL \leq 30 p F$

| Symbol            | Parameter                 | Min | Max                  | Unit |

|-------------------|---------------------------|-----|----------------------|------|

| Тснсн             | Clock Period              |     | 325.5 <sup>(1)</sup> | ns   |

| T <sub>CHCX</sub> | Clock High Time           | 30  |                      | ns   |

| T <sub>CLCX</sub> | Clock Low Time            | 30  |                      | ns   |

| T <sub>CLCH</sub> | Clock Rise Time           |     | 10                   | ns   |

| T <sub>CHCL</sub> | Clock Fall Time           |     | 10                   | ns   |

| T <sub>CLSV</sub> | Clock Low to Select Valid |     | 10                   | ns   |

| T <sub>CLOV</sub> | Clock Low to Data Valid   |     | 10                   | ns   |

Note: 32-bit format with Fs = 48 kHz.

#### Waveforms

#### Figure 11. Audio Interface Waveforms

#### **Flash Memory**

Definition of Symbols

#### Table 14. Flash Memory Timing Symbol Definitions

| Signals |            |  |  |

|---------|------------|--|--|

| s       | ISP        |  |  |

| R       | RST        |  |  |

| В       | FBUSY flag |  |  |

| Conditions |                 |  |  |

|------------|-----------------|--|--|

| L          | Low             |  |  |

| V          | Valid           |  |  |

| х          | No Longer Valid |  |  |

Timings

#### Table 15. Flash Memory AC Timing

$V_{DD}$  = 2.7 to 3.3V,  $T_A$  = -40° to +85°C

| Symbol            | Parameter                              | Min  | Тур | Max | Unit  |

|-------------------|----------------------------------------|------|-----|-----|-------|

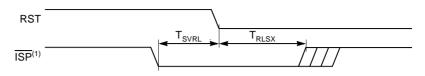

| T <sub>SVRL</sub> | Input ISP Valid to RST Edge            | 50   |     |     | ns    |

| T <sub>RLSX</sub> | Input ISP Hold after RST Edge          | 50   |     |     | ns    |

| T <sub>BHBL</sub> | FLASH Internal Busy (Programming) Time |      | 10  |     | ms    |

| N <sub>FCY</sub>  | Number of Flash Write Cycles           | 100K |     |     | Cycle |

| T <sub>FDR</sub>  | Flash Data Retention Time              | 10   |     |     | Year  |

Figure 14. Flash Memory – ISP Waveforms

Note: 1. ISP must be driven through a pull-down resistor (see Section "In-system Programming", page 22).

#### Figure 15. Flash Memory – Internal Busy Waveforms

#### **External Clock Drive and Logic Level References**

Definition of Symbols

Table 16.

External Clock Timing Symbol Definitions

| Conditions |                 |  |  |  |

|------------|-----------------|--|--|--|

| н          | High            |  |  |  |

| L          | Low             |  |  |  |

| Х          | No Longer Valid |  |  |  |

Timings

#### Table 17. External Clock AC Timings

$V_{DD}$  = 2.7 to 3.3V,  $T_A$ = -40 to +85°C

| Symbol            | Parameter               | Min | Max | Unit |

|-------------------|-------------------------|-----|-----|------|

| T <sub>CLCL</sub> | Clock Period            | 50  |     | ns   |

| T <sub>CHCX</sub> | High Time               | 10  |     | ns   |

| T <sub>CLCX</sub> | Low Time                | 10  |     | ns   |

| T <sub>CLCH</sub> | Rise Time               | 3   |     | ns   |

| T <sub>CHCL</sub> | Fall Time               | 3   |     | ns   |

| T <sub>CR</sub>   | Cyclic Ratio in X2 Mode | 40  | 60  | %    |

#### Waveforms

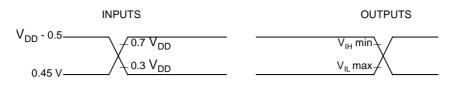

Figure 16. External Clock Waveform

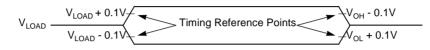

#### Figure 17. AC Testing Input/Output Waveforms

Notes: 1. During AC testing, all inputs are driven at  $V_{DD}$ -0.5V for a logic 1 and 0.45V for a logic 0. 2. Timing measurements are made on all outputs at  $V_{IH}$  min for a logic 1 and  $V_{IL}$  max for a logic 0.

#### Figure 18. Float Waveforms

Note: For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loading  $V_{OH}/V_{OL}$  level occurs with  $I_{OL}/I_{OH} = \pm 20$  mA.

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

#### e-mail

literature@atmel.com

Web Site

http://www.atmel.com

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2004. All rights reserved. Atmel<sup>®</sup> and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.