Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7120bbcz-rl |  |

|----------------------------|---------------------------------------------------------------------|--|

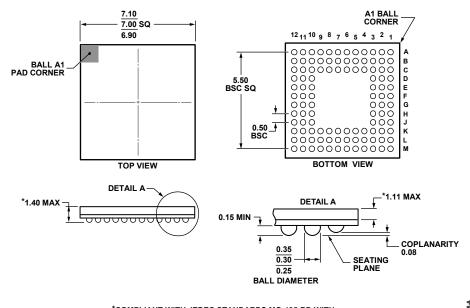

| Supplier Device Package    | 108-CSPBGA (7x7)                                                    |  |

| Package / Case             | 108-LFBGA, CSPBGA                                                   |  |

| Mounting Type              | Surface Mount                                                       |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                  |  |

| Oscillator Type            | Internal                                                            |  |

| Data Converters            | A/D 11x12b; D/A 12x12b                                              |  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |  |

| RAM Size                   | 2K x 32                                                             |  |

| EEPROM Size                | -                                                                   |  |

| Program Memory Type        | FLASH                                                               |  |

| Program Memory Size        | 126KB (63K x 16)                                                    |  |

| Number of I/O              | 32                                                                  |  |

| Peripherals                | POR, PWM, WDT                                                       |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |  |

| Speed                      | 41.78MHz                                                            |  |

| Core Size                  | 16/32-Bit                                                           |  |

| Core Processor             | ARM7®                                                               |  |

| Product Status             | Active                                                              |  |

| Details                    |                                                                     |  |

# **ABSOLUTE MAXIMUM RATINGS**

AGND = 0 V,  $T_A = 25$ °C, unless otherwise noted.

Table 8.

| Parameter                                 | Rating                                       |

|-------------------------------------------|----------------------------------------------|

| AVDD to IOVDD                             | -0.3 V to +0.3 V                             |

| AGND to DGND                              | −0.3 V to +0.3 V                             |

| IOVDD to IOGND, AVDD to AGND              | −0.3 V to +6 V                               |

| Digital Input Voltage to IOGND            | −0.3 V to +5.3 V                             |

| Digital Output Voltage to IOGND           | $-0.3 \text{ V to IOV}_{DD} + 0.3 \text{ V}$ |

| $V_{REF}$ _2.5 and $V_{REF}$ _1.2 to AGND | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$  |

| Analog Inputs to AGND                     | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$  |

| Analog Outputs to AGND                    | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$  |

| Operating Temperature Range, Industrial   | −40°C to +105°C                              |

| Storage Temperature Range                 | −65°C to +150°C                              |

| Junction Temperature                      | 150°C                                        |

| Peak Solder Reflow Temperature            |                                              |

| SnPb Assemblies (10 sec to 30 sec)        | 240°C                                        |

| RoHS-Compliant Assemblies                 | 260°C                                        |

| (20 sec to 40 sec)                        |                                              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environments. Careful attention to PCB thermal design is required.  $\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance

**Table 9. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις | Unit |

|----------------------|-----------------|-----|------|

| CSP_BGA <sup>1</sup> | 40              | 12  | °C/W |

<sup>&</sup>lt;sup>1</sup>Test Condition 1: Thermal impendance simulated values are based on JEDEC 2S2P thermal test board with thermal vias. See JEDEC JESD-51.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

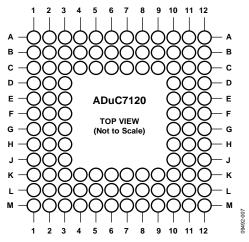

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 7. ADuC7020 Pin Configuration

Table 10. ADuC7120 Pin Function Descriptions

| Pin No. | Mnemonic                 | Type <sup>1</sup> | Description                                                                                       |  |  |

|---------|--------------------------|-------------------|---------------------------------------------------------------------------------------------------|--|--|

| A1      | IDAC1                    | AO                | IDAC1 Output. The output for this pin is 200 mA.                                                  |  |  |

| A2      | PVDD_IDAC1               | S                 | Power for IDAC1.                                                                                  |  |  |

| A3      | PVDD_IDAC1               | S                 | Power for IDAC1.                                                                                  |  |  |

| A4      | IDAC1                    | AO                | IDAC1 Output. The output for this pin is 200 mA.                                                  |  |  |

| A5      | IDAC3                    | AO                | IDAC3 Output. The output for this pin is 80 mA.                                                   |  |  |

| A6      | C <sub>DAMP</sub> _IDAC4 | Al                | Damping Capacitor Pin for IDAC4.                                                                  |  |  |

| A7      | PVDD_IDAC2               | S                 | 2.0 V Power for IDAC2.                                                                            |  |  |

| A8      | IDAC2                    | AO                | IDAC2 Output. The output for this pin is 45 mA.                                                   |  |  |

| A9      | IDAC0                    | AO                | IDAC0 Output. The output for this pin is 250 mA.                                                  |  |  |

| A10     | PVDD_IDAC0               | S                 | Power for IDACO.                                                                                  |  |  |

| A11     | PVDD_IDAC0               | S                 | Power for IDACO.                                                                                  |  |  |

| A12     | IDAC0                    | AO                | IDAC0 Output. The output for this pin is 250 mA.                                                  |  |  |

| B1      | C <sub>DAMP</sub> _IDAC1 | Al                | Damping Capacitor for IDAC1.                                                                      |  |  |

| B2      | P1.7/PLAO[4]             | I/O               | General-Purpose Input and Output (GPIO) Port 1.7 (P1.7).                                          |  |  |

|         |                          |                   | Programmable Logic Array for Output Element 4 (PLAO[4]).                                          |  |  |

| B3      | P1.6/PLAO[5]             | I/O               | General-Purpose Input and Output Port 1.6 (P1.6).                                                 |  |  |

|         |                          |                   | Programmable Logic Array for Output Element 5 (PLAO[5]).                                          |  |  |

| B4      | C <sub>DAMP</sub> _IDAC3 | Al                | Damping Capacitor for IDAC3.                                                                      |  |  |

| B5      | IDAC4                    | AO                | IDAC4 Output. The output for this pin is 20 mA.                                                   |  |  |

| B6      | AGND                     | S                 | Analog Ground.                                                                                    |  |  |

| B7      | AVDD_IDAC                | S                 | Output of 2.5 V LDO Regulator for Internal IDACs. Connect a 470 nF capacitor to AGND to this pin. |  |  |

| B8      | I <sub>REF</sub>         | AI/O              | Generates Reference Current for IDACs. Set by the external resistor, R <sub>EXT</sub> .           |  |  |

| B9      | PGND                     | S                 | Power Ground.                                                                                     |  |  |

| B10     | PGND                     | S                 | Power Ground.                                                                                     |  |  |

| B11     | IDAC_TST                 | AI/O              | IDAC Test Purposes.                                                                               |  |  |

| B12     | C <sub>DAMP</sub> _IDAC0 | Al                | Damping Capacitor Pin for IDAC0.                                                                  |  |  |

| C1      | P2.6/IRQ3/PLAI[15]       | I/O               | General-Purpose Input and Output Port 2.6 (P2.6).                                                 |  |  |

|         |                          |                   | External Interrupt Request 3, Active High (IRQ3).                                                 |  |  |

|         |                          |                   | Programmable Logic Array for Input Element 15 (PLAI[15]).                                         |  |  |

| Pin No.  | Mnemonic                               | Type <sup>1</sup> | Description                                                                                                                                                    |

|----------|----------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E3       | P0.4/MOSI/PLAI[11]/TRIP                | I/O               | General-Purpose Input and Output Port 0.4 (P0.4).                                                                                                              |

|          |                                        |                   | SPI Master Out Slave In (MOSI).                                                                                                                                |

|          |                                        |                   | Programmable Logic Array for Input Element 11 (PLAI[11]).                                                                                                      |

|          |                                        |                   | PWM Trip Interrupt (TRIP). The TRIP function of Pin E3 is the input that allows the PWM trip interrupt to be triggered.                                        |

| E10      | TMS                                    | DI                | JTAG Test Port Input, Test Mode Select. Debug and download access.                                                                                             |

| E11      | P0.1/SDA0/PLAI[4]                      | 1/0               | General-Purpose Input and Output Port 0.1 (P0.1).                                                                                                              |

|          | 1 0.1/35/10/1 2/11[1]                  | 1,70              | I <sup>2</sup> C Interface Serial Data for I <sup>2</sup> C0 (SDA0).                                                                                           |

|          |                                        |                   | Programmable Logic Array for Input Element 4 (PLAI[4]).                                                                                                        |

| E12      | P3.7/BM/PLAO[11]                       | I/O               | General-Purpose Input and Output Port 3.7 (P3.7).                                                                                                              |

|          |                                        | ,, -              | Boot Mode (BM).                                                                                                                                                |

|          |                                        |                   | Programmable Logic Array for Output Element 11 (PLAO[11]).                                                                                                     |

| F1       | DGND                                   | S                 | Digital Ground.                                                                                                                                                |

| F2       | P3.5/PLAO[9]                           | I/O               | General-Purpose Input and Output Port 3.5 (P3.5).                                                                                                              |

|          | 1 5.5/1 [1 (0[5]                       | ., 0              | Programmable Logic Array for Output Element 9 (PLAO[9]).                                                                                                       |

| F3       | P0.5/CS/PLAI[10]/ADC <sub>CONVST</sub> | I/O               | General-Purpose Input and Output Port 0.5 (P0.5).                                                                                                              |

|          |                                        | ,, -              | SPI Slave Select Input (CS).                                                                                                                                   |

|          |                                        |                   | Programmable Logic Array for Input Element 10 (PLAI[10]).                                                                                                      |

|          |                                        |                   | ADC Conversions (ADC <sub>CONVST</sub> ). The ADC <sub>CONVST</sub> function of Pin F3 initiates the ADC                                                       |

|          |                                        |                   | conversions using the PLA or the timer output.                                                                                                                 |

| F10      | TCK                                    | DI                | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                   |

| F11      | P2.0/IRQ0/PLAI[13]                     | I/O               | General-Purpose Input and Output Port 2.0 (P2.0).                                                                                                              |

|          | 1 2.0/11(20/1 [/1[13]                  | 1,0               | External Interrupt Request 0, Active High (IRQ0).                                                                                                              |

|          |                                        |                   | Programmable Logic Array for Input Element 13 (PLAI[13]).                                                                                                      |

| F12      | DGND                                   | S                 | Digital Ground.                                                                                                                                                |

| G1       | DVDD                                   | S                 | Output of 2.6 V On-Chip LDO Regulator. Connect a 470 nF capacitor to DGND to this pin.                                                                         |

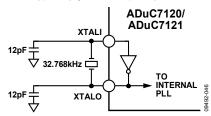

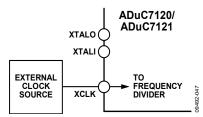

| G2       | XTALO                                  | DO                | Crystal Oscillator Inverter Output. If an external crystal is not used, this pin can remain unconnected.                                                       |

| G3       | P0.6/MRST/PLAI[2]                      | I/O               | General-Purpose Input and Output Port 0.6 (P0.6).                                                                                                              |

|          |                                        |                   | Power On Reset Output (MRST).                                                                                                                                  |

|          |                                        |                   | Programmable Logic Array for Input Element 2 (PLAI[2]).                                                                                                        |

| G10      | P0.7/TRST/PLAI[3]                      | I/O               | General-Purpose Input and Output Port 0.7 (P0.7).                                                                                                              |

|          |                                        |                   | JTAG Test Port Input, Test Reset (TRST). Debug and download access.                                                                                            |

|          |                                        |                   | Programmable Logic Array for Input Element 3 (PLAI[3]).                                                                                                        |

| G11      | P2.1/IRQ1/PLAI[12]                     | 1/0               | General-Purpose Input and Output Port 2.1 (P2.1)                                                                                                               |

| <b>.</b> |                                        | ,, 0              | External Interrupt Request 1, Active High (IRQ1).                                                                                                              |

|          |                                        |                   | Programmable Logic Array for Input Element 12 (PLAI[12]).                                                                                                      |

| G12      | DVDD                                   | S                 | Output of 2.6 V On-Chip LDO Regulator. Connect a 470 nF capacitor to DGND to this pin.                                                                         |

| H1       | IOVDD                                  | S                 | 3.3 V GPIO Supply.                                                                                                                                             |

| H2       | XTALI                                  | DI                | Crystal Oscillator Inverter Input and Internal Clock Generator Circuits Input. If an external crystal is not used, connect this pin to the DGND system ground. |

| H3       | P1.4/PWM1/ECLK/XCLK/PLAI[8]            | I/O               | General-Purpose Input and Output Port 1.4 (P1.4).                                                                                                              |

|          |                                        | ., 0              | Pulse-Width Modulator 1 Output (PWM1).                                                                                                                         |

|          |                                        |                   | Base System Clock Output (ECLK).                                                                                                                               |

|          |                                        |                   | Base System Clock Input (XCLK).                                                                                                                                |

|          |                                        |                   | Programmable Logic Array for Input Element 8 (PLAI[8]).                                                                                                        |

| H10      | P2.4/PWM5/PLAO[7]                      | I/O               | General-Purpose Input and Output Port 2.4 (P2.4).                                                                                                              |

|          |                                        |                   | Pulse-Width Modulator 5 Output (PWM5).                                                                                                                         |

|          |                                        |                   | Programmable Logic Array for Output Element 7 (PLAO[7]).                                                                                                       |

| H11      | P2.2/PLAI[1]                           | I/O               | General-Purpose Input and Output Port 2.2 (P2.2).                                                                                                              |

|          |                                        |                   | Programmable Logic Array for Input Element 1 (PLAI[1]).                                                                                                        |

| H12      | IOVDD                                  | S                 | 3.3 V GPIO Supply.                                                                                                                                             |

# OVERVIEW OF THE ARM7TDMI CORE

The ARM7<sup>™</sup> core is a 32-bit reduced instruction set computer (RISC). It uses a single 32-bit bus for instruction and data. The length of the data can be 8 bits, 16 bits, or 32 bits. The length of the instruction word is 32 bits.

The ARM7TDMI® is an ARM7 core with four additional features, as follows:

- T support for the thumb (16-bit) instruction set

- D support for debug

- M support for long multiplications

- I includes the EmbeddedICE<sup>™</sup> module to support embedded system debugging

# THUMB (T) MODE

An ARM® instruction is 32 bits long. The ARM7TDMI processor supports a second instruction set that has been compressed into 16 bits, the Thumb® instruction set. Faster execution from 16-bit memory and greater code density can usually be achieved by using the Thumb instruction set instead of the ARM instruction set, which makes the ARM7TDMI core suitable for embedded applications.

However, the Thumb mode has the following two limitations:

- Thumb code typically requires more instructions for the same job. As a result, ARM code is usually best for maximizing the performance of time critical code.

- The Thumb instruction set does not include some of the instructions needed for exception handling, which automatically switches the core to ARM code for exception handling.

See the ADuC7XXX Microconverter<sup>™</sup> Get Started Guide for details on the core architecture, the programming model, and both the ARM and ARM Thumb instruction sets.

### **LONG MULTIPLY (M)**

The ARM7TDMI instruction set includes four extra instructions that perform 32-bit by 32-bit multiplication with a 64-bit result, and 32-bit by 32-bit multiplication accumulation (MAC) with a 64-bit result. These results are achieved in fewer cycles than required on a standard ARM7 core.

### **EmbeddedICE (I)**

EmbeddedICE provides integrated on-chip support for the core. The EmbeddedICE module contains the breakpoint and watchpoint registers that halts code for debugging purposes. These registers are controlled through the JTAG test port.

When a breakpoint or watchpoint is encountered, the processor halts and enters a debug state. When in a debug state, the breakpoint and watchpoint registers can be inspected, as well as the Flash/EE, static random access memory (SRAM), and memory mapped registers.

#### **EXCEPTIONS**

ARM supports five types of exceptions and a privileged processing mode for each type. The five exception types include the following:

- Normal interrupt (IRQ) can service general-purpose interrupt handling of internal and external events.

- Fast interrupt (FIQ) can service data transfers or communication channels with low latency.; FIQ has priority over IRQ.

- Memory abort.

- Attempted execution of an undefined instruction.

- Software interrupt instruction (SWI) can make a call to an operating system.

Typically, the programmer defines interrupt as IRQ, but for higher priority interrupt, that is, faster response time, the programmer can define interrupt as FIQ.

| Address | Name     | Byte | Access Type | Cycle |

|---------|----------|------|-------------|-------|

| 0x0940  | I2C1ID1  | 1    | R/W         | 2     |

| 0x0944  | I2C1ID2  | 1    | R/W         | 2     |

| 0x0948  | I2C1ID3  | 1    | R/W         | 2     |

| 0x094C  | I2C1FSTA | 1    | R/W         | 2     |

### Table 24. SPI Base Address = 0xFFFF0A00

| Address | Name   | Byte | Access Type | Cycle |

|---------|--------|------|-------------|-------|

| 0x0A00  | SPISTA | 2    | R           | 2     |

| 0x0A04  | SPIRX  | 1    | R           | 2     |

| 80A0x0  | SPITX  | 1    | W           | 2     |

| 0x0A0C  | SPIDIV | 1    | R/W         | 2     |

| 0x0A10  | SPICON | 2    | R/W         | 2     |

**Table 25. PLA Base Address = 0xFFFF0B00**

| Tubic 20.1 Eri Buoc Hudicoo Oni III oboo |                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name                                     | Byte                                                                                                                                                                                | Access Type                                                                                                                                                                                                                                                                          | Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| PLAELM0                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM1                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM2                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM3                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM4                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM5                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM6                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM7                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM8                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM9                                  | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM10                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM11                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM12                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM13                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM14                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLAELM15                                 | 2                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PLACLK                                   | 1                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |