Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | ARM7®                                                            |

| Core Size                  | 16/32-Bit                                                        |

| Speed                      | 41.78MHz                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                               |

| Program Memory Size        | 126KB (63K x 16)                                                 |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | ·                                                                |

| RAM Size                   | 2K x 32                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                        |

| Data Converters            | A/D 11x12b; D/A 12x12b                                           |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 108-LFBGA, CSPBGA                                                |

| Supplier Device Package    | 108-CSPBGA (7x7)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7120bbcz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **SPECIFICATIONS**

AVDD = IOVDD = 3.0 V to 3.6 V, PVDD\_IDACx = 1.5 V to 2.1 V, reference voltage ( $V_{REF}$ ) = 2.5 V internal reference, core frequency ( $f_{CORE}$ ) = 41.78 MHz, ambient temperature ( $T_A$ ) = -40°C to +105°C, unless otherwise noted.

| Parameter                                 | Min  | Тур               | Max                      | Unit    | Test Conditions/Comments                                                                                                         |

|-------------------------------------------|------|-------------------|--------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| ADC CHANNEL SPECIFICATIONS                |      | •76               |                          |         | Eight acquisition clocks and                                                                                                     |

|                                           |      |                   |                          |         | ADC frequency (f <sub>ADC</sub> )/2                                                                                              |

| ADC Power-Up Time                         |      | 5                 |                          | μs      |                                                                                                                                  |

| DC Accuracy <sup>1, 2</sup>               |      |                   |                          |         |                                                                                                                                  |

| Resolution                                | 12   |                   |                          | Bits    |                                                                                                                                  |

| Integral Nonlinearity                     |      | ±0.6              | ±2.2                     | LSB     |                                                                                                                                  |

|                                           |      | ±0.6              | ±2                       | LSB     | –10°C to +95°C temperature range only                                                                                            |

|                                           |      |                   |                          |         | 2.5 V internal reference, not production tested for PADC0x and PADC1x channels                                                   |

| Differential Nonlinearity <sup>3, 4</sup> |      | ±0.5              | +1.4/-0.99               | LSB     | 2.5 V internal reference, guaranteed monotonic                                                                                   |

| DC Code Distribution                      |      | 1                 |                          | LSB     | ADC input is a dc voltage                                                                                                        |

| ENDPOINT ERRORS <sup>5</sup>              |      |                   |                          |         | Internally unbuffered channels                                                                                                   |

| Offset Error                              |      |                   |                          |         | ,                                                                                                                                |

| All Channels Except IDACx<br>Channels     |      | ±2                | ±5                       | LSB     |                                                                                                                                  |

| IDACx Channels Only                       |      | 1                 |                          | % of FS |                                                                                                                                  |

| Offset Error Match                        |      | ±1                |                          | LSB     |                                                                                                                                  |

| Gain Error                                |      | ±1<br>±2          | ±5.3                     | LSB     |                                                                                                                                  |

| Gain Endi                                 |      | ±2<br>±2          | ±5.5                     | LSB     | $-10^{\circ}$ C to $+95^{\circ}$ C temperature range only                                                                        |

| Gain Error Match                          |      | ±2<br>±1          | ±5                       | LSB     |                                                                                                                                  |

| DYNAMIC PERFORMANCE                       |      | ±1                |                          | LJD     | Input frequency $(f_{IN}) = 10$ kHz sine wave,                                                                                   |

| DINAMIC PERFORMANCE                       |      |                   |                          |         | sample frequency (IN) = 10 KH2 sine wave,<br>sample frequency (f <sub>SAMPLE</sub> ) = 1 MSPS,<br>internally unbuffered channels |

| Signal-to-Noise Ratio (SNR)               |      | 69                |                          | dB      | Includes distortion and noise components                                                                                         |

| Total Harmonic Distortion (THD)           |      | -78               |                          | dB      |                                                                                                                                  |

| Peak Harmonic or Spurious Noise           |      | -75               |                          | dB      |                                                                                                                                  |

| Channel to Channel Crosstalk              |      | -80               |                          | dB      | Measured on adjacent channels                                                                                                    |

| ANALOG INPUT                              |      | 00                |                          |         |                                                                                                                                  |

| Input Voltage Ranges                      |      |                   |                          |         |                                                                                                                                  |

| Differential Mode                         |      |                   | $V_{CM}^6 \pm V_{REF}/2$ | v       | See Table 42                                                                                                                     |

| Single-Ended Mode                         |      |                   |                          | v       | Buffer bypassed                                                                                                                  |

| Single Ended Mode                         | 0.15 |                   | AV <sub>DD</sub> – 1.5   | v       | Buffer enabled                                                                                                                   |

| Leakage Current                           | 0.15 | ±0.2              | ±1                       | μA      | build chabled                                                                                                                    |

| Input Capacitance                         |      | <u>+0.2</u><br>20 | ±1                       | pF      | During ADC acquisition buffer bypassed                                                                                           |

| input capacitance                         |      | 20                |                          | pr      | During ADC acquisition buffer enabled                                                                                            |

| PADC0x INPUT                              |      | 20                |                          |         | 28.3 k $\Omega$ resistor, PGA gain = 3, acquisition<br>time = 3.2 $\mu$ s, pseudo differential mode                              |

| Full-Scale Input Range                    | 20   |                   | 1000                     | μA      | time – 5.2 μs, pseudo differential filode                                                                                        |

| Input Leakage at PADC0x <sup>4</sup>      | 20   | 0.15              | 2                        | nA      |                                                                                                                                  |

| Resolution                                | 11   | 0.15              | 2                        | Bits    | 0.1% accuracy, 5 ppm external resistor for                                                                                       |

|                                           |      |                   |                          |         | current to voltage                                                                                                               |

| Gain Error <sup>₄</sup>                   |      |                   | 1                        | %       |                                                                                                                                  |

| Gain Drift⁴                               |      |                   | 50                       | ppm/°C  |                                                                                                                                  |

| Offset <sup>₄</sup>                       |      | 3                 | 6                        | nA      | PGA offset not included                                                                                                          |

| Offset Drift⁴                             |      | 30                | 60                       | pA/°C   |                                                                                                                                  |

| PADC0x Compliant Range                    | 0.1  |                   | AV <sub>DD</sub> – 1.2   | V       |                                                                                                                                  |

| Pin No. | Mnemonic                                  | Type <sup>1</sup> | Description                                                                             |

|---------|-------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|

| C3      | P0.2/SPICLK/ADC <sub>BUSY</sub> /PLAO[13] | I/O               | General-Purpose Input and Output Port 0.2 (P0.2).                                       |

|         |                                           |                   | SPI Clock (SPICLK).                                                                     |

|         |                                           |                   | Status of the ADC (ADC <sub>BUSY</sub> ).                                               |

|         |                                           |                   | Programmable Logic Array for Output Element 13 (PLAO[13]).                              |

| C4      | P3.0/PLAO[0]                              | I/O               | General-Purpose Input and Output Port 3.0 (P3.0).                                       |

| C7      |                                           | 1/0               | Programmable Logic Array for Output Element 0 (PLAO[0]).                                |

| C5      | PVDD_IDAC3                                | c                 | 2.0 V Power for the IDAC3.                                                              |

|         | _                                         | S                 | 2.0 V Power for IDAC4.                                                                  |

| C6      | PVDD_IDAC4                                | S                 |                                                                                         |

| C7      | AVDD                                      | S                 | Analog Supply (3.3 V).                                                                  |

| C8      | CDAMP_IDAC2                               | AI                | Damping Capacitor Pin for IDAC2.                                                        |

| C9      | P2.7/PLAI[0]                              | I/O               | General-Purpose Input and Output Port 2.7 (P2.7).                                       |

|         |                                           |                   | Programmable Logic Array for Input Element 0 (PLAI[0]).                                 |

| C10     | P1.2/TDI/PLAO[15]                         | DI                | General-Purpose Input and Output Port 1.2 (P1.2).                                       |

|         |                                           |                   | JTAG Test Port Input, Test Data In (TDI). The TDI function of Pin C10 is for debug and  |

|         |                                           |                   | download access.                                                                        |

|         |                                           |                   | Programmable Logic Array for Output Element 15 (PLAO[15]).                              |

| C11     | P3.1/PLAO[1]                              | I/O               | General-Purpose Input and Output Port 3.1 (P3.1).                                       |

|         |                                           |                   | Programmable Logic Array for Output Element 1 (PLAO[1]).                                |

| C12     | RST                                       | I                 | Reset Input (Active Low).                                                               |

| D1      | P3.2/IRQ4/PWM3/PLAO[2]                    | I/O               | General-Purpose Input and Output Port 3.2 (P3.2).                                       |

|         |                                           |                   | External Interrupt Request 4, Active High (IRQ4).                                       |

|         |                                           |                   | Pulse-Width Modulator 3 Output (PWM3).                                                  |

|         |                                           |                   | Programmable Logic Array for Output Element 2 (PLAO[2]).                                |

| D2      | P1.1/SOUT/SDA1/PLAI[6]                    | I/O               | General-Purpose Input and Output Port 1.1 (P1.1).                                       |

|         |                                           |                   | Serial Output, Transmit Data, UART (SOUT).                                              |

|         |                                           |                   | l <sup>2</sup> C Interface Serial Data for l <sup>2</sup> C1 (SDA1).                    |

|         |                                           |                   | Programmable Logic Array for Input Element 6 (PLAI[6]).                                 |

| D3      | P0.3/MISO/PLAO[12]/SYNC                   | I/O               | General-Purpose Input and Output Port 0.3 (P0.3).                                       |

| 05      | 10.5/11/00/12/05/10                       | 1, 0              | SPI Master In Slave Out (MISO).                                                         |

|         |                                           |                   | Programmable Logic Array for Output Element 12 (PLAO[12]).                              |

|         |                                           |                   | Synchronous Reset (SYNC). Input to reset synchronously the PWM counters using an        |

|         |                                           |                   | external source.                                                                        |

| D10     | P1.3/TDO/PLAO[14]                         | DO                | General-Purpose Input and Output Port 1.3 (P1.3).                                       |

| DIO     |                                           | 00                | JTAG Test Port Output, Test Data Out (TDO). The TDO function of Pin D10 is for debug    |

|         |                                           |                   | and download access.                                                                    |

|         |                                           |                   | Programmable Logic Array for Output Element 14 (PLAO[14]).                              |

| D11     | P0.0/SCL0/PLAI[5]                         | I/O               | General-Purpose Input and Output Port 0.0 (P0.0).                                       |

|         |                                           | 1/0               | l <sup>2</sup> C Interface Serial Clock for l <sup>2</sup> C0 (SCL0).                   |

|         |                                           |                   | Programmable Logic Array for Input Element 5 (PLAI[5]).                                 |

| D12     |                                           | I/O               | General-Purpose Input and Output Port 3.6 (P3.6).                                       |

| DIZ     | P3.6/PLAO[10]                             | 1/0               |                                                                                         |

| F1      |                                           | 1/0               | Programmable Logic Array for Output Element 10 (PLAO[10]).                              |

| E1      | P3.3/IRQ5/PWM4/PLAO[3]                    | I/O               | General-Purpose Input and Output Port 3.3 (P3.3).                                       |

|         |                                           |                   | External Interrupt Request 5, Active High (IRQ5).                                       |

|         |                                           |                   | Pulse-Width Modulator 4 Output (PWM4).                                                  |

|         |                                           |                   | Programmable Logic Array for Output Element 3 (PLAO[3]).                                |

| E2      | P3.4/PLAO[8]                              | I/O               | General-Purpose Input and Output Port 3.4 (P3.4).                                       |

|         |                                           |                   | Programmable Logic Array for Output Element 8 (PLAO[8]).                                |

| E3      | P0.4/MOSI/PLAI[11]/TRIP                   | I/O               | General-Purpose Input and Output Port 0.4 (P0.4).                                       |

|         |                                           |                   | SPI Master Out Slave In (MOSI).                                                         |

|         |                                           |                   | Programmable Logic Array for Input Element 11 (PLAI[11]).                               |

|         |                                           |                   | PWM Trip Interrupt (TRIP). The TRIP function of Pin E3 is the input that allows the PWM |

|         |                                           |                   | trip interrupt to be triggered.                                                         |

| E10     | тмѕ                                       | DI                | JTAG Test Port Input, Test Mode Select. Debug and download access.                      |

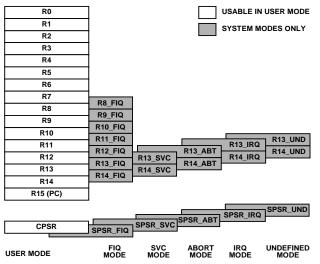

#### **ARM REGISTERS**

ARM7TDMI has a total of 37 registers: 31 general-purpose registers and 6 status registers. Each operating mode has dedicated banked registers.

When writing user level programs, 15 general-purpose 32-bit registers (R0 to R14), the program counter (R15), and the current program status register (CPSR) are usable. The remaining registers are used for system level programming and exception handling only.

When an exception occurs, some of the standard registers are replaced with registers specific to the exception mode. All exception modes have replacement banked registers for the stack pointer (R13) and the link register (R14) as represented in Figure 9. The fast interrupt mode has more registers (R8 to R12) for fast interrupt processing, which means that interrupt processing can begin without the need to save or restore these registers, thus saving critical time in the interrupt handling process.

Figure 9. Register Organization

More information relative to the model of the programmer and the ARM7TDMI core architecture can be found in the following materials from ARM, Ltd.:

- ARM DDI 0029G, ARM7TDMI Technical Reference Manual

- ARM DDI 0100, ARM Architecture Reference Manual

#### **INTERRUPT LATENCY**

The worst case latency for a FIQ consists of the following:

- The longest time the request can take to pass through the synchronizer.

- The time for the longest instruction to complete (the longest instruction is a load multiple (LDM)) that loads all the registers including the PC.

- The time for the data abort entry.

- The time for FIQ entry.

At the end of this time, the ARM7TDMI executes the instruction at 0x1C (FIQ interrupt vector address). The maximum total time is 50 processor cycles, which is just under 1.2 µs in a system using a continuous 41.78 MHz processor clock.

The maximum IRQ latency calculation is similar but must allow the fact that FIQ has higher priority and can delay entry into the IRQ handling routine for an arbitrary length of time. This time can be reduced to 42 cycles if the LDM command is not used. Some compilers have an option to compile without using this command. Another option is to run the devices in thumb mode wherein the time is reduced to 22 cycles.

The minimum latency for FIQ or IRQ interrupts is five cycles, which consist of the shortest time the request can take through the synchronizer plus the time to enter the exception mode.

The ARM7TDMI always runs in ARM (32-bit) mode when in privileged modes, for example, when executing interrupt service routines.

9492-008

| 0xFFFFFFFF |                              | 1 |

|------------|------------------------------|---|

| 0xFFFF0FBC |                              |   |

| 0xFFFF0F80 | PWM                          |   |

| 0xFFFF0EA8 |                              |   |

| 0xFFFF0E80 | FLASH CONTROL<br>INTERFACE 1 |   |

|            |                              |   |

| 0xFFFF0E28 | FLASH CONTROL<br>INTERFACE 0 |   |

| 0xFFFF0E00 |                              |   |

| 0xFFFF0D78 | GPIO                         |   |

| 0xFFFF0D00 | GFIO                         |   |

| 0xFFFF0B54 |                              |   |

| 0xFFFF0B00 | PLA                          |   |

| 0xFFFF0A14 |                              |   |

| 0xFFFF0A00 | SPI                          |   |

|            |                              |   |

| 0xFFFF0950 | I <sup>2</sup> C1            |   |

| 0xFFFF0900 |                              |   |

| 0xFFFF08D0 | 2C0                          |   |

| 0xFFFF0880 | 1-00                         |   |

| 0xFFFF082C |                              |   |

| 0xFFFF0800 | UART0                        |   |

|            |                              | } |

|            |                              |   |

|            |                              |   |

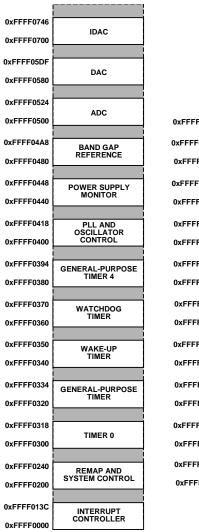

Figure 12. Memory Mapped Registers

#### **COMPLETE MMR LISTING**

The Access Type column corresponds to the access time reading or writing an MMR, where R is read, W is write, and R/W is read/ write. It depends on the AMBA bus that accesses the peripheral. The processor has two AMBA buses: AHB used for system modules, and APB used for lower performance peripherals. **Table 12. IRO Base Address = 0xFFFF0000**

| Table 12. IRQ Base Address = 0xFFFF0000 |         |      |             |       |  |  |

|-----------------------------------------|---------|------|-------------|-------|--|--|

| Address                                 | Name    | Byte | Access Type | Cycle |  |  |

| 0x0000                                  | IRQSTA  | 4    | R           | 1     |  |  |

| 0x0004                                  | IRQSIG  | 4    | R           | 1     |  |  |

| 0x0008                                  | IRQEN   | 4    | R/W         | 1     |  |  |

| 0x000C                                  | IRQCLR  | 4    | W           | 1     |  |  |

| 0x0010                                  | SWICFG  | 4    | W           | 1     |  |  |

| 0x0014                                  | IRQBASE | 4    | R/W         | 1     |  |  |

| 0x001C                                  | IRQVEC  | 4    | R/W         | 1     |  |  |

| 0x0020                                  | IRQP0   | 4    | R/W         | 1     |  |  |

| 0x0024                                  | IRQP1   | 4    | R/W         | 1     |  |  |

| 0x0028                                  | IRQP2   | 4    | R/W         | 1     |  |  |

| 0x002C                                  | IRQP3   | 4    | R/W         | 1     |  |  |

| 0x0030                                  | IRQCONN | 1    | R/W         | 1     |  |  |

| 0x0034                                  | IRQCONE | 4    | R/W         | 1     |  |  |

| Address | Name    | Byte | Access Type | Cycle |

|---------|---------|------|-------------|-------|

| 0x0038  | IRQCLRE | 1    | W           | 1     |

| 0x003C  | IRQSTAN | 1    | R/W         | 1     |

| 0x0100  | FIQSTA  | 4    | R           | 1     |

| 0x0104  | FIQSIG  | 4    | R           | 1     |

| 0x0108  | FIQEN   | 4    | R/W         | 1     |

| 0x010C  | FIQCLR  | 4    | W           | 1     |

| 0x011C  | FIQVEC  | 4    | R           | 1     |

| 0x013C  | FIQSTAN | 1    | R/W         | 1     |

Table 13. Remap and System Control Base Address = 0xFFFF0200

| Address | Name              | Byte | Access Type | Cycle |

|---------|-------------------|------|-------------|-------|

| 0x0220  | REMAP             | 1    | R/W         | 1     |

| 0x0230  | RSTSTA            | 1    | R           | 1     |

| 0x0234  | RSTCLR            | 1    | W           | 1     |

| 0x0248  | <b>RSTCFGKEY0</b> | 1    | W           | 1     |

| 0x024C  | RSTCFG            | 1    | R/W         | 1     |

| 0x0250  | RSTCFGKEY1        | 1    | W           | 1     |

#### Table 14. Timer Base Address = 0xFFFF0300

| Table 14. Timer Base Address = 0xFFFF0300 |        |      |                   |       |  |  |

|-------------------------------------------|--------|------|-------------------|-------|--|--|

| Address                                   | Name   | Byte | Access Type       | Cycle |  |  |

| 0x0300                                    | TOLD   | 2    | R/W               | 2     |  |  |

| 0x0304                                    | T0VAL0 | 2    | R                 | 2     |  |  |

| 0x0308                                    | T0VAL1 | 4    | R                 | 2     |  |  |

| 0x030C                                    | T0CON  | 4    | R/W               | 2     |  |  |

| 0x0310                                    | TOCLRI | 1    | W                 | 2     |  |  |

| 0x0314                                    | TOCAP  | 2    | R                 | 2     |  |  |

| 0x0320                                    | T1LD   | 4    | R/W               | 2     |  |  |

| 0x0324                                    | T1VAL  | 4    | R                 | 2     |  |  |

| 0x0328                                    | T1CON  | 4    | R/W               | 2     |  |  |

| 0x032C                                    | T1CLRI | 1    | W                 | 2     |  |  |

| 0x0330                                    | T1CAP  | 4    | R                 | 2     |  |  |

| 0x0340                                    | T2LD   | 4    | R/W               | 2     |  |  |

| 0x0344                                    | T2VAL  | 4    | R                 | 2     |  |  |

| 0x0348                                    | T2CON  | 4    | R/W               | 2     |  |  |

| 0x034C                                    | T2CLRI | 1    | W                 | 2     |  |  |

| 0x0360                                    | T3LD   | 2    | R/W               | 2     |  |  |

| 0x0364                                    | T3VAL  | 2    | R                 | 2     |  |  |

| 0x0368                                    | T3CON  | 2    | R/W one time only | 2     |  |  |

| 0x036C                                    | T3CLRI | 1    | W                 | 2     |  |  |

| 0x0380                                    | T4LD   | 4    | R/W               | 2     |  |  |

| 0x0384                                    | T4VAL  | 4    | R                 | 2     |  |  |

| 0x0388                                    | T4CON  | 4    | R/W               | 2     |  |  |

| 0x038C                                    | T4CLRI | 1    | W                 | 2     |  |  |

| 0x0390                                    | T4CAP  | 4    | R                 | 2     |  |  |

# Table 15. PLL and Oscillator Control Base Address = 0xFFFF0400

| Address | Name    | Byte | Access Type | Cycle |

|---------|---------|------|-------------|-------|

| 0x0404  | POWKEY1 | 2    | W           | 2     |

| 0x0408  | POWCON  | 1    | R/W         | 2     |

| 0x040C  | POWKEY2 | 2    | W           | 2     |

| 0x0410  | PLLKEY1 | 2    | W           | 2     |

| 0x0414  | PLLCON  | 1    | R/W         | 2     |

| 0x0418  | PLLKEY2 | 2    | W           | 2     |

### **Data Sheet**

## ADuC7120/ADuC7121

#### Table 16. PSM Base Address = 0xFFFF0440

| Address | Name   | Byte | Access Type | Cycle |  |  |

|---------|--------|------|-------------|-------|--|--|

| 0x0440  | PSMCON | 2    | R/W         | 2     |  |  |

|         |        |      |             |       |  |  |

| Table 17. Band Gap Reference Base Address = 0xFFFF0480 |        |      |             |       |  |

|--------------------------------------------------------|--------|------|-------------|-------|--|

| Address                                                | Name   | Byte | Access Type | Cycle |  |

| 0x0480                                                 | REFCON | 1    | R/W         | 2     |  |

#### Table 18. ADC Base Address = 0xFFFF0500

| Address | Name   | Byte | Access Type | Cycle |

|---------|--------|------|-------------|-------|

| 0x0500  | ADCCON | 4    | R/W         | 2     |

| 0x0504  | ADCCP  | 1    | R/W         | 2     |

| 0x0508  | ADCCN  | 1    | R/W         | 2     |

| 0x050C  | ADCSTA | 1    | R           | 2     |

| 0x0510  | ADCDAT | 4    | R           | 2     |

| 0x0514  | ADCRST | 1    | W           | 2     |

| 0x0518  | ADCGN  | 2    | R/W         | 2     |

| 0x051C  | ADCOF  | 2    | R/W         | 2     |

| 0x0520  | PGA_GN | 2    | R/W         | 2     |

#### Table 19. DAC Base Address = 0xFFFF0580

| Address | Name    | Byte | Access Type | Cycle |

|---------|---------|------|-------------|-------|

| 0x0580  | DAC0CON | 2    | R/W         | 2     |

| 0x0584  | DAC0DAT | 4    | R/W         | 2     |

| 0x0588  | DAC1CON | 2    | R/W         | 2     |

| 0x058C  | DAC1DAT | 4    | R/W         | 2     |

| 0x05B0  | DAC2CON | 2    | R/W         | 2     |

| 0x05B4  | DAC2DAT | 4    | R/W         | 2     |

| 0x05D8  | DAC3CON | 2    | R/W         | 2     |

| 0x05DC  | DAC3DAT | 4    | R/W         | 2     |

#### Table 20. IDAC Base Address = 0xFFFF0700

| Table 20. IDAC base Address = 0xFFFF0700 |               |      |             |       |  |  |

|------------------------------------------|---------------|------|-------------|-------|--|--|

| Address                                  | Name          | Byte | Access Type | Cycle |  |  |

| 0x0700                                   | IDAC0CON      | 2    | R/W         | 2     |  |  |

| 0x0704                                   | IDAC0DAT      | 4    | R/W         | 2     |  |  |

| 0x0708                                   | IDAC0BW       | 1    | R/W         | 2     |  |  |

| 0x070C                                   | IDAC1CON      | 2    | R/W         | 2     |  |  |

| 0x0710                                   | IDAC1DAT      | 4    | R/W         | 2     |  |  |

| 0x0714                                   | IDAC1BW       | 1    | R/W         | 2     |  |  |

| 0x0718                                   | IDAC2CON      | 2    | R/W         | 2     |  |  |

| 0x071C                                   | IDAC2DAT      | 4    | R/W         | 2     |  |  |

| 0x0720                                   | IDAC2BW       | 1    | R/W         | 2     |  |  |

| 0x0724                                   | IDAC3CON      | 2    | R/W         | 2     |  |  |

| 0x0728                                   | IDAC3DAT      | 4    | R/W         | 2     |  |  |

| 0x072C                                   | IDAC3BW       | 1    | R/W         | 2     |  |  |

| 0x0730                                   | IDAC4CON      | 2    | R/W         | 2     |  |  |

| 0x0734                                   | IDAC4DAT      | 4    | R/W         | 2     |  |  |

| 0x0738                                   | IDAC4BW       | 1    | R/W         | 2     |  |  |

| 0x073C                                   | TSDCON        | 1    | R/W         | 2     |  |  |

| 0x0740                                   | IDACSTA       | 1    | R/W         | 2     |  |  |

| 0x0744                                   | IDACOPULLDOWN | 1    | R/W         | 2     |  |  |

| Address | Name    | Byte | Access Type | Cycle |

|---------|---------|------|-------------|-------|

| 0x0800  | COMTX   | 1    | W           | 2     |

|         | COMRX   | 1    | R           | 2     |

|         | COMDIV0 | 1    | R/W         | 2     |

| 0x0804  | COMIEN0 | 1    | R/W         | 2     |

|         | COMDIV1 | 1    | R/W         | 2     |

| 0x0808  | COMIID0 | 1    | R           | 2     |

| 0x080C  | COMCON0 | 1    | R/W         | 2     |

| 0x0810  | COMCON1 | 1    | R/W         | 2     |

| 0x0814  | COMSTA0 | 1    | R           | 2     |

| 0X082C  | COMDIV2 | 2    | R/W         | 2     |

### Table 21. UARTO Base Address = 0xFFFF0800

#### Table 22. I<sup>2</sup>C0 Base Address = 0xFFFF0880

| Address | Name      | Byte | Access Type | Cycle |

|---------|-----------|------|-------------|-------|

| 0x0880  | I2C0MCTL  | 2    | R/W         | 2     |

| 0x0884  | I2C0MSTA  | 2    | R           | 2     |

| 0x0888  | I2C0MRX   | 1    | R           | 2     |

| 0x088C  | I2C0MTX   | 2    | W           | 2     |

| 0x0890  | I2C0MCNT0 | 2    | R/W         | 2     |

| 0x0894  | I2C0MCNT1 | 1    | R           | 2     |

| 0x0898  | I2C0ADR0  | 1    | R/W         | 2     |

| 0x089C  | I2C0ADR1  | 1    | R/W         | 2     |

| 0x08A0  | I2C0SBYTE | 1    | R/W         | 2     |

| 0x08A4  | I2C0DIV   | 2    | R/W         | 2     |

| 0x08A8  | I2C0SCTL  | 2    | R/W         | 2     |

| 0x08AC  | I2C0SSTA  | 2    | R           | 2     |

| 0x08B0  | I2C0SRX   | 1    | R           | 2     |

| 0x08B4  | I2C0STX   | 1    | W           | 2     |

| 0x08B8  | I2C0ALT   | 1    | R/W         | 2     |

| 0x08BC  | 12C0ID0   | 1    | R/W         | 2     |

| 0x08C0  | I2C0ID1   | 1    | R/W         | 2     |

| 0x08C4  | 12C0ID2   | 1    | R/W         | 2     |

| 0x08C8  | 12C0ID3   | 1    | R/W         | 2     |

| 0x08CC  | I2C0FSTA  | 1    | R/W         | 2     |

#### Table 23. I<sup>2</sup>C1 Base Address = 0xFFFF0900

| Address | Name      | Byte | Access Type | Cycle |

|---------|-----------|------|-------------|-------|

| 0x0900  | I2C1MCTL  | 2    | R/W         | 2     |

| 0x0904  | I2C1MSTA  | 2    | R           | 2     |

| 0x0908  | I2C1MRX   | 1    | R           | 2     |

| 0x090C  | I2C1MTX   | 2    | W           | 2     |

| 0x0910  | I2C1MCNT0 | 2    | R/W         | 2     |

| 0x0914  | I2C1MCNT1 | 1    | R           | 2     |

| 0x0918  | I2C1ADR0  | 1    | R/W         | 2     |

| 0x091C  | I2C1ADR1  | 1    | R/W         | 2     |

| 0x0920  | I2C1SBYTE | 1    | R/W         | 2     |

| 0x0924  | I2C1DIV   | 2    | R/W         | 2     |

| 0x0928  | I2C1SCTL  | 2    | R/W         | 2     |

| 0x092C  | I2C1SSTA  | 2    | R           | 2     |

| 0x0930  | I2C1SRX   | 1    | R           | 2     |

| 0x0934  | I2C1STX   | 1    | W           | 2     |

| 0x0938  | I2C1ALT   | 1    | R/W         | 2     |

| 0x093C  | I2C1ID0   | 1    | R/W         | 2     |

| Table . | 52. ADuC/ | 120 ADCCP <sup>2</sup> MMR Bit Designations |

|---------|-----------|---------------------------------------------|

| Bit(s)  | Setting   | Description                                 |

| [7:5]   | Reserved  | Reserved                                    |

| [4:0]   |           | Positive channel selection bits             |

|         | 00000     | PADC0P                                      |

|         | 00001     | PADC1P                                      |

|         | 00010     | ADC0                                        |

|         | 00011     | ADC1                                        |

|         | 00100     | ADC2                                        |

|         | 00101     | ADC3                                        |

|         | 00110     | ADC4                                        |

|         | 00111     | ADC5                                        |

|         | 01000     | ADC6                                        |

|         | 01001     | ADC7                                        |

|         | 01010     | ADC8                                        |

|         | 01011     | ADC9                                        |

|         | 01100     | ADC10/AINCM                                 |

|         | 01101     | Temperature sensor                          |

|         | 01110     | DVDD_IDAC0                                  |

|         | 01111     | DVDD_IDAC1                                  |

|         | 10000     | DVDD_IDAC2                                  |

|         | 10001     | DVDD_IDAC3                                  |

|         | 10010     | DVDD_IDAC4                                  |

|         | 10011     | IOVDD_MON                                   |

|         | 10100     | PVDD_IDAC0                                  |

|         | 10101     | PVDD_IDAC1                                  |

|         | 10110     | V <sub>REF</sub>                            |

|         | 10111     | AGND                                        |

|         | Others    | Reserved                                    |

#### Table 32. ADuC7120 ADCCP<sup>1</sup> MMR Bit Designations

10110 V<sub>REF</sub> 10111 AGND Others Reserved

Description

Reserved

Reserved

<sup>1</sup> ADC channel availability depends on device model.

Bit(s)

Setting

10100

10101

#### Table 34. ADuC7120 ADCCN<sup>1</sup> MMR Bit Designations

| Tuble 51, The uc, T20 The Cort Mining the Designation |                                                                |                                 |  |  |

|-------------------------------------------------------|----------------------------------------------------------------|---------------------------------|--|--|

| Bit(s)                                                | Setting                                                        | Description                     |  |  |

| [7:5]                                                 | Reserved                                                       | Reserved                        |  |  |

| [4:0]                                                 |                                                                | Negative channel selection bits |  |  |

|                                                       | 00000                                                          | PADCON                          |  |  |

|                                                       | 00001                                                          | PADC1N                          |  |  |

|                                                       | 00010                                                          | ADC0                            |  |  |

|                                                       | 00011                                                          | ADC1                            |  |  |

|                                                       | 00100                                                          | ADC2                            |  |  |

|                                                       | 00101                                                          | ADC3                            |  |  |

|                                                       | 00110                                                          | ADC4                            |  |  |

|                                                       | 00111                                                          | ADC5                            |  |  |

|                                                       | 01000                                                          | ADC6                            |  |  |

|                                                       | 01001                                                          | ADC7                            |  |  |

|                                                       | 01010                                                          | ADC8                            |  |  |

|                                                       | 01011                                                          | ADC9                            |  |  |

|                                                       | 01100                                                          | ADC10/AINCM                     |  |  |

|                                                       | 01101                                                          | VREF                            |  |  |

|                                                       | 01110                                                          | AGND                            |  |  |

|                                                       | 01111                                                          | PGND                            |  |  |

|                                                       | 10000                                                          | IOGND                           |  |  |

|                                                       | Others                                                         | Reserved                        |  |  |

| <sup>1</sup> ADC ch                                   | <sup>1</sup> ADC channel availability depends on device model. |                                 |  |  |

<sup>1</sup> ADC channel availability depends on device model.

#### Table 33. ADuC7121 ADCCP<sup>1</sup> MMR Bit Designations

| Bit(s) | Setting  | Description                     | Table 35. ADuC7121 ADCCN <sup>1</sup> MMR Bit Designations |                 |                                 |

|--------|----------|---------------------------------|------------------------------------------------------------|-----------------|---------------------------------|

| [7:5]  | Reserved | Reserved                        | Bit(s)                                                     | Setting         | Description                     |

| [4:0]  |          | Positive channel selection bits | [7:5]                                                      | Reserved        | Reserved                        |

|        | 00000    | PADC0P                          | [4:0]                                                      |                 | Negative channel selection bits |

|        | 00001    | PADC1P                          |                                                            | 00000           | PADCON                          |

|        | 00010    | Reserved                        |                                                            | 00001           | PADC1N                          |

|        | 00011    | Reserved                        |                                                            | 00010           | Reserved                        |

|        | 00100    | Reserved                        |                                                            | 00011           | Reserved                        |

|        | 00101    | Reserved                        |                                                            | 00100           | Reserved                        |

|        | 00110    | ADC4                            |                                                            | 00101           | Reserved                        |

|        | 00111    | ADC5                            |                                                            | 00110           | ADC4                            |

|        | 01000    | ADC6                            |                                                            | 00111           | ADC5                            |

|        | 01001    | ADC7                            |                                                            | 01000           | ADC6                            |

|        | 01010    | ADC8                            |                                                            | 01001           | ADC7                            |

|        | 01011    | ADC9                            |                                                            | 01010           | ADC8                            |

|        | 01100    | ADC10/AINCM                     |                                                            | 01011           | ADC9                            |

|        | 01101    | Temperature sensor              |                                                            | 01100           | ADC10/AINCM                     |

|        | 01110    | DVDD_IDAC0                      |                                                            | 01101           | V <sub>REF</sub>                |

|        | 01111    | DVDD_IDAC1                      |                                                            | 01110           | AGND                            |

|        | 10000    | DVDD_IDAC2                      |                                                            | 01111           | PGND                            |

|        | 10001    | DVDD_IDAC3                      |                                                            | 10000           | IOGND                           |

|        | 10010    | DVDD_IDAC4                      |                                                            | Others          | Reserved                        |

|        | 10011    | IOVDD_MON                       | <sup>1</sup> ADC cl                                        | nannel availabi | lity depends on device model.   |

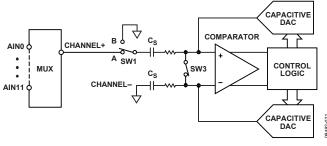

#### Single-Ended Mode

In single-ended mode, SW2 is always connected internally to ground. The  $V_{\rm IN^-}$  input pin can be floating. The input signal range on  $V_{\rm IN^+}$  is 0 V to  $V_{\rm REF}.$

Figure 23. ADC in Single-Ended Mode

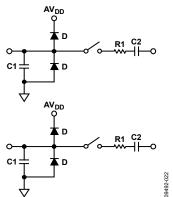

#### Analog Input Structure

Figure 24 shows the equivalent circuit of the analog input structure of the ADC. The four diodes provide ESD protection for the analog inputs. Ensure that the analog input signals never exceed the supply rails by more than 300 mV. Voltage in excess of 300 mV causes these diodes to become forward biased and start conducting into the substrate. These diodes can conduct up to 10 mA without causing irreversible damage to the device.

The C1 capacitors in Figure 24 are typically 4 pF and can be primarily attributed to pin capacitance. The resistors are lumped components made up of the on resistance of the switches. The value of these resistors is typically about 100  $\Omega$ . The C2 capacitors are the ADC sampling capacitors and have a capacitance of 16 pF typical.

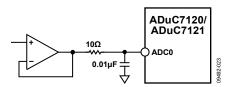

Figure 24. Equivalent Analog Input Circuit Conversion Phase: Switches Open, Track Phase: Switches Closed

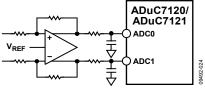

For ac applications, removing high frequency components from the analog input signal is recommended with a resistor capacitor (RC) low-pass filter on the relevant analog input pins. In applications where harmonic distortion and SNR are critical, drive the analog input from a low impedance source. Large source impedances significantly affect the ac performance of the ADC and can necessitate the use of an input buffer amplifier. The choice of the op amp is a function of the particular application. Figure 25 and Figure 26 give an example of an ADC front end.

Figure 25. Buffering Single-Ended/Pseudo Differential Input

Figure 26. Buffering Differential Inputs

When no amplifier drives the analog input, limit the source impedance to values lower than 1 k $\Omega$ . The maximum source impedance depends on the amount of THD that can be tolerated. The THD increases as the source impedance increases and the performance degrades.

#### **DRIVING THE ANALOG INPUTS**

An internal or external reference can be used for the ADC. In differential mode of operation, there are restrictions on the  $V_{\rm CM}$ . These restrictions are dependent on the reference value and supply voltage used to ensure the signal remains within the supply rails. Table 42 lists calculated  $V_{\rm CM}$  minimum and  $V_{\rm CM}$  maximum values.

|          |                      |       | <b>V</b> см (V) |                         |  |

|----------|----------------------|-------|-----------------|-------------------------|--|

| AVDD (V) | V <sub>REF</sub> (V) | Min   | Max             | Signal Peak-to-Peak (V) |  |

| 3.3      | 2.5                  | 1.25  | 2.05            | 2.5                     |  |

|          | 2.048                | 1.024 | 2.276           | 2.048                   |  |

|          | 1.25                 | 0.75  | 2.55            | 1.25                    |  |

| 3.0      | 2.5                  | 1.25  | 1.75            | 2.5                     |  |

|          | 2.048                | 1.024 | 1.976           | 2.048                   |  |

|          | 1.25                 | 0.75  | 2.25            | 1.25                    |  |

#### **POWER SUPPLY MONITOR (PSM)**

The PSM on the ADuC7120/ADuC7121 indicates when the IOVDD supply pin drops below one of two supply trip points. The monitor function is controlled via the PSMCON register. If enabled in the IRQEN or FIQEN register, the monitor interrupts the core using the PSMI bit in the PSMCON MMR. This bit clears immediately after the CMP bit goes high. If the interrupt generated is exited before CMP goes high (IOVDD supply voltage is above the trip point), no further interrupts are generated until CMP returns high. The user must ensure that the code execution remains within the interrupt service routine (ISR) until CMP returns high.

This monitor function allows the user to save working registers to avoid possible data loss due to low supply or brownout conditions. It also ensures that normal code execution does not resume until a safe supply level is established.

The PSM does not operate correctly when using JTAG debug; therefore, disable PSM while in JTAG debug mode.

| Bit(s) | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:4] | Reserved | These bits are reserved.                                                                                                                                                                                                                                                                                                                                                                                            |

| 3      | CMP      | Comparator bit. This is a read only bit that directly reflects the state of the comparator.                                                                                                                                                                                                                                                                                                                         |

|        |          | Read 1 indicates that the IOVDD supply is above its selected trip point or the PSM is in power-down mode.                                                                                                                                                                                                                                                                                                           |

|        |          | Read 0 indicates the IOVDD supply is below its selected trip point. Set this bit before leaving the interrupt service routine.                                                                                                                                                                                                                                                                                      |

| 2      | ТР       | Trip point selection bit.                                                                                                                                                                                                                                                                                                                                                                                           |

|        |          | 0 = 2.79 V.                                                                                                                                                                                                                                                                                                                                                                                                         |

|        |          | 1 = 3.07 V.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1      | PSMEN    | Power supply monitor enable bit.                                                                                                                                                                                                                                                                                                                                                                                    |

|        |          | Set to 1 to enable the power supply monitor circuit.                                                                                                                                                                                                                                                                                                                                                                |

|        |          | Cleared to 0 to disable the power supply monitor circuit.                                                                                                                                                                                                                                                                                                                                                           |

| 0      | PSMI     | Power supply monitor interrupt bit. This bit is set high by the MicroConverter if the CMP bit is low, indicating low input/output supply. The PSMI bit can interrupt the processor. When the CMP bit returns high, the PSMI bit can be cleared by writing a 1 to this location. Writing a 0 to this location has no effect. There is no timeout delay. PSMI can be cleared immediately after the CMP bit goes high. |

### NONVOLATILE FLASH/EE MEMORY Flash/ee memory overview

The ADuC7120/ADuC7121 incorporate Flash/EE memory technology on chip to provide the user with nonvolatile, in circuit reprogrammable memory space.

Similar to EEPROM, flash memory can be programmed in system at a byte level, although it must first be erased. The erase is performed in page blocks. As a result, flash memory is often (and more correctly) referred to as Flash/EE memory.

Overall, Flash/EE memory represents the ideal memory device that includes no volatility, in circuit programmability, high density, and low cost. Incorporated in the ADuC7120/ ADuC7121, Flash/EE memory technology allows the user to update program code space in circuit, without the need to replace one time programmable (OTP) devices at remote operating nodes.

The ADuC7120/ADuC7121 contain two 64 kB arrays of Flash/EE memory. In Flash Block 0, the lower 62 kB is available to the user, and the upper 2 kB of this Flash/EE memory array program contain permanently embedded firmware, allowing in circuit serial download. The 2 kB of embedded firmware also contain a power-on configuration routine that downloads factory calibrated coefficients to the various calibrated peripherals (band gap references and so forth). This 2 kB embedded firmware is hidden from the user code. It is not possible for the user to read, write, or erase this page.

In Flash Block 1, all 64 kB of Flash/EE memory are available to the user.

The 128 kB of Flash/EE memory can be programmed in circuit using serial download mode or JTAG mode.

#### Flash/EE Memory Reliability

The Flash/EE memory arrays on the ADuC7120/ADuC7121 are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to cycle through many program, read, and erase cycles. A single endurance cycle is composed of four independent, sequential events, defined as follows:

- 1. Initial page erase sequence

- 2. Read and verify sequence a single Flash/EE

- 3. Byte program sequence memory

- 4. Second read and verify sequence endurance cycle

In reliability qualification, every half word (16-bit wide) location of the three pages (top, middle, and bottom) in the Flash/EE memory is cycled 10,000 times from 0x0000 to 0xFFFF.

As indicated in the Specifications section, the Flash/EE memory endurance qualification is carried out in accordance with JEDEC Retention Lifetime Specification, Method A117 over the industrial temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C. The results allow the specification of a minimum endurance figure over a supply temperature of 10,000 cycles.

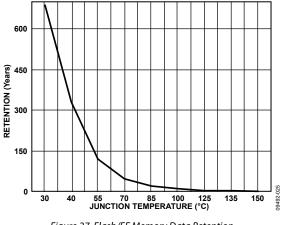

Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. The devices are qualified in accordance with the formal JEDEC Retention Lifetime Specification, Method A117 at a specific junction temperature  $(T_1 = 85^{\circ}C)$ . As part of this qualification procedure, the Flash/EE memory is cycled to the specified endurance limit, previously described, before data retention is characterized. The Flash/EE memory is guaranteed to retain its data for its fully specified retention lifetime every time the Flash/EE memory is reprogrammed. Retention lifetime, based on activation energy of 0.6 eV, derates with  $T_1$ , as shown in Figure 27.

Figure 27. Flash/EE Memory Data Retention

#### Serial Downloading (In Circuit Programming)

The ADuC7120/ADuC7121 facilitate code download via the I<sup>2</sup>C serial port. If the BM function of the P3.7/BM/PLAO[11] pin is pulled low through an external 1 k $\Omega$  resistor, the ADuC7120/ADuC7121 enter serial download mode after a reset or power cycle. In the Flash, if Address 0x0014 is 0xFFFFFFF and BM is pulled low, the devices enter download mode; if this address contains any other value, user code is executed. When in serial download mode, the user can download code to the full 128 kB of Flash/EE memory while the devices are in circuit in their target application hardware. A PC serial download executable and hardware dongle are provided as part of the development system for serial downloads via the I<sup>2</sup>C port. The I<sup>2</sup>C maximum allowed baud rate is 100 kHz for the I<sup>2</sup>C downloader.

#### JTAG Access

The JTAG protocol uses the on-chip JTAG interface to facilitate code download and debug.

#### FLASH/EE MEMORY SECURITY

The 126 kB of Flash/EE memory available to the user can be read and write protected. Bit 31 of the FEE0PRO and FEE0HID MMRs protects it from read through by JTAG and I<sup>2</sup>C programming mode. The other 31 bits of this register protect writing to the Flash/EE memory; each bit protects four pages, that is, 2 kB. Write protection is activated for all access types. FEE1PRO and FEE1HID protect Flash Block 1. Bit 31 of the FEE1PRO and FEE1HID MMRs protects the 64 kB of Block 1 from being read through JTAG. Bit 30 protects writing to the top 8 pages of Block 1. The other 30 bits of this register protect writing to the Flash/EE memory; each bit protects four pages, that is, 2 kB.

#### **Three Levels of Protection**

Protection can be set and removed by writing directly into the FEExHID MMRs. This protection does not remain after reset.

Protection can be set by writing into the FEExPRO MMRs. It takes effect only after a save protection command (0x0C) and a reset. The FEExPRO MMRs are protected by a key to avoid direct access. The key is saved one time only and must be reentered to modify the FEExPRO. A mass erase sets the key back to 0xFFFF but also erases all user code.

The Flash/EE memory can be permanently protected by using the FEExPRO MMRs and a particular value of the 0xDEADDEAD key. Entering the key again to modify the FEExPRO register is not allowed.

#### Sequence to Write the Key to Protection Registers

- 1. Write the bit in the FEExPRO corresponding to the page to be protected.

- 2. Enable key protection by setting Bit 6 of FEExMOD (Bit 5 must equal 0).

- 3. Write a 32-bit key in FEExADR and FEExDAT.

- 4. Run the write key command 0x0C in FEExCON; wait for the read to be successful by monitoring FEExSTA.

- 5. Reset the device.

To remove or modify the protection, the same sequence is used with a modified value of FEExPRO. If the key chosen is the value 0xDEAD, the memory protection cannot be removed. Only a mass erase unprotects the device, but it also erases all user code.

The sequence to write the key is shown in the following example; this protects writing Page 4 to Page 7 of the Flash/EE memory:

| <pre>FEE0PRO=0xFFFFFFFF;</pre> | //Protect Page 4 to Page 7 $$ |

|--------------------------------|-------------------------------|

| FEE0MOD=0x48;                  | //Write key enable            |

| FEE0ADR=0x1234;                | //16-bit key value            |

| FEE0DAT=0x5678;                | //16-bit key value            |

| FEE0CON= 0x0C;                 | //Write key command           |

Follow the same sequence to permanently protect the devices with FEExADR = 0xDEAD and FEExDAT = 0xDEAD.

### FLASH/EE CONTROL INTERFACE

#### **FEE0DAT Register**

FEE0DAT is a 16-bit data register.

| Name:          | <b>FEE0DAT</b> |

|----------------|----------------|

| Address:       | 0xFFFF0E0C     |

| Default value: | 0xXXXX         |

|                |                |

Access: Read and write

#### FEE0ADR Register

FEE0ADR is a 16-bit address register.

| Name:          | FEE0ADR        |

|----------------|----------------|

| Address:       | 0xFFFF0E10     |

| Default value: | 0x0000         |

| Access:        | Read and write |

#### FEE0SGN Register

FEE0SGN is a 24-bit code signature.

| Name:          | <b>FEE0SGN</b> |

|----------------|----------------|

| Address:       | 0xFFFF0E18     |

| Default value: | 0xFFFFFF       |

| Access:        | Read only      |

#### FEE0PRO Register

FEE0PRO provides protection following subsequent reset MMR. It requires a software key (see Table 45).

| Name:          | <b>FEE0PRO</b> |

|----------------|----------------|

| Address:       | 0xFFFF0E1C     |

| Default value: | 0x00000000     |

| Access:        | Read and write |

#### FEE0HID Register

FEE0HID provides immediate protection MMR. It does not require any software keys (see Table 45).

| Name:          | FEE0HID        |

|----------------|----------------|

| Address:       | 0xFFFF0E20     |

| Default value: | 0xFFFFFFFF     |

| Access:        | Read and write |

### Data Sheet

## ADuC7120/ADuC7121

| Bit(s)          | Descrip                                                                                                               | tion                                                                                       | Table 48. FEExMOD MMR Bit Designations |                                                                                                                                                              |                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 1               | Comma                                                                                                                 | nd fail.                                                                                   | Bit(s)                                 | Descripti                                                                                                                                                    | on                                                                                    |

|                 | Set automatically when a command completes<br>unsuccessfully.<br>Cleared automatically when reading FEExSTA register. |                                                                                            | [7:5]                                  | Reserved. These bits are always set to 0 except wh<br>writing keys. See the Sequence to Write the Key to<br>Protection Registers section for details.        |                                                                                       |

| 0               |                                                                                                                       | ind complete.                                                                              | 4                                      |                                                                                                                                                              | nterrupt enable.                                                                      |

| 0               | Set by N                                                                                                              | AicroConverter when a command is complete.<br>automatically when reading FEExSTA register. |                                        | Set by the user to enable the Flash/EE interrupt. The<br>interrupt occurs when a command is complete.<br>Cleared by the user to disable the Flash/EE interru |                                                                                       |

| FEEON           | 10D Reg                                                                                                               | ister                                                                                      | 3                                      |                                                                                                                                                              | te command protection.                                                                |

| Name:<br>Addres | -                                                                                                                     | FEE0MOD<br>0xFFFF0E04                                                                      |                                        | Set by the<br>Cleared to                                                                                                                                     | user to enable the erase and write commands.<br>protect the Flash/EE memory against   |

| Addres          | 55:                                                                                                                   | 0XFFFF0E04                                                                                 | 2                                      |                                                                                                                                                              | te command.<br>The user must set this bit to 0.                                       |

| Default         | t value:                                                                                                              | 0x80                                                                                       | [1:0]                                  |                                                                                                                                                              | a the user must set this bit to 0.<br>wait states. Both Flash/EE blocks must have the |

| Access          | :                                                                                                                     | Read and write                                                                             | [1:0]                                  |                                                                                                                                                              | t state value for any change to take effect.                                          |

|                 |                                                                                                                       | •                                                                                          | FEE0C                                  | ON Regist                                                                                                                                                    | ter                                                                                   |

| FEE1N           | 1OD Reg                                                                                                               | ister                                                                                      | Name:                                  |                                                                                                                                                              | FEE0CON                                                                               |

| Name:           |                                                                                                                       | FEE1MOD                                                                                    | 4 1 1                                  |                                                                                                                                                              | 0. 55550500                                                                           |

| Addres          | s.                                                                                                                    | 0xFFFF0E84                                                                                 | Addres                                 | s:                                                                                                                                                           | 0xFFFF0E08                                                                            |