Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18856-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                  | Function               | Input Type             | Output Type | Description                                                          |

|---------------------------------------------------------------------------------------|------------------------|------------------------|-------------|----------------------------------------------------------------------|

| RB2/ANB2/SDA2 <sup>(3,4)</sup> /SDI2 <sup>(1)</sup> /                                 | RB2                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CWG3IN <sup>(1)</sup> /IOCB2                                                          | ANB2                   | AN                     | _           | ADC Channel B2 input.                                                |

|                                                                                       | SDA2 <sup>(3,4)</sup>  | I <sup>2</sup> C/SMBus | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                     |

|                                                                                       | SDI2 <sup>(1)</sup>    | TTL/ST                 | _           | MSSP2 SPI serial data input.                                         |

|                                                                                       | CWG3IN <sup>(1)</sup>  | TTL/ST                 | _           | Complementary Waveform Generator 3 input.                            |

|                                                                                       | IOCB2                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB3/ANB3/C1IN2-/C2IN2-/IOCB3                                                          | RB3                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                       | ANB3                   | AN                     | _           | ADC Channel B3 input.                                                |

|                                                                                       | C1IN2-                 | AN                     | -           | Comparator negative input.                                           |

|                                                                                       | C2IN2-                 | AN                     | -           | Comparator negative input.                                           |

|                                                                                       | IOCB3                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB4/ANB4/ADCACT <sup>(1)</sup> /T5G <sup>(1)</sup> /<br>SMTWIN2 <sup>(1)</sup> /IOCB4 | RB4                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| SMTWINZ\''/IOCB4                                                                      | ANB4                   | AN                     |             | ADC Channel B4 input.                                                |

|                                                                                       | ADCACT <sup>(1)</sup>  | TTL/ST                 | _           | ADC Auto-Conversion Trigger input.                                   |

|                                                                                       | T5G <sup>(1)</sup>     | TTL/ST                 | _           | Timer5 gate input.                                                   |

|                                                                                       | SMTWIN2 <sup>(1)</sup> | TTL/ST                 | _           | Signal Measurement Timer2 (SMT2) window input.                       |

|                                                                                       | IOCB4                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB5/ANB5/T1G <sup>(1)</sup> /SMTSIG2 <sup>(1)</sup> /<br>CCP3 <sup>(1)</sup> /IOCB5   | RB5                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CCP3 <sup>1</sup> //IOCB5                                                             | ANB5                   | AN                     |             | ADC Channel B5 input.                                                |

|                                                                                       | T1G <sup>(1)</sup>     | TTL/ST                 |             | Timer1 gate input.                                                   |

|                                                                                       | SMTSIG2 <sup>(1)</sup> | TTL/ST                 |             | Signal Measurement Timer2 (SMT2) signal input.                       |

|                                                                                       | CCP3 <sup>(1)</sup>    | TTL/ST                 | CMOS/OD     | Capture/compare/PWM3 (default input location for capture function).  |

|                                                                                       | IOCB5                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB6/ANB6/CLCIN2 <sup>(1)</sup> /IOCB6/<br>ICSPCLK                                     | RB6                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| IUSPULK                                                                               | ANB6                   | AN                     | _           | ADC Channel B6 input.                                                |

|                                                                                       | CLCIN2 <sup>(1)</sup>  | TTL/ST                 | _           | Configurable Logic Cell source input.                                |

|                                                                                       | IOCB6                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

|                                                                                       | ICSPCLK                | ST                     | _           | In-Circuit Serial Programming <sup>™</sup> and debugging clock input |

| RB7/ANB7/DAC1OUT2/T6IN <sup>(1)</sup> /<br>CLCIN3 <sup>(1)</sup> /IOCB7/ICSPDAT       | RB7                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CLCIN3 <sup>11</sup> /IOCB7/ICSPDAI                                                   | ANB7                   | AN                     | _           | ADC Channel B7 input.                                                |

|                                                                                       | DAC1OUT2               | —                      | AN          | Digital-to-Analog Converter output.                                  |

|                                                                                       | T6IN <sup>(1)</sup>    | TTL/ST                 | —           | Timer6 external digital clock input.                                 |

|                                                                                       | CLCIN3 <sup>(1)</sup>  | TTL/ST                 | _           | Configurable Logic Cell source input.                                |

|                                                                                       | IOCB7                  | TTL/ST                 | —           | Interrupt-on-change input.                                           |

|                                                                                       | ICSPDAT                | ST                     | CMOS        | In-Circuit Serial Programming™ and debugging data input/<br>output.  |

#### **TABLE 1-3**: PIC16F18876 PINOUT DESCRIPTION (CONTINUED)

AN = Analog input of output of the second o

Note 1: pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal. All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options

2: as described in Table 13-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| Name                                                                                | Function               | Input Type                                                        | Output Type | Description                                                                                       |  |

|-------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------|--|

| RC0/ANC0/T1CKI <sup>(1)</sup> /T3CKI <sup>(1)</sup> /T3G <sup>(1)</sup> /           | RC0                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

| SMTWIN1 <sup>(1)</sup> /IOCC0/SOSCO                                                 | ANC0                   | AN                                                                | _           | ADC Channel C0 input.                                                                             |  |

|                                                                                     | T1CKI <sup>(1)</sup>   | ICKI <sup>(1)</sup> TTL/ST — Timer1 external digital clock input. |             |                                                                                                   |  |

|                                                                                     | T3CKI <sup>(1)</sup>   | TTL/ST                                                            | _           | Timer3 external digital clock input.                                                              |  |

|                                                                                     | T3G <sup>(1)</sup>     | TTL/ST                                                            | _           | Timer3 gate input.                                                                                |  |

|                                                                                     | SMTWIN1 <sup>(1)</sup> | TTL/ST                                                            | —           | Signal Measurement Timer1 (SMT1) input.                                                           |  |

|                                                                                     | IOCC0                  | TTL/ST                                                            | _           | Interrupt-on-change input.                                                                        |  |

|                                                                                     | SOSCO                  | —                                                                 | AN          | 32.768 kHz secondary oscillator crystal driver output.                                            |  |

| RC1/ANC1/SMTSIG1 <sup>(1)</sup> /CCP2 <sup>(1)</sup> /                              | RC1                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

| IOCC1/SOSCI                                                                         | ANC1                   | AN                                                                | —           | ADC Channel C1 input.                                                                             |  |

|                                                                                     | SMTSIG1 <sup>(1)</sup> | TTL/ST                                                            | _           | Signal Measurement Timer1 (SMT1) signal input.                                                    |  |

|                                                                                     | CCP2 <sup>(1)</sup>    | TTL/ST                                                            | CMOS/OD     | Capture/compare/PWM2 (default input location for capture function).                               |  |

|                                                                                     | IOCC1                  | TTL/ST                                                            | —           | Interrupt-on-change input.                                                                        |  |

|                                                                                     | SOSCI                  | AN                                                                | —           | 32.768 kHz secondary oscillator crystal driver input.                                             |  |

| RC2/ANC2/T5CKI <sup>(1)</sup> /CCP1 <sup>(1)</sup> /IOCC2                           | RC2                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

|                                                                                     | ANC2                   | AN                                                                | —           | ADC Channel C2 input.                                                                             |  |

|                                                                                     | T5CKI <sup>(1)</sup>   | TTL/ST                                                            | _           | Timer5 external digital clock input.                                                              |  |

|                                                                                     | CCP1 <sup>(1)</sup>    | TTL/ST                                                            | CMOS/OD     | Capture/compare/PWM1 (default input location for capture function).                               |  |

|                                                                                     | IOCC2                  | TTL/ST                                                            | —           | Interrupt-on-change input.                                                                        |  |

| RC3/ANC3/SCL1 <sup>(3,4)</sup> /SCK1 <sup>(1)</sup> /<br>T2IN <sup>(1)</sup> /IOCC3 | RC3                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

| 121N**/10003                                                                        | ANC3                   | AN                                                                | —           | ADC Channel C3 input.                                                                             |  |

|                                                                                     | SCL1 <sup>(3,4)</sup>  | I <sup>2</sup> C/SMBus                                            | OD          | MSSP1 I <sup>2</sup> C clock input/output.                                                        |  |

|                                                                                     | SCK1 <sup>(1)</sup>    | TTL/ST                                                            | CMOS/OD     | MSSP1 SPI clock input/output (default input location, SCK1 is a PPS remappable input and output). |  |

|                                                                                     | T2IN <sup>(1)</sup>    | TTL/ST                                                            | —           | Timer2 external input.                                                                            |  |

|                                                                                     | IOCC3                  | TTL/ST                                                            | —           | Interrupt-on-change input.                                                                        |  |

| RC4/ANC4/SDA1 <sup>(3,4)</sup> /SDI1 <sup>(1)</sup> /IOCC4                          | RC4                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

|                                                                                     | ANC4                   | AN                                                                | —           | ADC Channel C4 input.                                                                             |  |

|                                                                                     | SDA1 <sup>(3,4)</sup>  | I <sup>2</sup> C/SMBus                                            | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                  |  |

|                                                                                     | SDI1 <sup>(1)</sup>    | TTL/ST                                                            | —           | MSSP1 SPI serial data input.                                                                      |  |

|                                                                                     | IOCC4                  | TTL/ST                                                            | —           | Interrupt-on-change input.                                                                        |  |

| RC5/ANC5/T4IN <sup>(1)</sup> /IOCC5                                                 | RC5                    | TTL/ST                                                            | CMOS/OD     | General purpose I/O.                                                                              |  |

|                                                                                     | ANC5                   | AN                                                                | -           | ADC Channel C5 input.                                                                             |  |

|                                                                                     | T4IN <sup>(1)</sup>    | TTL/ST                                                            | _           | Timer4 external input.                                                                            |  |

|                                                                                     | IOCC5                  | TTL/ST                                                            | _           | Interrupt-on-change input.                                                                        |  |

#### **TABLE 1-3**: PIC16F18876 PINOUT DESCRIPTION (CONTINUED)

CMOS = CMOS compatible input or output Legend: AN = Analog input or output OD = Open-Drain = Schmitt Trigger input with CMOS levels TTL = TTL compatible input ST I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>CHV= High Voltage XTAL= Crystal levels

This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx Note 1: pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal. All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options

2: as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| Address      | Name        | PIC16(L)F18856 | PIC16(L)F18876 | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3        | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |

|--------------|-------------|----------------|----------------|---------|---------|---------|---------|--------------|---------|---------|---------|-----------------------|------------------------------|

| Bank 30      | (Continued) |                |                |         |         |         |         |              |         |         |         |                       |                              |

| F47h         | INLVLB      |                |                | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3      | INLVLB2 | INLVLB1 | INLVLB0 | 1111 1111             | 1111 1111                    |

| F48h         | IOCBP       |                |                | IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3       | IOCBP2  | IOCBP1  | IOCBP0  | 0000 0000             | 0000 0000                    |

| F49h         | IOCBN       |                |                | IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3       | IOCBN2  | IOCBN1  | IOCBN0  | 0000 0000             | 0000 0000                    |

| F4Ah         | IOCBF       |                |                | IOCBF7  | IOCBF6  | IOCBF5  | IOCBF4  | IOCBF3       | IOCBF2  | IOCBF1  | IOCBF0  | 0000 0000             | 0000 0000                    |

| F4Bh         | CCDNB       |                |                | CCDNB7  | CCDNB6  | CCDNB5  | CCDNB4  | CCDNB3       | CCDNB2  | CCDNB1  | CCDNB0  | 0000 0000             | 0000 0000                    |

| F4Ch         | CCDPB       |                |                | CCDPB7  | CCDPB6  | CCDPB5  | CCDPB4  | CCDPB3       | CCDPB2  | CCDPB1  | CCDPB0  | 0000 0000             | 0000 0000                    |

| F4Dh         | —           |                | -              |         |         |         | U       | nimplemented |         | •       | •       | -                     | —                            |

| F4Eh         | ANSELC      |                |                | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3        | ANSC2   | ANSC1   | ANSC0   | 1111 1111             | 1111 1111                    |

| F4Fh         | WPUC        |                |                | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3        | WPUC2   | WPUC1   | WPUC0   | 0000 0000             | 0000 0000                    |

| F50h         | ODCONC      |                |                | ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3        | ODCC2   | ODCC1   | ODCC0   | 0000 0000             | 0000 0000                    |

| F51h         | SLRCONC     |                |                | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3        | SLRC2   | SLRC1   | SLRC0   | 1111 1111             | 1111 1111                    |

| F52h         | INLVLC      |                |                | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3      | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                    |

| F53h         | IOCCP       |                |                | IOCCP7  | IOCCP6  | IOCCP5  | IOCCP4  | IOCCP3       | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                    |

| F54h         | IOCCN       |                |                | IOCCN7  | IOCCN6  | IOCCN5  | IOCCN4  | IOCCN3       | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                    |

| F55h         | IOCCF       |                |                | IOCCF7  | IOCCF6  | IOCCF5  | IOCCF4  | IOCCF3       | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                    |

| F56h         | CCDNC       |                |                | CCDNC7  | CCDNC6  | CCDNC5  | CCDNC4  | CCDNC3       | CCDNC2  | CCDNC1  | CCDNC0  | 0000 0000             | 0000 0000                    |

| F57h         | CCDPC       |                |                | CCDPC7  | CCDPC6  | CCDPC5  | CCDPC4  | CCDPC3       | CCDPC2  | CCDPC1  | CCDPC0  | 0000 0000             | 0000 0000                    |

| F58h         | -           | -              | -              |         |         |         | U       | nimplemented |         |         |         | —                     | —                            |

| F59h         | ANSELD      | _              | Х              | ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3        | ANSD2   | ANSD1   | ANSD0   | 1111 1111             | 1111 1111                    |

| F090         | ANGELD      | Χ.             | -              |         |         |         | U       | nimplemented |         |         |         |                       |                              |

| <b>FEA</b> b | WPUD        | —              | Х              | WPUD7   | WPUD6   | WPUD5   | WPUD4   | WPUD3        | WPUD2   | WPUD1   | WPUD0   | 0000 0000             | 0000 0000                    |

| F5Ah         |             | х.             | —              |         |         |         | U       | nimplemented |         |         |         |                       |                              |

| <b>FED</b> b |             | —              | Х              | ODCD7   | ODCD6   | ODCD5   | ODCD4   | ODCD3        | ODCD2   | ODCD1   | ODCD0   | 0000 0000             | 0000 0000                    |

| F5Bh         | ODCOND      | х·             | —              |         |         |         | U       | nimplemented |         |         |         |                       |                              |

#### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18855/75 devices only. Legend:

Note 1:

2: Unimplemented, read as '1'.

## PIC16(L)F18856/76

#### 6.4.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. Therefore, the device will always be executing code while the OST is operating.

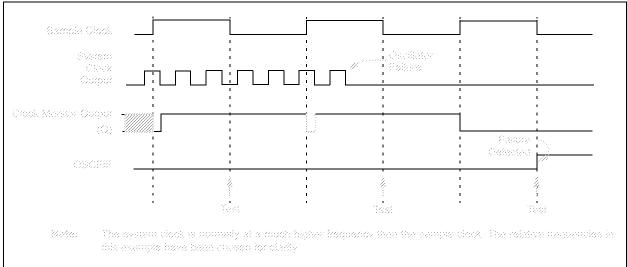

#### FIGURE 6-10: FSCM TIMING DIAGRAM

## PIC16(L)F18856/76

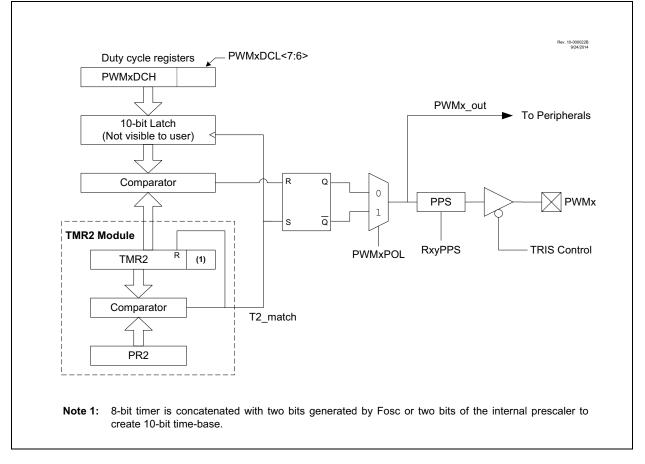

#### 19.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2 register

- PR2 register

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 19-2 shows a simplified block diagram of PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = '0', the output will be the default state.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin

#### FIGURE 19-2: SIMPLIFIED PWM BLOCK DIAGRAM

# PIC16(L)F18856/76

#### 29.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 29-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

#### FIGURE 29-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

|                              |                                                                                                                                                                                | Rev. 10-000200B<br>5/19/2016 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| MODE                         | 0b01001                                                                                                                                                                        |                              |

| TMRx_clk                     |                                                                                                                                                                                |                              |

| PRx                          | 5                                                                                                                                                                              |                              |

| Instruction <sup>(1)</sup> - | BSF BSF BCF                                                                                                                                                                    |                              |

| ON                           |                                                                                                                                                                                |                              |

| TMRx_ers                     |                                                                                                                                                                                |                              |

| TMRx                         | $0 \qquad \left( 1 \left( 2 \left( 3 \right) \left( 4 \right) \right) 5 \right) \qquad 0 \qquad \left( 1 \right) $                                                             | 2                            |

| CCP_pset                     |                                                                                                                                                                                |                              |

| TMRx_postscaled              |                                                                                                                                                                                |                              |

| PWM Duty<br>Cycle            | 3                                                                                                                                                                              |                              |

| PWM Output                   |                                                                                                                                                                                |                              |

|                              | BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the CF<br>to clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input. |                              |

#### 30.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 28.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

#### 30.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 30.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 30-1 demonstrates the code to perform this function.

#### EXAMPLE 30-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

### 30.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

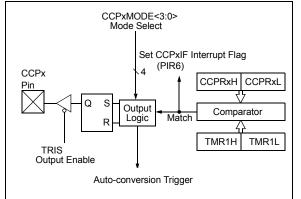

### 30.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- Set the CCPx output

- Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 30-2 shows a simplified diagram of the compare operation.

#### 31.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<3:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSPxCON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRISx register) appropriately programmed as follows:

- SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding

TRIS bit cleared

- SCK (Slave mode) must have corresponding

TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. The MSSP consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full Detect bit, BF of the SSPxSTAT register, and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSPxCON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSPxBUF register to complete successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The Buffer Full bit, BF of the SSPxSTAT register, indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various Status conditions.

#### SPI Master SSPM<3:0> = 00xx SPI Slave SSPM<3:0> = 010x = 1010 SDO SDI Serial Input Buffer Serial Input Buffer (SSPxBUF) (SSPxBUF) SDI SDO Shift Register Shift Register (SSPxSR) (SSPxSR) LSb MSb MSb LSb Serial Clock SCK SCK Slave Select General I/O SS (optional) Processor 1 Processor 2

#### FIGURE 31-5: SPI MASTER/SLAVE CONNECTION

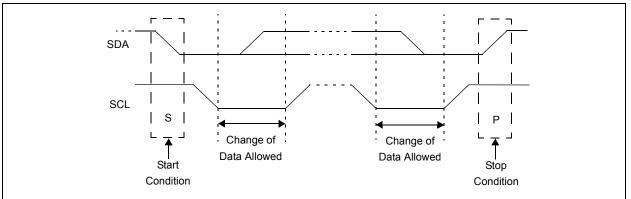

#### 31.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 31-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 31.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

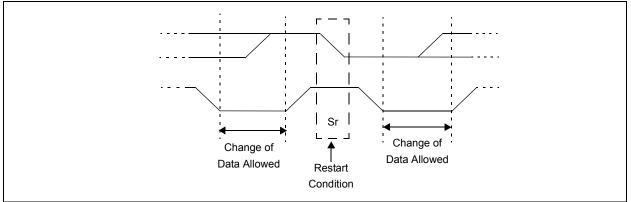

#### 31.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 31-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with R/W clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with R/W clear, or high address match fails.

#### 31.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

#### FIGURE 31-12: I<sup>2</sup>C START AND STOP CONDITIONS

#### 31.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 31-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish I<sup>2</sup>C communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data byte to the slave and clocks out the slaves ACK on the ninth SCL pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

### 31.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 31-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 31-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

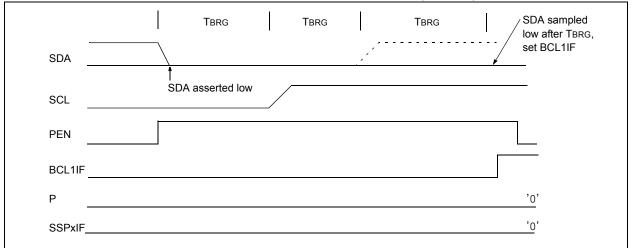

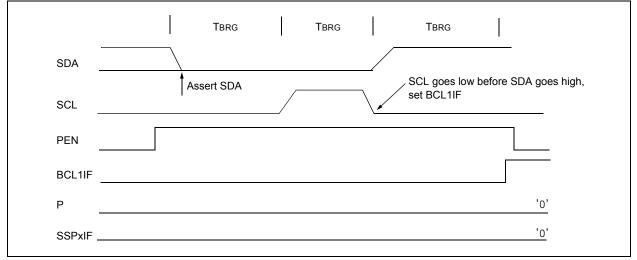

#### 31.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 31-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 31-39).

#### FIGURE 31-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 31-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

### 32.1 SMT Operation

The core of the module is the 24-bit counter, SMTxTMR combined with a complex data acquisition front-end. Depending on the mode of operation selected, the SMT can perform a variety of measurements summarized in Table 32-1.

#### 32.1.1 CLOCK SOURCES

Clock sources available to the SMT include:

- Fosc

- Fosc/4

- HFINTOSC (16 MHz)

- LFINTOSC

- MFINTOSC/16 (31.25 kHz)

The SMT clock source is selected by configuring the CSEL<2:0> bits in the SMTxCLK register. The clock source can also be prescaled using the PS<1:0> bits of the SMTxCON0 register. The prescaled clock source is used to clock both the counter and any synchronization logic used by the module.

#### 32.1.2 PERIOD MATCH INTERRUPT

Similar to other timers, the SMT triggers an interrupt when SMTxTMR rolls over to '0'. This happens when SMTxTMR = SMTxPR, regardless of mode. Hence, in any mode that relies on an external signal or a window to reset the timer, proper operation requires that SMTxPR be set to a period larger than that of the expected signal or window.

#### 32.2 Basic Timer Function Registers

The SMTxTMR time base and the SMTxCPW/SMTxPR/SMTxCPR buffer registers serve several functions and can be manually updated using software.

#### 32.2.1 TIME BASE

The SMTxTMR is the 24-bit counter that is the center of the SMT. It is used as the basic counter/timer for measurement in each of the modes of the SMT. It can be reset to a value of 24'h00\_0000 by setting the RST bit of the SMTxSTAT register. It can be written to and read from software, but it is not guarded for atomic access, therefore reads and writes to the SMTxTMR should only be made when the GO = 0, or the software should have other measures to ensure integrity of SMTxTMR reads/writes.

#### 32.2.2 PULSE WIDTH LATCH REGISTERS

The SMTxCPW registers are the 24-bit SMT pulse width latch. They are used to latch in the value of the SMTxTMR when triggered by various signals, which are determined by the mode the SMT is currently in.

The SMTxCPW registers can also be updated with the current value of the SMTxTMR value by setting the CPWUP bit of the SMTxSTAT register.

#### 32.2.3 PERIOD LATCH REGISTERS

The SMTxCPR registers are the 24-bit SMT period latch. They are used to latch in other values of the SMTxTMR when triggered by various other signals, which are determined by the mode the SMT is currently in.

The SMTxCPR registers can also be updated with the current value of the SMTxTMR value by setting the CPRU bit in the SMTxSTAT register.

#### 32.3 Halt Operation

The counter can be prevented from rolling-over using the STP bit in the SMTxCON0 register. When halting is enabled, the period match interrupt persists until the SMTxTMR is reset (either by a manual reset, **Section 32.2.1 "Time Base"**) or by clearing the SMTxGO bit of the SMTxCON1 register and writing the SMTxTMR values in software.

### 32.4 Polarity Control

The three input signals for the SMT have polarity control to determine whether or not they are active high/positive edge or active low/negative edge signals.

The following bits apply to Polarity Control:

- WSEL bit (Window Polarity)

- SSEL bit (Signal Polarity)

- CSEL bit (Clock Polarity)

These bits are located in the SMTxCON0 register.

#### 32.5 Status Information

The SMT provides input status information for the user without requiring the need to deal with the polarity of the incoming signals.

#### 32.5.1 WINDOW STATUS

Window status is determined by the WS bit of the SMTxSTAT register. This bit is only used in Windowed Measure, Gated Counter and Gated Window Measure modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

#### 32.5.2 SIGNAL STATUS

Signal status is determined by the AS bit of the SMTxSTAT register. This bit is used in all modes except Window Measure, Time of Flight and Capture modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

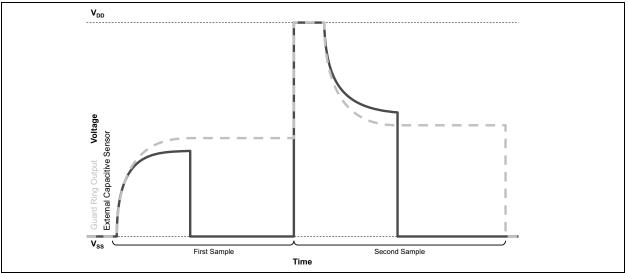

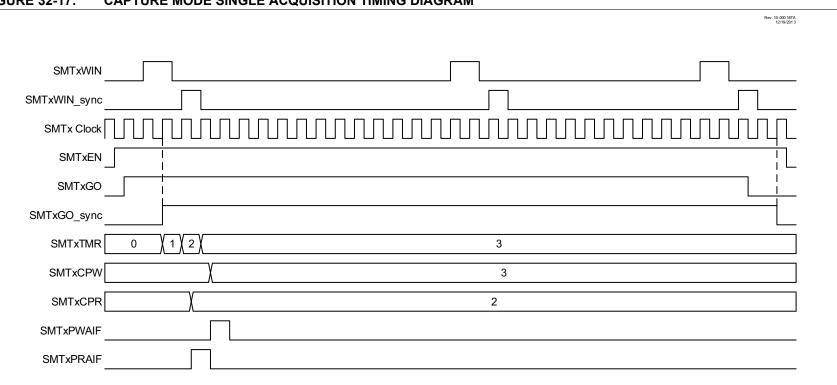

#### FIGURE 32-17: CAPTURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC16(L)F18856/76

#### 33.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR3 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Interrupt Enable bit of the PIE3 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 33.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RC1STA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RC1STA register which resets the EUSART. Clearing the CREN bit of the RC1STA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

Note: If all receive characters in the receive FIFO have framing errors, repeated reads of the RCREG will not clear the FERR bit.

#### 33.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RC1STA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RC1STA register or by resetting the EUSART by clearing the SPEN bit of the RC1STA register.

#### 33.1.2.6 Receiving 9-Bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 33.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RC1STA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

#### 33.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SPBRGH, SPBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

Table 33-1 contains the formulas for determining the baud rate. Example 33-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 33-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

#### EXAMPLE 33-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{Fosc}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPBRGH:SPBRGL:

1

| $X = \frac{Fosc}{\frac{Desired Baud Rate}{64} - 1}$                     |

|-------------------------------------------------------------------------|

| $=\frac{\frac{16000000}{9600}}{64}-1$                                   |

| = [25.042] = 25                                                         |

| Calculated Baud Rate = $\frac{16000000}{64(25+1)}$                      |

| = 9615                                                                  |

| Error = $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$ |

| $=\frac{(9615-9600)}{9600} = 0.16\%$                                    |

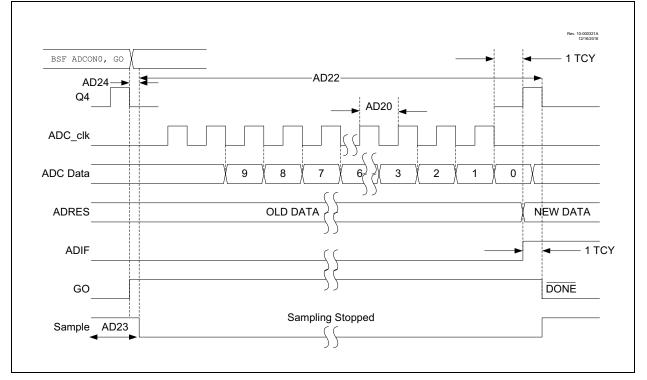

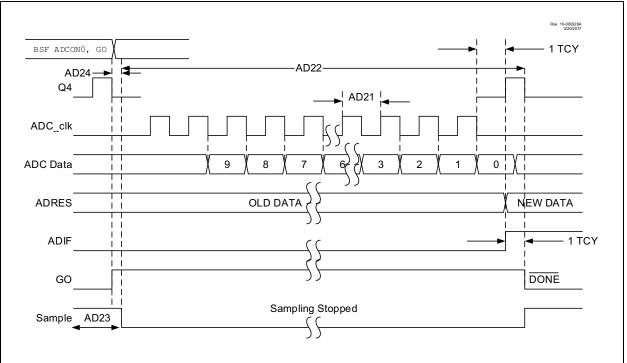

#### TABLE 37-13: ANALOG-TO-DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| rating Conditions (unless othe | erwise stated) |

|--------------------------------|----------------|

|--------------------------------|----------------|

| otanuai       | u ope | rating conditions (unless otherwise          | Stated |         |      |       |                                                   |

|---------------|-------|----------------------------------------------|--------|---------|------|-------|---------------------------------------------------|

| Param.<br>No. | Sym.  | Characteristic                               | Min.   | Тур†    | Max. | Units | Conditions                                        |

| AD20          | Tad   | ADC Clock Period                             | 1      | 1       | 9    | μS    | Using Fosc as the ADC clock<br>source ADOCS = 0   |

| AD21          |       |                                              | 1      | 2       | 6    | μS    | Using FRC as the ADC clock<br>source ADOCS = 1    |

| AD22          | TCNV  | Conversion Time                              | —      | 11+3Tcy | —    | Tad   | Set of GO/DONE bit to Clear of GO/DONE bit        |

| AD23          | TACQ  | Acquisition Time                             | _      | 2       | _    | μS    |                                                   |

| AD24          | Тнср  | Sample and Hold Capacitor<br>Disconnect Time | —      | —       | _    | μS    | Fosc-based clock source<br>Frc-based clock source |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 37-10: ADC CONVERSION TIMING (ADC CLOCK Fosc-BASED)

## PIC16(L)F18856/76

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |          |      |  |  |  |

|-------------------------|-------------|----------|----------|------|--|--|--|

| Dimension               | Limits      | MIN      | NOM      | MAX  |  |  |  |

| Number of Pins          | Ν           |          | 44       |      |  |  |  |

| Pitch                   | е           |          | 0.65 BSC |      |  |  |  |

| Overall Height          | Α           | 0.80     | 0.90     | 1.00 |  |  |  |

| Standoff                | A1          | 0.00     | 0.02     | 0.05 |  |  |  |

| Terminal Thickness      | A3          | 0.20 REF |          |      |  |  |  |

| Overall Width           | E           |          | 8.00 BSC |      |  |  |  |

| Exposed Pad Width       | E2          | 6.25     | 6.45     | 6.60 |  |  |  |

| Overall Length          | D           | 8.00 BSC |          |      |  |  |  |

| Exposed Pad Length      | D2          | 6.25     | 6.45     | 6.60 |  |  |  |

| Terminal Width          | b           | 0.20     | 0.30     | 0.35 |  |  |  |

| Terminal Length         | L           | 0.30     | 0.40     | 0.50 |  |  |  |

| Terminal-to-Exposed-Pad | К           | 0.20     | -        | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2