Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

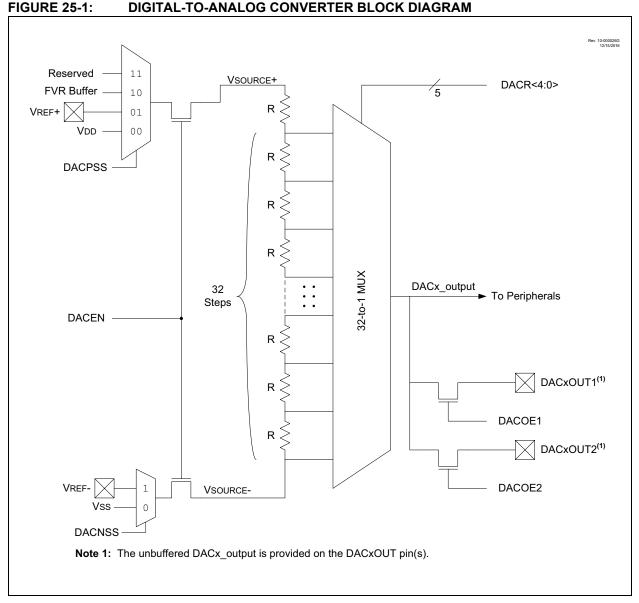

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18856-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

#### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as shown in Table 4-1.

### TABLE 4-1:CONFIGURATION WORD<br/>LOCATIONS

| Configuration Word | Location |

|--------------------|----------|

| CONFIG1            | 8007h    |

| CONFIG2            | 8008h    |

| CONFIG3            | 8009h    |

| CONFIG4            | 800Ah    |

| CONFIG5            | 800Bh    |

| Note: | The DEBUG bit in Configuration Words is     |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

#### REGISTER 6-7: OSCTUNE: HFINTOSC TUNING REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     |     |         |         | IUTAH   | N<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'.                                                                           |

|---------|-------------------------------------------------------------------------------------------------------|

| bit 5-0 | HFTUN<5:0>: HFINTOSC Frequency Tuning bits 11 1111 = Maximum frequency                                |

|         | •                                                                                                     |

|         |                                                                                                       |

|         |                                                                                                       |

|         | 10 0001                                                                                               |

|         | 10 0000 = Center frequency. Oscillator module is running at the calibrated frequency (default value). |

|         | 01 1111                                                                                               |

|         | •                                                                                                     |

|         | •                                                                                                     |

|         | •                                                                                                     |

|         | 00 0000 = Minimum frequency.                                                                          |

| U-0                                                                                                               | U-0                                                                                                               | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0           | R/W-0/0    |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|----------------|------------------|-------------------|------------|

| _                                                                                                                 | —                                                                                                                 | SMT2PWAIE                          | SMT2PRAIE       | SMT2IE         | SMT1PWAIE        | SMT1PRAIE         | SMT1IE     |

| bit 7                                                                                                             |                                                                                                                   |                                    |                 |                |                  |                   | bit 0      |

|                                                                                                                   |                                                                                                                   |                                    |                 |                |                  |                   |            |

| Legend:                                                                                                           |                                                                                                                   |                                    |                 |                |                  |                   |            |

| R = Reada                                                                                                         | ble bit                                                                                                           | W = Writable b                     | bit             | U = Unimpler   | mented bit, read | l as '0'          |            |

| u = Bit is u                                                                                                      | nchanged                                                                                                          | x = Bit is unkn                    | own             | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is s                                                                                                    | set                                                                                                               | '0' = Bit is clea                  | ared            | HS = Hardwa    | are set          |                   |            |

|                                                                                                                   |                                                                                                                   |                                    |                 |                |                  |                   |            |

| bit 7-6                                                                                                           | Unimpleme                                                                                                         | nted: Read as '0                   | )'.             |                |                  |                   |            |

| bit 6                                                                                                             |                                                                                                                   | E: SMT2 Pulse-V                    |                 |                | able bit         |                   |            |

| <ul> <li>1 = Enables the SMT acquisition interrupt</li> <li>0 = Disables the SMT acquisition interrupt</li> </ul> |                                                                                                                   |                                    |                 |                |                  |                   |            |

|                                                                                                                   |                                                                                                                   | •                                  | •               |                | •,               |                   |            |

| bit 5                                                                                                             |                                                                                                                   | : SMT2 Period A<br>s the SMT acqui |                 | •              | DIT              |                   |            |

|                                                                                                                   |                                                                                                                   | es the SMT acqui                   | •               |                |                  |                   |            |

| bit 4                                                                                                             | SMT2IE: SM                                                                                                        | IT2 Overflow Inte                  | errupt Enable b | bit            |                  |                   |            |

|                                                                                                                   | 1 = Enable                                                                                                        | s the SMT overfl                   | low interrupt   |                |                  |                   |            |

|                                                                                                                   | 0 = Disable                                                                                                       | es the SMT overf                   | flow interrupt  |                |                  |                   |            |

| bit 2                                                                                                             |                                                                                                                   | E: SMT1 Pulse-V                    |                 | •              | able bit         |                   |            |

|                                                                                                                   | <ul> <li>1 = Enables the SMT acquisition interrupt</li> <li>0 = Disables the SMT acquisition interrupt</li> </ul> |                                    |                 |                |                  |                   |            |

| bit 1                                                                                                             |                                                                                                                   |                                    |                 |                | .i+              |                   |            |

| bit 1 SMT1PRAIE: SMT1 Period Acquisition Interrupt Enable bit<br>1 = Enables the SMT acquisition interrupt        |                                                                                                                   |                                    |                 |                |                  |                   |            |

|                                                                                                                   |                                                                                                                   | es the SMT acqu                    |                 |                |                  |                   |            |

| bit 0                                                                                                             | SMT1IE: SM                                                                                                        | 1T1 Overflow Inte                  | errupt Enable b | bit            |                  |                   |            |

|                                                                                                                   | 1 = Enable                                                                                                        | s the SMT overfl                   | low interrupt   |                |                  |                   |            |

|                                                                                                                   |                                                                                                                   |                                    |                 |                |                  |                   |            |

#### REGISTER 7-10: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE8.

0 = Disables the SMT overflow interrupt

#### 11.7 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic Program Memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 11.4 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word – 1 (refer to Example 11-1). This determines how many times the shifter will shift into the accumulator for each data word.

- Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial – 2 (refer to Example 11-1).

- Determine whether shifting in trailing zeros is desired and set the ACCM bit of CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has >8 bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a. If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the CRCIF (or the BUSY bit) to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b.If manual entry is used, monitor the CRCIF (or BUSY bit) to determine when the CRCACC registers will hold the check value.

#### 11.8 Program Memory Scan Configuration

If desired, the Program Memory Scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the Scanner to work with the CRC you need to perform the following steps:

- Set the EN bit to enable the module. This can be performed at any point preceding the setting of the SCANGO bit, but if it gets disabled, all internal states of the Scanner are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 11.10 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 11.10.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H and SCANHADRL/H registers with the beginning and ending locations in memory that are to be scanned.

- 5. Begin the scan by setting the SCANGO bit in the SCANCON0 register. The scanner will wait (CRCGO must be set) for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

#### 11.9 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

#### 11.10 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 11-1.

| R/W-0/0                           | R/W-0/0 | R/W-0/0      | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|-----------------------------------|---------|--------------|---------|--------------|------------------|---------|---------|

| WPUA7                             | WPUA6   | WPUA5        | WPUA4   | WPUA3        | WPUA2            | WPUA1   | WPUA0   |

| bit 7                             |         |              |         | 1 1          |                  |         | bit 0   |

|                                   |         |              |         |              |                  |         |         |

| Legend:                           |         |              |         |              |                  |         |         |

| R = Readable bit W = Writable bit |         |              |         |              |                  |         |         |

| R = Readable                      | bit     | W = Writable | bit     | U = Unimplem | nented bit, read | as '0'  |         |

#### REGISTER 12-6: WPUA: WEAK PULL-UP PORTA REGISTER

'0' = Bit is cleared

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits<sup>(1)</sup> 1 = Pull-up enabled 0 = Pull-up disabled

'1' = Bit is set

Note 1: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### REGISTER 12-7: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCA7   | ODCA6   | ODCA5   | ODCA4   | ODCA3   | ODCA2   | ODCA1   | ODCA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ODCA<7:0>: PORTA Open-Drain Enable bits

For RA<7:0> pins, respectively

- 1 = Port pin operates as open-drain drive (sink current only)

- 0 = Port pin operates as standard push-pull drive (source and sink current)

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRD7   | SLRD6   | SLRD5   | SLRD4   | SLRD3   | SLRD2   | SLRD1   | SLRD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

#### REGISTER 12-38: SLRCOND: PORTD SLEW RATE CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **SLRD<7:0>:** PORTD Slew Rate Enable bits For RD<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 12-39: INLVLD: PORTD INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4 | INLVLD3 | INLVLD2 | INLVLD1 | INLVLD0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLD<7:0>: PORTD Input Level Select bits

For RD<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

#### 12.14.8 CURRENT-CONTROLLED DRIVE MODE CONTROL

The CCDPE and CCDNE registers (Register 12-53 and Register 12-54) control the Current-Controlled Drive mode for both the positive-going and negative-going drivers. When a CCDPE[y] or CCDNE[y] bit is set and the CCDEN bit of the CCDCON register is set, the Current-Controlled mode is enabled for the corresponding port pin. When the CCDPE[y] or CCDNE[y] bit is clear, the Current-Controlled mode for the corresponding port pin is disabled. If the CCDPE[y] or CCDNE[y] bit is set and the CCDEN bit is clear, operation of the port pin is undefined (see **Section 12.1.1** "**Current-Controlled Drive**" for current-controlled use precautions).

#### 12.14.9 PORTE FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

#### 12.14.10 PORTE FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0 "Peripheral Pin Select (PPS) Module"** for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| ABLE 15-1: SUMMART OF REGISTERS ASSOCIATED WITH INTERROPT-ON-CHANGE |        |        |        |        |        |        |        |        |                     |  |

|---------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|--|

| Name                                                                | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

| ANSELA                                                              | ANSA7  | ANSA6  | ANSA4  | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 205                 |  |

| ANSELC                                                              | ANSC7  | ANSC6  | ANSC5  | ANSC4  | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 221                 |  |

| TRISA                                                               | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 204                 |  |

| TRISC                                                               | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 220                 |  |

| INTCON                                                              | GIE    | PEIE   | —      | —      | —      | —      | —      | INTEDG | 134                 |  |

| PIE0                                                                | _      | _      | TMR0IE | IOCIE  |        |        |        | INTE   | 135                 |  |

| IOCAP                                                               | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 262                 |  |

| IOCAN                                                               | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 262                 |  |

| IOCAF                                                               | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 262                 |  |

| IOCBP                                                               | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 263                 |  |

| IOCBN                                                               | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 263                 |  |

| IOCBF                                                               | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 263                 |  |

| IOCCP                                                               | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 264                 |  |

| IOCCN                                                               | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 264                 |  |

| IOCCF                                                               | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 264                 |  |

| IOCEP                                                               | —      | —      | —      | —      | IOCEP3 | —      | —      | —      | 265                 |  |

| IOCEN                                                               | —      | —      | —      | —      | IOCEN3 | —      | —      | —      | 265                 |  |

| IOCEF                                                               | —      | _      |        |        | IOCEF3 |        |        |        | 266                 |  |

#### TABLE 15-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

#### 21.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The OUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The OUT bit is affected by the polarity bit.

#### 21.3 ZCD Logic Polarity

The POL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the POL bit is set, a OUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The POL bit affects the ZCD interrupts. See **Section 21.4 "ZCD Interrupts"**.

#### 21.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR2 register will be set when either edge detector is triggered and its associated enable bit is set. The INTP enables rising edge interrupts and the INTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- ZCDIE bit of the PIE2 register

- INTP bit of the ZCDxCON register (for a rising edge detection)

- INTN bit of the ZCDxCON register (for a falling edge detection)

- PEIE and GIE bits of the INTCON register

Changing the POL bit will cause an interrupt, regardless of the level of the EN bit.

The ZCDIF bit of the PIR2 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

#### 21.5 Correcting for VCPINV offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late.

#### 21.5.1 CORRECTION BY AC COUPLING

When the external voltage source is sinusoidal, the effects of the ZCPINV offset can be eliminated by isolating the external voltage source from the ZCD pin with a capacitor, in addition to the voltage reducing resistor. The capacitor will cause a phase shift resulting in the ZCD output switch in advance of the actual zero crossing event. The phase shift will be the same for both rising and falling zero crossings, which can be compensated for by either delaying the CPU response to the ZCD switch by a timer or other means, or selecting a capacitor value large enough that the phase shift is negligible.

To determine the series resistor and capacitor values for this configuration, start by computing the impedance, Z, to obtain a peak current of  $300 \ \mu$ A. Next, arbitrarily select a suitably large non-polar capacitor and compute its reactance, Xc, at the external voltage source frequency. Finally, compute the series resistor, capacitor peak voltage, and phase shift by the formulas shown in Equation 21-2.

When this technique is used and the input signal is not present, the ZCD will tend to oscillate. To avoid this oscillation, connect the ZCD pin to VDD or GND with a high-impedance resistor such as 200K.

#### REGISTER 24-3: NCO1ACCL: NCO1 ACCUMULATOR REGISTER – LOW BYTE

| المعممط |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         | NCO1A   | CC<7:0> |         |         |         |

| R/W-0/0 |

|         |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1ACC<7:0>: NCO1 Accumulator, Low Byte

#### REGISTER 24-4: NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCO1ACC | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NOC1ACC<15:8>: NCO1 Accumulator, High Byte

#### REGISTER 24-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | _   | _   | _   |         | NCO1AC  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

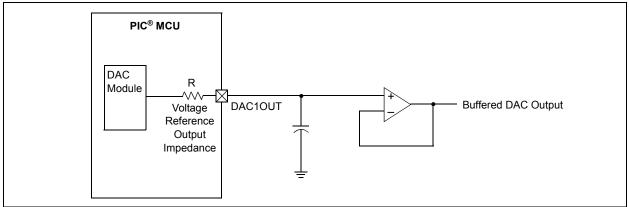

#### FIGURE 25-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### 29.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0>= 00011)

- Reset on rising edge (MODE<4:0> = 00100)

- Reset on falling edge (MODE<4:0> = 00101)

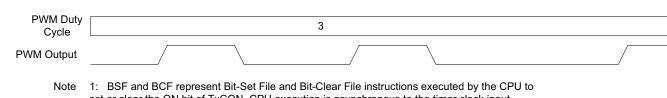

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 29-6.

### FIGURE 29-6: EDGE-TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE = 00100)

|                              | Rev. 10 -000 1578<br>500/2014                                                                                                                                                          |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                         | 0b00100                                                                                                                                                                                |

| TMRx_dk                      |                                                                                                                                                                                        |

| PRx                          | 5                                                                                                                                                                                      |

| Instruction <sup>(1)</sup> - | BSF BSF                                                                                                                                                                                |

| ON                           |                                                                                                                                                                                        |

| TMRx_ers                     |                                                                                                                                                                                        |

| TMRx                         | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                 |

| TMRx_postscaled              |                                                                                                                                                                                        |

| PWM Duty<br>Cycle            | 3                                                                                                                                                                                      |

| PWM Output                   |                                                                                                                                                                                        |

|                              | 1: BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the CPU to set or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input. |

#### 29.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

TMRx\_ers

TMRx\_postscaled

TMRx

0

**FIGURE 29-12:**

• Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the PRx value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

> 2 3

1)

5

0

4

PIC16(L)F18856/76

#### Rev. 10-000203A 4/7/2016 MODE 0b10001 TMRx\_clk PRx 5 Instruction<sup>(1)</sup> BSF (BCF) BSF BSF BCF ON

1 2 3 4

5

0

RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

0

set or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input.

، 3

1 2 5

4

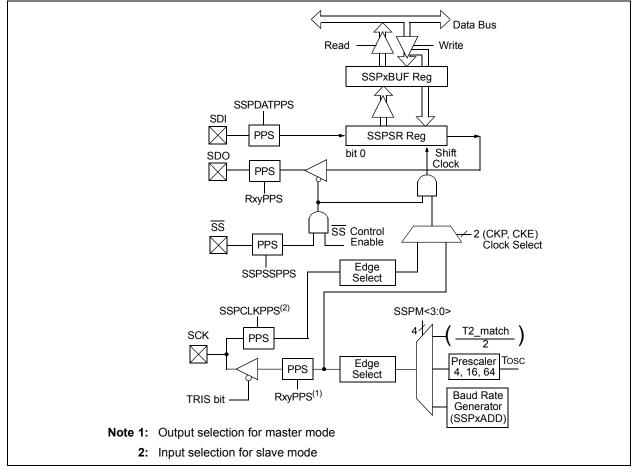

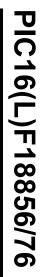

#### 31.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULES

#### 31.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- · Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 31-1 is a block diagram of the SPI interface module.

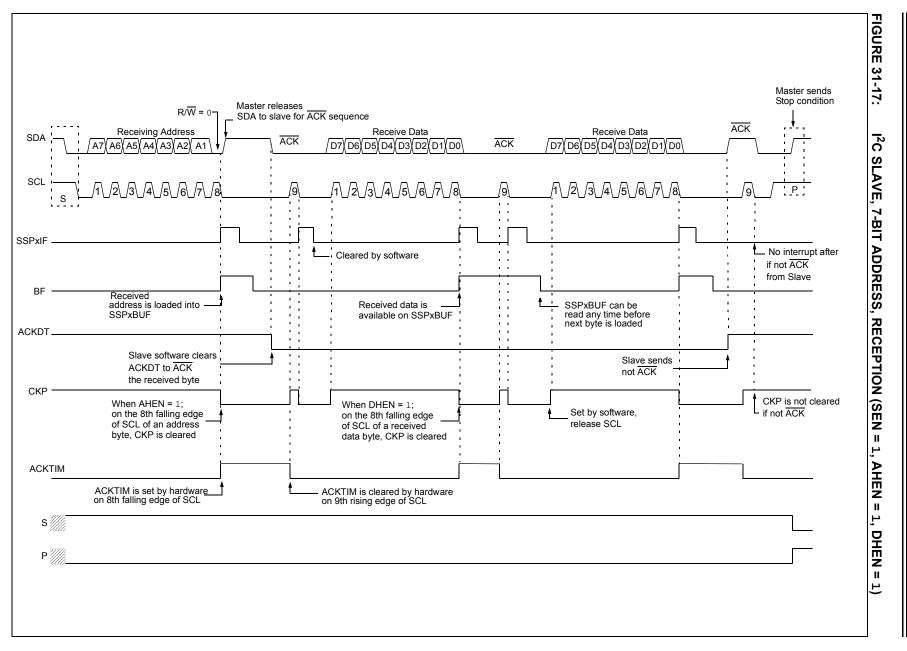

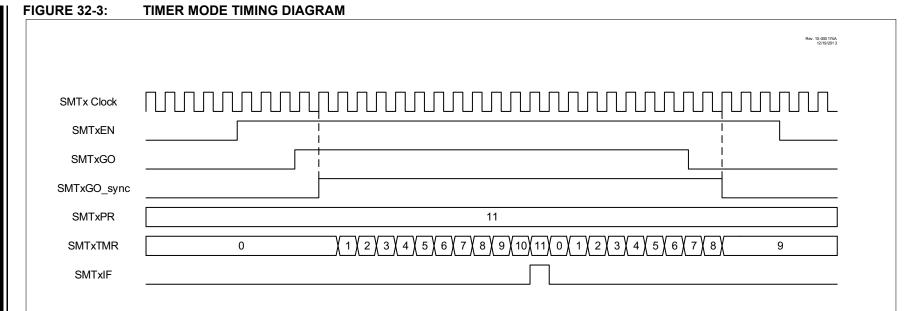

#### FIGURE 32-13: GATED WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAMS

PIC16(L)F18856/76

#### 32.7 Interrupts

The SMT can trigger an interrupt under three different conditions:

- PW Acquisition Complete

- PR Acquisition Complete

- Counter Period Match

The interrupts are controlled by the PIR and PIE registers of the device.

### 32.7.1 PW AND PR ACQUISITION INTERRUPTS

The SMT can trigger interrupts whenever it updates the SMTxCPW and SMTxCPR registers, the circumstances for which are dependent on the SMT mode, and are discussed in each mode's specific section. The SMTxCPW interrupt is controlled by SMTxPWAIF and SMTxPWAIE bits in registers PIR8 and PIE8, respectively. The SMTxCPR interrupt is controlled by the SMTxPRAIF and SMTxPRAIE bits, also located in registers PIR8 and PIE8, respectively.

In synchronous SMT modes, the interrupt trigger is synchronized to the SMTxCLK. In Asynchronous modes, the interrupt trigger is asynchronous. In either mode, once triggered, the interrupt will be synchronized to the CPU clock.

#### 32.7.2 COUNTER PERIOD MATCH INTERRUPT

As described in Section 32.1.2 "Period Match interrupt", the SMT will also interrupt upon SMTxTMR, matching SMTxPR with its period match limit functionality described in Section 32.3 "Halt Operation". The period match interrupt is controlled by SMTxIF and SMTxIE, located in registers PIR8 and PIE8, respectively.

|                | - Bit set by closer                    | 2, , | ;             | ·<br>· | ;<br>; | · · · · · · · · · · · · · · · · · · · | ·····         | · · ·          | Alap Glearad |

|----------------|----------------------------------------|------|---------------|--------|--------|---------------------------------------|---------------|----------------|--------------|

| - 80 BR 80     |                                        |      |               |        | · · ·  |                                       |               | ·              | ·····        |

| X03 068 -      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | animutaj<br>S |        |        | ;<br>                                 |               |                | ······       |

| <b>23638</b> 2 |                                        |      |               | ·····  |        |                                       | un and a same |                |              |

| 8039           |                                        |      | ·····         |        |        | Oleans                                | i due la ĝeer | 8eed of \$6083 |              |

#### FIGURE 33-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

Construction of and readers of a construction of the construction of the readers of the construction of the const

#### 33.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TX1STA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TX1STA register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 33-9 for the timing of the Break character sequence.

#### 33.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

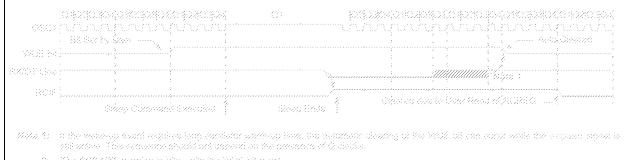

#### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | MILLIMETERS | 6     |

|--------------------------|------------------|------|-------------|-------|

|                          | Dimension Limits | MIN  | NOM         | MAX   |

| Number of Pins           | N                |      | 28          | •     |

| Pitch                    | е                |      | 0.65 BSC    |       |

| Overall Height           | А                | _    | -           | 2.00  |

| Molded Package Thickness | A2               | 1.65 | 1.75        | 1.85  |

| Standoff                 | A1               | 0.05 | -           | -     |

| Overall Width            | E                | 7.40 | 7.80        | 8.20  |

| Molded Package Width     | E1               | 5.00 | 5.30        | 5.60  |

| Overall Length           | D                | 9.90 | 10.20       | 10.50 |

| Foot Length              | L                | 0.55 | 0.75        | 0.95  |

| Footprint                | L1               |      | 1.25 REF    |       |

| Lead Thickness           | С                | 0.09 | -           | 0.25  |

| Foot Angle               | φ                | 0°   | 4°          | 8°    |

| Lead Width               | b                | 0.22 | -           | 0.38  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B