#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

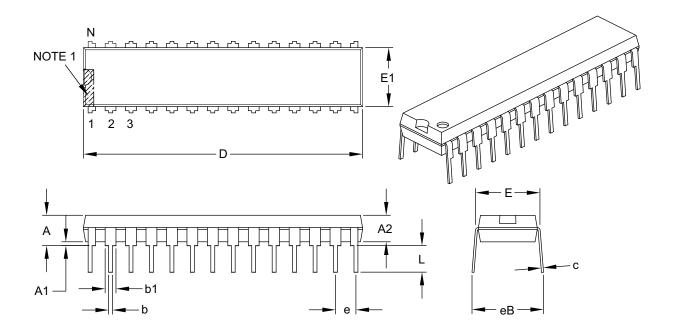

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18856-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F188XX Family Types

| Device         | Data Sheet Index | Program Flash<br>Memory (Words) | Program Flash<br>Memory (KB) | EEPROM<br>(bytes) | Data SRAM<br>(bytes) | I/O Pins <sup>(1)</sup> | 10-Bit ADC <sup>2</sup> (ch) | 5-Bit DAC | Comparator | 8-Bit (with HLT)/<br>16-Bit Timers | SMT | Windowed<br>Watchdog Timer | <b>CRC and Memory Scan</b> | CCP/10-Bit PWM | Zero-Cross Detect | CWG | NCO | CLC | DSM | EUSART/I <sup>2</sup> C/SPI | Peripheral Pin Select | Peripheral Module<br>Disable |

|----------------|------------------|---------------------------------|------------------------------|-------------------|----------------------|-------------------------|------------------------------|-----------|------------|------------------------------------|-----|----------------------------|----------------------------|----------------|-------------------|-----|-----|-----|-----|-----------------------------|-----------------------|------------------------------|

| PIC16(L)F18854 | (1)              | 4096                            | 7                            | 256               | 512                  | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Y                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

| PIC16(L)F18855 | (2)              | 8192                            | 14                           | 256               | 1024                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

| PIC16(L)F18856 | (3)              | 16384                           | 28                           | 256               | 2048                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

| PIC16(L)F18857 | (4)              | 32768                           | 56                           | 256               | 4096                 | 25                      | 24                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Υ                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

| PIC16(L)F18875 | (2)              | 8192                            | 14                           | 256               | 1024                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Y                 | 3   | 1   | 4   | 1   | 1/2                         | Υ                     | Y                            |

| PIC16(L)F18876 | (3)              | 16384                           | 28                           | 256               | 2048                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Y                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

| PIC16(L)F18877 | (4)              | 32768                           | 56                           | 256               | 4096                 | 36                      | 35                           | 1         | 2          | 3/4                                | 2   | Y                          | Y                          | 5/2            | Y                 | 3   | 1   | 4   | 1   | 1/2                         | Y                     | Y                            |

**Note 1:** One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document)

1: DS40001826 PIC16(L)F18854 Data Sheet, 28-Pin, Full-Featured 8-bit Microcontrollers

DS40001802 PIC16(L)F18855/75 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

DS40001824 PIC16(L)F18856/76 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

4: DS40001825

2:

3:

PIC16(L)F18857/77 Data Sheet, 28/40-Pin, Full-Featured 8-bit Microcontrollers

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

| Name                                                                                  | Function               | Input Type             | Output Type | Description                                                          |

|---------------------------------------------------------------------------------------|------------------------|------------------------|-------------|----------------------------------------------------------------------|

| RB2/ANB2/SDA2 <sup>(3,4)</sup> /SDI2 <sup>(1)</sup> /                                 | RB2                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CWG3IN <sup>(1)</sup> /IOCB2                                                          | ANB2                   | AN                     | _           | ADC Channel B2 input.                                                |

|                                                                                       | SDA2 <sup>(3,4)</sup>  | I <sup>2</sup> C/SMBus | OD          | MSSP2 I <sup>2</sup> C serial data input/output.                     |

|                                                                                       | SDI2 <sup>(1)</sup>    | TTL/ST                 | _           | MSSP2 SPI serial data input.                                         |

|                                                                                       | CWG3IN <sup>(1)</sup>  | TTL/ST                 | _           | Complementary Waveform Generator 3 input.                            |

|                                                                                       | IOCB2                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB3/ANB3/C1IN2-/C2IN2-/IOCB3                                                          | RB3                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

|                                                                                       | ANB3                   | AN                     | _           | ADC Channel B3 input.                                                |

|                                                                                       | C1IN2-                 | AN                     | _           | Comparator negative input.                                           |

|                                                                                       | C2IN2-                 | AN                     | _           | Comparator negative input.                                           |

|                                                                                       | IOCB3                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB4/ANB4/ADCACT <sup>(1)</sup> /T5G <sup>(1)</sup> /<br>SMTWIN2 <sup>(1)</sup> /IOCB4 | RB4                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| SMTWINZ\''/IOCB4                                                                      | ANB4                   | AN                     |             | ADC Channel B4 input.                                                |

|                                                                                       | ADCACT <sup>(1)</sup>  | TTL/ST                 | _           | ADC Auto-Conversion Trigger input.                                   |

|                                                                                       | T5G <sup>(1)</sup>     | TTL/ST                 | _           | Timer5 gate input.                                                   |

|                                                                                       | SMTWIN2 <sup>(1)</sup> | TTL/ST                 | _           | Signal Measurement Timer2 (SMT2) window input.                       |

|                                                                                       | IOCB4                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB5/ANB5/T1G <sup>(1)</sup> /SMTSIG2 <sup>(1)</sup> /<br>CCP3 <sup>(1)</sup> /IOCB5   | RB5                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CCP3 <sup>1</sup> //IOCB5                                                             | ANB5                   | AN                     |             | ADC Channel B5 input.                                                |

|                                                                                       | T1G <sup>(1)</sup>     | TTL/ST                 |             | Timer1 gate input.                                                   |

|                                                                                       | SMTSIG2 <sup>(1)</sup> | TTL/ST                 |             | Signal Measurement Timer2 (SMT2) signal input.                       |

|                                                                                       | CCP3 <sup>(1)</sup>    | TTL/ST                 | CMOS/OD     | Capture/compare/PWM3 (default input location for capture function).  |

|                                                                                       | IOCB5                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

| RB6/ANB6/CLCIN2 <sup>(1)</sup> /IOCB6/<br>ICSPCLK                                     | RB6                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| IUSPULK                                                                               | ANB6                   | AN                     | _           | ADC Channel B6 input.                                                |

|                                                                                       | CLCIN2 <sup>(1)</sup>  | TTL/ST                 | _           | Configurable Logic Cell source input.                                |

|                                                                                       | IOCB6                  | TTL/ST                 | _           | Interrupt-on-change input.                                           |

|                                                                                       | ICSPCLK                | ST                     | _           | In-Circuit Serial Programming <sup>™</sup> and debugging clock input |

| RB7/ANB7/DAC1OUT2/T6IN <sup>(1)</sup> /<br>CLCIN3 <sup>(1)</sup> /IOCB7/ICSPDAT       | RB7                    | TTL/ST                 | CMOS/OD     | General purpose I/O.                                                 |

| CLCIN3 <sup>11</sup> /IOCB7/ICSPDAI                                                   | ANB7                   | AN                     | _           | ADC Channel B7 input.                                                |

|                                                                                       | DAC1OUT2               | —                      | AN          | Digital-to-Analog Converter output.                                  |

|                                                                                       | T6IN <sup>(1)</sup>    | TTL/ST                 | —           | Timer6 external digital clock input.                                 |

|                                                                                       | CLCIN3 <sup>(1)</sup>  | TTL/ST                 | _           | Configurable Logic Cell source input.                                |

|                                                                                       | IOCB7                  | TTL/ST                 | —           | Interrupt-on-change input.                                           |

|                                                                                       | ICSPDAT                | ST                     | CMOS        | In-Circuit Serial Programming™ and debugging data input/<br>output.  |

#### **TABLE 1-3**: PIC16F18876 PINOUT DESCRIPTION (CONTINUED)

AN = Analog input of output of the second o

Note 1: pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal. All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options

2: as described in Table 13-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| IADLE           | 3-13. 3PE  |                                  |          | REGISTE  |             | KI DANKS ( | )-31 (CONTIF | NUED)    |              |          |                       |                              |

|-----------------|------------|----------------------------------|----------|----------|-------------|------------|--------------|----------|--------------|----------|-----------------------|------------------------------|

| Address         | Name       | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7    | Bit 6    | Bit 5       | Bit 4      | Bit 3        | Bit 2    | Bit 1        | Bit 0    | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 28 (       | Continued) |                                  |          |          |             |            |              |          |              |          |                       | -                            |

| E22h            | CLC2GLS2   |                                  | LC2G3D4T | LC2G3D4N | LC2G3D3T    | LC2G3D3N   | LC2G3D2T     | LC2G3D2N | LC2G3D1T     | LC2G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E23h            | CLC2GLS3   |                                  | LC2G4D4T | LC2G4D4N | LC2G4D3T    | LC2G4D3N   | LC2G4D2T     | LC2G4D2N | LC2G4D1T     | LC2G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E24h            | CLC3CON    |                                  | LC3EN    | —        | LC3OUT      | LC3INTP    | LC3INTN      |          | LC3MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |

| E25h            | CLC3POL    |                                  | LC3POL   | _        | _           |            | LC3G4POL     | LC3G3POL | LC3G2POL     | LC3G1POL | 0 xxxx                | 0 uuuu                       |

| E26h            | CLC3SEL0   |                                  |          | _        | LC3D1S<5:0> |            |              |          |              | xx xxxx  | uu uuuu               |                              |

| E27h            | CLC3SEL1   |                                  |          | _        |             |            | xx xxxx      | uu uuuu  |              |          |                       |                              |

| E28h            | CLC3SEL2   |                                  |          | _        | LC3D3S<5:0> |            |              |          |              |          | xx xxxx               | uu uuuu                      |

| E29h            | CLC3SEL3   |                                  |          | _        | LC3D4S<5:0> |            |              |          | xx xxxx      | uu uuuu  |                       |                              |

| E2Ah            | CLC3GLS0   |                                  | LC3G1D4T | LC3G1D4N | LC3G1D3T    | LC3G1D3N   | LC3G1D2T     | LC3G1D2N | LC3G1D1T     | LC3G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Bh            | CLC3GLS1   |                                  | LC3G2D4T | LC3G2D4N | LC3G2D3T    | LC3G2D3N   | LC3G2D2T     | LC3G2D2N | LC3G2D1T     | LC3G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Ch            | CLC3GLS2   |                                  | LC3G3D4T | LC3G3D4N | LC3G3D3T    | LC3G3D3N   | LC3G3D2T     | LC3G3D2N | LC3G3D1T     | LC3G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Dh            | CLC3GLS3   |                                  | LC3G4D4T | LC3G4D4N | LC3G4D3T    | LC3G4D3N   | LC3G4D2T     | LC3G4D2N | LC3G4D1T     | LC3G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E2Eh            | CLC4CON    |                                  | LC4EN    | -        | LC4OUT      | LC4INTP    | LC4INTN      |          | LC4MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |

| E2Fh            | CLC4POL    |                                  | LC4POL   | —        |             | _          | LC4G4POL     | LC4G3POL | LC4G2POL     | LC4G1POL | 0 xxxx                | 0 uuuu                       |

| E30h            | CLC4SEL0   |                                  | _        | —        |             |            | LC4          | D1S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E31h            | CLC4SEL1   |                                  |          | _        |             |            | LC4          | D2S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E32h            | CLC4SEL2   |                                  | _        | —        |             |            | LC4          | D3S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E33h            | CLC4SEL3   |                                  |          | _        |             |            | LC4          | D4S<5:0> |              |          | xx xxxx               | uu uuuu                      |

| E34h            | CLC4GLS0   |                                  | LC4G1D4T | LC4G1D4N | LC4G1D3T    | LC4G1D3N   | LC4G1D2T     | LC4G1D2N | LC4G1D1T     | LC4G1D1N | xxxx xxxx             | uuuu uuuu                    |

| E35h            | CLC4GLS1   |                                  | LC4G2D4T | LC4G2D4N | LC4G2D3T    | LC4G2D3N   | LC4G2D2T     | LC4G2D2N | LC4G2D1T     | LC4G2D1N | xxxx xxxx             | uuuu uuuu                    |

| E36h            | CLC4GLS2   |                                  | LC4G3D4T | LC4G3D4N | LC4G3D3T    | LC4G3D3N   | LC4G3D2T     | LC4G3D2N | LC4G3D1T     | LC4G3D1N | xxxx xxxx             | uuuu uuuu                    |

| E37h            | CLC4GLS3   |                                  | LC4G4D4T | LC4G4D4N | LC4G4D3T    | LC4G4D3N   | LC4G4D2T     | LC4G4D2N | LC4G4D1T     | LC4G4D1N | xxxx xxxx             | uuuu uuuu                    |

| E38h to<br>E6Fh | _          | —                                |          |          |             | U          | nimplemented |          |              |          | _                     | _                            |

#### TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

# 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIEx registers)

The PIR1, PIR2, PIR3 and PIR4 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving")

- PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

| Note 1: | Individual  | inte | rrupt | flag  | bits | s are | e set, |

|---------|-------------|------|-------|-------|------|-------|--------|

|         | regardless  | of   | the   | state | of   | any   | other  |

|         | enable bits | -    |       |       |      |       |        |

2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

| REGISTE<br>R/W-0/0 | -                               | R/W-0/0                             | R/W-0/0      | U-0                                | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|--------------------|---------------------------------|-------------------------------------|--------------|------------------------------------|------------------|------------------|-------------|--|--|--|

| SCANIE             |                                 | NVMIE                               | NCO1IE       | 0-0                                | CWG3IE           | CWG2IE           | CWG1IE      |  |  |  |

| bit 7              |                                 |                                     | NCOTE        |                                    | CWG3IE           | CWGZIE           | bit C       |  |  |  |

|                    |                                 |                                     |              |                                    |                  |                  |             |  |  |  |

| Legend:            |                                 |                                     |              |                                    |                  |                  |             |  |  |  |

| R = Reada          | = Readable bit W = Writable bit |                                     | bit          | U = Unimplemented bit, read as '0' |                  |                  |             |  |  |  |

| u = Bit is u       | inchanged                       | x = Bit is unk                      | nown         | -n/n = Value                       | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is       | set                             | '0' = Bit is cle                    | ared         | HS = Hardwa                        | are set          |                  |             |  |  |  |

| bit 7              | SCANIE: Sca                     | anner Interrupt                     | Enable bit   |                                    |                  |                  |             |  |  |  |

|                    |                                 | the scanner ir                      |              |                                    |                  |                  |             |  |  |  |

|                    | 0 = Disable                     | s the scanner i                     | nterrupt     |                                    |                  |                  |             |  |  |  |

| bit 6              |                                 | Interrupt Enab                      |              |                                    |                  |                  |             |  |  |  |

|                    |                                 | the CRC inter                       |              |                                    |                  |                  |             |  |  |  |

|                    |                                 | s the CRC inte                      | •            |                                    |                  |                  |             |  |  |  |

| bit 5              |                                 | Interrupt Enat                      |              | -1                                 |                  |                  |             |  |  |  |

|                    |                                 | sk complete int<br>errupt not enal  |              | a                                  |                  |                  |             |  |  |  |

| bit 4              | NCO1IE: NC                      | O Interrupt Ena                     | able bit     |                                    |                  |                  |             |  |  |  |

|                    |                                 | llover interrupt                    |              |                                    |                  |                  |             |  |  |  |

|                    |                                 | llover interrupt                    |              |                                    |                  |                  |             |  |  |  |

| bit 3              | •                               | ted: Read as '                      |              |                                    |                  |                  |             |  |  |  |

| bit 2              |                                 |                                     |              | nerator (CWG)                      | 3 Interrupt Enat | ole bit          |             |  |  |  |

|                    |                                 | nterrupt enable<br>nterrupt disable |              |                                    |                  |                  |             |  |  |  |

| bit 1              |                                 | -                                   |              | erator (CMG)                       | 2 Interrupt Enat | ale hit          |             |  |  |  |

|                    |                                 | nterrupt is ena                     |              |                                    |                  |                  |             |  |  |  |

|                    |                                 | nterrupt disable                    |              |                                    |                  |                  |             |  |  |  |

| bit 0              | CWG1IE: Co                      | mplementary V                       | Vaveform Ger | nerator (CWG)                      | 2 Interrupt Enat | ole bit          |             |  |  |  |

|                    |                                 | nterrupt is ena                     |              |                                    | -                |                  |             |  |  |  |

|                    | 0 = CWG1 i                      | nterrupt disable                    | ed           |                                    |                  |                  |             |  |  |  |

| Note:              | Bit PEIE of the IN              | TCON register                       | must be      |                                    |                  |                  |             |  |  |  |

|                    | set to enable a                 | ny peripheral                       | interrupt    |                                    |                  |                  |             |  |  |  |

|                    | controlled by regis             | ters PIE1-PIE8                      | 3.           |                                    |                  |                  |             |  |  |  |

# **REGISTER 7-9: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7**

#### 12.8.8 CURRENT-CONTROLLED DRIVE MODE CONTROL

The CCDPC and CCDNC registers (Register 12-30 and Register 12-31) control the Current-Controlled Drive mode for both the positive-going and negative-going drivers. When a CCDPC[y] or CCDNC[y] bit is set and the CCDEN bit of the CCDCON register is set, the Current-Controlled mode is enabled for the corresponding port pin. When the CCDPC[y] or CCDNC[y] bit is clear, the Current-Controlled mode for the corresponding port pin is disabled. If the CCDPC[y] or CCDNC[y] bit is set and the CCDEN bit is clear, operation of the port pin is undefined (see **Section 12.1.1** "**Current-Controlled Drive**" for current-controlled use precautions).

#### 12.8.9 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

# 18.12 Register Definitions: Comparator Control

### REGISTER 18-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

| R/W-0/0                                                            | R-0/0        | U-0                                                    | R/W-0/0                | U-0                               | U-0          | R/W-0/0         | R/W-0/0       |  |  |  |  |

|--------------------------------------------------------------------|--------------|--------------------------------------------------------|------------------------|-----------------------------------|--------------|-----------------|---------------|--|--|--|--|

| ON                                                                 | OUT          | —                                                      | POL                    |                                   | —            | HYS             | SYNC          |  |  |  |  |

| bit 7                                                              |              |                                                        | <u>.</u>               |                                   | ~            | -               | bit 0         |  |  |  |  |

|                                                                    |              |                                                        |                        |                                   |              |                 |               |  |  |  |  |

| Legend:                                                            |              |                                                        |                        |                                   |              |                 |               |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |              |                                                        |                        |                                   |              | id as '0'       |               |  |  |  |  |

| u = Bit is und                                                     | changed      | x = Bit is unk                                         | nown                   | -n/n = Value                      | at POR and B | OR/Value at all | other Resets  |  |  |  |  |

| '1' = Bit is se                                                    | t            | '0' = Bit is cle                                       | ared                   |                                   |              |                 |               |  |  |  |  |

| bit 7                                                              | ON: Compar   | ator Enable bit                                        |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    | •            | ON: Comparator Enable bit<br>1 = Comparator is enabled |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    |              |                                                        | and consumes           | s no active pow                   | /er          |                 |               |  |  |  |  |

| bit 6                                                              | OUT: Compa   | OUT: Comparator Output bit                             |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    |              | (inverted pola                                         | rity):                 |                                   |              |                 |               |  |  |  |  |

|                                                                    | 1 = CxVP < 0 | -                                                      |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    | 0 = CxVP > 0 | (non-inverted                                          | polarity) <sup>.</sup> |                                   |              |                 |               |  |  |  |  |

|                                                                    | 1 = CxVP > 0 |                                                        | polarity).             |                                   |              |                 |               |  |  |  |  |

|                                                                    | 0 = CxVP <   | CxVN                                                   |                        |                                   |              |                 |               |  |  |  |  |

| bit 5                                                              | Unimplemer   | nted: Read as                                          | '0'                    |                                   |              |                 |               |  |  |  |  |

| bit 4                                                              | •            | rator Output P                                         | •                      | bit                               |              |                 |               |  |  |  |  |

|                                                                    |              | tor output is in<br>tor output is no                   |                        |                                   |              |                 |               |  |  |  |  |

| bit 3-2                                                            | Unimplemer   | ted: Read as                                           | ʻ0'                    |                                   |              |                 |               |  |  |  |  |

| bit 1                                                              | HYS: Compa   | rator Hysteres                                         | is Enable bit          |                                   |              |                 |               |  |  |  |  |

|                                                                    |              | ator hysteresis                                        |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    | •            | ator hysteresis                                        |                        |                                   |              |                 |               |  |  |  |  |

| bit 0                                                              |              | parator Output                                         |                        |                                   |              |                 |               |  |  |  |  |

|                                                                    |              |                                                        |                        | ) pin is synchr<br>Timer1 clock s |              | ges on Timer1   | clock source. |  |  |  |  |

|                                                                    |              |                                                        | imer1 and I/O          |                                   |              |                 |               |  |  |  |  |

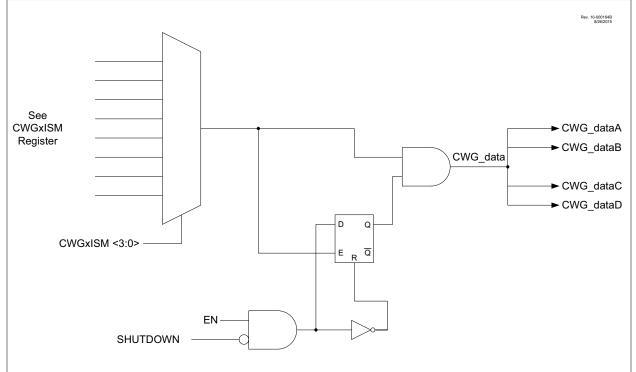

### 20.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 20.9 "CWG Steering Mode"**.

# 20.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWGxCLKCON register.

# 20.12 Configuring the CWG

The following steps illustrate how to properly configure the CWG.

- 1. Ensure that the TRIS control bits corresponding to the desired CWG pins for your application are set so that the pins are configured as inputs.

- 2. Clear the EN bit, if not already cleared.

- 3. Set desired mode of operation with the MODE bits.

- Set desired dead-band times, if applicable to mode, with the CWGxDBR and CWGxDBF registers.

- 5. Setup the following controls in the CWGxAS0 and CWGxAS1 registers.

- a. Select the desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using autoshutdown because start-up will be from a shutdown state).

- c. Set which pins will be affected by auto-shutdown with the CWGxAS1 register.

- d. Set the SHUTDOWN bit and clear the REN bit.

- 6. Select the desired input source using the CWGxISM register.

- 7. Configure the following controls.

- a. Select desired clock source using the CWGxCLKCON register.

- b. Select the desired output polarities using the CWGxCON1 register.

- c. Set the output enables for the desired outputs.

- 8. Set the EN bit.

- Clear TRIS control bits corresponding to the desired output pins to configure these pins as outputs.

- 10. If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit to start the CWG.

### 20.12.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the LSBD and LSAC bits of the CWGxAS0 register. LSBD<1:0> controls the CWGxB and D override levels and LSAC<1:0> controls the CWGxA and C override levels. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not affect the override level.

### 20.12.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the REN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 20-13 and Figure 20-14.

#### 20.12.2.1 Software Controlled Restart

When the REN bit of the CWGxAS0 register is cleared, the CWG must be restarted after an auto-shutdown event by software. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the SHUTDOWN bit will remain set. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

#### 20.12.2.2 Auto-Restart

When the REN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically. The SHUTDOWN bit will clear automatically when all shutdown sources go low. The overrides will remain in effect until the first rising edge event after the SHUTDOWN bit is cleared. The CWG will then resume operation.

# 23.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Result formatting

- Conversion Trigger Selection

- · ADC Acquisition Time

- ADC Precharge Time

- Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

### 23.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

Note: Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 23.1.2 CHANNEL SELECTION

There are several channel selections available:

- Eight PORTA pins (RA<7:0>)

- Eight PORTB pins (RB<7:0>)

- Eight PORTC pins (RC<7:0>)

- Eight PORTD pins (RD<7:0>, PIC16(L)F18875 only)

- Three PORTE pins (RE<2:0>, PIC16(L)F18875 only)

- Temperature Indicator

- · DAC output

- Fixed Voltage Reference (FVR)

- AVss (ground)

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 23.2 "ADC Operation"** for more information.

Note: It is recommended that when switching from an ADC channel of a higher voltage to a channel of a lower voltage, the software selects the Vss channel before switching to the channel of the lower voltage. If the ADC does not have a dedicated Vss input channel, the Vss selection (DAC1R<4:0> = b'00000') through the DAC output channel can be used. If the DAC is in use, a free input channel can be connected to Vss, and can be used in place of the DAC.

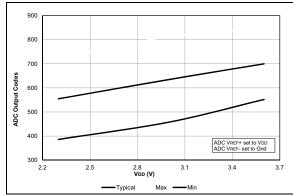

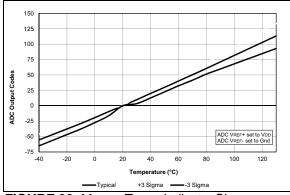

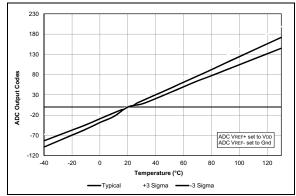

#### 23.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADREF register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

- FVR 1.024V

- FVR 2.048V

- FVR 4.096V

The ADNREF bit of the ADREF register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 16.0 "Fixed Voltage Reference (FVR)"** for more details on the Fixed Voltage Reference.

#### 23.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCLK register and the ADCS bit of the ADCON0 register. There are two possible clock sources:

- Fosc/(2\*(n+1)) (where n is from 0 to 63),

- FRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 23-2.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 37-13 for more information. Table 23-1 gives examples of appropriate ADC clock selections.

- Note 1: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

- 2: The internal control logic of the ADC runs off of the clock selected by the ADCS bit of ADCON0. What this can mean is when the ADCS bit of ADCON0 is set to 1 (ADC runs on FRC), there may be unexpected delays in operation when setting ADC control bits.

| REGISTER 26-4: | MDCARH: MODULATION HIGH CARRIER CONTROL REGISTER |  |

|----------------|--------------------------------------------------|--|

|                |                                                  |  |

| U-0                                        | U-0                                                                  | U-0                              | U-0            | R/W-x/u           | R/W-x/u          | R/W-x/u               | R/W-x/u      |

|--------------------------------------------|----------------------------------------------------------------------|----------------------------------|----------------|-------------------|------------------|-----------------------|--------------|

| —                                          | —                                                                    | _                                | _              |                   | MDCHS            | S<3:0> <sup>(1)</sup> |              |

| bit 7                                      |                                                                      |                                  |                |                   |                  |                       | bit 0        |

|                                            |                                                                      |                                  |                |                   |                  |                       |              |

| Legend:                                    |                                                                      |                                  |                |                   |                  |                       |              |

| R = Readable                               | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                  |                |                   |                  |                       |              |

| u = Bit is unchanged x = Bit is unknown -r |                                                                      |                                  |                | -n/n = Value a    | at POR and BO    | R/Value at all c      | other Resets |

| '1' = Bit is set '0' = Bit is cleared      |                                                                      |                                  |                |                   |                  |                       |              |

|                                            |                                                                      |                                  |                |                   |                  |                       |              |

| bit 7-4                                    | Unimplemen                                                           | ted: Read as 'o                  | )'             |                   |                  |                       |              |

| bit 3-0                                    | MDCHS<3:0>                                                           | Modulator Da                     | ta High Carrie | er Selection bits | <sub>5</sub> (1) |                       |              |

|                                            | 1111 = LC4                                                           |                                  | 5              |                   |                  |                       |              |

|                                            | 1110 = LC3                                                           | out                              |                |                   |                  |                       |              |

|                                            | 1101 = LC2                                                           | _out                             |                |                   |                  |                       |              |

|                                            | 1100 = LC1                                                           |                                  |                |                   |                  |                       |              |

|                                            | 1011 = NCC                                                           | •                                |                |                   |                  |                       |              |

|                                            | 1010 = PWN                                                           |                                  |                |                   |                  |                       |              |

|                                            | 1001 = PWN                                                           |                                  |                |                   |                  |                       |              |

|                                            |                                                                      | 25 output (PWN                   |                |                   |                  |                       |              |

|                                            |                                                                      | P4 output (PWN<br>P3 output (PWN | •              | • /               |                  |                       |              |

|                                            |                                                                      | 2 output (PWN                    |                |                   |                  |                       |              |

|                                            |                                                                      | 2 output (PWN)                   |                |                   |                  |                       |              |

|                                            |                                                                      | erence clock mo                  |                |                   |                  |                       |              |

|                                            | 0010 = HFIN                                                          |                                  |                | - /               |                  |                       |              |

|                                            | 0001 = Fos                                                           | C                                |                |                   |                  |                       |              |

|                                            | 0000 = Pin s                                                         | selected by MD                   | CARHPPS        |                   |                  |                       |              |

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### 29.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 29-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

#### FIGURE 29-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rev. 10-000200B<br>5/19/2016 |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| MODE                         | 0b01001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |

| TMRx_clk                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |