Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18856t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

001 = 2 000 = 1

| REGISTE        | R 6-6: OSCF     | RQ: HFINTO        | SC FREQUE     | NCY SELEC      | TION REGIS       | TER                      |              |

|----------------|-----------------|-------------------|---------------|----------------|------------------|--------------------------|--------------|

| U-0            | U-0             | U-0               | U-0           | U-0            | R/W-q/q          | R/W-q/q                  | R/W-q/q      |

|                |                 |                   |               |                | I                | HFFRQ<2:0> <sup>(1</sup> | )            |

| bit 7          |                 |                   |               |                |                  |                          | bit 0        |

|                |                 |                   |               |                |                  |                          |              |

| Legend:        |                 |                   |               |                |                  |                          |              |

| R = Reada      | ble bit         | W = Writable      | bit           | U = Unimpler   | nented bit, read | d as '0'                 |              |

| u = Bit is u   | nchanged        | x = Bit is unkr   | nown          | -n/n = Value a | at POR and BC    | R/Value at all o         | other Resets |

| '1' = Bit is s | set             | '0' = Bit is clea | ared          |                |                  |                          |              |

|                |                 |                   |               |                |                  |                          |              |

| bit 7-3        | Unimplemen      | ted: Read as '    | 0'            |                |                  |                          |              |

| bit 2-0        | HFFRQ<2:0>      | HFINTOSC F        | requency Sele | ection bits    |                  |                          |              |

|                | Nominal Freq    | (MHz) (NOSC       | = 110):       |                |                  |                          |              |

|                | 111 = Reserved  |                   |               |                |                  |                          |              |

|                | 110 <b>= 32</b> |                   |               |                |                  |                          |              |

|                | 101 = 16        |                   |               |                |                  |                          |              |

| 100 = 12       |                 |                   |               |                |                  |                          |              |

|                | 011 = 8         |                   |               |                |                  |                          |              |

|                | 010 = 4         |                   |               |                |                  |                          |              |

|                | _               |                   |               |                |                  |                          |              |

Note 1: When RSTOSC=110 (HFINTOSC 1 MHz), the HFFRQ bits will default to '010' upon Reset; when RSTOSC = 000 (HFINTOSC 32 MHz), the HFFRQ bits will default to '110' upon Reset.

| U-0                                                                                                                                   | U-0                                       | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0           | R/W-0/0    |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|-----------------|----------------|------------------|-------------------|------------|

| _                                                                                                                                     | —                                         | SMT2PWAIE                          | SMT2PRAIE       | SMT2IE         | SMT1PWAIE        | SMT1PRAIE         | SMT1IE     |

| bit 7                                                                                                                                 |                                           |                                    |                 |                |                  |                   | bit 0      |

|                                                                                                                                       |                                           |                                    |                 |                |                  |                   |            |

| Legend:                                                                                                                               |                                           |                                    |                 |                |                  |                   |            |

| R = Reada                                                                                                                             | ble bit                                   | W = Writable b                     | bit             | U = Unimpler   | mented bit, read | l as '0'          |            |

| u = Bit is u                                                                                                                          | nchanged                                  | x = Bit is unkn                    | own             | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is s                                                                                                                        | set                                       | '0' = Bit is clea                  | ared            | HS = Hardwa    | are set          |                   |            |

|                                                                                                                                       |                                           |                                    |                 |                |                  |                   |            |

| bit 7-6                                                                                                                               | Unimpleme                                 | nted: Read as '0                   | )'.             |                |                  |                   |            |

| bit 6                                                                                                                                 |                                           | E: SMT2 Pulse-V                    |                 |                | able bit         |                   |            |

|                                                                                                                                       |                                           | s the SMT acqui                    |                 |                |                  |                   |            |

|                                                                                                                                       |                                           | es the SMT acqu                    | •               |                | •,               |                   |            |

| bit 5                                                                                                                                 |                                           | : SMT2 Period A<br>s the SMT acqui |                 | •              | DIT              |                   |            |

|                                                                                                                                       |                                           | es the SMT acqui                   | •               |                |                  |                   |            |

| bit 4                                                                                                                                 | SMT2IE: SM                                | IT2 Overflow Inte                  | errupt Enable b | bit            |                  |                   |            |

|                                                                                                                                       | 1 = Enable                                | s the SMT overfl                   | low interrupt   |                |                  |                   |            |

|                                                                                                                                       | 0 = Disable                               | es the SMT overf                   | flow interrupt  |                |                  |                   |            |

| bit 2                                                                                                                                 |                                           | E: SMT1 Pulse-V                    |                 | •              | able bit         |                   |            |

|                                                                                                                                       | 1 = Enables the SMT acquisition interrupt |                                    |                 |                |                  |                   |            |

| <ul> <li>0 = Disables the SMT acquisition interrupt</li> <li>bit 1 SMT1PRAIE: SMT1 Period Acquisition Interrupt Enable bit</li> </ul> |                                           |                                    |                 |                |                  |                   |            |

| bit 1 SMT1PRAIE: SMT1 Period Acquisition Interrupt Enable bit<br>1 = Enables the SMT acquisition interrupt                            |                                           |                                    |                 |                |                  |                   |            |

|                                                                                                                                       |                                           | es the SMT acqu                    |                 |                |                  |                   |            |

| bit 0                                                                                                                                 | SMT1IE: SM                                | 1T1 Overflow Inte                  | errupt Enable b | bit            |                  |                   |            |

|                                                                                                                                       | 1 = Enable                                | s the SMT overfl                   | low interrupt   |                |                  |                   |            |

|                                                                                                                                       |                                           |                                    |                 |                |                  |                   |            |

## REGISTER 7-10: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE8.

0 = Disables the SMT overflow interrupt

| U-0                           | U-0                                                                                                           | R/W/HS-0/0        | R/W/HS-0/0       | R/W/HS-0/0      | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0     |

|-------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|------------------|------------------|----------------|

| _                             | _                                                                                                             | TMR6IF            | TMR5IF           | TMR4IF          | TMR3IF           | TMR2IF           | TMR1IF         |

| bit 7                         | •                                                                                                             |                   |                  |                 |                  | •                | bit 0          |

|                               |                                                                                                               |                   |                  |                 |                  |                  |                |

| Legend:                       |                                                                                                               |                   |                  |                 |                  |                  |                |

| R = Readable                  | bit                                                                                                           | W = Writable      |                  | •               | nented bit, read |                  |                |

| u = Bit is uncha              | anged                                                                                                         | x = Bit is unkr   | nown             | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets    |

| '1' = Bit is set              |                                                                                                               | '0' = Bit is clea | ared             | HS = Hardwa     | ire set          |                  |                |

| h ii <b>7</b> 0               | 11                                                                                                            | tada Daadaa (     | o.'              |                 |                  |                  |                |

| bit 7-6                       | •                                                                                                             | ted: Read as '    |                  |                 |                  |                  |                |

| bit 5                         |                                                                                                               | er6 Interrupt Fla | -                | 1.1 modo o TN   | /IR6 to PR6 mat  | ch occurred (m   | ust be cleared |

|                               | in softwa                                                                                                     |                   |                  | 1.1 moue, a m   | NRO LO FRO MAL   | choccurred (m    | usi de cleareu |

|                               |                                                                                                               | event has occ     | urred            |                 |                  |                  |                |

| bit 4                         | TRM5IF: Time                                                                                                  | er5 Overflow In   | iterrupt Flag bi | it              |                  |                  |                |

|                               |                                                                                                               | erflow occurred   | •                | ared in softwar | e)               |                  |                |

|                               |                                                                                                               | overflow occu     |                  |                 |                  |                  |                |

| bit 3                         |                                                                                                               | er4 Interrupt Fl  | -                | 1,1 mada a TN   | AD4 to DD4 mot   | ab accurred (m   | ust be sleared |

|                               | in softwa                                                                                                     |                   | eniowed, or in   | I. I mode, a In | /IR4 to PR4 mat  | ch occurred (m   | ust be cleared |

|                               |                                                                                                               | event has occ     | urred            |                 |                  |                  |                |

| bit 2                         | TRM3IF: Time                                                                                                  | er3 Overflow In   | iterrupt Flag bi | it              |                  |                  |                |

|                               |                                                                                                               | erflow occurred   | •                | ared in softwar | e)               |                  |                |

| 0 = No TMR3 overflow occurred |                                                                                                               |                   |                  |                 |                  |                  |                |

| bit 1                         |                                                                                                               |                   |                  |                 |                  |                  |                |

|                               | 1 = The TMR2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be clo<br>in software) |                   |                  |                 |                  |                  | ust be cleared |

|                               | 0 = No TMR2 event has occurred                                                                                |                   |                  |                 |                  |                  |                |

| bit 0                         | TRM1IF: Time                                                                                                  | er1 Overflow In   | iterrupt Flag bi | it              |                  |                  |                |

|                               |                                                                                                               | erflow occurred   | •                | ared in softwar | e)               |                  |                |

|                               | 0 = No TMR1                                                                                                   | overflow occu     | rred             |                 |                  |                  |                |

## REGISTER 7-15: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

## 12.7 Register Definitions: PORTB

## REGISTER 12-12: PORTB: PORTB REGISTER

| R/W-x/u                                                 | R/W-x/u | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------------------------------------------------------|---------|---------|-------------------------------------------------------|---------|---------|---------|---------|

| RB7                                                     | RB6     | RB5     | RB4                                                   | RB3     | RB2     | RB1     | RB0     |

| bit 7                                                   | •       |         |                                                       |         |         |         | bit 0   |

|                                                         |         |         |                                                       |         |         |         |         |

| Legend:                                                 |         |         |                                                       |         |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit |         |         |                                                       |         |         | as '0'  |         |

| u = Bit is unchanged x = Bit is unknown                 |         |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |         |

| '1' = Bit is set '0' = Bit is cleared                   |         |         |                                                       |         |         |         |         |

bit 7-0 **RB<7:0>**: PORTB I/O Value bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

## REGISTER 12-13: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TRISB<7:0>: PORTB Tri-State Control bit

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

## 12.10 PORTD Registers (PIC16(L)F18876 only)

## 12.10.1 DATA REGISTER CONTROL

PORTD is an 8-bit wide bidirectional port. The corresponding data direction register is TRISD (Register 12-33). Setting a TRISD bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12.4.9 shows how to initialize an I/O port.

Reading the PORTD register (Register 12-32) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATD).

The PORT data latch LATD (Register 12-34) holds the output port data, and contains the latest value of a LATD or PORTD write.

### 12.10.2 DIRECTION CONTROL

The TRISD register (Register 12-33) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

## 12.10.3 INPUT THRESHOLD CONTROL

The INLVLD register (Register 12-39) controls the input voltage threshold for each of the available PORTD input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTD register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

## 12.10.4 OPEN-DRAIN CONTROL

The ODCOND register (Register 12-37) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCOND bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCOND bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

**Note:** It is not necessary to set open-drain control when using the pin for I<sup>2</sup>C; the I<sup>2</sup>C module controls the pin and makes the pin open-drain.

## 12.10.5 SLEW RATE CONTROL

The SLRCOND register (Register 12-38) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCOND bit is set, the corresponding port pin drive is slew rate limited. When an SLRCOND bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

## 12.10.6 ANALOG CONTROL

The ANSELD register (Register 12-35) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no effect on digital output functions. A pin with TRIS clear and ANSELD set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELD bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

## 12.10.7 WEAK PULL-UP CONTROL

The WPUD register (Register 12-36) controls the individual weak pull-ups for each port pin.

|               |                 |             |       | Rema  | appable to  | Pins of PORTx |       |       |       |  |

|---------------|-----------------|-------------|-------|-------|-------------|---------------|-------|-------|-------|--|

| Output Signal | RxyPPS Register | PIC16F18856 |       |       | PIC16F18876 |               |       |       |       |  |

| Name          | Value           | PORTA       | PORTB | PORTC | PORTA       | PORTB         | PORTC | PORTD | PORTE |  |

| ADGRDG        | 0x25            | ٠           |       | •     | •           |               | •     |       |       |  |

| ADGRDA        | 0x24            | ٠           |       | •     | •           |               | •     |       |       |  |

| CWG3D         | 0x23            | ٠           |       | •     | •           |               |       | •     |       |  |

| CWG3C         | 0x22            | ٠           |       | •     | •           |               |       | •     |       |  |

| CWG3B         | 0x21            | ٠           |       | •     | •           |               |       |       | •     |  |

| CWG3A         | 0x20            |             | •     | •     |             | •             | •     |       |       |  |

| CWG2D         | 0x1F            |             | •     | •     |             | •             |       | •     |       |  |

| CWG2C         | 0x1E            |             | •     | •     |             | •             |       | •     |       |  |

| CWG2B         | 0x1D            |             | •     | •     |             | •             |       | •     |       |  |

| CWG2A         | 0x1C            |             | •     | •     |             | •             | •     |       |       |  |

| DSM           | 0x1B            | •           |       | •     | •           |               |       | •     |       |  |

| CLKR          | 0x1A            |             | •     | •     |             | •             | •     |       |       |  |

| NCO           | 0x19            | ٠           |       | •     | •           |               |       | •     |       |  |

| TMR0          | 0x18            |             | •     | •     |             | •             | •     |       |       |  |

| SDO2/SDA2     | 0x17            |             | •     | •     |             | •             |       | •     |       |  |

| SCK2/SCL2     | 0x16            |             | •     | •     |             | •             |       | •     |       |  |

| SD01/SDA1     | 0x15            |             | •     | •     |             | •             | •     |       |       |  |

| SCK1/SCL1     | 0x14            |             | •     | •     |             | •             | •     |       |       |  |

| C2OUT         | 0x13            | ٠           |       | •     | •           |               |       |       | •     |  |

| C10UT         | 0x12            | ٠           |       | •     | •           |               |       | •     |       |  |

| DT            | 0x11            |             | •     | •     |             | •             | ٠     |       |       |  |

| TX/CK         | 0x10            |             | •     | •     |             | •             | •     |       |       |  |

| PWM7OUT       | 0x0F            | ٠           |       | •     | •           |               | •     |       |       |  |

| PWM6OUT       | 0x0E            | ٠           |       | •     | •           |               |       | •     |       |  |

| CCP5          | 0x0D            | ٠           |       | •     | •           |               |       |       | •     |  |

| CCP4          | 0x0C            |             | •     | •     |             | •             |       | •     |       |  |

| CCP3          | 0x0B            |             | •     | •     |             | •             |       | •     |       |  |

| CCP2          | 0x0A            |             | •     | •     |             | •             | •     |       |       |  |

| CCP1          | 0x09            |             | •     | •     |             | •             | •     |       |       |  |

| CWG1D         | 0x08            |             | •     | •     |             | •             |       | •     |       |  |

| CWG1C         | 0x07            |             | •     | •     |             | •             |       | •     |       |  |

| CWG1B         | 0x06            |             | •     | •     |             | •             |       | •     |       |  |

| CWG1A         | 0x05            |             | •     | •     |             | •             | •     |       |       |  |

| CLC4OUT       | 0x04            |             | •     | •     |             | •             |       | •     |       |  |

| CLC3OUT       | 0x03            |             | •     | •     |             | •             |       | •     |       |  |

| CLC2OUT       | 0x02            | •           |       | •     | •           |               | •     |       |       |  |

| CLC10UT       | 0x01            | •           |       | •     | •           |               | •     |       |       |  |

## TABLE 13-3: PPS OUTPUT SIGNAL ROUTING OPTIONS

Note: When RxyPPS = 0x00, port pin Rxy output value is controlled by the respective LATxy bit.

## 23.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

### 23.2.5 EXTERNAL TRIGGER DURING SLEEP

If the external trigger is received during sleep while ADC clock source is set to the FRC, then the ADC module will perform the conversion and set the ADIF bit upon completion.

If an external trigger is received when the ADC clock source is something other than FRC, then the trigger will be recorded, but the conversion will not begin until the device exits Sleep.

## 23.2.6 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the ADGO bit is set by hardware.

The Auto-conversion Trigger source is selected with the ADACT<4:0> bits of the ADACT register.

## **REGISTER 24-6:** NCO1INCL: NCO1 INCREMENT REGISTER – LOW BYTE<sup>(1,2)</sup>

| R/W-0/0         R/W-0/0         R/W-0/0         R/W-0/0         R/W-0/0         R/W-0/0         R/W-1/1           NCO1INC<7:0>           bit 7         bit | Logondy |         |         |         |         |         |         | ]       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

|                                                                                                                                                            | bit 7   |         |         |         |         |         |         | bit 0   |

| R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-1/1                                                                                                    |         |         |         | NCO1IN  | NC<7:0> |         |         |         |

|                                                                                                                                                            | R/W-0/0 | R/W-1/1 |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1INC<7:0>: NCO1 Increment, Low Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: DDSINC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL; NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

## **REGISTER 24-7:** NCO1INCH: NCO1 INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCO1IN  | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1INC<15:8>: NCO1 Increment, High Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

## **REGISTER 24-8:** NCO1INCU: NCO1 INCREMENT REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | —   | —   | —   |         | NCO1IN  | C<19:16> |         |

| bit 7 |     |     |     |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, Upper Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

| R/W/HC-0/0        | R/W-0/0                                                                    | R/W-0/0            | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |

|-------------------|----------------------------------------------------------------------------|--------------------|----------------|-----------------|------------------|----------------|--------------|--|

| 0N <sup>(1)</sup> | CKPS<2:0>                                                                  |                    |                |                 | OUTP             | S<3:0>         |              |  |

| bit 7             |                                                                            |                    |                | ·               |                  |                | bit 0        |  |

| Legend:           |                                                                            |                    |                |                 |                  |                |              |  |

| R = Readable      | bit                                                                        | W = Writable       | bit            | U = Unimplen    | nented bit, read | d as '0'       |              |  |

| u = Bit is unch   | anged                                                                      | x = Bit is unknown |                | -               |                  | R/Value at all | other Resets |  |

| '1' = Bit is set  | -                                                                          | '0' = Bit is clea  | ared           | HC = Bit is cle | eared by hardv   | vare           |              |  |

| bit 7             | ON: Timerx                                                                 | On hit             |                |                 |                  |                |              |  |

|                   | 1 = Timerx                                                                 |                    |                |                 |                  |                |              |  |

|                   | -                                                                          | is off: all counte | rs and state m | achines are res | set              |                |              |  |

| bit 6-4           |                                                                            |                    |                |                 |                  |                |              |  |

|                   | CKPS<2:0>: Timer2-type Clock Prescale Select bits<br>111 = 1:128 Prescaler |                    |                |                 |                  |                |              |  |

|                   | 111 = 1.128  Prescaler $110 = 1.64  Prescaler$                             |                    |                |                 |                  |                |              |  |

|                   | 101 = 1:32 Prescaler                                                       |                    |                |                 |                  |                |              |  |

|                   | 100 = 1:16 Prescaler                                                       |                    |                |                 |                  |                |              |  |

|                   | 011 = 1:8 Prescaler                                                        |                    |                |                 |                  |                |              |  |

|                   | 010 = 1:4 Prescaler                                                        |                    |                |                 |                  |                |              |  |

|                   | 001 = 1:2 Prescaler                                                        |                    |                |                 |                  |                |              |  |

|                   | 000 = 1:1 P                                                                | rescaler           |                |                 |                  |                |              |  |

| bit 3-0           | OUTPS<3:0>: Timerx Output Postscaler Select bits                           |                    |                |                 |                  |                |              |  |

|                   | 1111 = 1:16 Postscaler                                                     |                    |                |                 |                  |                |              |  |

|                   | 1110 = 1:15 Postscaler                                                     |                    |                |                 |                  |                |              |  |

|                   | 1101 = 1:14 Postscaler                                                     |                    |                |                 |                  |                |              |  |

|                   | 1100 = 1:13 Postscaler                                                     |                    |                |                 |                  |                |              |  |

|                   | 1011 = 1:12  Postscaler                                                    |                    |                |                 |                  |                |              |  |

|                   | 1010 = 1:11  Postscaler                                                    |                    |                |                 |                  |                |              |  |

|                   | 1001 = 1:10 Postscaler<br>1000 = 1:9 Postscaler                            |                    |                |                 |                  |                |              |  |

|                   | 0100 = 1.9 Postscaler<br>0111 = 1.8 Postscaler                             |                    |                |                 |                  |                |              |  |

|                   | 0111 = 1.7  Postscaler                                                     |                    |                |                 |                  |                |              |  |

|                   | 0101 = 1.6 Postscaler                                                      |                    |                |                 |                  |                |              |  |

|                   | 0100 = 1.5 Postscaler                                                      |                    |                |                 |                  |                |              |  |

|                   | 0011 = 1:4 F                                                               |                    |                |                 |                  |                |              |  |

|                   | 0010 = 1:3 F                                                               | Postscaler         |                |                 |                  |                |              |  |

|                   | 0001 = 1:2 F                                                               | Postscaler         |                |                 |                  |                |              |  |

|                   | 0000 = 1:1 F                                                               | Postscaler         |                |                 |                  |                |              |  |

## REGISTER 29-2: TxCON: TIMER2/4/6 CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 29.5 "Operation Examples".

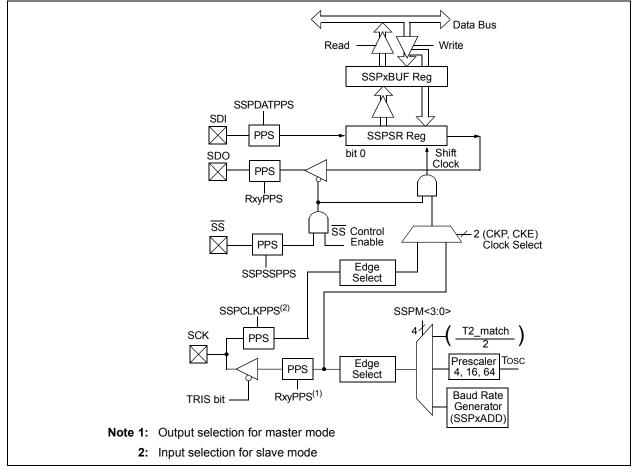

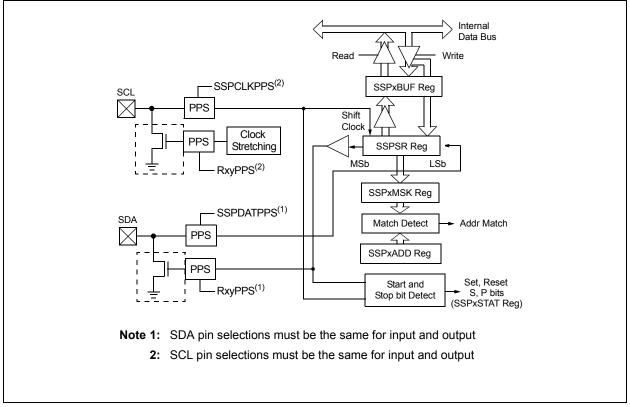

## 31.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULES

## 31.1 MSSP Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 31-1 is a block diagram of the SPI interface module.

DS40001824B-page 518

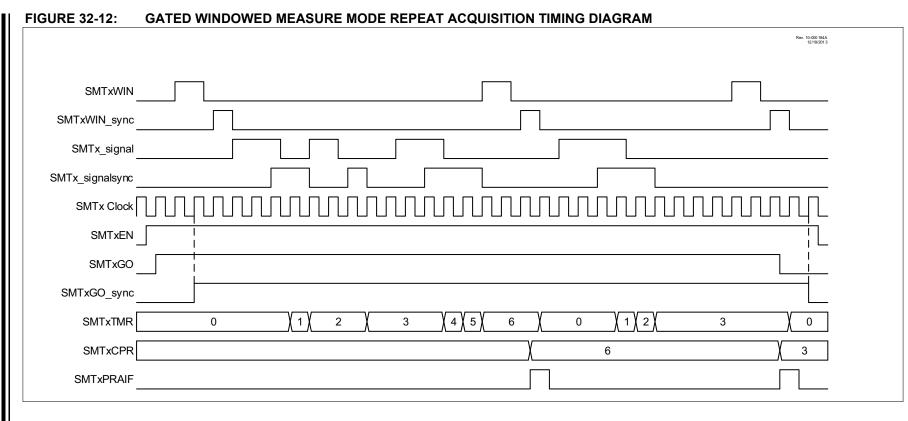

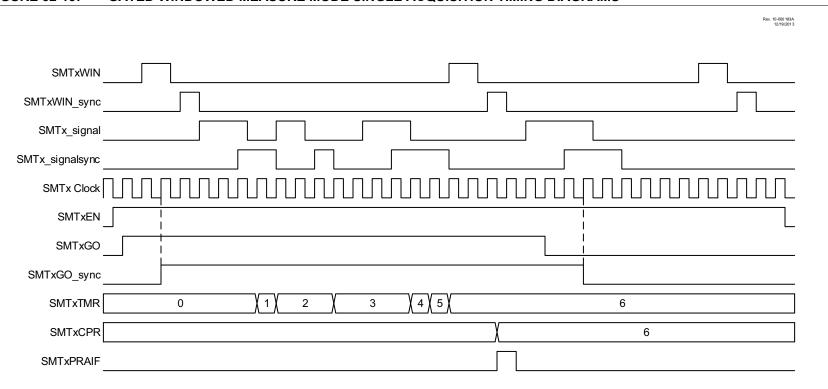

## FIGURE 32-13: GATED WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAMS

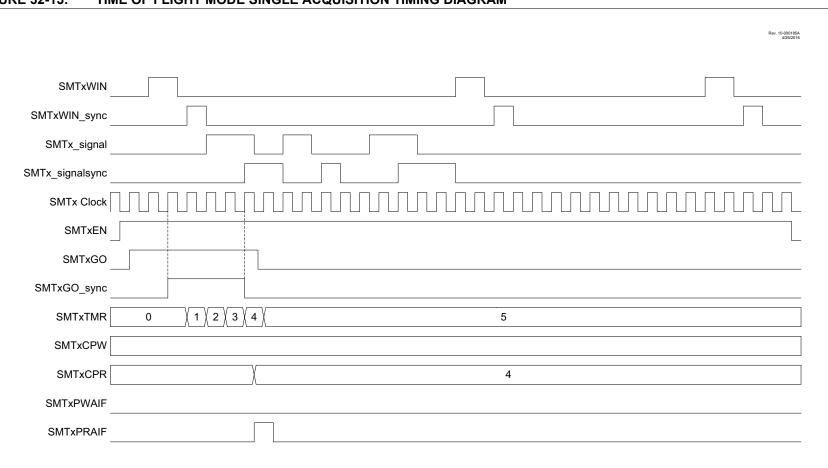

## 32.6.7 TIME OF FLIGHT MEASURE MODE

This mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMTx\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMTxCPR register and resetting the timer upon observing a rising edge on the SMTx\_signal input. In the event of two SMTWINx rising edges without an SMTx\_signal rising edge, it will update the SMTxCPW register with the current value of the timer and reset the timer value. See Figure 32-14 and Figure 32-15.

## FIGURE 32-15: TIME OF FLIGHT MODE SINGLE ACQUISITION TIMING DIAGRAM

## **REGISTER 32-7:** SMTxTMRL: SMT TIMER REGISTER – LOW BYTE

| 0 R/W-0/0          |

|--------------------|

|                    |

| bit 0              |

|                    |

|                    |

|                    |

| t all other Resets |

|                    |

| t;                 |

bit 7-0 SMTxTMR<7:0>: Significant bits of the SMT Counter – Low Byte

## REGISTER 32-8: SMTxTMRH: SMT TIMER REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMTxTM  | R<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxTMR<15:8>: Significant bits of the SMT Counter – High Byte

#### REGISTER 32-9: SMTxTMRU: SMT TIMER REGISTER – UPPER BYTE

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------|---------|---------|---------|----------|---------|---------|---------|

|             |         |         | SMTxTMF | R<23:16> |         |         |         |

| bit 7 bit 0 |         |         |         |          |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 SMTxTMR<23:16>: Significant bits of the SMT Counter – Upper Byte

#### 33.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RC1STA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

#### 33.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RC1STA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                                      | Start<br>bit / bit 0 / bit 1 / 5 / bit 7/8/ Stop bit / bit 0 / 5 / bit 7/8/ Stop bit / 5 / bit 7/8/ Stop bit / 5 / bit 7/8/ Stop bit                        |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg →<br>Rcv Buffer Reg.<br>RCIDL | Word 1 Word 2 Strength CREG RCREG                                                                                                                           |

| Read Rcv<br>Buffer Reg.<br>RCREG               |                                                                                                                                                             |

| RCIF<br>(Interrupt Flag)                       |                                                                                                                                                             |

| OERR bit                                       |                                                                                                                                                             |

| CREN                                           |                                                                                                                                                             |

|                                                | timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, sing the OERR (overrun) bit to be set. |

FIGURE 33-5:

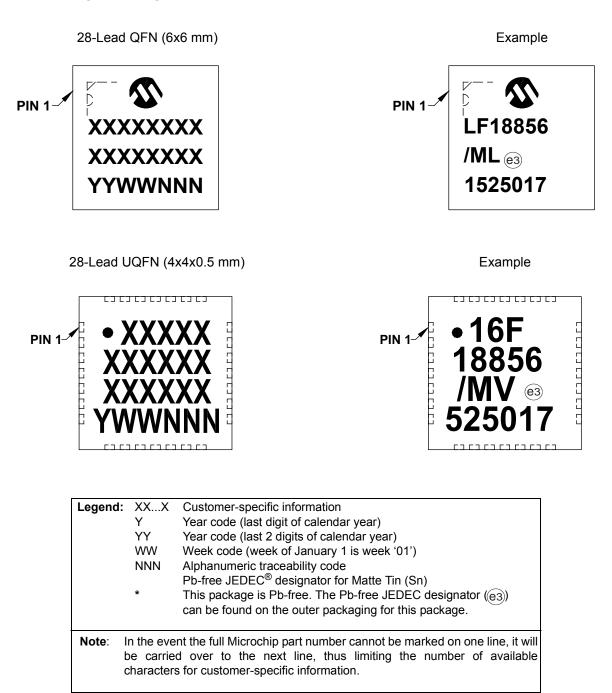

## 40.1 Package Marking Information (Continued)