Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

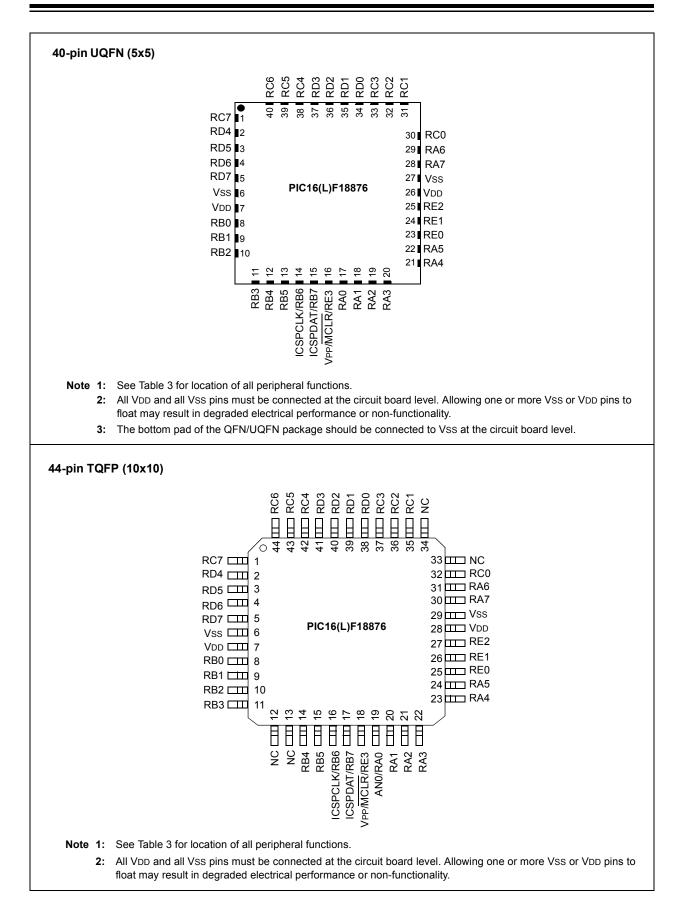

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18876-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PIC16(L)F18856 MEMORY MAP, BANK 30 TABLE 3-10:

|      | Bank 30 |

|------|---------|

| F0Ch | _       |

| F0Dh |         |

| F0Eh |         |

| F0Fh |         |

| F10h | RA0PPS  |

| F11h | RA1PPS  |

| F12h | RA2PPS  |

| F13h | RA3PPS  |

| F14h | RA4PPS  |

| F15h | RA5PPS  |

| F16h | RA6PPS  |

| F17h | RA7PPS  |

| F18h | RB0PPS  |

| F19h | RB1PPS  |

| F1Ah | RB2PPS  |

| F1Bh | RB3PPS  |

| F1Ch | RB4PPS  |

| F1Dh | RB5PPS  |

| F1Eh | RB6PPS  |

| F1Fh | RB7PPS  |

| F20h | RC0PPS  |

| F21h | RC1PPS  |

| F22h | RC2PPS  |

| F23h | RC3PPS  |

| F24h | RC4PPS  |

| F25h | RC5PPS  |

| F26h | RC6PPS  |

| F27h | RC7PPS  |

| F28h |         |

|      |         |

| F37h |         |

| F38h | ANSELA  |

| F39h | WPUA    |

| F3Ah | ODCONA  |

| F3Bh | SLRCONA |

| F3Ch | INLVLA  |

| F3Dh | IOCAP   |

| F3Eh | IOCAN   |

| F3Fh | IOCAF   |

|      | Bank 30 |

|------|---------|

| F40h | CCDNA   |

| F41h | CCDPA   |

| F42h | —       |

| F43h | ANSELB  |

| F44h | WPUB    |

| F45h | ODCONB  |

| F46h | SLRCONB |

| F47h | INLVLB  |

| F48h | IOCBP   |

| F49h | IOCBN   |

| F4Ah | IOCBF   |

| F4Bh | CCDNB   |

| F4Ch | CCDPB   |

| F4Dh | —       |

| F4Eh | ANSELC  |

| F4Fh | WPUC    |

| F50h | ODCONC  |

| F51h | SLRCONC |

| F52h | INLVLC  |

| F53h | IOCCP   |

| F54h | IOCCN   |

| F55h | IOCCF   |

| F56h | CCDNC   |

| F57h | CCDPC   |

| F58h | -       |

|      | _       |

| F64h |         |

| F65h | WPUE    |

| F66h | —       |

| F67h | —       |

| F68h | INLVLE  |

| F69h | IOCEP   |

| F6Ah | IOCEN   |

| F6Bh | IOCEF   |

| F6Ch | —       |

| F6Dh | _       |

| F6Eh | _       |

| F6Fh |         |

Legend:

= Unimplemented data memory locations, read as '0'.

| TABLE   | 3-13: SPE | ECIAL F                          | UNCTION | REGISTE     | R SUMMA    | RY BANKS (    | )-31 (CONTII       | NUED)         |             |         |                       |                              |

|---------|-----------|----------------------------------|---------|-------------|------------|---------------|--------------------|---------------|-------------|---------|-----------------------|------------------------------|

| Address | Name      | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7   | Bit 6       | Bit 5      | Bit 4         | Bit 3              | Bit 2         | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 1  |           |                                  |         |             |            |               |                    |               |             |         |                       |                              |

|         |           |                                  |         |             | CPU        | CORE REGISTER | S; see Table 3-2 f | for specifics |             |         |                       |                              |

| 08Ch    | ADRESL    |                                  |         |             |            | A             | DRESL<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |

| 08Dh    | ADRESH    |                                  |         | ADRESH<7:0> |            |               |                    |               |             |         |                       | 0000 0000                    |

| 08Eh    | ADPREVL   |                                  |         |             |            | A             | OPREVL<7:0>        |               |             |         | 0000 0000             | 0000 0000                    |

| 08Fh    | ADPREVH   |                                  |         |             |            | 0000 0000     | 0000 0000          |               |             |         |                       |                              |

| 090h    | ADACCL    |                                  |         | ADACCL<7:0> |            |               |                    |               |             |         |                       | uuuu uuuu                    |

| 091h    | ADACCH    |                                  |         | ADACCH<7:0> |            |               |                    |               |             |         |                       | uuuu uuuu                    |

| 092h    | -         | _                                |         |             |            | U             | nimplemented       |               |             |         | -                     | -                            |

| 093h    | ADCON0    |                                  | ADON    | ADCONT      | —          | ADCS          | —                  | ADFRM0        | _           | ADGO    | 00-0 -0-0             | 00-0 -0-0                    |

| 094h    | ADCON1    |                                  | ADPPOL  | ADIPEN      | ADGPOL     | _             | —                  | —             | _           | ADDSEN  | 0000                  | 0000                         |

| 095h    | ADCON2    |                                  | ADPSIS  |             | ADCRS<2:0> |               | ADACLR             |               | ADMD<2:0>   |         | 0000 0000             | 0000 0000                    |

| 096h    | ADCON3    |                                  | -       |             | ADCALC<2:0 | >             | ADSOI              |               | ADTMD<2:0>  |         | -000 0000             | -000 0000                    |

| 097h    | ADSTAT    |                                  | ADAOV   | ADUTHR      | ADLTHR     | ADMATH        | —                  |               | ADSTAT<2:0> |         | 0000 -000             | 0000 -000                    |

| 098h    | ADCLK     |                                  | _       | —           |            |               | ADO                | CCS<5:0>      |             |         | 00 0000               | 00 0000                      |

| 099h    | ADACT     |                                  | -       | —           | _          |               |                    | ADACT<4:0>    |             |         | 0 0000                | 0 0000                       |

| 09Ah    | ADREF     |                                  | _       | —           | _          | ADNREF        | —                  | —             | ADPRE       | EF<1:0> | 000                   | 000                          |

| 09Bh    | ADCAP     |                                  | _       | —           |            |               |                    | ADCAP<4:0>    |             |         | 0 0000                | 0 0000                       |

| 09Ch    | ADPRE     |                                  |         |             |            | ŀ             | ADPRE<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |

| 09Dh    | ADACQ     |                                  |         |             |            | ŀ             | ADACQ<7:0>         |               |             |         | 0000 0000             | 0000 0000                    |

| 09Eh    | ADPCH     |                                  | _       | —           |            |               | ADF                | PCH<5:0>      |             |         | 00 0000               | 00 0000                      |

| 09Fh    | —         | —                                |         |             |            | U             | nimplemented       |               |             |         | _                     | —                            |

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| Address                                                         | Name   | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7 | Bit 6 | Bit 5 | Bit 4         | Bit 3             | Bit 2         | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on all<br>other Resets |

|-----------------------------------------------------------------|--------|----------------------------------|-------|-------|-------|---------------|-------------------|---------------|-------|-------|-----------------------|------------------------------|

| Bank 30                                                         | )      |                                  |       |       |       |               |                   |               |       |       |                       |                              |

|                                                                 |        |                                  |       |       | CPU   | CORE REGISTER | RS; see Table 3-2 | for specifics |       |       |                       |                              |

| F0Ch     —     —     —     —       F0Fh     —     —     —     — |        |                                  |       |       |       |               |                   |               |       |       | _                     |                              |

| F10h                                                            | RA0PPS |                                  | —     | —     |       |               | RAC               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F11h                                                            | RA1PPS |                                  | _     | _     |       |               | 00 0000           | uu uuuu       |       |       |                       |                              |

| F12h                                                            | RA2PPS |                                  | —     | —     |       |               | 00 0000           | uu uuuu       |       |       |                       |                              |

| F13h                                                            | RA3PPS |                                  | —     | —     |       |               | 00 0000           | uu uuuu       |       |       |                       |                              |

| F14h                                                            | RA4PPS |                                  | —     | —     |       |               | 00 0000           | uu uuuu       |       |       |                       |                              |

| F15h                                                            | RA5PPS |                                  | —     | —     |       |               | RA5               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F16h                                                            | RA6PPS |                                  | —     | —     |       |               | RA6               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F17h                                                            | RA7PPS |                                  | —     | —     |       |               | RA7               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F18h                                                            | RB0PPS |                                  | —     | —     |       |               | RBC               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F19h                                                            | RB1PPS |                                  | —     | —     |       |               | RB1               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Ah                                                            | RB2PPS |                                  | —     | —     |       |               | RB2               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Bh                                                            | RB3PPS |                                  | —     | _     |       |               | RB3               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Ch                                                            | RB4PPS |                                  | —     | _     |       |               | RB4               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Dh                                                            | RB5PPS |                                  | —     | _     |       |               | RB5               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Eh                                                            | RB6PPS |                                  | —     | —     |       |               | RB6               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F1Fh                                                            | RB7PPS |                                  | —     | _     |       |               | RB7               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F20h                                                            | RC0PPS |                                  | —     | —     |       |               | RCC               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F21h                                                            | RC1PPS |                                  | —     | —     |       |               | RC1               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F22h                                                            | RC2PPS |                                  | —     | _     |       |               | RC2               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

| F23h                                                            | RC3PPS |                                  | —     | —     |       |               | RC3               | PPS<5:0>      |       |       | 00 0000               | uu uuuu                      |

# © 2016-2017 Microchip Technology Inc.

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

| TABLE 3          | 3-13: SPE   | CIA            | LF             | UNCTION       | REGISTE       |         | RY BANKS | 0-31 (CONTII  | NUED)   |         |         |                       |                              |

|------------------|-------------|----------------|----------------|---------------|---------------|---------|----------|---------------|---------|---------|---------|-----------------------|------------------------------|

| Address          | Name        | PIC16(L)F18856 | PIC16(L)F18876 | Bit 7         | Bit 6         | Bit 5   | Bit 4    | Bit 3         | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 30 (        | (Continued) |                |                |               |               |         |          |               |         |         |         |                       |                              |

| 550              |             | —              | Х              | SLRD7         | SLRD6         | SLRD5   | SLRD4    | SLRD3         | SLRD2   | SLRD1   | SLRD0   | 1111 1111             | 1111 1111                    |

| F5Ch             | SLRCOND     | х              | -              |               |               | •       | U        | Inimplemented |         |         |         |                       |                              |

|                  |             | —              | Х              | INLVLD7       | INLVLD6       | INLVLD5 | INLVLD4  | INLVLD3       | INLVLD2 | INLVLD1 | INLVLD0 | 1111 1111             | 1111 1111                    |

| F5Dh             | INLVLD      | х              | —              |               |               | 1       | U        | Inimplemented |         |         | •       |                       |                              |

| F5Eh<br><br>F60h | _           | -              | -              |               | Unimplemented |         |          |               |         |         |         |                       | _                            |

| 50.41            | 000010      | —              | Х              | CCDND7        | CCDND6        | CCDND5  | CCDND4   | CCDND3        | CCDND2  | CCDND1  | CCDND0  | 0000 0000             | 0000 0000                    |

| F61h             | CCDND       | —              |                | Unimplemented |               |         |          |               |         |         |         |                       |                              |

| 5001             | 00000       | —              | Х              | CCDPD7        | CCDPD6        | CCDPD5  | CCDPD4   | CCDPD3        | CCDPD2  | CCDPD1  | CCDPD0  | 0000 0000             | 0000 0000                    |

| F62h             | CCDPD       | х              | —              |               | Unimplemented |         |          |               |         |         |         |                       |                              |

| F63h             | _           | _              | -              |               |               |         | U        | Inimplemented |         |         |         | —                     | —                            |

| 50.41            |             | —              | Х              | —             | —             | —       | —        | -             | ANSE2   | ANSE1   | ANSE0   | 111                   | 111                          |

| F64h             | ANSELE      | х              | —              |               |               |         | U        | Inimplemented | •       |         |         |                       |                              |

| Forh             |             | —              | Х              | —             | —             | —       | —        | WPUE3         | WPUE2   | WPUE1   | WPUE0   | 0000                  | 0000                         |

| F65h             | WPUE        | х              | —              | -             | —             | —       | —        | WPUE3         | —       | _       | —       | 0                     | 0                            |

| Fach             | ODOONE      |                | Х              | _             | _             | —       | —        | -             | ODCE2   | ODCE1   | ODCE0   | 000                   | 000                          |

| F66h             | ODCONE      | х              | —              |               |               |         | U        | Inimplemented |         |         |         |                       |                              |

|                  |             | —              | Х              | -             | —             | —       | _        | -             | SLRE2   | SLRE1   | SLRE0   | 111                   | 111                          |

| F67h             | SLRCONE     | х              | -              |               |               |         | U        | Inimplemented |         |         |         |                       |                              |

| F68h             | INLVLE      | —              | Х              | _             | _             | —       | _        | INLVLE3       | INLVLE2 | INLVLE1 | INLVLE0 | 1111                  | 1111                         |

| 1 0011           |             | х              | —              | —             | _             | _       | _        | INLVLE3       | —       |         | _       | 1                     | 1                            |

| F69h             | IOCEP       |                |                | —             | _             | _       | _        | IOCEP3        | —       |         | _       | 0                     | 0                            |

| F6Ah             | IOCEN       |                |                | _             |               | _       | _        | IOCEN3        | _       |         | _       | 0                     | 0                            |

#### DECISTED SUMMARY RANKS 0.24 (CONTINUED) TION

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18855/75 devices only. Legend:

Note 1:

2: Unimplemented, read as '1'.

# TABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

|                     |       |                |                |       |                      |       |       |              | - /    |        |        |                       |                              |

|---------------------|-------|----------------|----------------|-------|----------------------|-------|-------|--------------|--------|--------|--------|-----------------------|------------------------------|

| Address             | Name  | PIC16(L)F18856 | PIC16(L)F18876 | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other Resets |

| Bank 30 (Continued) |       |                |                |       |                      |       |       |              |        |        |        |                       |                              |

| F6Bh                | IOCEF |                |                | _     | —                    | —     | _     | IOCEF3       | _      | _      | —      | 0                     | 0                            |

| F6Ch                | CCDNE | —              | х              | -     | CCDNE2 CCDNE1 CCDNE0 |       |       |              |        |        |        | 000                   | 000                          |

|                     |       | х              | —              |       |                      |       | Ur    | nimplemented |        |        |        |                       |                              |

| F6Dh                | CCDPE | —              | х              | _     | —                    | —     | -     | -            | CCDPE2 | CCDPE1 | CCDPE0 | 000                   | 000                          |

|                     |       | х              | —              |       |                      |       | Ur    | nimplemented |        |        |        |                       |                              |

| F6Eh                | _     | _              | -              |       | Unimplemented — —    |       |       |              |        |        |        |                       | _                            |

| F6Fh                | _     |                | -              |       |                      |       | Ur    | nimplemented |        |        |        |                       | _                            |

PIC16(L)F18856/76

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Register present on PIC16F18855/75 devices only.

2: Unimplemented, read as '1'.

| R/W/HS-0/0                                                           | R/W/HS-0/0                                                                                                                                       | U-0                                                                                     | U-0                                            | U-0            | U-0                                            | R/W/HS-0/0       | R/W/HS-0/0   |  |  |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|----------------|------------------------------------------------|------------------|--------------|--|--|--|--|

| OSFIF                                                                | CSWIF                                                                                                                                            | _                                                                                       | _                                              | _              | _                                              | ADTIF            | ADIF         |  |  |  |  |

| bit 7                                                                |                                                                                                                                                  |                                                                                         |                                                |                |                                                |                  | bit C        |  |  |  |  |

|                                                                      |                                                                                                                                                  |                                                                                         |                                                |                |                                                |                  |              |  |  |  |  |

| Legend:                                                              |                                                                                                                                                  |                                                                                         |                                                |                |                                                |                  |              |  |  |  |  |

| R = Readabl                                                          | e bit                                                                                                                                            | W = Writable bit U = Unimplemented bit, read as '0'                                     |                                                |                |                                                |                  |              |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/ |                                                                                                                                                  |                                                                                         |                                                |                |                                                | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is se                                                      | t                                                                                                                                                | '0' = Bit is clea                                                                       | ared                                           | HS = Hardwa    | ire set                                        |                  |              |  |  |  |  |

| bit 7                                                                |                                                                                                                                                  | ator Fail-Safe I                                                                        |                                                |                | oarod in coffwa                                | ro)              |              |  |  |  |  |

|                                                                      | <ul> <li>1 = Oscillator fail-safe interrupt has occurred (must be cleared in software)</li> <li>0 = No oscillator fail-safe interrupt</li> </ul> |                                                                                         |                                                |                |                                                |                  |              |  |  |  |  |

| bit 6                                                                | CSWIF: Clock Switch Complete Interrupt Flag bit                                                                                                  |                                                                                         |                                                |                |                                                |                  |              |  |  |  |  |

|                                                                      |                                                                                                                                                  | switch module<br>switch does no                                                         |                                                |                | tion (must be cl<br>tion                       | eared in softwa  | are)         |  |  |  |  |

| bit 5-2                                                              | Unimplemen                                                                                                                                       | ted: Read as '                                                                          | )'                                             |                |                                                |                  |              |  |  |  |  |

| bit 1                                                                | 1 = An A/D m                                                                                                                                     |                                                                                         | as beyond the                                  | configured thr | mpare Interrupt<br>eshold (must b<br>threshold |                  | ftware)      |  |  |  |  |

| bit 0                                                                | 1 = An A/D co                                                                                                                                    | -to-Digital Conv<br>onversion or co<br>onversion or co                                  | mplex operati                                  | on has comple  | ted (must be cl                                | eared in softwa  | ire)         |  |  |  |  |

| cc<br>its<br>El<br>U<br>ap                                           | terrupt flag bits a<br>ondition occurs, r<br>corresponding<br>nable bit, GIE, c<br>ser software<br>opropriate interru                            | egardless of the<br>enable bit or th<br>of the INTCON<br>should ensu<br>upt flag bits a | e state of<br>e Global<br>register.<br>ire the |                |                                                |                  |              |  |  |  |  |

# REGISTER 7-12: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

prior to enabling an interrupt.

# 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-14 for more details.

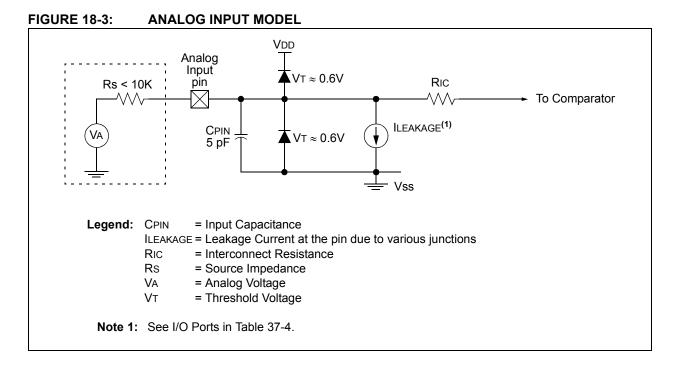

# 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

## REGISTER 18-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| —     | _   | _   | —   | —   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

|       |     |     |     |     |         |          |         |

# Legend:

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-2 <b>Unimplemented:</b> Read as 10 <sup>°</sup> | bit 7-2 | Unimplemented: Read as '0' |

|-------------------------------------------------------|---------|----------------------------|

|-------------------------------------------------------|---------|----------------------------|

bit 2-0 NCH<2:0>: Comparator Negative Input Channel Select bits

- 111 = CxVN connects to AVss

- 110 = CxVN connects to FVR Buffer 2

- 101 = CxVN unconnected

- 100 = CxVN unconnected

- 011 = CxVN connects to CxIN3- pin

- 010 = CxVN connects to CxIN2- pin

- 001 = CxVN connects to CxIN1- pin

- 000 = CxVN connects to CxIN0- pin

# REGISTER 18-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | —   | —   | —   |         | PCH<2:0> |         |

| bit 7 |     |     | •   | •   |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-2 Unimplemented: Read as '0'

bit 5-3 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP unconnected

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

| Name     | Bit 7                                        | Bit 6            | Bit 5           | Bit 4   | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|----------|----------------------------------------------|------------------|-----------------|---------|------------|----------|--------|--------|---------------------|

| PWM6CON  | PWM6EN                                       |                  | PWM6OUT         | PWM6POL | —          | -        | —      | —      | 287                 |

| PWM6DCH  |                                              |                  |                 | PWM6DC< | <9:2>      |          |        |        | 288                 |

| PWM6DCL  | PWM6D                                        | )C<1:0>          | _               | _       | _          | _        | _      | _      | 288                 |

| PWM7CON  | PWM7EN                                       |                  | PWM7OUT         | PWM7POL | _          | _        | _      | _      | 287                 |

| PWM7DCH  |                                              |                  |                 | PWM7DC< | <9:2>      |          |        |        | 288                 |

| PWM7DCL  | PWM7D                                        | )C<1:0>          | _               | _       | _          | _        | _      | _      | 288                 |

| T2CON    | ON                                           |                  | CKPS<2:0>       |         |            | OUTPS    | <3:0>  |        | 441                 |

| T4CON    | ON                                           |                  | CKPS<2:0>       |         |            | OUTPS    | <3:0>  |        | 441                 |

| T6CON    | ON                                           |                  | CKPS<2:0>       |         | OUTPS<3:0> |          |        |        |                     |

| T2TMR    | Holding Register for the 8-bit TMR2 Register |                  |                 |         |            |          |        |        |                     |

| T4TMR    | Holding Register for the 8-bit TMR4 Register |                  |                 |         |            |          |        |        |                     |

| T6TMR    | Holding Regi                                 | ster for the 8-l | oit TMR6 Regist | er      |            |          |        |        |                     |

| T2PR     | TMR2 Period                                  | Register         |                 |         |            |          |        |        |                     |

| T4PR     | TMR4 Period                                  | Register         |                 |         |            |          |        |        |                     |

| T6PR     | TMR6 Period                                  | Register         |                 |         |            |          |        |        |                     |

| RxyPPS   | —                                            | —                |                 |         | RxyPPS<    | 5:0>     |        |        | 250                 |

| CWG1ISM  | _                                            | _                | _               | —       |            | IS<3     | :0>    |        | 312                 |

| CWG2ISM  |                                              |                  |                 |         |            | IS<3     | :0>    |        | 312                 |

| CWG3ISM  |                                              |                  |                 |         |            | IS<3     | :0>    |        | 312                 |

| CLCxSELy | _                                            | _                |                 |         | LCxDyS<    | 5:0>     |        |        | 329                 |

| MDSRC    | —                                            |                  | _               |         | М          | DMS<4:0> |        |        | 399                 |

| MDCARH   | _                                            |                  | _               | _       |            | MDCHS    | s<3:0> |        | 400                 |

| MDCARL   | —                                            | _                | _               | —       |            | MDCLS    | <3:0>  |        | 401                 |

| TRISA    | TRISA7                                       | TRISA6           | TRISA5          | TRISA4  | TRISA3     | TRISA2   | TRISA1 | TRISA0 | 204                 |

| TRISC    | TRISC7                                       | TRISC6           | TRISC5          | TRISC4  | TRISC3     | TRISC2   | TRISC1 | TRISC0 | 220                 |

# TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWMx

Legend: - = Unimplemented locations, read as '0'. Shaded cells are not used by the PWMx module.

#### Register Bit 6 Name Bit 7 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 on Page 357 ADCON0 ADON ADCONT ADCS ADFRM0 ADGO ADCON1 ADPPOL ADIPEN ADGPOL ADDSEN \_ 358 ADCON2 ADPSIS ADCRS<2:0> ADACLR ADMD<2:0> 359 ADCON3 ADSOI ADTMD<2:0> ADCALC<2:0> 360 ADACT ADACT<4:0> \_ 359 ADACCH ADACCH 369 ADACCL ADACCL 369 ADPREVH ADPREVH 368 ADPREVL ADPREVL 369 ADRESH ADRESH 367 ADRESL ADRESL 367 ADSTAT ADAOV ADUTHR ADLTHR ADSTAT<2:0> ADMATH 361 ADCLK ADCCS<5:0> 362 ADREF ADNREF ADPREF<1:0> 362 ADCAP \_\_\_\_ ADCAP<4:0> 365 ADPRE ADPRE<7:0> 364 ADACQ ADACQ<7:0> 364 ADPCH ADPCH<5:0> \_ \_ 363 ADCNT ADCNT<7:0> 366 ADRPT ADRPT<7:0> 365 ADLTHL ADLTH<7:0> 371 ADLTHH ADLTH<15:8> 371 ADUTHL ADUTH<7:0> 372 ADUTHH ADUTH<15:8> 372 ADSTPTL ADSTPT<7:0> 370 ADSTPTH ADSTPT<15:8> 370 ADFLTRL ADFLTR<7:0> 366 ADFLTRH ADFLTR<15:8> 366 ADERRL ADERR<7:0> 371 ADERRH ADERR<15:8> 370 ANSELA ANSA7 ANSA6 ANSA5 ANSA4 ANSA3 ANSA2 ANSA1 ANSA0 205 ANSELB ANSB7 ANSB6 ANSB5 ANSB4 ANSB3 ANSB2 ANSB1 ANSB0 213 ANSELC ANSC7 ANSC6 ANSC5 ANSC4 ANSC3 ANSC2 ANSC1 ANSC0 221 ANSELD<sup>(1)</sup> ANSD7 ANSD6 ANSD5 ANSD4 ANSD3 ANSD2 ANSD1 ANSD0 228 ANSELE ANSE2<sup>(1)</sup> ANSE1<sup>(1)</sup> ANSE0<sup>(1)</sup> ANSE3 \_\_\_\_ 238 DAC1CON1 DAC1R<4:0> 389 \_\_\_\_ FVREN **FVRCON** CDAFVR<1:0> ADFVR<1:0> **FVRRDY** TSEN TSRNG 269 INTCON GIE PEIE INTEDG \_\_\_\_ \_\_\_\_ \_\_\_\_ 134 PIE1 OSFIE CSWIE ADTIE ADIE 136 PIR1 **OSFIF** CSWIF ADTIF ADIF 145 HFOR MFOR OSCSTAT EXTOR LFOR SOR ADOR PLLR 124 \_\_\_\_

# TABLE 23-6: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: -= unimplemented read as '0'. Shaded cells are not used for the ADC module.

**Note 1:** PIC16(L)F18876 only.

## 32.5.3 GO STATUS

Timer run status is determined by the TS bit of the SMTxSTAT register, and will be delayed in time by synchronizer delays in non-Counter modes.

# 32.6 Modes of Operation

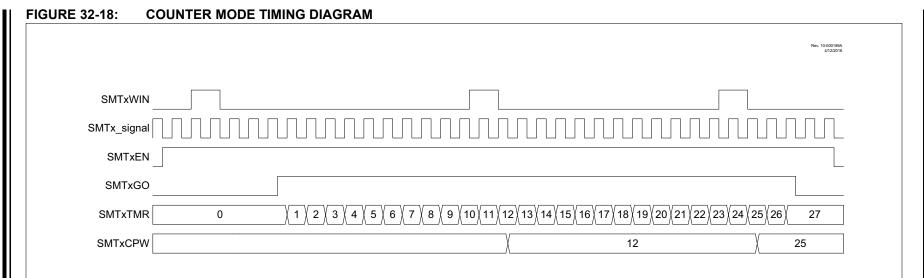

The modes of operation are summarized in Table 32-1. The following sections provide detailed descriptions, examples of how the modes can be used. Note that all waveforms assume WPOL/SPOL/CPOL = 0. When WPOL/SPOL/CPOL = 1, all SMTSIGx, SMTWINx and SMT clock signals will have a polarity opposite to that indicated. For all modes, the REPEAT bit controls whether the acquisition is repeated or single. When REPEAT = 0 (Single Acquisition mode), the timer will stop incrementing and the SMTxGO bit will be reset upon the completion of an acquisition. Otherwise, the timer will continue and allow for continued acquisitions to overwrite the previous ones until the timer is stopped in software.

# 32.6.1 TIMER MODE

Timer mode is the simplest mode of operation where the SMTxTMR is used as a 16/24-bit timer. No data acquisition takes place in this mode. The timer increments as long as the SMTxGO bit has been set by software. No SMT window or SMT signal events affect the SMTxGO bit. Everything is synchronized to the SMT clock source. When the timer experiences a period match (SMTxTMR = SMTxPR), SMTxTMR is reset and the period match interrupt trips. See Figure 32-3.

| MODE      | Mode of Operation                 | Synchronous<br>Operation | Reference                                    |

|-----------|-----------------------------------|--------------------------|----------------------------------------------|

| 0000      | Timer                             | Yes                      | Section 32.6.1 "Timer Mode"                  |

| 0001      | Gated Timer                       | Yes                      | Section 32.6.2 "Gated Timer Mode"            |

| 0010      | Period and Duty Cycle Acquisition | Yes                      | Section 32.6.3 "Period and Duty-Cycle Mode"  |

| 0011      | High and Low Time Measurement     | Yes                      | Section 32.6.4 "High and Low Measure Mode"   |

| 0100      | Windowed Measurement              | Yes                      | Section 32.6.5 "Windowed Measure Mode"       |

| 0101      | Gated Windowed Measurement        | Yes                      | Section 32.6.6 "Gated Window Measure Mode"   |

| 0110      | Time of Flight                    | Yes                      | Section 32.6.7 "Time of Flight Measure Mode" |

| 0111      | Capture                           | Yes                      | Section 32.6.8 "Capture Mode"                |

| 1000      | Counter                           | No                       | Section 32.6.9 "Counter Mode"                |

| 1001      | Gated Counter                     | No                       | Section 32.6.10 "Gated Counter Mode"         |

| 1010      | Windowed Counter                  | No                       | Section 32.6.11 "Windowed Counter Mode"      |

| 1011-1111 | Reserved                          | —                        | _                                            |

TABLE 32-1: MODES OF OPERATION

| R/W/HC-0/0              | R/W/HC-0/0                                                                                 | R/W/HC-0/0                                                                                                                            | U-0                                                                                             | U-0                  | R-0/0            | R-0/0            | R-0/0        |

|-------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------------|

| CPRUP                   | CPWUP                                                                                      | RST                                                                                                                                   | —                                                                                               | _                    | TS               | WS               | AS           |

| bit 7                   |                                                                                            |                                                                                                                                       |                                                                                                 |                      |                  |                  | bit 0        |

|                         |                                                                                            |                                                                                                                                       |                                                                                                 |                      |                  |                  |              |

| Legend:                 |                                                                                            |                                                                                                                                       |                                                                                                 |                      |                  |                  |              |

| HC = Bit is clea        | -                                                                                          | are                                                                                                                                   |                                                                                                 | HS = Bit is se       | et by hardware   |                  |              |

| R = Readable            | bit                                                                                        | W = Writable                                                                                                                          | bit                                                                                             | U = Unimpler         | mented bit, read | 1 as '0'         |              |

| u = Bit is uncha        | anged                                                                                      | x = Bit is unkr                                                                                                                       | iown                                                                                            | -n/n = Value a       | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set        |                                                                                            | '0' = Bit is clea                                                                                                                     | ared                                                                                            | q = Value dep        | pends on condit  | tion             |              |

| bit 7<br>bit 6<br>bit 5 | 1 = Request to<br>0 = SMTxPR><br>CPWUP: SM<br>1 = Request to<br>0 = SMTxCPV<br>RST: SMT Ma | Manual Perio<br>update to SMT<br>registers upda<br>Manual Pulse<br>update to SMT<br>Wregisters upo<br>anual Timer Re<br>Reset to SMTx | CPRx registers<br>ate is complete<br>Width Buffer<br>CPW register<br>late is complet<br>set bit | e<br>Update bit<br>s |                  |                  |              |

|                         |                                                                                            | R registers upd                                                                                                                       | •                                                                                               | e                    |                  |                  |              |

| bit 4-3                 | -                                                                                          | ted: Read as '                                                                                                                        |                                                                                                 |                      |                  |                  |              |

| bit 2                   | 1 = SMT time                                                                               | Value Status b<br>r is incrementir<br>r is not increme                                                                                | ng                                                                                              |                      |                  |                  |              |

| bit 1                   | <b>WS</b> : SMTxWI<br>1 = SMT wind<br>0 = SMT wind                                         |                                                                                                                                       | bit                                                                                             |                      |                  |                  |              |

| bit 0                   | 1 = SMT acqu                                                                               | nal Value Statu<br>uisition is in pro<br>uisition is not in                                                                           | gress                                                                                           |                      |                  |                  |              |

# REGISTER 32-3: SMTxSTAT: SMT STATUS REGISTER

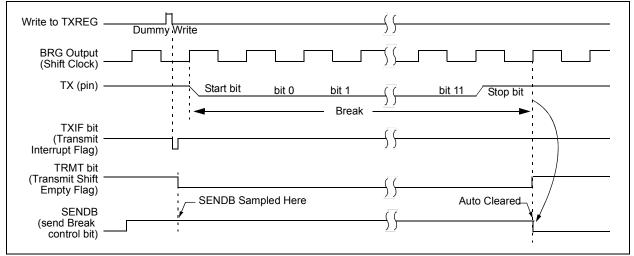

# 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RC1STA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUD1CON register before placing the EUSART in Sleep mode.

# TABLE 37-11:RESET, WDT, OSCILLATOR START-UP TIMER, POWER-UP TIMER, BROWN-OUT<br/>RESET AND LOW-POWER BROWN-OUT RESET SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |         |                                                   |                      |                      |                      |             |                                                                     |  |  |

|---------------------------------------------------------|---------|---------------------------------------------------|----------------------|----------------------|----------------------|-------------|---------------------------------------------------------------------|--|--|

| Param.<br>No.                                           | Sym.    | Characteristic                                    | Min.                 | Тур†                 | Max.                 | Units       | Conditions                                                          |  |  |

| RST01*                                                  | TMCLR   | MCLR Pulse Width Low to ensure Reset              | 2                    | _                    | _                    | μS          |                                                                     |  |  |

| RST02*                                                  | Tioz    | I/O high-impedance from Reset detection           | _                    | _                    | 2                    | μS          |                                                                     |  |  |

| RST03                                                   | TWDT    | Watchdog Timer Time-out Period                    | —                    | 16                   |                      | ms          | 16 ms Nominal Reset Time                                            |  |  |

| RST04*                                                  | TPWRT   | Power-up Timer Period                             | _                    | 65                   |                      | ms          |                                                                     |  |  |

| RST05                                                   | Tost    | Oscillator Start-up Timer Period <sup>(1,2)</sup> | _                    | 1024                 |                      | Tosc        |                                                                     |  |  |

| RST06                                                   | VBOR    | Brown-out Reset Voltage <sup>(4)</sup>            | 2.55<br>2.30<br>1.80 | 2.70<br>2.45<br>1.90 | 2.85<br>2.60<br>2.10 | V<br>V<br>V | BORV = 0<br>BORV = 1 (PIC16F18856/76)<br>BORV = 1 (PIC16LF18856/76) |  |  |

| RST07                                                   | VBORHYS | Brown-out Reset Hysteresis                        | _                    | 40                   | _                    | mV          |                                                                     |  |  |

| RST08                                                   | TBORDC  | Brown-out Reset Response Time                     | _                    | 3                    | _                    | μS          |                                                                     |  |  |

| RST09                                                   | Vlpbor  | Low-Power Brown-out Reset Voltage                 | 2.3                  | 2.45                 | 2.7                  | V           |                                                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

# TABLE 37-12: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>:

| •             | Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |                                                   |        |      |        |           |                             |  |  |  |

|---------------|-------------------------------------------------------------------------|---------------------------------------------------|--------|------|--------|-----------|-----------------------------|--|--|--|

| Param.<br>No. | Sym.                                                                    | Characteristic                                    | Min.   | Тур† | Max.   | Unit<br>s | Conditions                  |  |  |  |

| AD01          | NR                                                                      | Resolution                                        | —      | _    | 10     | bit       |                             |  |  |  |

| AD02          | Eĩ∟                                                                     | Integral Error                                    | —      | ±0.1 | ±1.0   | LSb       | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD03          | Edl                                                                     | Differential Error                                | _      | ±0.1 | ±1.0   | LSb       | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD04          | EOFF                                                                    | Offset Error                                      | _      | 0.5  | 2.0    | LSb       | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD05          | Egn                                                                     | Gain Error                                        | —      | ±0.2 | ±1.0   | LSb       | ADCREF+ = 3.0V, ADCREF-= 0V |  |  |  |

| AD06          | VADREF                                                                  | ADC Reference Voltage<br>(ADREF+ - ADREF-)        | 1.8    |      | Vdd    | V         |                             |  |  |  |

| AD07          | VAIN                                                                    | Full-Scale Range                                  | ADREF- | _    | ADREF+ | V         |                             |  |  |  |

| AD08          | Zain                                                                    | Recommended Impedance of<br>Analog Voltage Source | _      | 10   | _      | kΩ        |                             |  |  |  |

| AD09          | Rvref                                                                   | ADC Voltage Reference Ladder<br>Impedance         |        | 50   | _      | kΩ        | Note 3                      |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error is the sum of the offset, gain and integral non-linearity (INL) errors.

2: The ADC conversion result never decreases with an increase in the input and has no missing codes.

3: This is the impedance seen by the VREF pads when the external reference pads are selected.

Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

# TABLE 37-25: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                |                             |              |            |      |                                             |                                             |  |

|---------------------------------------------------------|----------------|-----------------------------|--------------|------------|------|---------------------------------------------|---------------------------------------------|--|

| Param.<br>No.                                           | Symbol         | Characteristic              |              | Min.       | Max. | Units                                       | Conditions                                  |  |

| SP100*                                                  | Тнідн          | Clock high time             | 100 kHz mode | 4.0        | —    | μS                                          | Device must operate at a minimum of 1.5 MHz |  |

|                                                         |                |                             | 400 kHz mode | 0.6        | _    | μS                                          | Device must operate at a minimum of 10 MHz  |  |

|                                                         |                |                             | SSP module   | 1.5Tcy     |      |                                             |                                             |  |

| SP101* TLOW                                             | Clock low time | 100 kHz mode                | 4.7          | —          | μS   | Device must operate at a minimum of 1.5 MHz |                                             |  |

|                                                         |                |                             | 400 kHz mode | 1.3        | —    | μS                                          | Device must operate at a minimum of 10 MHz  |  |

|                                                         |                |                             | SSP module   | 1.5Tcy     |      |                                             |                                             |  |

| SP102* TR                                               | TR             | SDA and SCL rise time       | 100 kHz mode | —          | 1000 | ns                                          |                                             |  |

|                                                         |                |                             | 400 kHz mode | 20 + 0.1CB | 300  | ns                                          | CB is specified to be from 10-400 pF        |  |

| SP103*                                                  | TF             | SDA and SCL fall time       | 100 kHz mode | —          | 250  | ns                                          |                                             |  |

|                                                         |                |                             | 400 kHz mode | 20 + 0.1CB | 250  | ns                                          | CB is specified to be from 10-400 pF        |  |

| SP106*                                                  | THD:DAT        | Data input hold time        | 100 kHz mode | 0          |      | ns                                          |                                             |  |

|                                                         |                |                             | 400 kHz mode | 0          | 0.9  | μs                                          |                                             |  |

| SP107*                                                  | TSU:DAT        | U:DAT Data input setup time | 100 kHz mode | 250        |      | ns                                          | (Note 2)                                    |  |

|                                                         |                |                             | 400 kHz mode | 100        |      | ns                                          |                                             |  |

| SP109*                                                  | ΤΑΑ            | Output valid from           | 100 kHz mode | —          | 3500 | ns                                          | (Note 1)                                    |  |

|                                                         |                | clock                       | 400 kHz mode | —          | —    | ns                                          |                                             |  |

| SP110*                                                  | TBUF           | Bus free time               | 100 kHz mode | 4.7        | —    | μS                                          | Time the bus must be free                   |  |

|                                                         |                |                             | 400 kHz mode | 1.3        | —    | μS                                          | before a new transmission can start         |  |

| SP111                                                   | Св             | Bus capacitive loading      |              | —          | 400  | pF                                          |                                             |  |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

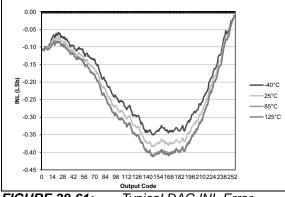

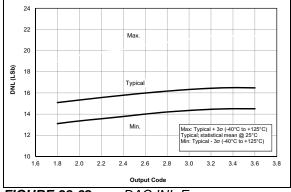

**FIGURE 38-62:** DAC INL Error, VDD = 3.0V, PIC16LF18856/76 Only.

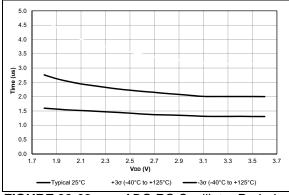

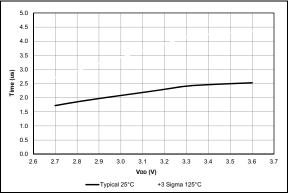

FIGURE 38-63: ADC RC Oscillator Period, PIC16LF18856/76 Only.

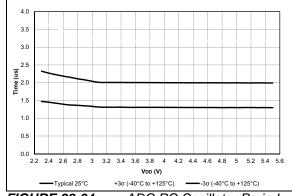

FIGURE 38-64: ADC RC Oscillator Period, PIC16F18856/76 Only.

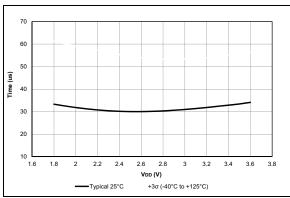

FIGURE 38-65: Bandgap Ready Time, PIC16LF18856/76 Only.

FIGURE 38-66: BOR Response Time, PIC16LF18856/76 Only.

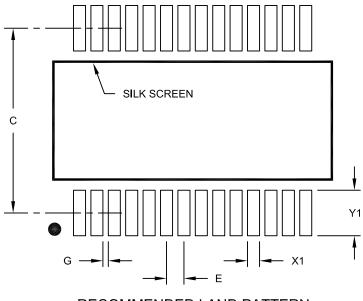

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units  |          |      |      |  |

|--------------------------|--------|----------|------|------|--|

| Dimension                | Limits | MIN      | NOM  | MAX  |  |

| Contact Pitch            | E      | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С      |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1     |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1     |          |      | 1.75 |  |

| Distance Between Pads    | G      | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A