Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18876-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE   | 3-13: SPE                                       | CIAL F                           | UNCTION | I REGISTE | R SUMMA | RY BANKS ( | )-31 (CONTI                   | NUED)     |           |           |                       |                           |  |

|---------|-------------------------------------------------|----------------------------------|---------|-----------|---------|------------|-------------------------------|-----------|-----------|-----------|-----------------------|---------------------------|--|

| Address | Name                                            | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7   | Bit 6     | Bit 5   | Bit 4      | Bit 3                         | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR, BOR | Value on all other Resets |  |

| Bank 8  | 3ank 8                                          |                                  |         |           |         |            |                               |           |           |           |                       |                           |  |

|         | CPU CORE REGISTERS; see Table 3-2 for specifics |                                  |         |           |         |            |                               |           |           |           |                       |                           |  |

| 40Ch    | SCANLADRL                                       |                                  |         |           |         |            | LADR<7:0>                     |           |           |           | 0000 0000             | 0000 0000                 |  |

| 40Dh    | SCANLADRH                                       |                                  |         |           |         |            | LADR<15:8>                    |           |           |           | 0000 0000             | 0000 0000                 |  |

| 40Eh    | SCANHADRL                                       |                                  |         |           |         |            | HADR<7:0>                     |           |           |           | 1111 1111             | 1111 1111                 |  |

| 40Fh    | SCANHADRH                                       |                                  |         |           |         | ł          | HADR<15:8>                    |           |           |           | 1111 1111             | 1111 1111                 |  |

| 410h    | SCANCON0                                        |                                  | EN      | SCANGO    | BUSY    | INVALID    | INTM                          | —         | MOD       | E<1:0>    | 0000 0-00             | 0000 0-00                 |  |

| 411h    | SCANTRIG                                        |                                  | —       | —         | —       | _          |                               | TSEL<     | <3:0>     |           | 0000                  | 0000                      |  |

| 412h    | -                                               | —                                |         |           |         | U          | nimplemented                  |           |           |           | _                     | —                         |  |

| 413h    | -                                               | —                                |         |           |         | U          | nimplemented                  |           |           |           | _                     | —                         |  |

| 414h    | -                                               | —                                |         |           |         | U          | nimplemented                  |           |           |           | -                     | —                         |  |

| 415h    | -                                               | —                                |         |           |         | U          | nimplemented                  |           |           |           | _                     | —                         |  |

| 416h    | CRCDATL                                         |                                  |         |           |         |            | DATA<7:0>                     |           |           |           | XXXX XXXX             | xxxx xxxx                 |  |

| 417h    | CRCDATH                                         |                                  |         |           |         |            | DATA<15:8>                    |           |           |           | XXXX XXXX             | XXXX XXXX                 |  |

| 418h    | CRCACCL                                         |                                  |         |           |         |            | ACC<7:0>                      |           |           |           | 0000 0000             | 0000 0000                 |  |

| 419h    | CRCACCH                                         |                                  |         |           |         |            | ACC<15:8>                     |           |           |           | 0000 0000             | 0000 0000                 |  |

| 41Ah    | CRCSHIFTL                                       | L SHIFT<7:0>                     |         |           |         |            |                               | 0000 0000 | 0000 0000 |           |                       |                           |  |

| 41Bh    | CRCSHIFTH                                       | IFTH SHIFT<15:8>                 |         |           |         |            |                               |           | 0000 0000 | 0000 0000 |                       |                           |  |

| 41Ch    | CRCXORL                                         |                                  |         |           |         | X<7:1>     |                               |           |           | —         | xxxx xxx-             | xxxx xxx-                 |  |

| 41Dh    | CRCXORH                                         |                                  |         |           |         |            | X<15:8>                       |           |           | XXXX XXXX | xxxx xxxx             |                           |  |

| 41Eh    | CRCCON0                                         |                                  | EN      | CRCGO     | BUSY    | ACCM       | —                             | —         | SHIFTM    | FULL      | 000000                | 000000                    |  |

| 41Fh    | CRCCON1                                         |                                  |         | DLE       | EN<3:0> | ·          | PLEN<3:0> 0000 0000 0000 0000 |           |           |           |                       |                           |  |

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| TABLE                  | ABLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |                                  |          |          |          |                      |              |          |              |          |                       |                              |  |

|------------------------|---------------------------------------------------------------------|----------------------------------|----------|----------|----------|----------------------|--------------|----------|--------------|----------|-----------------------|------------------------------|--|

| Address                | Name                                                                | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7    | Bit 6    | Bit 5    | Bit 4                | Bit 3        | Bit 2    | Bit 1        | Bit 0    | Value on:<br>POR, BOR | Value on all<br>other Resets |  |

| Bank 2                 | Bank 28                                                             |                                  |          |          |          |                      |              |          |              |          |                       |                              |  |

|                        | CPU CORE REGISTERS; see Table 3-2 for specifics                     |                                  |          |          |          |                      |              |          |              |          |                       |                              |  |

| E0Ch — — Unimplemented |                                                                     |                                  |          |          |          |                      |              |          |              |          |                       | _                            |  |

| E0Dh                   | —                                                                   | -                                |          |          |          | U                    | nimplemented |          |              |          | -                     | _                            |  |

| E0Eh                   | —                                                                   | -                                |          |          |          | U                    | nimplemented |          |              |          | -                     | _                            |  |

| E0Fh                   | CLCDATA                                                             |                                  | —        | —        | _        | _                    | MLC4OUT      | MLC3OUT  | MLC2OUT      | MLC10UT  | 0000                  | 0000                         |  |

| E10h                   | CLC1CON                                                             |                                  | LC1EN    | —        | LC10UT   | LC1INTP              | LC1INTN      |          | LC1MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |  |

| E11h                   | CLC1POL                                                             |                                  | LC1POL   | —        |          |                      | LC1G4POL     | LC1G3POL | LC1G2POL     | LC1G1POL | 0 xxxx                | 0 uuuu                       |  |

| E12h                   | CLC1SEL0                                                            |                                  | —        | —        |          |                      | LC1          | D1S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E13h                   | CLC1SEL1                                                            |                                  | —        | —        |          | LC1D2S<5:0>          |              |          |              |          |                       | uu uuuu                      |  |

| E14h                   | CLC1SEL2                                                            |                                  | —        | —        |          |                      | LC1          | D3S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E15h                   | CLC1SEL3                                                            |                                  | —        | —        |          |                      | LC1          | D4S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E16h                   | CLC1GLS0                                                            |                                  | LC1G1D4T | LC1G1D4N | LC1G1D3T | LC1G1D3N             | LC1G1D2T     | LC1G1D2N | LC1G1D1T     | LC1G1D1N | xxxx xxxx             | uuuu uuuu                    |  |

| E17h                   | CLC1GLS1                                                            |                                  | LC1G2D4T | LC1G2D4N | LC1G2D3T | LC1G2D3N             | LC1G2D2T     | LC1G2D2N | LC1G2D1T     | LC1G2D1N | xxxx xxxx             | uuuu uuuu                    |  |

| E18h                   | CLC1GLS2                                                            |                                  | LC1G3D4T | LC1G3D4N | LC1G3D3T | LC1G3D3N             | LC1G3D2T     | LC1G3D2N | LC1G3D1T     | LC1G3D1N | xxxx xxxx             | uuuu uuuu                    |  |

| E19h                   | CLC1GLS3                                                            |                                  | LC1G4D4T | LC1G4D4N | LC1G4D3T | LC1G4D3N             | LC1G4D2T     | LC1G4D2N | LC1G4D1T     | LC1G4D1N | xxxx xxxx             | uuuu uuuu                    |  |

| E1Ah                   | CLC2CON                                                             |                                  | LC2EN    | —        | LC2OUT   | LC2INTP              | LC2INTN      |          | LC2MODE<2:0> |          | 0-x0 0000             | 0-x0 0000                    |  |

| E1Bh                   | CLC2POL                                                             |                                  | LC2POL   | —        | —        | —                    | LC2G4POL     | LC2G3POL | LC2G2POL     | LC2G1POL | 0 xxxx                | 0 uuuu                       |  |

| E1Ch                   | CLC2SEL0                                                            |                                  | —        | —        |          |                      | LC2          | D1S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E1Dh                   | CLC2SEL1                                                            |                                  | —        | —        |          |                      | LC2          | D2S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E1Eh                   | CLC2SEL2                                                            |                                  | —        | —        |          |                      | LC2          | D3S<5:0> |              |          | xx xxxx               | uu uuuu                      |  |

| E1Fh                   | CLC2SEL3                                                            |                                  | —        | —        |          | LC2D4S<5:0>xx xxxx - |              |          |              |          |                       |                              |  |

| E20h                   | CLC2GLS0                                                            |                                  | LC2G1D4T | LC2G1D4N | LC2G1D3T | LC2G1D3N             | LC2G1D2T     | LC2G1D2N | LC2G1D1T     | LC2G1D1N | xxxx xxxx             | uuuu uuuu                    |  |

| E21h                   | CLC2GLS1                                                            |                                  | LC2G2D4T | LC2G2D4N | LC2G2D3T | LC2G2D3N             | LC2G2D2T     | LC2G2D2N | LC2G2D1T     | LC2G2D1N | xxxx xxxx             | uuuu uuuu                    |  |

#### TION DECISTED SUMMARY PANKS 0.24 (CONTINUED)

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18855/75 devices only. Legend:

Note 1:

Unimplemented, read as '1'. 2:

| R-q/q            | R-0/q                    | R-0/q                                                                 | R-0/q                        | R-q/q               | R-q/q               | U-0               | R-q/q  |

|------------------|--------------------------|-----------------------------------------------------------------------|------------------------------|---------------------|---------------------|-------------------|--------|

| EXTOR            | HFOR                     | MFOR                                                                  | LFOR                         | SOR                 | ADOR                | _                 | PLLR   |

| bit 7            |                          |                                                                       |                              |                     |                     |                   | bit    |

| Legend:          |                          |                                                                       |                              |                     |                     |                   |        |

| R = Readable     | bit                      | W = Writable b                                                        | it                           | U = Unimpleme       | ented bit, read as  | '0'               |        |

| u = Bit is unch  | nanged                   | x = Bit is unkno                                                      | own                          | -n/n = Value at     | POR and BOR/V       | alue at all other | Resets |

| '1' = Bit is set |                          | '0' = Bit is clea                                                     | red                          |                     |                     |                   |        |

| bit 7            | 1 = The os<br>0 = The os | FOSC (external) O<br>cillator is ready to<br>cillator is not enab     | be used<br>led, or is not ye |                     | d.                  |                   |        |

| bit 6            | 1 = The os               | TOSC Oscillator F<br>cillator is ready to<br>cillator is not enab     | be used                      | t ready to be used  | d.                  |                   |        |

| bit 5            | 1 = The osc              | ITOSC Oscillator I<br>sillator is ready to b<br>sillator is not enabl | be used                      | ready to be used    |                     |                   |        |

| bit 4            | 1 = The os               | TOSC Oscillator R<br>cillator is ready to<br>cillator is not enab     | be used                      | t ready to be used  | ł.                  |                   |        |

| bit 3            | 1 = The os               | dary (Timer1) Osc<br>cillator is ready to<br>cillator is not enab     | be used                      |                     | ł.                  |                   |        |

| bit 2            | 1 = The os               | Oscillator Ready<br>cillator is ready to<br>cillator is not enab      | be used                      | t ready to be used  | ł                   |                   |        |

| bit 1            | Unimpleme                | nted: Read as '0'                                                     |                              |                     |                     |                   |        |

| bit 0            |                          | s Ready bit<br>L is ready to be u<br>L is not enabled, t              |                              | ut source is not re | eady, or the PLL is | not locked.       |        |

| U-0              | U-0          | R/W/HS-0/0                                                                                     | R/W/HS-0/0      | R/W/HS-0/0      | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0     |

|------------------|--------------|------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|------------------|----------------|

| _                | _            | TMR6IF                                                                                         | TMR5IF          | TMR4IF          | TMR3IF           | TMR2IF           | TMR1IF         |

| bit 7            | •<br>•       |                                                                                                |                 |                 |                  | •                | bit 0          |

|                  |              |                                                                                                |                 |                 |                  |                  |                |

| Legend:          |              |                                                                                                |                 |                 |                  |                  |                |

| R = Readable     | bit          | W = Writable                                                                                   |                 | •               | nented bit, read |                  |                |

| u = Bit is unch  | anged        | x = Bit is unkr                                                                                | Iown            | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets    |

| '1' = Bit is set |              | '0' = Bit is clea                                                                              | ared            | HS = Hardwa     | ire set          |                  |                |

| LH 7 0           |              | tada Daadaa (                                                                                  | - <sup>1</sup>  |                 |                  |                  |                |

| bit 7-6          | •            | ted: Read as '                                                                                 |                 |                 |                  |                  |                |

| bit 5            |              | er6 Interrupt Fla                                                                              | -               | 1:1 modo o TN   | /IR6 to PR6 mat  | ch occurred (m   | ust be cleared |

|                  | in softwa    |                                                                                                | enioweu, or in  | 1.1 moue, a m   | ARO LO FRO MAL   | choccurred (m    | usi de cleareu |

|                  |              | event has occ                                                                                  | urred           |                 |                  |                  |                |

| bit 4            | TRM5IF: Time | er5 Overflow In                                                                                | terrupt Flag bi | it              |                  |                  |                |

|                  |              | erflow occurred                                                                                | •               | ared in softwar | e)               |                  |                |

|                  |              | overflow occu                                                                                  |                 |                 |                  |                  |                |

| bit 3            |              | er4 Interrupt Fl                                                                               | -               | 1,1 mada a TN   | AD4 to DD4 mot   | ab accurred (m   | ust be sleared |

|                  | in softwa    |                                                                                                | eniowed, or in  | I. I mode, a In | /IR4 to PR4 mat  | choccurred (m    | ust be cleared |

|                  |              | event has occ                                                                                  | urred           |                 |                  |                  |                |

| bit 2            | TRM3IF: Time | er3 Overflow In                                                                                | terrupt Flag bi | it              |                  |                  |                |

|                  |              | erflow occurred                                                                                | •               | ared in softwar | e)               |                  |                |

| 1.11.4           |              | overflow occu                                                                                  |                 |                 |                  |                  |                |

| bit 1            |              | er2 Interrupt Fl                                                                               | -               | 1.1 made a TN   |                  |                  | unthe cleared  |

|                  | in softwa    | 2 postscaler overflowed, or in 1:1 mode, a TMR2 to PR2 match occurred (must be cleared<br>are) |                 |                 |                  |                  |                |

|                  |              | event has occ                                                                                  | urred           |                 |                  |                  |                |

| bit 0            | TRM1IF: Time | er1 Overflow In                                                                                | terrupt Flag bi | it              |                  |                  |                |

|                  |              | erflow occurred                                                                                | •               | ared in softwar | e)               |                  |                |

|                  | 0 = No TMR1  | overflow occu                                                                                  | rred            |                 |                  |                  |                |

### REGISTER 7-15: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

# 10.2 Data EEPROM Memory

Data EEPROM Memory consists of 256 bytes of user data memory. The EEPROM provides storage locations for 8-bit user defined data.

EEPROM can be read and/or written through:

- FSR/INDF indirect access (Section 10.3 "FSR and INDF Access")

- NVMREG access (Section 10.4 "NVMREG Access")

- In-Circuit Serial Programming (ICSP)

Unlike PFM, which must be written to by row, EEPROM can be written to word by word.

### 10.3 FSR and INDF Access

The FSR and INDF registers allow indirect access to the PFM or EEPROM.

#### 10.3.1 FSR READ

With the intended address loaded into an FSR register a MOVIW instruction or read of INDF will read data from the PFM or EEPROM.

Reading from NVM requires one instruction cycle. The CPU operation is suspended during the read, and resumes immediately after. Read operations return a single word of memory.

#### 10.3.2 FSR WRITE

Writing/erasing the NVM through the FSR registers (ex. MOVWI instruction) is not supported in the PIC16(L)F18856/76 devices.

### 10.4 NVMREG Access

The NVMREG interface allows read/write access to all the locations accessible by FSRs, and also read/write access to the User ID locations, and read-only access to the device identification, revision, and Configuration data.

Reading, writing, or erasing of NVM via the NVMREG interface is prevented when the device is code-protected.

#### 10.4.1 NVMREG READ OPERATION

To read a NVM location using the NVMREG interface, the user must:

- Clear the NVMREGS bit of the NVMCON1 register if the user intends to access PFM locations, or set NMVREGS if the user intends to access User ID, Configuration, or EEPROM locations.

- Write the desired address into the NVMADRH:NVMADRL register pair (Table 10-2).

- 3. Set the RD bit of the NVMCON1 register to initiate the read.

Once the read control bit is set, the CPU operation is suspended during the read, and resumes immediately after. The data is available in the very next cycle, in the NVMDATH:NVMDATL register pair; therefore, it can be read as two bytes in the following instructions.

NVMDATH:NVMDATL register pair will hold this value until another read or until it is written to by the user.

#### 20.1.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 20-2. This alternation creates the push-pull effect required for driving some transformer-based power supply designs.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

#### 20.1.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. In Forward Full-Bridge mode, CWGxA is driven to its active state, CWGxB and CWGxC are driven to their inactive state, and CWGxD is modulated by the input signal. In Reverse Full-Bridge mode, CWGxC is driven to its active state, CWGxA and CWGxD are driven to their inactive states, and CWGxB is modulated by the input signal. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or vice-versa. This dead-band control is described in Section 20.5 "Dead-Band Control", with additional details in Section 20.6 "Rising Edge and Reverse Dead Band" and Section 20.7 "Falling Edge and Forward Dead Band".

The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWGxCON0 while keeping MODE<2:1> static, without disabling the CWG module.

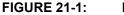

# 21.0 ZERO-CROSS DETECTION (ZCD) MODULE

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero crossing threshold is the zero crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 21-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- Low EMI cycle switching

# 21.1 External Resistor Selection

The ZCD module requires a current limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 21-1 and Figure 21-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

#### EQUATION 21-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

EXTERNAL VOLTAGE

| R-0/0            | R-0/0                                                                                                   | R-0/0                                                                                                                                                              | R/C/HS-0/0                                                                                                                   | U-0                    | R-0/0                                | R-0/0            | R-0/0        |

|------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------|------------------|--------------|

| ADAOV            | ADUTHR                                                                                                  | ADLTHR                                                                                                                                                             | ADMATH                                                                                                                       | —                      |                                      | ADSTAT<2:0>      |              |

| bit 7            |                                                                                                         |                                                                                                                                                                    |                                                                                                                              |                        |                                      |                  | bit 0        |

|                  |                                                                                                         |                                                                                                                                                                    |                                                                                                                              |                        |                                      |                  |              |

| Legend:          |                                                                                                         |                                                                                                                                                                    |                                                                                                                              |                        |                                      |                  |              |

| R = Readable     |                                                                                                         |                                                                                                                                                                    |                                                                                                                              |                        |                                      |                  |              |

| u = Bit is unch  | 0                                                                                                       | x = Bit is unki                                                                                                                                                    | nown                                                                                                                         | -n/n = Value           | at POR and BC                        | R/Value at all o | other Resets |

| '1' = Bit is set |                                                                                                         | '0' = Bit is cle                                                                                                                                                   | ared                                                                                                                         |                        |                                      |                  |              |

| bit 7            | 1 = ADC accu                                                                                            |                                                                                                                                                                    | Overflow bit<br>ERR calculatic<br>DERR calcula                                                                               |                        |                                      |                  |              |

| bit 6            | <b>ADUTHR:</b> AD<br>1 = ADERR ><br>0 = ADERR≤                                                          | ADUTH                                                                                                                                                              | ater-than Uppe                                                                                                               | er Threshold F         | lag bit                              |                  |              |

| bit 5            | <b>ADLTHR:</b> AD<br>1 = ADERR<,<br>0 = ADERR≥,                                                         | ADLTH                                                                                                                                                              | s-than Lower T                                                                                                               | hreshold Flag          | bit                                  |                  |              |

| bit 4            | 1 = Registers<br>updated                                                                                | ADACC, ADF                                                                                                                                                         |                                                                                                                              | ADLTH and the          | e ADAOV bit ar<br>s bit was last cle |                  | ave already  |

| bit 3            | Unimplemen                                                                                              | ted: Read as '                                                                                                                                                     | 0'                                                                                                                           |                        |                                      |                  |              |

| bit 2-0          | 111 = ADC m<br>110 = ADC m<br>101 = ADC m<br>100 = Not use<br>011 = ADC m<br>010 = ADC m<br>001 = ADC m | nodule is in 2 <sup>nd</sup><br>nodule is in 2 <sup>nd</sup><br>nodule is in 2 <sup>nd</sup><br>ed<br>nodule is in 1 <sup>st</sup><br>nodule is in 1 <sup>st</sup> | e Cycle Multist<br>conversion sta<br>acquisition sta<br>precharge sta<br>conversion sta<br>acquisition sta<br>precharge stag | age<br>age<br>ge<br>ge | <sub>5</sub> (1)                     |                  |              |

### REGISTER 23-5: ADSTAT: ADC THRESHOLD REGISTER

**Note 1:** If ADOSC=1, and Fosc<FRC, these bits may be invalid.

# 24.1 NCO OPERATION

The NCO operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCO output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 24-1.

The NCO output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCO output is then distributed internally to other peripherals and can be optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_overflow).

The NCO period changes in discrete steps to create an average frequency. This output depends on the ability of the receiving circuit (i.e., CWG or external resonant converter circuitry) to average the NCO output to reduce uncertainty.

### EQUATION 24-1: NCO OVERFLOW FREQUENCY

$FOVERFLOW = \frac{NCO \ Clock \ Frequency \times Increment \ Value}{2^{20}}$

# 24.1.1 NCO CLOCK SOURCES

Clock sources available to the NCO include:

- HFINTOSC

- Fosc

- LC1\_out

- LC2\_out

- LC3\_out

- LC4\_out

The NCO clock source is selected by configuring the N1CKS<2:0> bits in the NCO1CLK register.

#### 24.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCO1ACCL

- NCO1ACCH

- NCO1ACCU

#### 24.1.3 ADDER

The NCO Adder is a full adder, which operates independently from the source clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

### 24.1.4 INCREMENT REGISTERS

The increment value is stored in three registers making up a 20-bit incrementer. In order of LSB to MSB they are:

- NCO1INCL

- NCO1INCH

- NCO1INCU

When the NCO module is enabled, the NCO1INCU and NCO1INCH registers should be written first, then the NCO1INCL register. Writing to the NCO1INCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCO\_clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCO module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

**Note:** The increment buffer registers are not useraccessible.

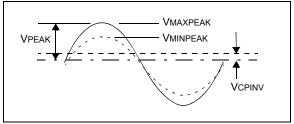

# 30.1 Capture Mode

The Capture mode function described in this section is available and identical for all CCP modules.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxMODE<3:0> bits of the CCPxCON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIR6 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value. Figure 30-1 shows a simplified diagram of the capture operation.

#### 30.1.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

# **Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

The capture source is selected by configuring the CCPxCTS<2:0> bits of the CCPxCAP register. The following sources can be selected:

- CCPxPPS input

- C1OUT\_sync

- C2OUT\_sync

- IOC\_interrupt

- LC1\_out

- LC2\_out

- LC3\_out

- LC4\_out

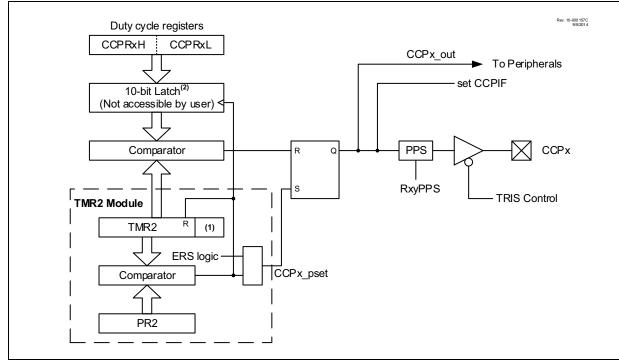

#### FIGURE 30-4: SIMPLIFIED PWM BLOCK DIAGRAM

# 30.3.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the PR2 register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the CCPxFMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR4 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### 30.3.3 CCP/PWM CLOCK SELECTION

The PIC16F18855/75 allows each individual CCP and PWM module to select the timer source that controls the module. Each module has an independent selection.

As there are up to three 8-bit timers with auto-reload (Timer2/4/6), PWM mode on the CCP and PWM modules can use any of these timers. The CCPTMRS0 and CCPTMRS1 registers is used to select which timer is used.

### 30.3.4 TIMER2 TIMER RESOURCE

This device has a newer version of the TMR2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to Section 29.5, Operation Examples for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the FOSC/4 clock source selected

#### 30.3.5 PWM PERIOD

The PWM period is specified by the PR2/4/6 register of Timer2/4/6. The PWM period can be calculated using the formula of Equation 30-1.

### EQUATION 30-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

$$(TMR2 Prescale Value)$$

Note 1: Tosc = 1/Fosc

When TMR2/4/6 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2/4/6 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

| Note: | The Timer postscaler (see Section 29.4 |

|-------|----------------------------------------|

|       | "Timer2 Interrupt") is not used in the |

|       | determination of the PWM frequency.    |

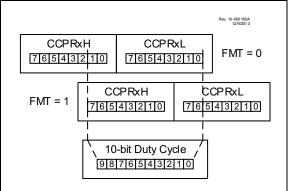

### 30.3.6 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the CCPRxFMT bit of the CCPxCON register (see Figure 30-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 30-2 is used to calculate the PWM pulse width.

Equation 30-3 is used to calculate the PWM duty cycle ratio.

#### FIGURE 30-5: PWM 10-BIT ALIGNMENT

### EQUATION 30-2: PULSE WIDTH

Pulse Width = (CCPRxH:CCPRxL register pair) •

TOSC • (TMR2 Prescale Value)

### EQUATION 30-3: DUTY CYCLE RATIO

Duty Cycle Ratio =

$$\frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 30-4).

### 30.3.7 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 30-4.

# EQUATION 30-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

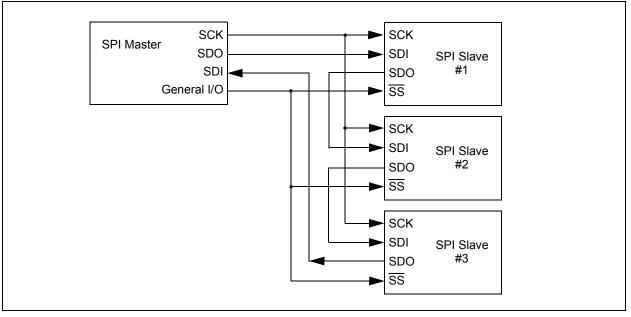

# FIGURE 31-7: SPI DAISY-CHAIN CONNECTION

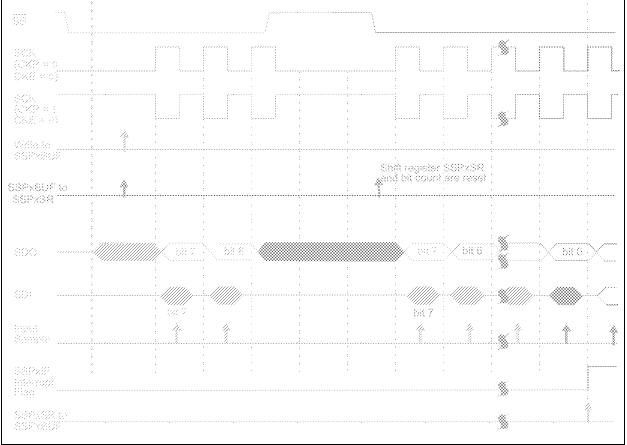

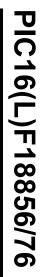

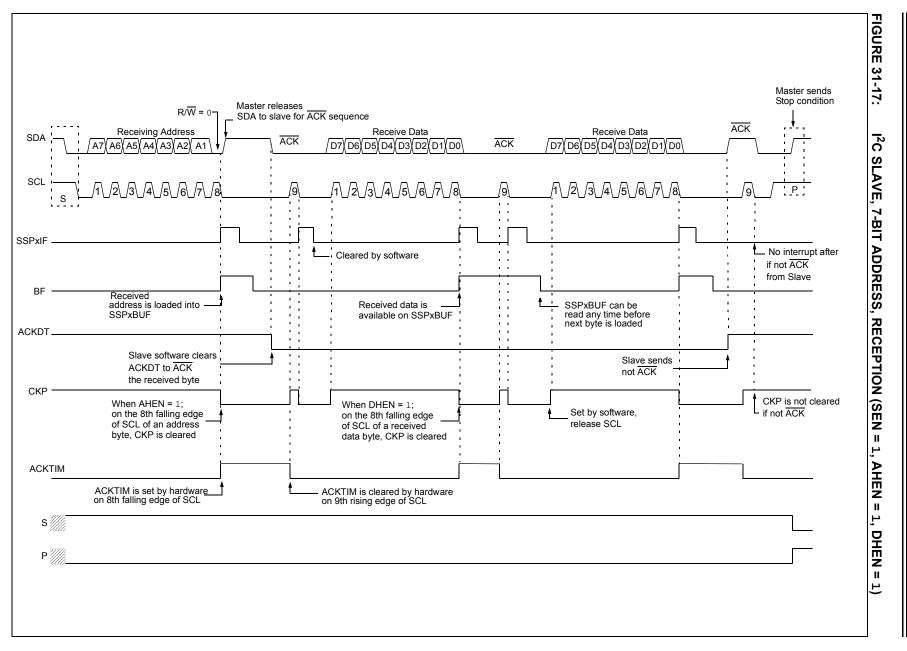

#### 31.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into IDLE mode (Figure 31-30).

#### 31.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

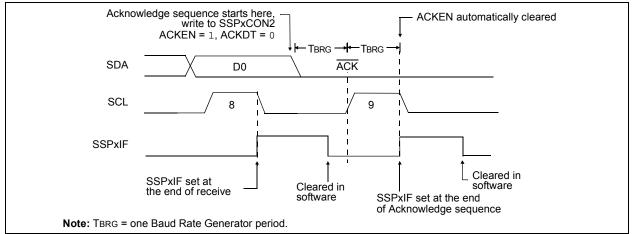

### 31.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 31-31).

### 31.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 31-30: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 31-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 32.5.3 GO STATUS

Timer run status is determined by the TS bit of the SMTxSTAT register, and will be delayed in time by synchronizer delays in non-Counter modes.

### 32.6 Modes of Operation

The modes of operation are summarized in Table 32-1. The following sections provide detailed descriptions, examples of how the modes can be used. Note that all waveforms assume WPOL/SPOL/CPOL = 0. When WPOL/SPOL/CPOL = 1, all SMTSIGx, SMTWINx and SMT clock signals will have a polarity opposite to that indicated. For all modes, the REPEAT bit controls whether the acquisition is repeated or single. When REPEAT = 0 (Single Acquisition mode), the timer will stop incrementing and the SMTxGO bit will be reset upon the completion of an acquisition. Otherwise, the timer will continue and allow for continued acquisitions to overwrite the previous ones until the timer is stopped in software.

# 32.6.1 TIMER MODE

Timer mode is the simplest mode of operation where the SMTxTMR is used as a 16/24-bit timer. No data acquisition takes place in this mode. The timer increments as long as the SMTxGO bit has been set by software. No SMT window or SMT signal events affect the SMTxGO bit. Everything is synchronized to the SMT clock source. When the timer experiences a period match (SMTxTMR = SMTxPR), SMTxTMR is reset and the period match interrupt trips. See Figure 32-3.

| MODE      | Mode of Operation                 | Synchronous<br>Operation | Reference                                    |

|-----------|-----------------------------------|--------------------------|----------------------------------------------|

| 0000      | Timer                             | Yes                      | Section 32.6.1 "Timer Mode"                  |

| 0001      | Gated Timer                       | Yes                      | Section 32.6.2 "Gated Timer Mode"            |

| 0010      | Period and Duty Cycle Acquisition | Yes                      | Section 32.6.3 "Period and Duty-Cycle Mode"  |

| 0011      | High and Low Time Measurement     | Yes                      | Section 32.6.4 "High and Low Measure Mode"   |

| 0100      | Windowed Measurement              | Yes                      | Section 32.6.5 "Windowed Measure Mode"       |

| 0101      | Gated Windowed Measurement        | Yes                      | Section 32.6.6 "Gated Window Measure Mode"   |

| 0110      | Time of Flight                    | Yes                      | Section 32.6.7 "Time of Flight Measure Mode" |

| 0111      | Capture                           | Yes                      | Section 32.6.8 "Capture Mode"                |

| 1000      | Counter                           | No                       | Section 32.6.9 "Counter Mode"                |

| 1001      | Gated Counter                     | No                       | Section 32.6.10 "Gated Counter Mode"         |

| 1010      | Windowed Counter                  | No                       | Section 32.6.11 "Windowed Counter Mode"      |

| 1011-1111 | Reserved                          | —                        | _                                            |

TABLE 32-1: MODES OF OPERATION

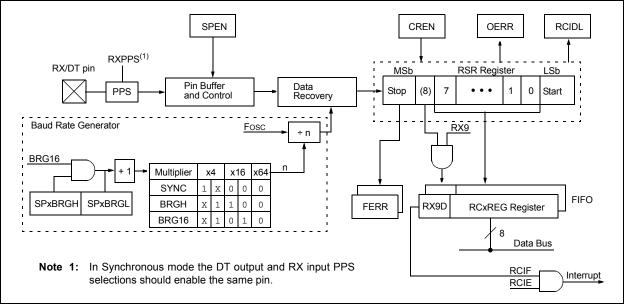

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TX1STA)

- Receive Status and Control (RC1STA)

- Baud Rate Control (BAUD1CON)

These registers are detailed in Register 33-1, Register 33-2 and Register 33-3, respectively.

The RX input pin is selected with the RXPPS. The CK input is selected with the TXPPS register. TX, CK, and DT output pins are selected with each pin's RxyPPS register. Since the RX input is coupled with the DT output in Synchronous mode, it is the user's responsibility to select the same pin for both of these functions when operating in Synchronous mode. The EUSART control logic will control the data direction drivers automatically.

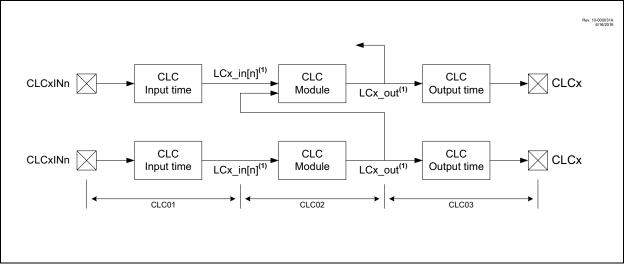

### TABLE 37-20: CONFIGURABLE LOGIC CELL (CLC) CHARACTERISTICS

|               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                             |      |          |      |          |                          |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|----------|------|----------|--------------------------|--|--|--|--|

| Param.<br>No. | Sym.                                                                                                                 | Characteristic                              | Min. | Тур†     | Max. | Units    | Conditions               |  |  |  |  |

| CLC01*        | TCLCIN                                                                                                               | CLC input time                              | _    | 7        | OS17 | ns       | (Note 1)                 |  |  |  |  |

| CLC02*        | TCLC                                                                                                                 | CLC module input to output progagation time |      | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |  |  |  |  |

| CLC03*        | TCLCOUT                                                                                                              | CLC output time Rise Time                   |      | OS18     |      |          | (Note 1)                 |  |  |  |  |

|               |                                                                                                                      | Fall Time                                   | _    | OS19     | _    | _        | (Note 1)                 |  |  |  |  |

| CLC04*        | FCLCMAX                                                                                                              | CLC maximum switching frequency             | _    | 32       | Fosc | MHz      |                          |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Table 37-10 for OS17, OS18 and OS19 rise and fall times.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

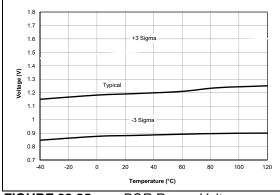

FIGURE 38-25: POR Rearm Voltage, VREGPM1 = 1, PIC16F18856/76 Only.

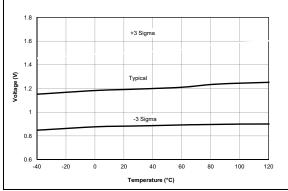

FIGURE 38-26: POR Rearm Voltage, Normal Power Mode, PIC16LF18856/76 Only.

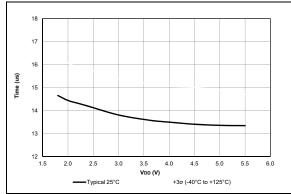

**FIGURE 38-27:** Wake From Sleep, VREGPM = 0, HFINTOSC = 4 MHz, PIC16F18856/76 Only.

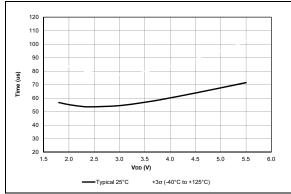

**FIGURE 38-28:** Wake From Sleep, VREGPM = 1, HFINTOSC = 4 MHz, PIC16F18856/76 Only.

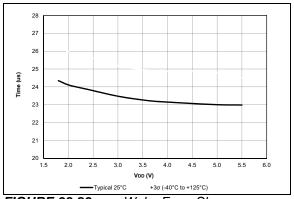

**FIGURE 38-29:** Wake From Sleep, VREGPM = 0, HFINTOSC = 16 MHz, PIC16F18856/76 Only.

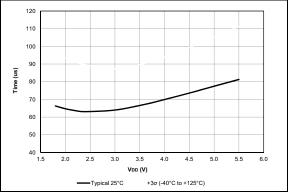

**FIGURE 38-30:** Wake From Sleep, VREGPM = 1, HFINTOSC = 16 MHz, PIC16F18856/76 Only.

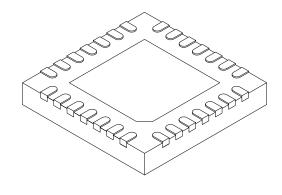

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | LLIMETERS |      |  |  |

|-------------------------|--------|----------|-----------|------|--|--|

| Dimension               | Limits | MIN      | NOM       | MAX  |  |  |

| Number of Pins          | N      |          | 28        |      |  |  |

| Pitch                   | е      |          | 0.65 BSC  |      |  |  |

| Overall Height          | Α      | 0.80     | 0.90      | 1.00 |  |  |

| Standoff                | A1     | 0.00     | 0.02      | 0.05 |  |  |

| Terminal Thickness      | A3     | 0.20 REF |           |      |  |  |

| Overall Width           | Е      |          | 6.00 BSC  |      |  |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70      | 4.20 |  |  |

| Overall Length          | D      |          | 6.00 BSC  |      |  |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70      | 4.20 |  |  |

| Terminal Width          | b      | 0.23     | 0.30      | 0.35 |  |  |

| Terminal Length         | L      | 0.50     | 0.55      | 0.70 |  |  |

| Terminal-to-Exposed Pad | К      | 0.20     | -         | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2