RECERCIC

22222

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 40-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 40-UQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18876-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| O/i | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC                           | Voltage Reference | DAC      | Comparators      | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART | WSQ                   | Timers/SMT                                   | CCP and PWM         | CWG                   | СГС                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change         | Basic          |

|-----|-------------|-------------|------------|-------------|-------------------------------|-------------------|----------|------------------|-------------------|----------------------------------------------|--------|-----------------------|----------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|-----------------------------|----------------|

| RA0 | 2           | 17          | 19         | 19          | ANA0                          | _                 | —        | C1IN0-<br>C2IN0- |                   | —                                            | —      | -                     | —                                            | _                   | —                     | CLCIN0 <sup>(1)</sup> | _   |                        | IOCA0                       | —              |

| RA1 | 3           | 18          | 20         | 20          | ANA1                          | —                 | —        | C1IN1-<br>C2IN1- | —                 | —                                            | —      | —                     | —                                            | _                   | —                     | CLCIN1 <sup>(1)</sup> |     | l                      | IOCA1                       | —              |

| RA2 | 4           | 19          | 21         | 21          | ANA2                          | VREF-             | DAC1OUT1 | C1IN0+<br>C2IN0+ | _                 | -                                            | —      | —                     | _                                            | -                   | —                     | —                     |     |                        | IOCA2                       | -              |

| RA3 | 5           | 20          | 22         | 22          | ANA3                          | VREF+             | _        | C1IN1+           | _                 | _                                            | —      | MDCARL <sup>(1)</sup> | —                                            |                     | —                     | _                     |     | I                      | IOCA3                       | _              |

| RA4 | 6           | 21          | 23         | 23          | ANA4                          | _                 | _        | —                |                   | _                                            | -      | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                         | CCP5 <sup>(1)</sup> | -                     | -                     | —   | —                      | IOCA4                       | _              |

| RA5 | 7           | 22          | 24         | 24          | ANA5                          | _                 | —        | _                | _                 | SS1 <sup>(1)</sup>                           | _      | MDSRC <sup>(1)</sup>  | —                                            | —                   | —                     | —                     | —   | _                      | IOCA5                       | _              |

| RA6 | 14          | 29          | 33         | 31          | ANA6                          | —                 | —        |                  | —                 | —                                            | —      | _                     | —                                            | -                   | —                     | —                     |     |                        | IOCA6                       | OSC2<br>CLKOUT |

| RA7 | 13          | 28          | 32         | 30          | ANA7                          | _                 | _        |                  | _                 | —                                            | —      | —                     | —                                            |                     | —                     | —                     |     |                        | IOCA7                       | OSC1<br>CLKIN  |

| RB0 | 33          | 8           | 9          | 8           | ANB0                          |                   | _        | C2IN1+           | ZCD               | SS2 <sup>(1)</sup>                           | —      | -                     | —                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | _                     |     |                        | INT <sup>(1)</sup><br>IOCB0 | —              |

| RB1 | 34          | 9           | 10         | 9           | ANB1                          | _                 | _        | C1IN3-<br>C2IN3- | _                 | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> | —      | —                     | —                                            |                     | CWG2IN <sup>(1)</sup> | —                     |     |                        | IOCB1                       | —              |

| RB2 | 35          | 10          | 11         | 10          | ANB2                          |                   | _        |                  | _                 | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | —      | —                     | —                                            |                     | CWG3IN <sup>(1)</sup> | —                     |     |                        | IOCB2                       | —              |

| RB3 | 36          | 11          | 12         | 11          | ANB3                          | —                 | _        | C1IN2-<br>C2IN2- | _                 | —                                            | _      | —                     | _                                            | _                   | —                     | —                     |     |                        | IOCB3                       | —              |

| RB4 | 37          | 12          | 14         | 14          | ANB4<br>ADCACT <sup>(1)</sup> | —                 | —        |                  | _                 | —                                            | —      | _                     | T5G <sup>(1)</sup><br>SMTWIN2 <sup>(1)</sup> | -                   | —                     | -                     |     |                        | IOCB4                       | —              |

| RB5 | 38          | 13          | 15         | 15          | ANB5                          | —                 | —        |                  | —                 | —                                            | —      | -                     | T1G <sup>(1)</sup><br>SMTSIG2 <sup>(1)</sup> | CCP3(1)             | —                     | —                     |     |                        | IOCB5                       | —              |

| RB6 | 39          | 14          | 16         | 16          | ANB6                          | _                 | —        | _                | _                 | —                                            | _      | —                     | —                                            | —                   | —                     | CLCIN2 <sup>(1)</sup> | —   | _                      | IOCB6                       | ICSPCLK        |

| RB7 | 40          | 15          | 17         | 17          | ANB7                          | _                 | DAC1OUT2 |                  | —                 | —                                            | —      | —                     | T6IN <sup>(1)</sup>                          | _                   | —                     | CLCIN3 <sup>(1)</sup> | —   |                        | IOCB7                       | ICSPDAT        |

#### TABLE 3:40/44-PIN ALLOCATION TABLE (PIC16(L)F18876)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

These pins are configured for 1<sup>2</sup>C logic levels.; The SCLx/SDAx signals must be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the 1<sup>2</sup>C specific or SMbus input buffer thresholds.

### 1.0 DEVICE OVERVIEW

The PIC16(L)F18856/76 are described within this data sheet. The PIC16(L)F18856 devices are available in 28-pin SPDIP, SSOP, SOIC, and UQFN packages. The PIC16(L)F18876 devices are available in 40-pin PDIP and UQFN and 44-pin TQFP and QFN packages.

Figure 1-1 shows a block diagram of the PIC16(L)F18856/76 devices. Table 1-2 and Table 1-3 show the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| SUIVIIVIAR I                                                   |                           |                |                |

|----------------------------------------------------------------|---------------------------|----------------|----------------|

| Peripheral                                                     |                           | PIC16(L)F18856 | PIC16(L)F18856 |

| Analog-to-Digital Converter with Computa                       | ation (ADC <sup>2</sup> ) | •              | ٠              |

| Cyclic Redundancy Check (CRC)                                  |                           | ٠              | ٠              |

| Digital-to-Analog Converter (DAC)                              |                           | •              | •              |

| Fixed Voltage Reference (FVR)                                  |                           | •              | •              |

| Enhanced Universal Synchronous/Asynch<br>Transmitter (EUSART1) | ronous Receiver/          | •              | •              |

| Digital Signal Modulator (DSM)                                 |                           | ٠              | ٠              |

| Numerically Controlled Oscillator (NCO1)                       |                           | •              | •              |

| Temperature Indicator                                          |                           | ٠              | •              |

| Zero-Cross Detect (ZCD)                                        |                           | •              | •              |

| Capture/Compare/PWM (CCP/ECCP) Mo                              | dules                     |                |                |

|                                                                | CCP1                      | •              | •              |

|                                                                | CCP2                      | •              | •              |

|                                                                | CCP3                      | •              | •              |

|                                                                | CCP4                      | •              | •              |

|                                                                | CCP5                      | •              | •              |

| Comparators                                                    |                           |                |                |

|                                                                | C1                        | •              | •              |

|                                                                | C2                        | •              | •              |

| Configurable Logic Cell (CLC)                                  |                           |                |                |

|                                                                | CLC1                      | •              | •              |

|                                                                | CLC2                      | •              | •              |

|                                                                | CLC3                      | •              | •              |

|                                                                | CLC4                      | •              | •              |

| Complementary Waveform Generator (CW                           |                           | •              | -              |

| Complementary Wavelorm Cellerator (OW                          | CWG1                      | •              | •              |

|                                                                | CWG2                      | •              | -              |

|                                                                | CWG2                      | •              | -              |

| Master Synchronous Sorial Ports                                | 01103                     | •              | •              |

| Master Synchronous Serial Ports                                | MSSP1                     |                | _              |

|                                                                | MSSP1<br>MSSP2            | •              | -              |

| Pulse-Width Modulator (PWM)                                    | W001-2                    | •              | •              |

|                                                                | PWM6                      |                | •              |

|                                                                | PWM7                      | •              | -              |

| Signal Measure Timer (SMT)                                     | 1 001017                  | •              | •              |

|                                                                | SMT1                      |                | •              |

|                                                                | SMT1<br>SMT2              | •              | -              |

| Timers                                                         | 01012                     | •              | •              |

|                                                                | Timer0                    |                | -              |

|                                                                | Timer0                    |                | •              |

|                                                                |                           | •              | •              |

|                                                                | Timer2                    | •              | •              |

|                                                                | Timer3                    | •              | •              |

|                                                                | Timer4                    | •              | •              |

|                                                                | Timer5                    | •              | •              |

|                                                                | Timer6                    | •              | •              |

| Name                                                       | Function              | Input<br>Type              | Output Type | Description                                                                                      |

|------------------------------------------------------------|-----------------------|----------------------------|-------------|--------------------------------------------------------------------------------------------------|

| RC4/ANC4/SDA1 <sup>(3,4)</sup> /SDI1 <sup>(1)</sup> /IOCC4 | RC4                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC4                  | AN                         | _           | ADC Channel C4 input.                                                                            |

|                                                            | SDA1 <sup>(3,4)</sup> | l <sup>2</sup> C/<br>SMBus | OD          | MSSP1 I <sup>2</sup> C serial data input/output.                                                 |

|                                                            | SDI1 <sup>(1)</sup>   | TTL/ST                     | -           | MSSP1 SPI serial data input.                                                                     |

|                                                            | IOCC4                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RC5/ANC5/T4IN <sup>(1)</sup> /IOCC5                        | RC5                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC5                  | AN                         | _           | ADC Channel C5 input.                                                                            |

|                                                            | T4IN <sup>(1)</sup>   | TTL/ST                     | -           | Timer4 external input.                                                                           |

|                                                            | IOCC5                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RC6/ANC6/CK <sup>(3)</sup> /IOCC6                          | RC6                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC6                  | AN                         | -           | ADC Channel C6 input.                                                                            |

|                                                            | CK <sup>(3)</sup>     | TTL/ST                     | CMOS/OD     | EUSART synchronous mode clock input/output.                                                      |

|                                                            | IOCC6                 | TTL/ST                     | -           | Interrupt-on-change input.                                                                       |

| RC7/ANC7/RX <sup>(1)</sup> /DT <sup>(3)</sup> /IOCC7       | RC7                   | TTL/ST                     | CMOS/OD     | General purpose I/O.                                                                             |

|                                                            | ANC7                  | AN                         | -           | ADC Channel C7 input.                                                                            |

|                                                            | RX <sup>(1)</sup>     | TTL/ST                     | -           | EUSART Asynchronous mode receiver data input.                                                    |

|                                                            | DT <sup>(3)</sup>     | TTL/ST                     | CMOS/OD     | EUSART Synchronous mode data input/output.                                                       |

|                                                            | IOCC7                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

| RE3/IOCE3/MCLR/Vpp                                         | RE3                   | TTL/ST                     | —           | General purpose input only (when $\overline{\text{MCLR}}$ is disabled by the Configuration bit). |

|                                                            | IOCE3                 | TTL/ST                     | _           | Interrupt-on-change input.                                                                       |

|                                                            | MCLR                  | ST                         | -           | Master clear input with internal weak pull up resistor.                                          |

|                                                            | VPP                   | HV                         | _           | ICSP™ High-Voltage Programming mode entry input.                                                 |

| Vdd                                                        | Vdd                   | Power                      | _           | Positive supply voltage input.                                                                   |

#### **TABLE 1-2:** PIC16F18856 PINOUT DESCRIPTION (CONTINUED)

CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Legend: AN = Analog input or output TTL = TTL compatible input ST

= Open-Drain = Schmitt Trigger input with I<sup>2</sup>C

1<sup>2</sup>C

Note

HV = High Voltage XTAL = Crystal levels This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx This is a PPS remappable input signal. The input function may be used for this signal. 1:

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options 2: as described in Table 13-3.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and 3: PPS output registers.

These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS 4: assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| IADLE 0-1. NUSC/CUSC DI SETTINGS | TABLE 6-1: | NOSC/COSC BIT SETTINGS |

|----------------------------------|------------|------------------------|

|----------------------------------|------------|------------------------|

| NOSC<2:0>/<br>COSC<2:0> | Clock Source                              |

|-------------------------|-------------------------------------------|

| 111                     | EXTOSC <sup>(1)</sup>                     |

| 110                     | HFINTOSC <sup>(2)</sup>                   |

| 101                     | LFINTOSC                                  |

| 100                     | SOSC                                      |

| 011                     | Reserved (it operates like<br>NOSC = 110) |

| 010                     | EXTOSC with 4x PLL <sup>(1)</sup>         |

| 001                     | HFINTOSC with 2x PLL <sup>(1)</sup>       |

| 000                     | Reserved (it operates like<br>NOSC = 110) |

| Note di EVTORC confir   | urad by the FEVTOCC bits of               |

**Note 1:** EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 4-1).

| NDIV<3:0>/<br>CDIV<3:0> | Clock divider |  |  |  |  |

|-------------------------|---------------|--|--|--|--|

| 1111-1010               | Reserved      |  |  |  |  |

| 1001                    | 512           |  |  |  |  |

| 1000                    | 256           |  |  |  |  |

| 0111                    | 128           |  |  |  |  |

| 0110                    | 64            |  |  |  |  |

| 0101                    | 32            |  |  |  |  |

| 0100                    | 16            |  |  |  |  |

| 0011                    | 8             |  |  |  |  |

| 0010                    | 4             |  |  |  |  |

| 0001                    | 2             |  |  |  |  |

| 0000                    | 1             |  |  |  |  |

#### REGISTER 6-3: OSCCON3: OSCILLATOR CONTROL REGISTER 3

| R/W/HC-0/0 | R/W-0/0 | U-0 | R-0/0 | R-0/0 | U-0 | U-0 | U-0   |

|------------|---------|-----|-------|-------|-----|-----|-------|

| CSWHOLD    | SOSCPWR | —   | ORDY  | NOSCR | —   |     | —     |

| bit 7      |         |     |       |       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7   | CSWHOLD: Clock Switch Hold bit                                                                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready</li> <li>0 = Clock switch may proceed when the oscillator selected by NOSC is ready; if this bit</li> </ul> |

|         | is clear at the time that NOSCR becomes '1', the switch will occur                                                                                                                                             |

| bit 6   | SOSCPWR: Secondary Oscillator Power Mode Select bit                                                                                                                                                            |

|         | 1 = Secondary oscillator operating in High-power mode                                                                                                                                                          |

|         | 0 = Secondary oscillator operating in Low-power mode                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'.                                                                                                                                                                                    |

| bit 4   | ORDY: Oscillator Ready bit (read-only)                                                                                                                                                                         |

|         | 1 = OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC                                                                                                                                 |

|         | 0 = A clock switch is in progress                                                                                                                                                                              |

| bit 3   | NOSCR: New Oscillator is Ready bit (read-only)                                                                                                                                                                 |

|         | 1 = A clock switch is in progress and the oscillator selected by NOSC indicates a "ready" condition                                                                                                            |

|         | 0 = A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready                                                                                                                        |

| bit 2-0 | Unimplemented: Read as '0'                                                                                                                                                                                     |

<sup>2:</sup> HFINTOSC settings are configured with the HFFRQ bits of the OSCFRQ register (Register 6-6).

|               |                 | Remappable to Pins of PORTx |            |       |       |       |           |                                                                              |       |  |  |

|---------------|-----------------|-----------------------------|------------|-------|-------|-------|-----------|------------------------------------------------------------------------------|-------|--|--|

| Output Signal | RxyPPS Register | F                           | PIC16F1885 | 6     |       | Р     | IC16F1887 | 6                                                                            |       |  |  |

| Name          | Value           | PORTA                       | PORTB      | PORTC | PORTA | PORTB | PORTC     | 76<br>PORTD<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | PORTE |  |  |

| ADGRDG        | 0x25            | ٠                           |            | •     | •     |       | ٠         |                                                                              |       |  |  |

| ADGRDA        | 0x24            | ٠                           |            | •     | •     |       | •         |                                                                              |       |  |  |

| CWG3D         | 0x23            | ٠                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| CWG3C         | 0x22            | ٠                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| CWG3B         | 0x21            | ٠                           |            | •     | •     |       |           |                                                                              | •     |  |  |

| CWG3A         | 0x20            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| CWG2D         | 0x1F            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG2C         | 0x1E            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG2B         | 0x1D            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG2A         | 0x1C            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| DSM           | 0x1B            | •                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| CLKR          | 0x1A            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| NCO           | 0x19            | ٠                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| TMR0          | 0x18            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| SDO2/SDA2     | 0x17            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| SCK2/SCL2     | 0x16            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| SD01/SDA1     | 0x15            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| SCK1/SCL1     | 0x14            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| C2OUT         | 0x13            | ٠                           |            | •     | •     |       |           |                                                                              | •     |  |  |

| C10UT         | 0x12            | ٠                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| DT            | 0x11            |                             | •          | •     |       | •     | ٠         |                                                                              |       |  |  |

| TX/CK         | 0x10            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| PWM7OUT       | 0x0F            | ٠                           |            | •     | •     |       | •         |                                                                              |       |  |  |

| PWM6OUT       | 0x0E            | ٠                           |            | •     | •     |       |           | •                                                                            |       |  |  |

| CCP5          | 0x0D            | ٠                           |            | •     | •     |       |           |                                                                              | •     |  |  |

| CCP4          | 0x0C            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CCP3          | 0x0B            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CCP2          | 0x0A            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| CCP1          | 0x09            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| CWG1D         | 0x08            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG1C         | 0x07            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG1B         | 0x06            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CWG1A         | 0x05            |                             | •          | •     |       | •     | •         |                                                                              |       |  |  |

| CLC4OUT       | 0x04            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CLC3OUT       | 0x03            |                             | •          | •     |       | •     |           | •                                                                            |       |  |  |

| CLC2OUT       | 0x02            | •                           |            | •     | •     |       | •         |                                                                              |       |  |  |

| CLC10UT       | 0x01            | •                           |            | •     | •     |       | •         |                                                                              |       |  |  |

#### TABLE 13-3: PPS OUTPUT SIGNAL ROUTING OPTIONS

Note: When RxyPPS = 0x00, port pin Rxy output value is controlled by the respective LATxy bit.

#### REGISTER 13-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

| U-0              | U-0 | R/W-0/u         | R/W-0/u | R/W-0/u         | R/W-0/u         | R/W-0/u | R/W-0/u |

|------------------|-----|-----------------|---------|-----------------|-----------------|---------|---------|

| —                | _   |                 |         | RxyPF           | PS<5:0>         |         |         |

| bit 7            |     |                 |         |                 |                 |         | bit 0   |

|                  |     |                 |         |                 |                 |         |         |

| Legend:          |     |                 |         |                 |                 |         |         |

| R = Readable bit |     | W = Writable bi | t       | II = I Inimplen | nented hit read | as '0'  |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                     |

|---------|--------------------------------------------------------------------------------|

| bit 5-0 | <b>RxyPPS&lt;5:0&gt;:</b> Pin Rxy Output Source Selection bits See Table 13-2. |

Note 1: TRIS control is overridden by the peripheral as required.

#### REGISTER 13-3: PPSLOCK: PPS LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |  |  |  |  |  |

|-------|-----|-----|-----|-----|-----|-----|-----------|--|--|--|--|--|

| —     | _   |     | _   |     | —   |     | PPSLOCKED |  |  |  |  |  |

| bit 7 |     |     |     |     |     |     |           |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1= PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

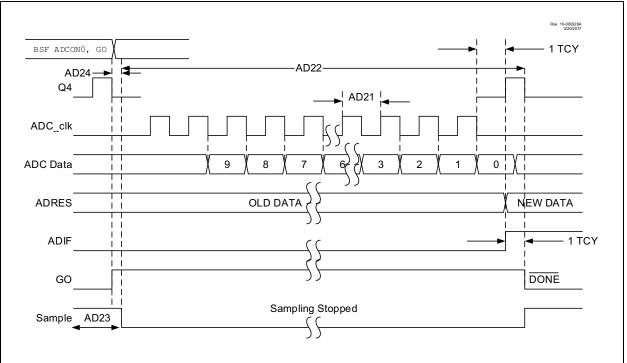

#### **17.4 ADC Acquisition Time**

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between consecutive conversions of the temperature indicator output.

#### TABLE 17-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE TEMPERATURE INDICATOR

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDFV  | R<1:0> | ADFVF | R<1:0> | 269                 |

**Legend:** Shaded cells are unused by the Temperature Indicator module.

| R/W-0/0            | R/W-0/0                                                                                                             | R/W-0/0                                                                                                                                                                                                                                 | U-0                                                                                                                                       | U-0                                                                                                                    | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------|------------------|--------------|--|

| N1PWS<2:0          |                                                                                                                     | ,2)                                                                                                                                                                                                                                     | _                                                                                                                                         | _                                                                                                                      | N1CKS<2:0>       |                  |              |  |

| bit 7              |                                                                                                                     |                                                                                                                                                                                                                                         |                                                                                                                                           |                                                                                                                        |                  |                  | bit C        |  |

| Legend:            |                                                                                                                     |                                                                                                                                                                                                                                         |                                                                                                                                           |                                                                                                                        |                  |                  |              |  |

| R = Readab         | le bit                                                                                                              | W = Writable b                                                                                                                                                                                                                          | bit                                                                                                                                       | U = Unimpler                                                                                                           | mented bit, read | d as '0'         |              |  |

| u = Bit is une     | changed                                                                                                             | x = Bit is unkn                                                                                                                                                                                                                         | own                                                                                                                                       | -n/n = Value                                                                                                           | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is se    | et                                                                                                                  | ʻ0' = Bit is clea                                                                                                                                                                                                                       | ired                                                                                                                                      |                                                                                                                        |                  |                  |              |  |

| bit 7-5<br>bit 4-3 | 111 = NCO<br>110 = NCO<br>101 = NCO<br>011 = NCO<br>010 = NCO<br>001 = NCO<br>000 = NCO                             | NCO1 Output<br>1 output is active<br>1 output is active | e for 128 input<br>e for 64 input<br>e for 32 input<br>e for 16 input<br>e for 8 input<br>e for 8 input<br>e for 2 input<br>e for 1 input | at clock periods<br>clock periods<br>clock periods<br>clock periods<br>clock periods<br>clock periods<br>clock periods | i                |                  |              |  |

|                    | Unimplemented: Read as '0'<br>N1CKS<2:0>: NCO1 Clock Source Select bits                                             |                                                                                                                                                                                                                                         |                                                                                                                                           |                                                                                                                        |                  |                  |              |  |

| bit 2-0            | 111 = Resen<br>111 = Resen<br>101 = LC4_c<br>100 = LC3_c<br>011 = LC2_c<br>010 = LC1_c<br>001 = HFINT<br>000 = Fosc | ved<br>ved<br>out<br>out<br>out<br>out                                                                                                                                                                                                  |                                                                                                                                           | נ שונס                                                                                                                 |                  |                  |              |  |

- **Note 1:** N1PWS applies only when operating in Pulse Frequency mode.

- 2: If NCO1 pulse width is greater than NCO1 overflow period, operation is undefined.

### 26.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCON1 register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCON1 register.

### 26.6 Programmable Modulator Data

The MDBIT of the MDCON0 register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

### 26.7 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON0 register.

#### 26.8 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the SLR bit of the SLRCON register associated with that pin. For example, clearing the slew rate limitation for pin RA5 would require clearing the SLRA5 bit of the SLRCONA register.

#### 26.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

#### 26.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

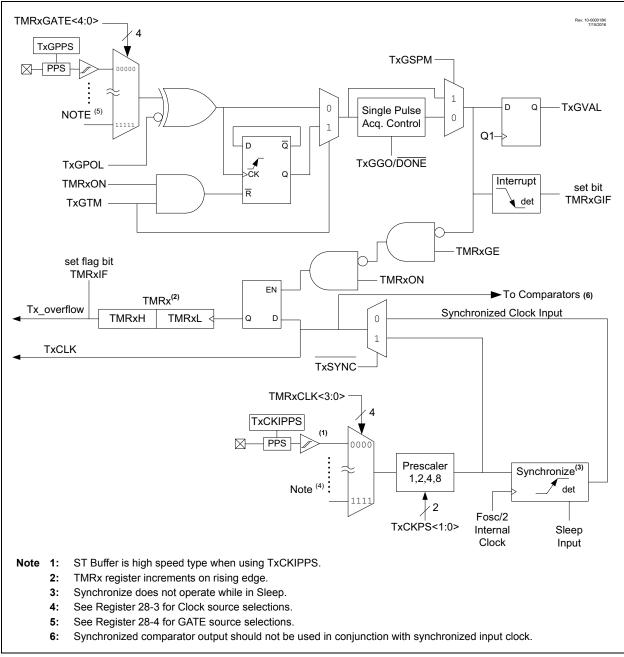

#### FIGURE 28-1: TIMER1 BLOCK DIAGRAM

#### 28.8 Timer1 Interrupts

The timer register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When the timer rolls over, the respective timer interrupt flag bit of the PIR5 register is set. To enable the interrupt on rollover, you must set these bits:

- ON bit of the T1CON register

- TMR1IE bit of the PIE4 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: To avoid immediate interrupt vectoring, the TMR1H:TMR1L register pair should be preloaded with a value that is not imminently about to rollover, and the TMR1IF flag should be cleared prior to enabling the timer interrupts.

### 28.9 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- ON bit of the T1CON register must be set

- TMR1IE bit of the PIE4 register must be set

- PEIE bit of the INTCON register must be set

- SYNC bit of the T1CON register must be set

- CLK bits of the T1CLK register must be configured

- The timer clock source must be enabled and continue operation during sleep. When the SOSC is used for this purpose, the SOSCEN bit of the OSCEN register must be set.

The device will wake-up on an overflow and execute the next instructions. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine.

Secondary oscillator will continue to operate in Sleep regardless of the SYNC bit setting.

### 28.10 CCP Capture/Compare Time Base

The CCP modules use the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value CCPRxH:CCPRxL register pair matches the value in the TMR1H:TMR1L register pair. This event can be an Auto-conversion Trigger.

The Timer1 to CCP1/2/3/4/5 mapping is not fixed, and can be assigned on an individual CCP module basis. All of the CCP modules may be configured to share a single Timer1 (or Timer3, or Timer5) resource, or different CCP modules may be configured to use different Timer1 resources. This timer to CCP mapping selection is made in the CCPTMRS0 and CCPTMRS1 registers.

For more information, see Section 30.0 "Capture/Compare/PWM Modules".

#### 28.11 CCP Auto-Conversion Trigger

When any of the CCP's are configured to trigger an auto-conversion, the trigger will clear the TMR1H:TMR1L register pair. This auto-conversion does not cause a timer interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1.

The timer should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Auto-conversion Trigger. Asynchronous operation of the timer can cause an Auto-conversion Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with an Auto-conversion Trigger from the CCP, the write will take precedence.

For more information, see Section 30.2.4 "Compare During Sleep".

#### REGISTER 31-2: SSPxCON1: SSPx CONTROL REGISTER 1

| R/C/HS-0/0          | R/C/HS-0/0                                                                                                                                                                                                                                                                   | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0/0                                                                                                                                                                                                                           | R/W-0/0                                                                                                                                          | R/W-0/0              | R/W-0/0             | R/W-0/0   |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|-----------|--|--|

| WCOL                | SSPOV <sup>(1)</sup>                                                                                                                                                                                                                                                         | SSPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CKP                                                                                                                                                                                                                               |                                                                                                                                                  | SSPN                 | A<3:0>              |           |  |  |

| pit 7               |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                   |                                                                                                                                                  |                      |                     | bit (     |  |  |

|                     |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                   |                                                                                                                                                  |                      |                     |           |  |  |

| .egend:             |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                   |                                                                                                                                                  |                      |                     |           |  |  |

| R = Readable bit    |                                                                                                                                                                                                                                                                              | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                   | U = Unimplement                                                                                                                                  | ed bit, read as '0'  |                     |           |  |  |

| u = Bit is unchange | ed                                                                                                                                                                                                                                                                           | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n                                                                                                                                                                                                                                 | -n/n = Value at P0                                                                                                                               | OR and BOR/Value     | at all other Resets |           |  |  |

| 1' = Bit is set     |                                                                                                                                                                                                                                                                              | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                   | HS = Bit is set by                                                                                                                               | hardware             | C = User cleared    |           |  |  |

| bit 7               |                                                                                                                                                                                                                                                                              | ollision Detect bit (Tr<br>3UF register is written<br>n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                   |                                                                                                                                                  | word (must be cleare | ed in software)     |           |  |  |

| bit 6               | In SPI mode:<br>1 = A new byte<br>Overflow c<br>setting ove<br>SPxBUF<br>0 = No overflov<br>In I <sup>2</sup> C mode:<br>1 = A byte is m                                                                                                                                     | <ul> <li>POV: Receive Overflow Indicator bit<sup>(1)</sup></li> <li>SPI mode:</li> <li>A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lose Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPxBUF, even if only transmitting data, to avo setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register (must be cleared in software).</li> <li>No overflow</li> <li>A overflow</li> <li>A new byte is received while the SSPxBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mo (must be cleared in software).</li> </ul> |                                                                                                                                                                                                                                   |                                                                                                                                                  |                      |                     |           |  |  |

| it 5                | In both modes, v<br>In SPI mode:<br>1 = Enables se<br>0 = Disables s<br>In I <sup>2</sup> C mode:                                                                                                                                                                            | SSPEN: Synchronous Serial Port Enable bit<br>n both modes, when enabled, the following pins must be properly configured as input or output<br><u>n SPI mode:</u><br>L = Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as the source of the serial port pins <sup>(2)</sup><br>D = Disables serial port and configures these pins as I/O port pins<br><u>n I<sup>2</sup>C mode:</u><br>L = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins <sup>(3)</sup>                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                   |                                                                                                                                                  |                      |                     |           |  |  |

| bit 4               | 0 = Idle state for<br>In I <sup>2</sup> C Slave mod<br>SCL release cor<br>1 = Enable clock                                                                                                                                                                                   | c clock is a high level<br>clock is a low level<br><u>de:</u><br>htrol<br>(<br>low (clock stretch). (<br>ode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                   | lata setup time.)                                                                                                                                |                      |                     |           |  |  |

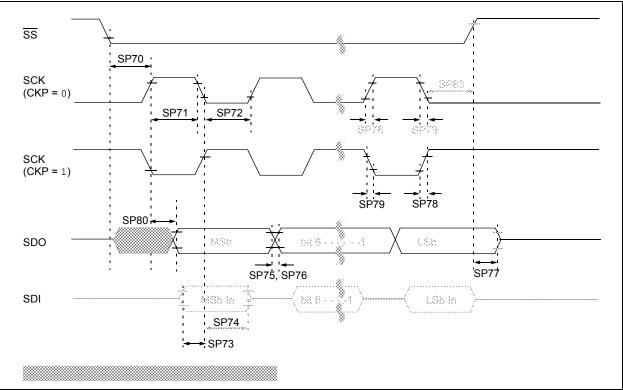

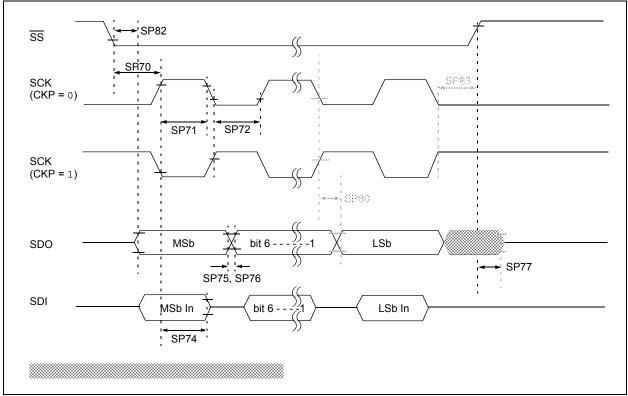

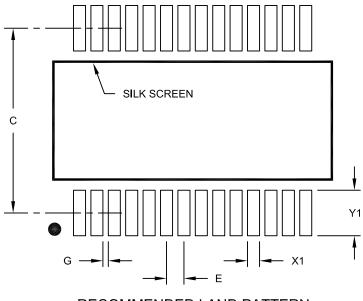

| pit 3-0             | 1111 = I <sup>2</sup> C Slav<br>1110 = I <sup>2</sup> C Slav<br>1101 = Reserve<br>1001 = Reserve<br>1001 = SPI Mas<br>1001 = Reserve<br>1000 = I <sup>2</sup> C Mas<br>0011 = I <sup>2</sup> C Slav<br>0110 = SPI Slav<br>0100 = SPI Mas<br>0010 = SPI Mas<br>0001 = SPI Mas | d<br>ware controlled Mast<br>ster mode, clock = Fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ess with Start and<br>ss with Start and<br>ter mode (slave i<br>osc/(4 * (SSPxAl<br>osc / (4 * (SSPxAl<br>osc / (4 * (SSPxA<br>ess<br>ss<br>K pin, <u>SS</u> pin con<br>K pin, <u>SS</u> pin con<br>Z-match/2<br>osc/64<br>osc/16 | d Stop bit interrupts of<br>Stop bit interrupts en<br>dle)<br>DD+1)) <sup>(5)</sup><br>DD+1)) <sup>(4)</sup><br>ntrol disabled, <del>SS</del> ca | nabled               | in                  |           |  |  |