Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18876-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0  | Device Overview                                                           | 16  |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Enhanced Mid-Range CPU                                                    | 33  |

| 3.0  | Memory Organization                                                       | 35  |

| 4.0  | Device Configuration                                                      | 92  |

| 5.0  | Resets                                                                    | 101 |

| 6.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          | 110 |

| 7.0  | Interrupts                                                                | 129 |

| 8.0  | Power-Saving Operation Modes                                              | 155 |

| 9.0  | Windowed Watchdog Timer (WWDT)                                            |     |

| 10.0 | Nonvolatile Memory (NVM) Control                                          | 170 |

| 11.0 | Cyclic Redundancy Check (CRC) Module                                      | 188 |

| 12.0 | I/O Ports                                                                 | 200 |

| 13.0 | Peripheral Pin Select (PPS) Module                                        | 243 |

| 14.0 | Peripheral Module Disable                                                 | 253 |

| 15.0 | Interrupt-On-Change                                                       | 260 |

| 16.0 | Fixed Voltage Reference (FVR)                                             | 268 |

|      | Temperature Indicator Module                                              |     |

|      | Comparator Module                                                         |     |

| 19.0 | Pulse-Width Modulation (PWM)                                              | 283 |

| 20.0 | Complementary Waveform Generator (CWG) Module                             | 290 |

| 21.0 | Zero-Cross Detection (ZCD) Module                                         | 314 |

| 22.0 | Configurable Logic Cell (CLC)                                             | 320 |

| 23.0 | Analog-to-Digital Converter With Computation (ADC2) Module                | 337 |

| 24.0 | Numerically Controlled Oscillator (NCO) Module                            | 376 |

| 25.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           | 386 |

|      | Data Signal Modulator (DSM) Module                                        |     |

| 27.0 | Timer0 Module                                                             | 404 |

| 28.0 | Timer1/3/5 Module with Gate Control                                       | 410 |

| 29.0 | Timer2/4/6 Module                                                         | 424 |

| 30.0 | Capture/Compare/PWM Modules                                               | 445 |

| 31.0 | Master Synchronous Serial Port (MSSP) Modules                             | 458 |

| 32.0 | Signal Measurement Timer (SMT)                                            | 509 |

| 33.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 554 |

| 34.0 | Reference Clock Output Module                                             | 582 |

| 35.0 | In-Circuit Serial Programming™ (ICSP™)                                    | 586 |

| 36.0 | Instruction Set Summary                                                   | 588 |

| 37.0 | Electrical Specifications                                                 | 602 |

| 38.0 | DC and AC Characteristics Graphs and Charts                               | 632 |

| 39.0 | Development Support                                                       | 648 |

| 40.0 | Packaging Information                                                     | 652 |

|      | s Sheet Revision History                                                  | 678 |

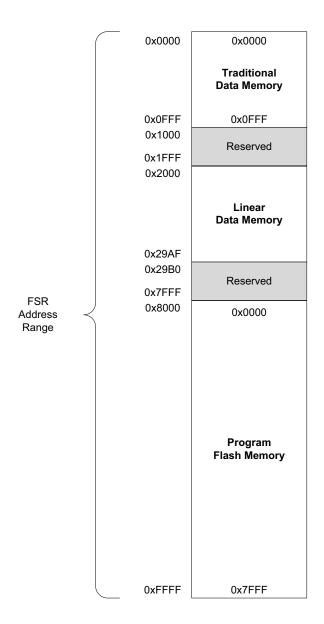

FIGURE 3-8: INDIRECT ADDRESSING

Rev. 10-000044A 7/30/2013

Note: Not all memory regions are completely implemented. Consult device memory tables for memory limits.

#### 4.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Words, Code Protection and Device ID.

### 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as shown in Table 4-1.

TABLE 4-1: CONFIGURATION WORD LOCATIONS

| Configuration Word | Location |

|--------------------|----------|

| CONFIG1            | 8007h    |

| CONFIG2            | 8008h    |

| CONFIG3            | 8009h    |

| CONFIG4            | 800Ah    |

| CONFIG5            | 800Bh    |

Note: The DEBUG bit in Configuration Words is managed automatically by device development tools including debuggers and programmers. For normal device operation, this bit should be maintained as a '1'.

### REGISTER 4-3: CONFIG3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|        |       | WDTPS at   | POR             |                                    |           |

|--------|-------|------------|-----------------|------------------------------------|-----------|

| WDTCPS | Value | Divider Ra | atio            | Typical time out<br>(Fin = 31 kHz) | of WDTPS? |

| 11110  | 11110 | 1:32       | 2 <sup>5</sup>  | 1 ms                               | No        |

| 10011  | 10011 |            |                 |                                    |           |

| 10010  | 10010 | 1:8388608  | 2 <sup>23</sup> | 256 s                              |           |

| 10001  | 10001 | 1:4194304  | 2 <sup>22</sup> | 128 s                              | 1         |

| 10000  | 10000 | 1:2097152  | 2 <sup>21</sup> | 64 s                               | 1         |

| 01111  | 01111 | 1:1048576  | 2 <sup>20</sup> | 32 s                               | 1         |

| 01110  | 01110 | 1:524299   | 2 <sup>19</sup> | 16 s                               | 1         |

| 01101  | 01101 | 1:262144   | 2 <sup>18</sup> | 8 s                                | 1         |

| 01100  | 01100 | 1:131072   | 2 <sup>17</sup> | 4 s                                |           |

| 01011  | 01011 | 1:65536    | 2 <sup>16</sup> | 2 s                                | 1         |

| 01010  | 01010 | 1:32768    | 2 <sup>15</sup> | 1 s                                | 1         |

| 01001  | 01001 | 1:16384    | 2 <sup>14</sup> | 512 ms                             | No        |

| 01000  | 01000 | 1:8192     | 2 <sup>13</sup> | 256 ms                             | 1         |

| 00111  | 00111 | 1:4096     | 2 <sup>12</sup> | 128 ms                             | 1         |

| 00110  | 00110 | 1:2048     | 2 <sup>11</sup> | 64 ms                              |           |

| 00101  | 00101 | 1:1024     | 2 <sup>10</sup> | 32 ms                              | 1         |

| 00100  | 00100 | 1:512      | 2 <sup>9</sup>  | 16 ms                              | ]         |

| 00011  | 00011 | 1:256      | 2 <sup>8</sup>  | 8 ms                               | 7         |

| 00010  | 00010 | 1:128      | 2 <sup>7</sup>  | 4 ms                               | ]         |

| 00001  | 00001 | 1:64       | 2 <sup>6</sup>  | 2 ms                               | ]         |

| 00000  | 00000 | 1:32       | 2 <sup>5</sup>  | 1 ms                               | 1         |

### REGISTER 7-5: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | RCIE    | TXIE    | BCL2IE  | SSP2IE  | BCL1IE  | SSP1IE  |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

| bit 7-6 | Unimplemented: Read as '0'                                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------|

| bit 5   | RCIE: USART Receive Interrupt Enable bit                                                                     |

|         | <ul><li>1 = Enables the USART receive interrupt</li><li>0 = Enables the USART receive interrupt</li></ul>    |

| bit 4   | TXIE: USART Transmit Interrupt Enable bit                                                                    |

|         | <ul><li>1 = Enables the USART transmit interrupt</li><li>0 = Disables the USART transmit interrupt</li></ul> |

| bit 3   | BCL2IE: MSSP2 Bus Collision Interrupt Enable bit                                                             |

|         | <ul><li>1 = MSSP bus Collision interrupt enabled</li><li>0 = MSSP bus Collision interrupt disabled</li></ul> |

| bit 2   | <b>SSP2IE:</b> Synchronous Serial Port (MSSP2) Interrupt Enable bit                                          |

|         | <ul><li>1 = MSSP bus collision Interrupt</li><li>0 = Disables the MSSP Interrupt</li></ul>                   |

| bit 1   | BCL1IE: MSSP1 Bus Collision Interrupt Enable bit                                                             |

|         | <ul><li>1 = MSSP bus collision interrupt enabled</li><li>0 = MSSP bus collision interrupt disabled</li></ul> |

| bit 0   | <b>SSP1IE:</b> Synchronous Serial Port (MSSP1) Interrupt Enable bit                                          |

|         | <ul><li>1 = Enables the MSSP interrupt</li><li>0 = Disables the MSSP interrupt</li></ul>                     |

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by PIE1-PIE8.

#### REGISTER 7-8: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|---------|---------|---------|

| _     | _   | _   | CCP5IE  | CCP4IE  | CCP3IE  | CCP2IE  | CCP1IE  |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

| bit 7-5<br>bit 4 | Unimplemented: Read as '0'.  CCP5IE: CCP5 Interrupt Enable bit  1 = CCP5 interrupt is enabled  0 = CCP5 interrupt is disabled |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3            | <b>CCP4IE:</b> CCP4 Interrupt Enable bit<br>1 = CCP4 interrupt is enabled<br>0 = CCP4 interrupt is disabled                   |

| bit 2            | <b>CCP3IE:</b> CCP3 Interrupt Enable bit<br>1 = CCP3 interrupt is enabled<br>0 = CCP3 interrupt is disabled                   |

| bit 1            | <b>CCP2IE:</b> CCP2 Interrupt Enable bit<br>1 = CCP2 interrupt is enabled<br>0 = CCP2 interrupt is disabled                   |

| bit 0            | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = CCP1 interrupt is enabled<br>0 = CCP1 interrupt is disabled                   |

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE8.

#### REGISTER 9-3: WDTPSL: WDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

| R-0/0                     | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |  |

|---------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PSCNT<7:0> <sup>(1)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                     |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSCNT<7:0>**: Prescale Select Low Byte bits<sup>(1)</sup>

Note 1: The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

| R-0/0                      | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |  |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PSCNT<15:8> <sup>(1)</sup> |       |       |       |       |       |       |       |  |  |

| bit 7                      |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSCNT<15:8>**: Prescale Select High Byte bits<sup>(1)</sup>

Note 1: The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ-ONLY)

| U-0   | R-0/0 | R-0/0 | R-0/0   | R-0/0 | R-0/0  | R-0/0                  | R-0/0 |

|-------|-------|-------|---------|-------|--------|------------------------|-------|

| _     |       | WDTTM | IR<3:0> | STATE | PSCNT< | :17:16> <sup>(1)</sup> |       |

| bit 7 |       |       |         |       |        |                        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 Unimplemented: Read as '0'

bit 6-3 WDTTMR<3:0>: Watchdog Timer Value bits

bit 2 STATE: WDT Armed Status bit

1 = WDT is armed0 = WDT is not armed

bit 1-0 **PSCNT<17:16>**: Prescale Select Upper Byte bits<sup>(1)</sup>

Note 1: The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### 10.4.9 WRERR BIT

The WRERR bit can be used to determine if a write error occurred.

WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- · An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

#### TABLE 10-4: ACTIONS FOR PFM WHEN WR = 1

| Free | LWLO | Actions for PFM when WR = 1                                                                                           | Comments                                                                                                                                              |

|------|------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | х    | Erase the 32-word row of NVMADRH:NVMADRL location. See Section 10.4.3 "NVMREG Write to EEPROM"                        | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch corresponding to NVMADR LSBs. See <b>Section 10.4.4</b> "NVMREG Erase of PFM" | Write protection is ignored     No memory access occurs                                                                                               |

| 0    | 0    | Write the write-latch data to PFM row. See Section 10.4.4 "NVMREG Erase of PFM"                                       | <ul> <li>If WP is enabled, WR is cleared and<br/>WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

#### REGISTER 11-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0   | R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

|       | SHIFT<15:8> |     |     |     |     |     |     |  |  |  |  |

| bit 7 | bit 7 bit   |     |     |     |     |     |     |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SHIFT<15:8>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

#### REGISTER 11-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |  |  |  |

|-------------|-----|-----|-----|-----|-----|--|--|--|--|--|

| SHIFT<7:0>  |     |     |     |     |     |  |  |  |  |  |

| bit 7 bit 0 |     |     |     |     |     |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SHIFT<7:0>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

#### REGISTER 11-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W R/W R/W R/W R/W R/W |  |  |  |  |  | R/W | R/W   |  |  |  |  |

|-------------------------|--|--|--|--|--|-----|-------|--|--|--|--|

| X<15:8>                 |  |  |  |  |  |     |       |  |  |  |  |

| bit 7                   |  |  |  |  |  |     | bit 0 |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 X<15:8>: XOR of Polynomial Term X<sub>N</sub> Enable bits

#### REGISTER 11-10: CRCXORL: CRC XOR LOW BYTE REGISTER

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | _     |

| bit 7   |         |         |         |         |         |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-1 XOR<7:1>: XOR of Polynomial Term X<sub>N</sub> Enable bits

bit 0 Unimplemented: Read as '1'

#### REGISTER 20-3: CWGxDBR: CWGx RISING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|--|--|

| _     | _   |         | DBR<5:0> |         |         |         |         |  |  |  |

| bit 7 |     |         |          |         |         |         | bit 0   |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **DBR<5:0>:** Rising Event Dead-Band Value for Counter bits

#### REGISTER 20-4: CWGxDBF: CWGx FALLING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|--|--|

| _     | _   |         | DBF<5:0> |         |         |         |         |  |  |  |

| bit 7 |     | •       |          |         |         |         | bit 0   |  |  |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **DBF<5:0>:** Falling Event Dead-Band Value for Counter bits

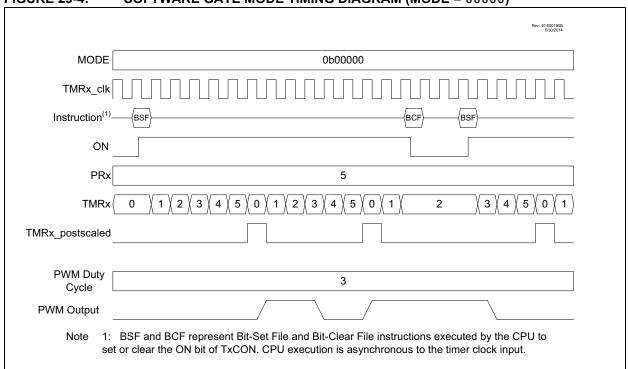

#### 29.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in Section 30.0 "Capture/Compare/PWM Modules". The signals are not a part of the Timer2 module.

#### 29.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON=1 and does not increment when ON=0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 29-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

#### 30.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 28.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

#### 30.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE6 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR6 register following any change in Operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 30.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 30-1 demonstrates the code to perform this function.

## EXAMPLE 30-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point ;to CCPxCON     |

|---------|-------------|-----------------------------------------|

| CLRF    |             | Turn CCP module off                     |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with ;the new prescaler |

|         | 995 995     | ; move value and CCP ON                 |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this ;value          |

#### 30.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

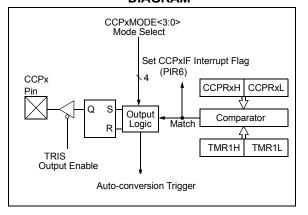

#### 30.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- · Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxMODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger and ADC conversion.

Figure 30-2 shows a simplified diagram of the compare operation.

FIGURE 30-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 31.4 I<sup>2</sup>C MODE OPERATION

All MSSP  $I^2C$  communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external  $I^2C$  devices.

#### 31.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

#### 31.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 31.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

- **Note 1:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

- 2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

#### 31.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

TABLE 31-1: I<sup>2</sup>C BUS TERMS

| IABLE 31-1.         | I C BOS IERIVIS                                                                                                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM                | Description                                                                                                                                                                         |

| Transmitter         | The device which shifts data out onto the bus.                                                                                                                                      |

| Receiver            | The device which shifts data in from the bus.                                                                                                                                       |

| Master              | The device that initiates a transfer, generates clock signals and terminates a transfer.                                                                                            |

| Slave               | The device addressed by the master.                                                                                                                                                 |

| Multi-master        | A bus with more than one device that can initiate data transfers.                                                                                                                   |

| Arbitration         | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                 |

| Synchronization     | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                              |

| Idle                | No master is controlling the bus, and both SDA and SCL lines are high.                                                                                                              |

| Active              | Any time one or more master devices are controlling the bus.                                                                                                                        |

| Addressed<br>Slave  | Slave device that has received a matching address and is actively being clocked by a master.                                                                                        |

| Matching<br>Address | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                 |

| Write Request       | Slave receives a matching address with R/W bit clear, and is ready to clock in data.                                                                                                |

| Read Request        | Master sends an address byte with the R/W bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |

| Clock Stretching    | When a device on the bus hold SCL low to stall communication.                                                                                                                       |

| Bus Collision       | Any time the SDA line is sampled low by the module while it is outputting and expected high state.                                                                                  |

TABLE 33-3: BAUD RATE FORMULAS

| C    | Configuration Bi | ts   | DDO/EUGADT Mada     | Parid Data Farmula |  |  |

|------|------------------|------|---------------------|--------------------|--|--|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Rate Formula  |  |  |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]    |  |  |

| 0    | 0                | 1    | 8-bit/Asynchronous  | Face//40 (5.14)]   |  |  |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]    |  |  |

| 0    | 1                | 1    | 16-bit/Asynchronous |                    |  |  |

| 1    | 0                | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]     |  |  |

| 1    | 1                | х    | 16-bit/Synchronous  |                    |  |  |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair.

TABLE 33-4: BAUD RATE FOR ASYNCHRONOUS MODES

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | _                 | _                             | _                           | _                 | _          | _                           | _                 |            | _                           | _                  | _          |                             |  |  |

| 1200   | _                 | _                             | _                           | 1221              | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00       | 143                         |  |  |

| 2400   | 2404              | 0.16                          | 207                         | 2404              | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00       | 71                          |  |  |

| 9600   | 9615              | 0.16                          | 51                          | 9470              | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00       | 17                          |  |  |

| 10417  | 10417             | 0.00                          | 47                          | 10417             | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42      | 16                          |  |  |

| 19.2k  | 19.23k            | 0.16                          | 25                          | 19.53k            | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |  |  |

| 57.6k  | 55.55k            | -3.55                         | 3                           | _                 | _          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |  |  |

| 115.2k | _                 | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |  |  |

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                  |            |                             |                   |            |                             |                |                  |                             |  |  |

|--------|------------------|-------------------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fos            | Fosc = 1.000 MHz |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 300    | _                | _                             | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300            | 0.16             | 51                          |  |  |

| 1200   | 1202             | 0.16                          | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202           | 0.16             | 12                          |  |  |

| 2400   | 2404             | 0.16                          | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | _              | _                | _                           |  |  |

| 9600   | 9615             | 0.16                          | 12                          | _                | _          | _                           | 9600              | 0.00       | 5                           | _              | _                | _                           |  |  |

| 10417  | 10417            | 0.00                          | 11                          | 10417            | 0.00       | 5                           | _                 | _          | _                           | _              | _                | _                           |  |  |

| 19.2k  | _                | _                             | _                           | _                | _          | _                           | 19.20k            | 0.00       | 2                           | _              | _                | _                           |  |  |

| 57.6k  | _                | _                             | _                           | _                | _          | _                           | 57.60k            | 0.00       | 0                           | _              | _                | _                           |  |  |

| 115.2k | _                | _                             | _                           | _                | _          | _                           | _                 | _          | _                           | _              | _                | _                           |  |  |

TABLE 33-4: BAUD RATE FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 32.000 MHz |                               |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | _                 | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |  |

| 1200   | _                 | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          | _                           |  |

| 2400   | _                 | _                             | _                           | _                 | _          | _                           | _                 | _          | _                           | _                  | _          |                             |  |

| 9600   | 9615              | 0.16                          | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |  |

| 10417  | 10417             | 0.00                          | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |  |

| 19.2k  | 19.23k            | 0.16                          | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |  |

| 57.6k  | 57.14k            | -0.79                         | 34                          | 56.82k            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |  |

| 115.2k | 117.64k           | 2.12                          | 16                          | 113.64k           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|-------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz              |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                             | _          | _                           | -                | _          | _                           | _                 | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | _                             | _          | _                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404                          | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615                          | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417                         | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231                         | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | _                | _          | _                           |

| 57.6k  | 55556                         | -3.55      | 8                           | _                | _          | _                           | 57.60k            | 0.00       | 3                           | _                | _          | _                           |

| 115.2k | _                             | _          | _                           | -                | _          | _                           | 115.2k            | 0.00       | 1                           | -                | _          | _                           |

|        | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                   |            |                             |                   |            |                             |                    |            |                             |

|--------|-------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz             |            |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0                         | 0.00       | 6666                        | 300.0             | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0              | 0.00       | 2303                        |

| 1200   | 1200                          | -0.02      | 3332                        | 1200              | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200               | 0.00       | 575                         |

| 2400   | 2401                          | -0.04      | 832                         | 2399              | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400               | 0.00       | 287                         |

| 9600   | 9615                          | 0.16       | 207                         | 9615              | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00       | 71                          |

| 10417  | 10417                         | 0.00       | 191                         | 10417             | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53       | 65                          |

| 19.2k  | 19.23k                        | 0.16       | 103                         | 19.23k            | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00       | 35                          |

| 57.6k  | 57.14k                        | -0.79      | 34                          | 56.818            | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00       | 11                          |

| 115.2k | 117.6k                        | 2.12       | 16                          | 113.636           | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00       | 5                           |

#### 37.0 ELECTRICAL SPECIFICATIONS

### 37.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias -40°C to +125°C              |

|-------------------------------------------------------------|

| Storage temperature65°C to +150°C                           |

| Voltage on pins with respect to Vss                         |

| on VDD pin                                                  |

| PIC16F18856/76                                              |

| PIC16LF18856/760.3V to +4.0V                                |

| on MCLR pin0.3V to +9.0V                                    |

| on all other pins0.3V to (VDD + 0.3V)                       |

| Maximum current                                             |

| on Vss pin <sup>(1)</sup>                                   |

| $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |

| $85^{\circ}\text{C} < \text{Ta} \le +125^{\circ}\text{C}$   |

| on VDD pin for 28-Pin devices <sup>(1)</sup>                |

| $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |

| $85^{\circ}C < TA \le +125^{\circ}C$                        |

| on VDD pin for 40-Pin devices <sup>(1)</sup>                |

| $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |

| $85^{\circ}C < TA \le +125^{\circ}C$                        |

| on any standard I/O pin ±50 mA                              |

| Clamp current, IK (VPIN < 0 or VPIN > VDD)                  |

| Total power dissipation <sup>(2)</sup>                      |

- **Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 37-6 to calculate device specifications.

- 2: Power dissipation is calculated as follows:

PDIS = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$  (VOI x IOL)

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

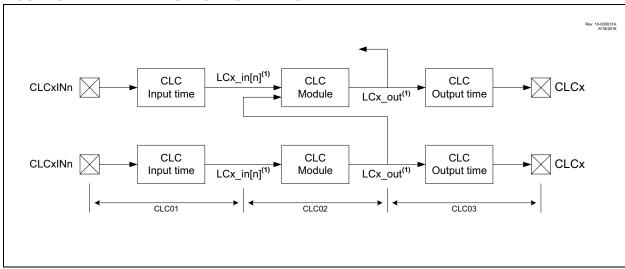

FIGURE 37-14: CLC PROPAGATION TIMING

### TABLE 37-20: CONFIGURABLE LOGIC CELL (CLC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ |                                                              |                                             |   |          |      |          |                          |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|---|----------|------|----------|--------------------------|--|--|--|

| Param.<br>No.                                                                                                                               | Sym   Characteristic   Min   Typt   Max   Units   Conditions |                                             |   |          |      |          |                          |  |  |  |

| CLC01*                                                                                                                                      | TCLCIN                                                       | CLC input time                              | _ | 7        | OS17 | ns       | (Note 1)                 |  |  |  |

| CLC02*                                                                                                                                      | TCLC                                                         | CLC module input to output progagation time |   | 24<br>12 | _    | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |  |  |  |

| CLC03*                                                                                                                                      | TCLCOUT                                                      | CLC output time Rise Time                   | _ | OS18     | _    | _        | (Note 1)                 |  |  |  |

|                                                                                                                                             |                                                              | Fall Time                                   | _ | OS19     | _    | _        | (Note 1)                 |  |  |  |

| CLC04*                                                                                                                                      | FCLCMAX                                                      | CLC maximum switching frequency             | _ | 32       | Fosc | MHz      |                          |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Table 37-10 for OS17, OS18 and OS19 rise and fall times.

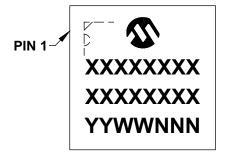

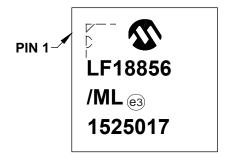

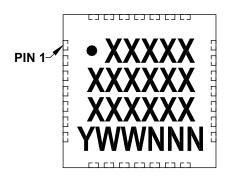

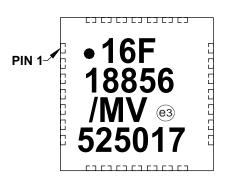

### **40.1** Package Marking Information (Continued)

28-Lead QFN (6x6 mm)

Example

28-Lead UQFN (4x4x0.5 mm)

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

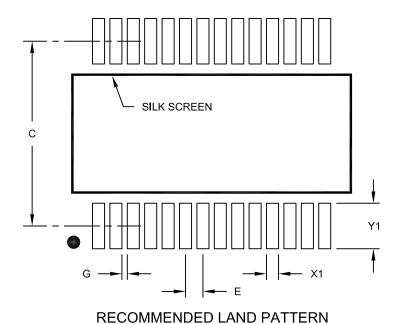

### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**te:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |             |      |      |  |  |

|--------------------------|-------------|-------------|------|------|--|--|

| Dimension                | MIN         | MIN NOM MAX |      |      |  |  |

| Contact Pitch            | E 0.65 BSC  |             |      |      |  |  |

| Contact Pad Spacing      | С           |             | 7.20 |      |  |  |

| Contact Pad Width (X28)  | X1          |             |      | 0.45 |  |  |

| Contact Pad Length (X28) | Y1          |             |      | 1.75 |  |  |

| Distance Between Pads    | G           | 0.20        |      |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A