Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18876-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: 28-PIN ALLOCATION TABLE (PIC16(L)F18856) (CONTINUED)

| O/I                | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC              | Voltage Reference | DAC | Comparators    | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)  | EUSART                                        | WSQ | Timers/SMT | CCP and PWM                                                | CWG                                                                                                      | CLC                                                 | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic |

|--------------------|------------------------|---------------|------------------|-------------------|-----|----------------|-------------------|------------------------------|-----------------------------------------------|-----|------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|------------------------|---------------------|-------|

| OUT <sup>(2)</sup> | _                      |               | ADGRDA<br>ADGRDB | _                 | _   | C1OUT<br>C2OUT |                   | SDO1<br>SCK1<br>SDO2<br>SCK2 | TX/<br>CK <sup>(3)</sup><br>DT <sup>(3)</sup> | DSM | TMR0       | CCP1<br>CCP2<br>CCP3<br>CCP4<br>CCP5<br>PWM60UT<br>PWM70UT | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D<br>CWG2A<br>CWG2B<br>CWG2C<br>CWG2D<br>CWG3D<br>CWG3B<br>CWG3C<br>CWG3D | CLC1OUT<br>CLC2OUT<br>CLC3OUT<br>CLC3OUT<br>CLC4OUT | NCO | CLKR                   |                     | _     |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTX pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

#### **Table of Contents**

| 1.0  | Device Overview                                                           |  |

|------|---------------------------------------------------------------------------|--|

| 2.0  | Enhanced Mid-Range CPU                                                    |  |

| 3.0  | Memory Organization                                                       |  |

| 4.0  | Device Configuration                                                      |  |

| 5.0  | Resets                                                                    |  |

| 6.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          |  |

| 7.0  | Interrupts                                                                |  |

| 8.0  | Power-Saving Operation Modes                                              |  |

| 9.0  | Windowed Watchdog Timer (WWDT)                                            |  |

| 10.0 | Nonvolatile Memory (NVM) Control                                          |  |

| 11.0 | Cyclic Redundancy Check (CRC) Module                                      |  |

| 12.0 | I/O Ports                                                                 |  |

| 13.0 | Peripheral Pin Select (PPS) Module                                        |  |

| 14.0 | Peripheral Module Disable                                                 |  |

| 15.0 | Interrupt-On-Change                                                       |  |

| 16.0 | Fixed Voltage Reference (FVR)                                             |  |

| 17.0 | Temperature Indicator Module                                              |  |

|      | Comparator Module                                                         |  |

| 19.0 | Pulse-Width Modulation (PWM)                                              |  |

| 20.0 | Complementary Waveform Generator (CWG) Module                             |  |

| 21.0 | Zero-Cross Detection (ZCD) Module                                         |  |

| 22.0 | Configurable Logic Cell (CLC)                                             |  |

| 23.0 | Analog-to-Digital Converter With Computation (ADC2) Module                |  |

| 24.0 | Numerically Controlled Oscillator (NCO) Module                            |  |

| 25.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           |  |

| 26.0 | Data Signal Modulator (DSM) Module                                        |  |

| 27.0 | Timer0 Module                                                             |  |

| 28.0 | Timer1/3/5 Module with Gate Control                                       |  |

| 29.0 | Timer2/4/6 Module                                                         |  |

| 30.0 | Capture/Compare/PWM Modules                                               |  |

| 31.0 | Master Synchronous Serial Port (MSSP) Modules                             |  |

| 32.0 |                                                                           |  |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |  |

| 34.0 | Reference Clock Output Module                                             |  |

| 35.0 | In-Circuit Serial Programming™ (ICSP™)                                    |  |

| 36.0 | Instruction Set Summary                                                   |  |

| 37.0 | Electrical Specifications                                                 |  |

| 38.0 | DC and AC Characteristics Graphs and Charts                               |  |

| 39.0 |                                                                           |  |

|      |                                                                           |  |

| Data | Sheet Revision History                                                    |  |

| <b>TABLE 1-2</b> : | PIC16F18856 PINOUT DESCRIPTION (CONTINUED) |

|--------------------|--------------------------------------------|

|--------------------|--------------------------------------------|

| Name                             | Function                                            | Input<br>Type | Output Type                       | Description                                  |

|----------------------------------|-----------------------------------------------------|---------------|-----------------------------------|----------------------------------------------|

| OUT <sup>(2)</sup>               | CWG3C                                               | -             | CMOS/OD                           | Complementary Waveform Generator 3 output C. |

|                                  | CWG3D — CMOS/OD Complementary Waveform Generator    |               |                                   |                                              |

|                                  |                                                     |               | Configurable Logic Cell 1 output. |                                              |

|                                  | CLC2OUT — CMOS/OD Configurable Logic Cell 2 output. |               |                                   |                                              |

|                                  | CLC3OUT                                             | _             | CMOS/OD                           | Configurable Logic Cell 3 output.            |

|                                  | CLC4OUT                                             |               | CMOS/OD                           | Configurable Logic Cell 4 output.            |

|                                  | NCO1                                                |               | CMOS/OD                           | Numerically Controller Oscillator output.    |

|                                  | CLKR                                                | _             | CMOS/OD                           | Clock Reference module output.               |

| Legend: AN = Analog input or out | out CMOS =                                          | CMOS co       | mpatible input or                 | r output OD = Open-Drain                     |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

### 3.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

- Data EEPROM Memory

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 3-1: DEVICE SIZES AND ADDRESSES

| Device            | Program Memory Size (Words) | Last Program Memory Address |

|-------------------|-----------------------------|-----------------------------|

| PIC16(L)F18856/76 | 16,384                      | 3FFFh                       |

#### 3.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 3-1 shows the memory sizes implemented. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 3-1).

| TABLE   | BLE 3-13: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |                                  |               |            |         |         |              |       |           |           |                       |                           |

|---------|--------------------------------------------------------------------|----------------------------------|---------------|------------|---------|---------|--------------|-------|-----------|-----------|-----------------------|---------------------------|

| Address | Name                                                               | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7         | Bit 6      | Bit 5   | Bit 4   | Bit 3        | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR, BOR | Value on all other Resets |

| Bank 8  |                                                                    |                                  |               |            |         |         |              |       |           |           |                       |                           |

|         | CPU CORE REGISTERS; see Table 3-2 for specifics                    |                                  |               |            |         |         |              |       |           |           |                       |                           |

| 40Ch    | SCANLADRL                                                          |                                  |               |            |         |         | LADR<7:0>    |       |           |           | 0000 0000             | 0000 0000                 |

| 40Dh    | SCANLADRH                                                          |                                  | LADR<15:8>    |            |         |         |              |       |           |           | 0000 0000             | 0000 0000                 |

| 40Eh    | SCANHADRL                                                          |                                  | HADR<7:0>     |            |         |         |              |       |           |           |                       | 1111 1111                 |

| 40Fh    | SCANHADRH                                                          |                                  |               |            |         |         | HADR<15:8>   |       |           | 1111 1111 | 1111 1111             |                           |

| 410h    | SCANCON0                                                           |                                  | EN            | SCANGO     | BUSY    | INVALID | INTM         | —     | 0000 0-00 | 0000 0-00 |                       |                           |

| 411h    | SCANTRIG                                                           |                                  | —             | —          | —       | _       |              | TSEL< |           | 0000      | 0000                  |                           |

| 412h    | -                                                                  | —                                | Unimplemented |            |         |         |              |       |           | _         | —                     |                           |

| 413h    | -                                                                  | —                                |               |            |         | U       | nimplemented |       |           |           | -                     | —                         |

| 414h    | -                                                                  | -                                |               |            |         | U       | nimplemented |       |           |           | -                     | -                         |

| 415h    | -                                                                  | —                                |               |            |         | U       | nimplemented |       |           |           | -                     | —                         |

| 416h    | CRCDATL                                                            |                                  |               |            |         |         | DATA<7:0>    |       |           |           | XXXX XXXX             | xxxx xxxx                 |

| 417h    | CRCDATH                                                            |                                  |               |            |         |         | DATA<15:8>   |       |           |           | XXXX XXXX             | xxxx xxxx                 |

| 418h    | CRCACCL                                                            |                                  |               |            |         |         | ACC<7:0>     |       |           |           | 0000 0000             | 0000 0000                 |

| 419h    | CRCACCH                                                            |                                  |               |            |         |         | ACC<15:8>    |       |           |           | 0000 0000             | 0000 0000                 |

| 41Ah    | CRCSHIFTL                                                          |                                  |               | SHIFT<7:0> |         |         |              |       |           |           |                       | 0000 0000                 |

| 41Bh    | CRCSHIFTH                                                          |                                  | SHIFT<15:8>   |            |         |         |              |       |           |           | 0000 0000             | 0000 0000                 |

| 41Ch    | CRCXORL                                                            |                                  |               |            |         | X<7:1>  |              |       |           | —         | xxxx xxx-             | xxxx xxx-                 |

| 41Dh    | CRCXORH                                                            |                                  |               |            |         |         | X<15:8>      |       |           | •         | XXXX XXXX             | xxxx xxxx                 |

| 41Eh    | CRCCON0                                                            |                                  | EN            | CRCGO      | BUSY    | ACCM    | —            | —     | SHIFTM    | FULL      | 000000                | 000000                    |

| 41Fh    | CRCCON1                                                            |                                  |               | DLE        | EN<3:0> |         |              | PLEN< | <3:0>     |           | 0000 0000             | 0000 0000                 |

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 220                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 220                 |

| LATC    | LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 220                 |

| ANSELC  | ANSC7   | ANSC6   | ANSC5   | ANSC4   | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 221                 |

| WPUC    | WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 221                 |

| ODCONC  | ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   | 222                 |

| SLRCONC | SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 222                 |

| INLVLC  | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 222                 |

| CCDPC   | CCDPC7  | CCDPC6  | CCDPC5  | CCDPC4  | CCDPC3  | CCDPC2  | CCDPC1  | CCDPC0  | 223                 |

| CCDNC   | CCDNC7  | CCDNC6  | CCDNC5  | CCDNC4  | CCDNC3  | CCDNC2  | CCDNC1  | CCDNC0  | 223                 |

| CCDCON  | CCDEN   | _       | _       | _       | _       | _       | CCDS    | 6<1:0>  | 201                 |

#### TABLE 12-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3 | Bit 2       | Bit 1 | Bit 0 | Register<br>on page |  |  |  |

|-----------------------|-------|-------|-------|-------------|-------|-------------|-------|-------|---------------------|--|--|--|

| RA4PPS                | —     | _     |       |             | RA    | IPPS<5:0>   |       |       | 250                 |  |  |  |

| RA5PPS                | —     | _     |       |             | RA    | 5PPS<5:0>   |       |       | 250                 |  |  |  |

| RA6PPS                | —     | _     |       |             | RA    | )PPS<5:0>   |       |       | 250                 |  |  |  |

| RA7PPS                | -     | _     |       |             | RA    | 7PPS<5:0>   |       |       | 250                 |  |  |  |

| RB0PPS                | —     | _     |       |             | RB    | )PPS<5:0>   |       |       | 250                 |  |  |  |

| RB1PPS                | —     | _     |       |             | RB    | IPPS<5:0>   |       |       | 250                 |  |  |  |

| RB2PPS                | —     | _     |       |             | RB2   | 2PPS<5:0>   |       |       | 250                 |  |  |  |

| RB3PPS                | —     | _     |       |             | RB    | 3PPS<5:0>   |       |       | 250                 |  |  |  |

| RB4PPS                | —     | _     |       |             | RB4   | IPPS<5:0>   |       |       | 250                 |  |  |  |

| RB5PPS                | —     | _     |       | RB5PPS<5:0> |       |             |       |       |                     |  |  |  |

| RB6PPS                | —     | _     |       | RB6PPS<5:0> |       |             |       |       |                     |  |  |  |

| RB7PPS                | —     | _     |       | RB7PPS<5:0> |       |             |       |       |                     |  |  |  |

| RC0PPS                | —     | _     |       | RC0PPS<5:0> |       |             |       |       |                     |  |  |  |

| RC1PPS                | —     | _     |       | RC1PPS<5:0> |       |             |       |       |                     |  |  |  |

| RC2PPS                | —     | _     |       | RC2PPS<5:0> |       |             |       |       |                     |  |  |  |

| RC3PPS                | —     | _     |       |             | RC    | 3PPS<5:0>   |       |       | 250                 |  |  |  |

| RC4PPS                | —     | _     |       |             | RC4   | 1PPS<5:0>   |       |       | 250                 |  |  |  |

| RC5PPS                | —     | _     |       |             | RC    | 5PPS<5:0>   |       |       | 250                 |  |  |  |

| RC6PPS                | —     | _     |       |             | RC    | 8PPS<5:0>   |       |       | 250                 |  |  |  |

| RC7PPS                | —     | _     |       |             | RC    | 7PPS<5:0>   |       |       | 250                 |  |  |  |

| RD0PPS <sup>(1)</sup> | —     | _     |       |             | RD    | )PPS<5:0>   |       |       | 250                 |  |  |  |

| RD1PPS <sup>(1)</sup> | —     | _     |       |             | RD'   | IPPS<5:0>   |       |       | 250                 |  |  |  |

| RD2PPS <sup>(1)</sup> | —     | _     |       |             | RD2   | 2PPS<5:0>   |       |       | 250                 |  |  |  |

| RD3PPS <sup>(1)</sup> | —     | _     |       |             | RD    | 3PPS<5:0>   |       |       | 250                 |  |  |  |

| RD4PPS <sup>(1)</sup> | —     | _     |       |             | RD4   | 1PPS<5:0>   |       |       | 250                 |  |  |  |

| RD5PPS <sup>(1)</sup> | —     | _     |       |             | RD    | 5PPS<5:0>   |       |       | 250                 |  |  |  |

| RD6PPS <sup>(1)</sup> | —     | _     |       |             | RD    | 6PPS<5:0>   |       |       | 250                 |  |  |  |

| RD7PPS <sup>(1)</sup> | _     | _     |       |             | RD    | 7PPS<5:0>   |       |       | 250                 |  |  |  |

| RE0PPS <sup>(1)</sup> | _     | _     |       |             | REG   | )PPS<5:0>   |       |       | 250                 |  |  |  |

| RE1PPS <sup>(1)</sup> | _     | _     |       |             | RE    | IPPS<5:0>   |       |       | 250                 |  |  |  |

| RE2PPS <sup>(1)</sup> | _     | _     |       |             | RE2   | RE2PPS<5:0> |       |       |                     |  |  |  |

#### TABLE 13-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

Legend:

— = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note

1:

PIC16F18875PIC16F18876 only.

| ILE OID I EIL | 14 0. I MID4 |         |         |     |         |         |         |

|---------------|--------------|---------|---------|-----|---------|---------|---------|

| U-0           | R/W-0/0      | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

| —             | UART1MD      | MSSP2MD | MSSP1MD |     | CWG3MD  | CWG2MD  | CWG1MD  |

| bit 7         |              |         |         |     |         |         | bit 0   |

|               |              |         |         |     |         |         |         |

### REGISTER 14-5: PMD4: PMD CONTROL REGISTER 4

| Legend:      |            |                                       |                                                       |

|--------------|------------|---------------------------------------|-------------------------------------------------------|

| R = Read     | lable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'                    |

| u = Bit is   | unchanged  | x = Bit is unknown                    | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is | set        | '0' = Bit is cleared                  | q = Value depends on condition                        |

| L:1 7        |            |                                       |                                                       |

| bit 7        | •          | nted: Read as '0'                     |                                                       |

| bit 6        |            | Disable EUSART bit                    |                                                       |

|              |            | T module disabled<br>T module enabled |                                                       |

|              |            |                                       |                                                       |

| bit 5        |            | Disable MSSP2 bit module disabled     |                                                       |

|              |            | module enabled                        |                                                       |

| bit 4        |            | Disable MSSP1 bit                     |                                                       |

|              |            | module disabled                       |                                                       |

|              |            | module enabled                        |                                                       |

| bit 3        | Unimpleme  | nted: Read as '0'                     |                                                       |

| bit 2        | CWG3MD: [  | Disable CWG3 bit                      |                                                       |

|              | 1 = CWG3 r | module disabled                       |                                                       |

|              | 0 = CWG3 r | nodule enabled                        |                                                       |

| bit 1        | CWG2MD:    | Disable CWG2 bit                      |                                                       |

|              |            | module disabled                       |                                                       |

|              | 0 = CWG2 r | module enabled                        |                                                       |

| bit 0        |            | Disable CWG1 bit                      |                                                       |

|              |            | nodule disabled                       |                                                       |

|              | 0 = CWG1 r | nodule enabled                        |                                                       |

#### **REGISTER 15-4:** IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBP7  | IOCBP6  | IOCBP5  | IOCBP4  | IOCBP3  | IOCBP2  | IOCBP1  | IOCBP0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 IOCBP<7:0>: Interrupt-on-Change PORTB Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 15-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   | •       |         |         | •       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCBN<7:0>:** Interrupt-on-Change PORTB Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 15-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      | •          |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF<7:0>: Interrupt-on-Change PORTB Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

#### 18.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 37-14 for more details.

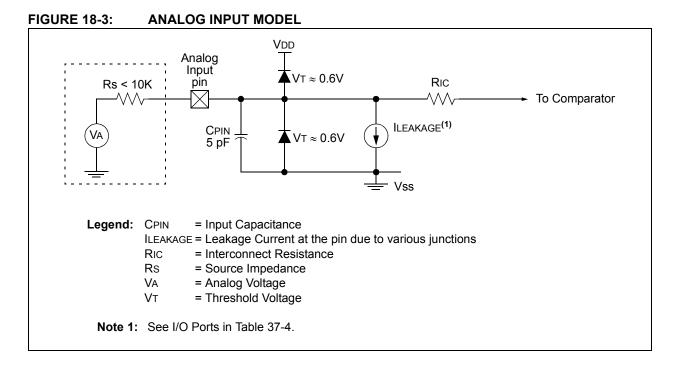

#### 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 20.5 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWGxDBR and CWGxDBF registers, respectively.

#### 20.5.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 20-9.

#### 20.5.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWGxCON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWGxA and CWGxC signals will change immediately upon the first rising input edge following a direction change, but the modulated signals (CWGxB or CWGxD, depending on the direction of the change) will experience a delay dictated by the dead-band counters. This is demonstrated in Figure 20-3.

#### 20.6 Rising Edge and Reverse Dead Band

CWGxDBR controls the rising edge dead-band time at the leading edge of CWGxA (Half-Bridge mode) or the leading edge of CWGxB (Full-Bridge mode). The CWGxDBR value is double-buffered. When EN = 0, the CWGxDBR register is loaded immediately when CWGxDBR is written. When EN = 1, then software must set the LD bit of the CWGxCON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

### 20.7 Falling Edge and Forward Dead Band

CWGxDBF controls the dead-band time at the leading edge of CWGxB (Half-Bridge mode) or the leading edge of CWGxD (Full-Bridge mode). The CWGxDBF value is double-buffered. When EN = 0, the CWGxDBF register is loaded immediately when CWGxDBF is written. When EN = 1 then software must set the LD bit of the CWGxCON0 register, and the buffer will be loaded at the next falling edge of the CWG input signal. If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output. Refer to Figure 20.6 and Figure 20-7 for examples.

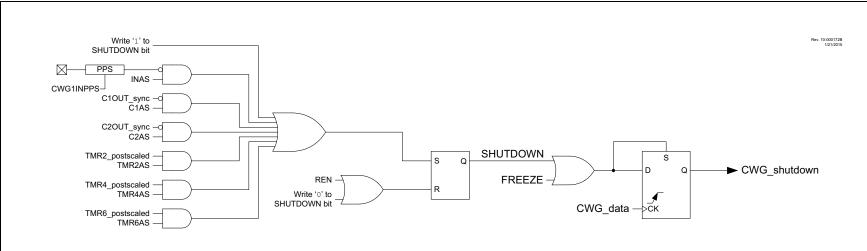

#### FIGURE 20-12: CWG SHUTDOWN BLOCK DIAGRAM

PIC16(L)F18856/76

#### 23.4.1 CVD OPERATION

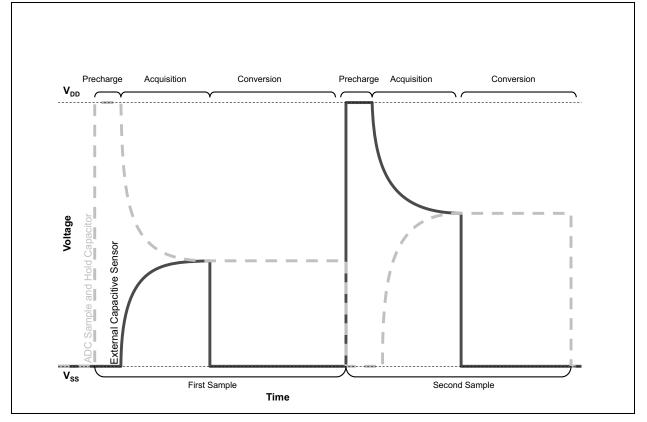

A CVD operation begins with the ADC's internal (C<sub>HOLD</sub>) sample and hold capacitor being disconnected from the path which connects it to the external capacitive sensor node. While disconnected, CHOLD is precharged to VDD or Vss, while the path to the sensor node is also discharged to VDD or VSS. Typically, this node is discharged to the level opposite that of CHOLD. When the precharge phase is complete, the VDD/VSS bias paths for the two nodes are shut off and CHOLD and the path to the external sensor node are reconnected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, which results in a final voltage level setting on CHOLD which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with the selected precharge levels for both the CHOLD and the inverted sensor nodes. Figure 23-7 shows the waveform for two inverted CVD measurements, which is known as differential CVD measurement.

#### REGISTER 23-2: ADCON1: ADC CONTROL REGISTER 1

| R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|---------|---------|-----|-----|-----|-----|---------|

| ADPPOL  | ADIPEN  | ADGPOL  | —   | —   | —   | _   | ADDSEN  |

| bit 7   |         |         |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7 ADDPOL: Precharge Polarity bit If ADPRE>0x00:

| ADPPOL | Action During 1st Precharge Stage  |                                   |  |  |  |  |  |

|--------|------------------------------------|-----------------------------------|--|--|--|--|--|

| ADFFUL | External (selected analog I/O pin) | Internal (AD sampling capacitor)  |  |  |  |  |  |

| 1      | Shorted to AVDD                    | C <sub>HOLD</sub> shorted to Vss  |  |  |  |  |  |

| 0      | Shorted to Vss                     | C <sub>HOLD</sub> shorted to AVDD |  |  |  |  |  |

|         | <u>Otherwise</u>                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------|

|         | The bit is ignored                                                                                              |

| bit 6   | ADIPEN: A/D Inverted Precharge Enable bit                                                                       |

|         | If ADDSEN = 1:                                                                                                  |

|         | 1 = The precharge and guard signals in the second conversion cycle are the opposite polarity of the first cycle |

|         | 0 = Both Conversion cycles use the precharge and guards specified by ADPPOL and ADGPOL                          |

|         | <u>Otherwise</u> :                                                                                              |

|         | The bit is ignored                                                                                              |

| bit 5   | ADGPOL: Guard Ring Polarity Selection bit                                                                       |

|         | 1 = ADC guard ring outputs start as digital high during precharge stage                                         |

|         | 0 = ADC guard ring outputs start as digital low during precharge stage                                          |

| bit 4-1 | Unimplemented: Read as '0'                                                                                      |

| bit 0   | ADDSEN: Double-Sample Enable bit                                                                                |

|         | 1 = See Table 23-5.                                                                                             |

|         | 0 = One conversion is performed for each trigger                                                                |

|         |                                                                                                                 |

#### TABLE 23-5: EXAMPLE OF REGISTER VALUES FOR ACCUMULATE AND AVERAGE MODES

| Trig<br>ADC | jger<br>ONT | Sample | ADRES | ADPREV<br>ADPSIS |             | ADACC             |

|-------------|-------------|--------|-------|------------------|-------------|-------------------|

| 0           | 1           | n      |       | 0                | 1           |                   |

| T1          | T1          | 1      | S(n)  | S(n-1)           | ADFLTR(n-1) | ADACC(n-1)-S(n-1) |

| T2          | _           | 2      | S(n)  | S(n-1)           | ADFLTR(n-2) | ADACC(n-1)+S(n-1) |

| Т3          | T2          | 3      | S(n)  | S(n-1)           | ADFLTR(n-1) | ADACC(n-1)-S(n-1) |

| T4          |             | 4      | S(n)  | S(n-1)           | ADFLTR(n-2) | ADACC(n-1)+S(n-1) |

| T5          | Т3          | 5      | S(n)  | S(n-1)           | ADFLTR(n-1) | ADACC(n-1)-S(n-1) |

| Т6          |             | 6      | S(n)  | S(n-1)           | ADFLTR(n-2) | ADACC(n-1)+S(n-1) |

### 27.0 TIMER0 MODULE

The Timer0 module is an 8/16-bit timer/counter with the following features:

- 16-bit timer/counter

- 8-bit timer/counter with programmable period

- Synchronous or asynchronous operation

- · Selectable clock sources

- Programmable prescaler (independent of Watchdog Timer)

- Programmable postscaler

- Operation during Sleep mode

- · Interrupt on match or overflow

- Output on I/O pin (via PPS) or to other peripherals

#### 27.1 Timer0 Operation

Timer0 can operate as either an 8-bit timer/counter or a 16-bit timer/counter. The mode is selected with the T016BIT bit of the T0CON register.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or a counter and increments on every rising edge of the external source.

#### 27.1.1 16-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

### 27.1.1.1 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode. It is actually a buffered version of the real high byte of Timer0, which is neither directly readable nor writable (see Figure 27-1). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0 without having to verify that the read of the high and low byte was valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

#### 27.1.2 8-BIT MODE

In normal operation, TMR0 increments on the rising edge of the clock source. A 15-bit prescaler on the clock input gives several prescale options (see prescaler control bits, T0CKPS<3:0> in the T0CON1 register).

The value of TMR0L is compared to that of the Period buffer, a copy of TMR0H, on each clock cycle. When the two values match, the following events happen:

- TMR0\_out goes high for one prescaled clock period

- TMR0L is reset

- The contents of TMR0H are copied to the period buffer

In 8-bit mode, the TMR0L and TMR0H registers are both directly readable and writable. The TMR0L register is cleared on any device Reset, while the TMR0H register initializes at FFh.

Both the prescaler and postscaler counters are cleared on the following events:

- A write to the TMR0L register

- A write to either the T0CON0 or T0CON1 registers

- Any device Reset Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or

- Brown-out Reset (BOR)

#### 27.1.3 COUNTER MODE

In Counter mode, the prescaler is normally disabled by setting the T0CKPS bits of the T0CON1 register to '0000'. Each rising edge of the clock input (or the output of the prescaler if the prescaler is used) increments the counter by '1'.

#### 27.1.4 TIMER MODE

In Timer mode, the Timer0 module will increment every instruction cycle as long as there is a valid clock signal and the T0CKPS bits of the T0CON1 register (Register 27-2) are set to '0000'. When a prescaler is added, the timer will increment at the rate based on the prescaler value.

#### 27.1.5 ASYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is set (T0ASYNC = '1'), the counter increments with each rising edge of the input source (or output of the prescaler, if used). Asynchronous mode allows the counter to continue operation during Sleep mode provided that the clock also continues to operate during Sleep.

#### 27.1.6 SYNCHRONOUS MODE

When the T0ASYNC bit of the T0CON1 register is clear (T0ASYNC = 0), the counter clock is synchronized to the system oscillator (Fosc/4). When operating in Synchronous mode, the counter clock frequency cannot exceed Fosc/4.

#### 27.2 Clock Source Selection

The T0CS<2:0> bits of the T0CON1 register are used to select the clock source for Timer0. Register 27-2 displays the clock source selections.

#### 29.7 Register Definitions: Timer2/4/6 Control

Long bit name prefixes for the Timer2/4/6 peripherals are shown in Table 29-2. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information TABLE 29-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer2     | T2              |

| Timer4     | T4              |

| Timer6     | Т6              |

#### REGISTER 29-1: TxCLKCON: TIMER2/4/6 CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | —   | _   | CS<3:0> |         |         |         |

| bit 7 |     | •   |     | -       |         |         | bit 0   |

| Legend:                                                    |          |                              |                                                       |

|------------------------------------------------------------|----------|------------------------------|-------------------------------------------------------|

| R = Readable bit                                           |          | W = Writable bit             | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged                                       |          | x = Bit is unknown           | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set                                           |          | '0' = Bit is cleared         |                                                       |

| bit 7-4                                                    | Unimpler | nented: Read as '0'          |                                                       |

| bit 3-0 <b>CS&lt;3:0&gt;:</b> Timer2/4/6 Clock Select bits |          | Timer2/4/6 Clock Select bits | ;                                                     |

| bit 3-0 | CS<3:0>: Timer2/4/6 Clock Select bits |

|---------|---------------------------------------|

|         | 1111 = Reserved                       |

|         | 1110 = Reserved                       |

|         | 1101 = LC4_out                        |

|         | 1100 = LC3_out                        |

|         | 1011 = LC2_out                        |

|         | 1010 = LC1_out                        |

|         | 1001 = ZCD1_output                    |

|         | 1000 = NCO output                     |

|         | 0111 = CLKR                           |

|         | 0110 <b>= S</b> osc                   |

|         | 0101 = MFINTOSC/16 (31.25 kHz)        |

|         | 0100 = LFINTOSC                       |

|         | 0011 = HFINTOSC (16 MHz)              |

|         | 0010 = Fosc                           |

|         | 0001 = Fosc/4                         |

|         | 0000 = TxCKIPPS                       |

|         |                                       |

| .,       |                                              |                                             |                          |        |                         |           | -       |        |                     |

|----------|----------------------------------------------|---------------------------------------------|--------------------------|--------|-------------------------|-----------|---------|--------|---------------------|

| Name     | Bit 7                                        | Bit 6                                       | Bit 5                    | Bit 4  | Bit 3                   | Bit 2     | Bit 1   | Bit 0  | Register<br>on Page |

| CCP1CON  | EN                                           | _                                           | - OUT FMT                |        |                         | MODE<3:0> |         |        |                     |

| CCP2CON  | EN                                           | _                                           | OUT                      | FMT    |                         | MODE      | =<3:0>  |        | 452                 |

| CCPTMRS0 | C4TSE                                        | L<1:0>                                      | C3TSE                    | L<1:0> | C2TSEL<1:0> C1TSEL<1:0> |           |         |        | 455                 |

| CCPTMRS1 | —                                            | —                                           | P7TSE                    | L<1:0> | P6TSEL<1:0> C5TSEL<1:0> |           |         | L<1:0> | 455                 |

| INTCON   | GIE                                          | PEIE                                        | _                        | —      | —                       | —         | —       | INTEDG | 134                 |

| PIE1     | OSFIE                                        | CSWIE                                       | —                        | —      | —                       | _         | ADTIE   | ADIE   | 136                 |

| PIR1     | OSFIF                                        | CSWIF                                       | —                        | —      | —                       | _         | ADTIF   | ADIF   | 145                 |

| PR2      | Timer2 Mod                                   | ule Period Re                               | gister                   |        |                         |           |         | L      | 425*                |

| TMR2     | Holding Reg                                  | olding Register for the 8-bit TMR2 Register |                          |        |                         |           |         | 425*   |                     |

| T2CON    | ON                                           |                                             | CKPS<2:0> OUTPS<3:0>     |        |                         |           |         |        | 441                 |

| T2CLKCON | _                                            | _                                           | — — — CS<3:0>            |        |                         |           |         | 440    |                     |

| T2RST    | —                                            | _                                           | — RSEL<4:0>              |        |                         |           |         | 443    |                     |

| T2HLT    | PSYNC                                        | CKPOL CKSYNC - MODE                         |                          |        |                         | E<3:0>    |         | 442    |                     |

| PR4      | Timer4 Module Period Register                |                                             |                          |        |                         |           | 425*    |        |                     |

| TMR4     | Holding Register for the 8-bit TMR4 Register |                                             |                          |        |                         |           | 425*    |        |                     |

| T4CON    | ON                                           | CKPS<2:0>                                   |                          |        | OUTPS<3:0>              |           |         |        | 441                 |

| T4CLKCON | —                                            | _                                           | _                        | _      | —                       |           | CS<3:0> |        | 440                 |

| T4RST    | _                                            | — — RSEL<4:0>                               |                          |        |                         |           |         | 443    |                     |

| T4HLT    | PSYNC                                        | CKPOL                                       | CKPOL CKSYNC — MODE<3:0> |        |                         |           | 442     |        |                     |

| PR6      | Timer6 Mod                                   | ner6 Module Period Register                 |                          |        |                         |           |         | 425*   |                     |

| TMR6     | Holding Register for the 8-bit TMR6 Register |                                             |                          |        |                         |           | 425*    |        |                     |

| T6CON    | ON                                           | CKPS<2:0>                                   |                          |        | OUTPS<3:0>              |           |         | 441    |                     |

| T6CLKCON |                                              | _                                           | —                        | —      | —                       |           | CS<2:0> |        | 440                 |

| T6RST    | —                                            | -                                           | _                        |        |                         | RSEL<4:0> |         |        | 443                 |

| T6HLT    | PSYNC                                        | CKPOL                                       | CKSYNC                   | _      |                         | MODE      | E<3:0>  |        | 442                 |

#### TABLE 29-3: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

#### **REGISTER 30-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE**

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | CCPRx   | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

bit 7-0

CCPxMODE = Capture mode

CCPRxH<7:0>: Captured value of TMR1H

CCPxMODE = Compare mode

CCPRxH<7:0>: MS Byte compared to TMR1H

CCPxMODE = PWM modes when CCPxFMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<1:0>: Pulse-width Most Significant two bits

CCPxMODE = PWM modes when CCPxFMT = 1:

CCPRxH<7:0>: Pulse-width Most Significant eight bits

#### REGISTER 30-5: CCPTMRS0: CCP TIMERS CONTROL 0 REGISTER

| R/W-0/0     | R/W-1/1 | R/W-0/0     | R/W-1/1 | R/W-0/0     | R/W-1/1 | R/W-0/0     | R/W-1/1 |

|-------------|---------|-------------|---------|-------------|---------|-------------|---------|

| C4TSEL<1:0> |         | C3TSEL<1:0> |         | C2TSEL<1:0> |         | C1TSEL<1:0> |         |

| bit 7       |         |             |         |             | bit 0   |             |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

| bit 7-6 | C4TSEL<1:0>: CCP4 Timer Selection<br>11 = CCP4 based on TMR5 (Capture/Compare) or TMR6 (PWM)<br>10 = CCP4 based on TMR3 (Capture/Compare) or TMR4 (PWM)<br>01 = CCP4 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | C3TSEL<1:0>: CCP4 Timer Selection<br>11 = CCP3 based on TMR5 (Capture/Compare) or TMR6 (PWM)<br>10 = CCP3 based on TMR3 (Capture/Compare) or TMR4 (PWM)<br>01 = CCP3 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved              |

| bit 3-2 | <b>C2TSEL&lt;1:0&gt;:</b> CCP4 Timer Selection<br>11 = CCP2 based on TMR5 (Capture/Compare) or TMR6 (PWM)<br>10 = CCP2 based on TMR3 (Capture/Compare) or TMR4 (PWM)<br>01 = CCP2 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved |

| bit 1-0 | C1TSEL<1:0>: CCP4 Timer Selection<br>11 = CCP1 based on TMR5 (Capture/Compare) or TMR6 (PWM)<br>10 = CCP1 based on TMR3 (Capture/Compare) or TMR4 (PWM)<br>01 = CCP1 based on TMR1 (Capture/Compare) or TMR2 (PWM)<br>00 = Reserved              |

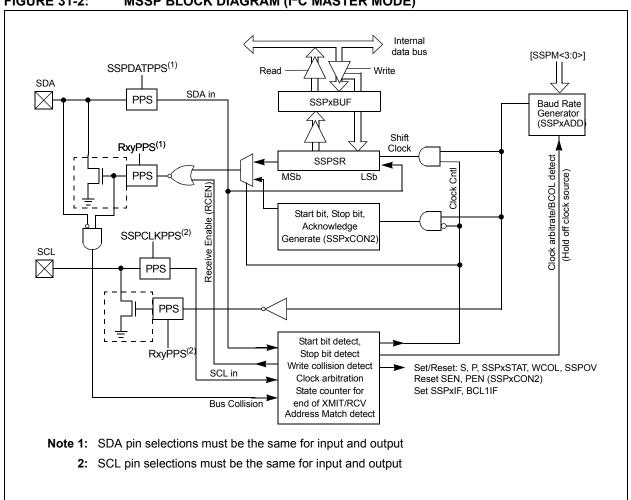

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- · Slave mode

- Byte NACKing (Slave mode)

- · Limited multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- · Clock stretching

- · Bus collision detection

- General call address matching

- · Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 31-2 is a block diagram of the I<sup>2</sup>C interface module in Master mode. Figure 31-3 is a diagram of the I<sup>2</sup>C interface module in Slave mode.

Note 1: In devices with more than one MSSP module, it is very important to pay close attention to SSPxCONx register names. SSPxCON1 and SSPxCON2 registers control different operational aspects of the same module, while SSPxCON1 and SSP2CON1 control the same features for two different modules.

2: Throughout this section, generic references to an MSSPx module in any of its operating modes may be interpreted as being equally applicable to MSSPx or MSSP2. Register names, module I/O signals, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required.

#### MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE) **FIGURE 31-2:**

#### 31.5.3 SLAVE TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register, and an ACK pulse is sent by the slave on the ninth bit.

Following the ACK, slave hardware clears the CKP bit and the SCL pin is held low (see **Section 31.5.6** "**Clock Stretching**" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data.

The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then the SCL pin should be released by setting the CKP bit of the SSPxCON1 register. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time.

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. This ACK value is copied to the ACKSTAT bit of the SSPxCON2 register. If ACKSTAT is set (not ACK), then the data transfer is complete. In this case, when the not ACK is latched by the slave, the slave goes idle and waits for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, the SCL pin must be released by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared by software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 31.5.3.1 Slave Mode Bus Collision

A slave receives a read request and begins shifting data out on the SDA line. If a bus collision is detected and the SBCDE bit of the SSPxCON3 register is set, the BCL1IF bit of the PIR3 register is set. Once a bus collision is detected, the slave goes idle and waits to be addressed again. User software can use the BCL1IF bit to handle a slave bus collision.

#### 31.5.3.2 7-bit Transmission

A master device can transmit a read request to a slave, and then clock data out of the slave. The list below outlines what software for a slave will need to do to accomplish a standard transmission. Figure 31-18 can be used as a reference to this list.

- 1. Master sends a Start condition on SDA and SCL.

- 2. S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit set is received by the Slave setting SSPxIF bit.

- 4. Slave hardware generates an ACK and sets SSPxIF.

- 5. SSPxIF bit is cleared by user.

- 6. Software reads the received address from SSPxBUF, clearing BF.

- 7.  $R/\overline{W}$  is set so CKP was automatically cleared after the ACK.

- 8. The slave software loads the transmit data into SSPxBUF.

- 9. CKP bit is set releasing SCL, allowing the master to clock the data out of the slave.

- 10. SSPxIF is set after the ACK response from the master is loaded into the ACKSTAT register.

- 11. SSPxIF bit is cleared.

- 12. The slave software checks the ACKSTAT bit to see if the master wants to clock out more data.

- Note 1: If the master ACKs the clock will be stretched.

- ACKSTAT is the only bit updated on the rising edge of SCL (9th) rather than the falling.

- 13. Steps 9-13 are repeated for each transmitted byte.

- 14. If the master sends a not ACK; the clock is not held, but SSPxIF is still set.

- 15. The master sends a Restart condition or a Stop.

- 16. The slave is no longer addressed.