#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18856-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## TABLE 3-5:PIC16F18856/76 MEMORY MAP BANK 8-15

|       | BANK 8         |       | BANK 9         |       | BANK 10        |      | BANK 11        |       | BANK 12        |      | BANK 13        |      | BANK 14        |       | BANK 15        |

|-------|----------------|-------|----------------|-------|----------------|------|----------------|-------|----------------|------|----------------|------|----------------|-------|----------------|

| 400h  |                | 480h  |                | 500h  |                | 580h |                | 600h  |                | 680h |                | 700h |                | 780h  |                |

|       | Core Registers |       | Core Registers |       | Core Registers |      | Core Registers |       | Core Registers |      | Core Registers |      | Core Registers |       | Core Registers |

|       | (Table 3-2)    |       | (Table 3-2)    |       | (Table 3-2)    |      | (Table 3-2)    |       | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |       | (Table 3-2)    |

| 40Bh  |                | 48Bh  |                | 50Bh  |                | 58Bh |                | 60Bh  |                | 68Bh |                | 70Bh |                | 78Bh  |                |

| 40Ch  | SCANLADRL      | 48Ch  | SMT1TMRL       | 50Ch  | SMT2TMRL       | 58Ch | NCO1ACCL       | 60Ch  | CWG1CLKCON     | 68Ch | CWG3CLKCON     | 70Ch | PIR0           | 78Ch  | —              |

| 40Dh  | SCANLADRH      | 48Dh  | SMT1TMRH       | 50Dh  | SMT2TMRH       | 58Dh | NCO1ACCH       | 60Dh  | CWG1ISM        | 68Dh | CWG3ISM        | 70Dh | PIR1           | 78Dh  | _              |

| 40Eh  | SCANHADRL      | 48Eh  | SMT1TMRU       | 50Eh  | SMT2TMRU       | 58Eh | NCO1ACCU       | 60Eh  | CWG1DBR        | 68Eh | CWG3DBR        | 70Eh | PIR2           | 78Eh  | —              |

| 40Fh  | SCANHADRH      | 48Fh  | SMT1CPRL       | 50Fh  | SMT2CPRL       | 58Fh | NCO1INCL       | 60Fh  | CWG1DBF        | 68Fh | CWG3DBF        | 70Fh | PIR3           | 78Fh  | —              |

| 410h  | SCANCON0       | 490h  | SMT1CPRH       | 510h  | SMT2CPRH       | 590h | NCO1INCH       | 610h  | CWG1CON0       | 690h | CWG3CON0       | 710h | PIR4           | 790h  | _              |

| 411h  | SCANTRIG       | 491h  | SMT1CPRU       | 511h  | SMT2CPRU       | 591h | NCO1INCU       | 611h  | CWG1CON1       | 691h | CWG3CON1       | 711h | PIR5           | 791h  | —              |

| 412h  | -              | 492h  | SMT1CPWL       | 512h  | SMT2CPWL       | 592h | NCO1CON        | 612h  | CWG1AS0        | 692h | CWG3AS0        | 712h | PIR6           | 792h  | —              |

| 413h  | —              | 493h  | SMT1CPWH       | 513h  | SMT2CPWH       | 593h | NCO1CLK        | 613h  | CWG1AS1        | 693h | CWG3AS1        | 713h | PIR7           | 793h  | —              |

| 414h  | -              | 494h  | SMT1CPWU       | 514h  | SMT2CPWU       | 594h | —              | 614h  | CWG1STR        | 694h | CWG3STR        | 714h | PIR8           | 794h  | —              |

| 415h  | —              | 495h  | SMT1PRL        | 515h  | SMT2PRL        | 595h | —              | 615h  | —              | 695h | —              | 715h | —              | 795h  | —              |

| 416h  | CRCDATL        | 496h  | SMT1PRH        | 516h  | SMT2PRH        | 596h | —              | 616h  | CWG2CLKCON     | 696h | —              | 716h | PIE0           | 796h  | PMD0           |

| 417h  | CRCDATH        | 497h  | SMT1PRU        | 517h  | SMT2PRU        | 597h | _              | 617h  | CWG2ISM        | 697h | _              | 717h | PIE1           | 797h  | PMD1           |

| 418h  | CRCACCL        | 498h  | SMT1CON0       | 518h  | SMT2CON0       | 598h | _              | 618h  | CWG2DBR        | 698h | -              | 718h | PIE2           | 798h  | PMD2           |

| 419h  | CRCACCH        | 499h  | SMT1CON1       | 519h  | SMT2CON1       | 599h | —              | 619h  | CWG2DBF        | 699h | -              | 719h | PIE3           | 799h  | PMD3           |

| 41Ah  | CRCSHIFTL      | 49Ah  | SMT1STAT       | 51Ah  | SMT2STAT       | 59Ah | _              | 61Ah  | CWG2CON0       | 69Ah | —              | 71Ah | PIE4           | 79Ah  | PMD4           |

| 41Bh  | CRCSHIFTH      | 49Bh  | SMT1CLK        | 51Bh  | SMT2CLK        | 59Bh | —              | 61Bh  | CWG2CON1       | 69Bh | —              | 71Bh | PIE5           | 79Bh  | PMD5           |

| 41Ch  | CRCXORL        | 49Ch  | SMT1SIG        | 51Ch  | SMT2SIG        | 59Ch | _              | 61Ch  | CWG2AS0        | 69Ch | —              | 71Ch | PIE6           | 79Ch  | —              |

| 41Dh  | CRCXORH        | 49Dh  | SMT1WIN        | 51Dh  | SMT2WIN        | 59Dh | —              | 61Dh  | CWG2AS1        | 69Dh | —              | 71Dh | PIE7           | 79Dh  | —              |

| 41Eh  | CRCCON0        | 49Eh  | —              | 51Eh  | —              | 59Eh | —              | 61Eh  | CWG2STR        | 69Eh | -              | 71Eh | PIE8           | 79Eh  | —              |

| 41Fh  | CRCCON1        | 49Fh  | —              | 51Fh  | —              | 59Fh | —              | 61Fh  | —              | 69Fh | —              | 71Fh | —              | 79Fh  | —              |

| 420h  |                | 4A0h  |                | 520h  |                | 5A0h |                | 620h  |                | 6A0h |                | 720h |                | 7A0h  |                |

|       | General        |       | General        |       | General        |      | General        |       | General        |      | General        |      | General        |       | General        |

|       | Purpose        |       | Purpose        |       | Purpose        |      | Purpose        |       | Purpose        |      | Purpose        |      | Purpose        |       | Purpose        |

|       | Register       |       | Register       |       | Register       |      | Register       |       | Register       |      | Register       |      | Register       |       | Register       |

|       | 80 Bytes       |       | 80 Bytes       |       | 80 Bytes       |      | 80 Bytes       |       | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |       | 80 Bytes       |

| 46Fh  |                | 4EFh  |                | 56Fh  |                | 5EFh |                | 66Fh  |                | 6EFh |                | 76Fh |                | 7EFh  |                |

| 470h  | Common RAM     | 4F0h  | Common RAM     | 570h  | Common RAM     | 5F0h | Common RAM     | 670h  | Common RAM     | 6F0h | Common RAM     | 770h | Common RAM     | 7F0h  | Common RAM     |

|       | Accesses       |       | Accesses       |       | Accesses       |      | Accesses       |       | Accesses       |      | Accesses       |      | Accesses       |       | Accesses       |

| 47Fh  | 70h – 7Fh      | 4FFh  | 70h – 7Fh      | 57Fh  | 70h – 7Fh      | 5FFh | 70h – 7Fh      | 67Fh  | 70h – 7Fh      | 6FFh | 70h – 7Fh      | 77Fh | 70h – 7Fh      | 7FFh  | 70h – 7Fh      |

| 4/111 |                | +1111 |                | 5/111 |                | 5111 |                | 0/111 |                |      |                |      |                | (1111 |                |

**Legend:** = Unimplemented data memory locations, read as '0'.

## 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 8.0** "**Power-Saving Operation Modes**" for more details.

## 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

## 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

## 8.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-On-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 8-1, the interrupt occurs during the 2<sup>nd</sup> instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

## 8.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the IDLE mode (Section 8.2.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set

- 4. The CPU clock is disabled

- 5. 31 kHz LFINTOSC, HFINTOSC and SOSC are unaffected and peripherals using them may continue operation in Sleep.

- Timer1 and peripherals that use it continue to operate in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary Oscillator

- 7. ADC is unaffected if the dedicated FRC oscillator is selected

- 8. I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance)

- 9. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 25.0 "5-Bit Digital-to-Analog Converter (DAC1) Module" and 16.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

## 8.2.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled.

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled.

- 5. Any external interrupt.

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 5.11 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

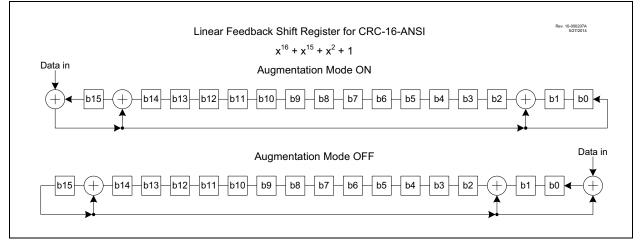

## FIGURE 11-1: CRC LFSR EXAMPLE

## 11.4 CRC Data Sources

Data can be input to the CRC module in two ways:

- User data using the CRCDAT registers

- Flash using the Program Memory Scanner

To set the number of bits of data, up to 16 bits, the DLEN bits of CRCCON1 must be set accordingly. Only data bits in CRCDATA registers up to DLEN will be used, other data bits in CRCDATA registers will be ignored.

Data is moved into the CRCSHIFT as an intermediate to calculate the check value located in the CRCACC registers.

The SHIFTM bit is used to determine the bit order of the data being shifted into the accumulator. If SHIFTM is not set, the data will be shifted in MSb first. The value of DLEN will determine the MSb. If SHIFTM bit is set, the data will be shifted into the accumulator in reversed order, LSb first.

The CRC module can be seeded with an initial value by setting the CRCACC<15:0> registers to the appropriate value before beginning the CRC.

## 11.4.1 CRC FROM USER DATA

To use the CRC module on data input from the user, the user must write the data to the CRCDAT registers. The data from the CRCDAT registers will be latched into the shift registers on any write to the CRCDATL register.

## 11.4.2 CRC FROM FLASH

To use the CRC module on data located in Flash memory, the user can initialize the Program Memory Scanner as defined in **Section 11.8, Program Memory Scan Configuration**.

## 11.5 CRC Check Value

The CRC check value will be located in the CRCACC registers after the CRC calculation has finished. The check value will depend on two mode settings of the CRCCON: ACCM and SHIFTM.

If the ACCM bit is set, the CRC module will augment the data with a number of zeros equal to the length of the polynomial to find the final check value. If the ACCM bit is not set, the CRC will stop at the end of the data. A number of zeros equal to the length of the polynomial can then be entered to find the same check value as augmented mode, alternatively the expected check value can be entered at this point to make the final result equal to 0.

A final XOR value may be needed with the check value to find the desired CRC result

## 11.6 CRC Interrupt

The CRC will generate an interrupt when the BUSY bit transitions from '1' to '0'. The CRCIF interrupt flag bit of the PIR6 register is set every time the BUSY bit transitions, regardless of whether or not the CRC interrupt is enabled. The CRCIF bit can only be cleared in software. The CRC interrupt enable is the CRCIE bit of the PIE6 register.

u = Bit is unchanged

| U-0                                                                  | U-0 | U-0 | U-0 | U-0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------------------------------------------------------------------|-----|-----|-----|--------|---------|---------|---------|

| —                                                                    | _   | _   | _   | _      | CCDPE2  | CCDPE1  | CCDPE0  |

| bit 7 bit 0                                                          |     |     |     |        |         |         |         |

|                                                                      |     |     |     |        |         |         |         |

| Legend:                                                              |     |     |     |        |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |     | as '0' |         |         |         |

-n/n = Value at POR and BOR/Value at all other Resets

### **REGISTER 12-53: CCDPE: CURRENT CONTROL DRIVE NEGATIVE PORTE REGISTER**

| '1' = Bit is set      | '0' = Bit is cleared                                                           |

|-----------------------|--------------------------------------------------------------------------------|

| <b>h</b> # <b>7</b> 0 | Unimplemented: Deed on (o)                                                     |

| bit 7-3               | Unimplemented: Read as '0'                                                     |

| bit 2-0               | CCDPE<2:0>: RE<2:0> Current Control Drive Positive Control bits <sup>(1)</sup> |

|                       | 1 = Current control source enabled                                             |

0 = Current control source disabled

x = Bit is unknown

Note 1: If CCDPEy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

### **REGISTER 12-54: CCDNE: CURRENT CONTROL DRIVE NEGATIVE PORTE REGISTER**

| U-0   | U-0         | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-------------|-----|-----|-----|---------|---------|---------|--|

| _     |             |     | _   | _   | CCDNE2  | CCDNE1  | CCDNE0  |  |

| bit 7 | bit 7 bit 0 |     |     |     |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as | '0' |

|---------|------------------------|-----|

|---------|------------------------|-----|

CCDNE<2:0>: RE<2:0> Current Control Drive Negative Control bits<sup>(1)</sup> bit 2-0

- 1 = Current control source enabled

- 0 = Current control source disabled

Note 1: If CCDNEy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

## 13.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- Note: The I<sup>2</sup>C SCLx and SDAx functions can be remapped through PPS. However, only the RB1, RB2, RC3 and RC4 pins have the I<sup>2</sup>C and SMBus specific input buffers implemented (which have different thresholds compared to the normal ST/TTL input levels of the other general purpose I/O pins). If the SCLx or SDAx functions are mapped to some other pin (other than RB1, RB2, RC3 or RC4), the general purpose TTL or ST input buffers (as configured based on INLVL register setting) will be used instead. In most applications, it is therefore recommended only to map the SCLx and SDAx pin functions to the RB1, RB2, RC3 or RC4 pins.

## 13.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 13-1.

#### EXAMPLE 13-1: PPS LOCK/UNLOCK SEQUENCE

| ; | suspend interrupts                     |

|---|----------------------------------------|

|   | BCF INTCON, GIE                        |

| ; | BANKSEL PPSLOCK ; set bank             |

| ; | required sequence, next 5 instructions |

|   | MOVLW 0x55                             |

|   | MOVWF PPSLOCK                          |

|   | MOVLW 0xAA                             |

|   | MOVWF PPSLOCK                          |

| ; | Set PPSLOCKED bit to disable writes or |

| ; | Clear PPSLOCKED bit to enable writes   |

|   | BSF PPSLOCK, PPSLOCKED                 |

| ; | restore interrupts                     |

|   | BSF INTCON, GIE                        |

## 13.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

## 13.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 13.7 Effects of a Reset

A device Power-On-Reset (POR) clears all PPS input and output selections to their default values. All other Resets leave the selections unchanged. Default input selections are shown in pin allocation Table 13-1 and Table 13-2.

## 22.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR5 register will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · CLCxIE bit of the PIE5 register

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the PIR5 register, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

## 22.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCxDATA register. Reading this register reads the outputs of all CLCs simultaneously. This prevents any reading skew introduced by testing or reading the LCxOUT bits in the individual CLCxCON registers.

## 22.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

## 22.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

## 22.6 CLCx Setup Steps

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 22-2).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with inputs.

- Clear all TRIS bits associated with outputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxGyPOL bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the PIE5 register.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

## REGISTER 23-27: ADERRL: ADC CALCULATION ERROR LOW BYTE REGISTER

| R-x              | R-x   | R-x                  | R-x  | R-x            | R-x              | R-x              | R-x          |

|------------------|-------|----------------------|------|----------------|------------------|------------------|--------------|

|                  |       |                      | ADEF | RR<7:0>        |                  |                  |              |

| bit 7            |       |                      |      |                |                  |                  | bit 0        |

|                  |       |                      |      |                |                  |                  |              |

| Legend:          |       |                      |      |                |                  |                  |              |

| R = Readable b   | oit   | W = Writable bit     |      | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unknowr   | ı    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleared |      |                |                  |                  |              |

bit 7-0 **ADERR<7:0>**: ADC Calculation Error LSB. Least Significant Byte of ADC Calculation Error. Calculation is determined by ADCALC bits of ADCON3, see Register 21-1 for more details.

## REGISTER 23-28: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-x/x      | R/W-x/x | R/W-x/x          | R/W-x/x | R/W-x/x      | R/W-x/x          | R/W-x/x  | R/W-x/x |

|--------------|---------|------------------|---------|--------------|------------------|----------|---------|

|              |         |                  | ADLTH   | <15:8>       |                  |          |         |

| bit 7        |         |                  |         |              |                  |          | bit 0   |

|              |         |                  |         |              |                  |          |         |

| Legend:      |         |                  |         |              |                  |          |         |

| R = Readable | bit     | W = Writable bit | t       | U = Unimpler | mented bit, read | 1 as '0' |         |

'1' = Bit is set '0' = Bit is cleared

-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0 **ADLTH<15:8>**: ADC Lower Threshold MSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

### REGISTER 23-29: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

x = Bit is unknown

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|------------|---------|---------|---------|---------|---------|---------|---------|

| ADLTH<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

|            |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ADLTH<7:0>**: ADC Lower Threshold LSB. ADLTH and ADUTH are compared with ADERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

u = Bit is unchanged

# 24.8 NCO Control Registers

## REGISTER 24-1: NCO1CON: NCO CONTROL REGISTER

| R/W-0/0                               | U-0                                                                                                                                                                                                 | R-0/0              | R/W-0/0 | U-0                                                   | U-0 | U-0 | R/W-0/0 |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-------------------------------------------------------|-----|-----|---------|--|--|

| N1EN                                  | —                                                                                                                                                                                                   | N1OUT              | N1POL   | —                                                     | —   | _   | N1PFM   |  |  |

| bit 7                                 | •                                                                                                                                                                                                   |                    |         | -                                                     |     |     | bit 0   |  |  |

|                                       |                                                                                                                                                                                                     |                    |         |                                                       |     |     |         |  |  |

| Legend:                               |                                                                                                                                                                                                     |                    |         |                                                       |     |     |         |  |  |

| R = Readable bit                      |                                                                                                                                                                                                     | W = Writable bit   |         | U = Unimplemented bit, read as '0'                    |     |     |         |  |  |

| u = Bit is unchanged                  |                                                                                                                                                                                                     | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |     |     |         |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                                                                                                                                                     |                    |         |                                                       |     |     |         |  |  |

| bit 7<br>bit 6<br>bit 5<br>bit 4      | N1EN: NCO1 Enable bit<br>1 = NCO1 module is enabled<br>0 = NCO1 module is disabled<br>Unimplemented: Read as '0'<br>N1OUT: NCO1 Output bit<br>Displays the current output value of the NCO1 module. |                    |         |                                                       |     |     |         |  |  |

| DIT 4                                 | N1POL: NCO1 Polarity<br>1 = NCO1 output signal is inverted<br>0 = NCO1 output signal is not inverted                                                                                                |                    |         |                                                       |     |     |         |  |  |

| bit 3-1                               | Unimplemented: Read as '0'                                                                                                                                                                          |                    |         |                                                       |     |     |         |  |  |

| bit 0                                 | N1PFM: NCO1 Pulse Frequency Mode bit1 = NCO1 operates in Pulse Frequency mode0 = NCO1 operates in Fixed Duty Cycle mode, divide by 2                                                                |                    |         |                                                       |     |     |         |  |  |

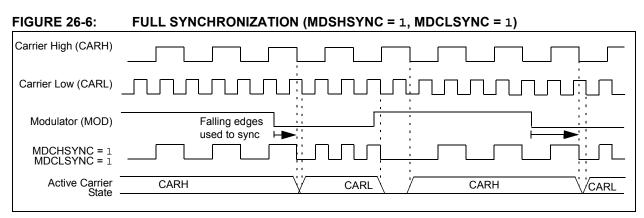

| FIGURE 26-5:                 | CARRIER LOW SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 1) |

|------------------------------|----------------------------------------------------------|

| Carrier High (CARH)          |                                                          |

| Carrier Low (CARL)           |                                                          |

| Modulator (MOD)              |                                                          |

| MDCHSYNC = 0<br>MDCLSYNC = 1 |                                                          |

| Active Carrier<br>State -    | CARH X CARL CARH X CARL                                  |

| FIGURE 28-6: TIMER1 GATE SI                                  | NGLE-PULSE AND TOGGLE COMBINED MODE                  |

|--------------------------------------------------------------|------------------------------------------------------|

| TMRxGE                                                       |                                                      |

| TxGPOL                                                       |                                                      |

| TxGSPM                                                       |                                                      |

| TxGTM                                                        |                                                      |

| TxGGO/ Set by soft<br>DONE Counting en<br>rising edge of set | abled on                                             |

| selected gate                                                |                                                      |

|                                                              |                                                      |

| TxGVAL                                                       |                                                      |

| TMRxH:TMRxL N<br>Count                                       | N + 1 N + 2 N + 3 N + 4                              |

| TMRxGIF    Cleared by software                               | Set by hardware on Cleared by falling edge of TxGVAL |

| L                                                            |                                                      |

| U-0                   | U-0                                                                    | U-0                                | R/W-0/0              | R/W-0/0      | R/W-0/0                                               | R/W-0/0  | R/W-0/0 |  |  |  |

|-----------------------|------------------------------------------------------------------------|------------------------------------|----------------------|--------------|-------------------------------------------------------|----------|---------|--|--|--|

| _                     |                                                                        | _                                  |                      |              | WSEL<4:0>                                             |          |         |  |  |  |

| bit 7                 |                                                                        |                                    |                      |              |                                                       |          | bit     |  |  |  |

|                       |                                                                        |                                    |                      |              |                                                       |          |         |  |  |  |

| Legend:               |                                                                        |                                    |                      |              |                                                       |          |         |  |  |  |

| R = Readable bit W    |                                                                        | W = Writable                       | e bit                | U = Unimpler | nented bit, read                                      | d as '0' |         |  |  |  |

| u = Bit is unchanged  |                                                                        | x = Bit is unł                     | x = Bit is unknown   |              | -n/n = Value at POR and BOR/Value at all other Resets |          |         |  |  |  |

| '1' = Bit is set      |                                                                        | '0' = Bit is cl                    | '0' = Bit is cleared |              | q = Value depends on condition                        |          |         |  |  |  |

| bit 7-5               | Unimplem                                                               | ented: Read as                     | ʻ0'                  |              |                                                       |          |         |  |  |  |

| bit 4-0               | •                                                                      | >: SMTx Windo                      |                      |              |                                                       |          |         |  |  |  |

| DIL 4-0               | 11111 = R                                                              |                                    |                      | 5            |                                                       |          |         |  |  |  |

|                       | •                                                                      |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | •                                                                      |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | •                                                                      | •                                  |                      |              |                                                       |          |         |  |  |  |

|                       | 11000 = Reserved                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 10111 = LC4_out                                                        |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 10110 = LC3_out                                                        |                                    |                      |              |                                                       |          |         |  |  |  |

|                       |                                                                        | 10101 = LC2_out<br>10100 = LC1_out |                      |              |                                                       |          |         |  |  |  |

|                       |                                                                        | CD1_output                         |                      |              |                                                       |          |         |  |  |  |

|                       |                                                                        | 20UT sync                          |                      |              |                                                       |          |         |  |  |  |

|                       |                                                                        | 10001 = C1OUT sync                 |                      |              |                                                       |          |         |  |  |  |

|                       | 10000 = PWM7_out                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 01111 <b>= P</b>                                                       | 01111 = PWM6_out                   |                      |              |                                                       |          |         |  |  |  |

|                       | 01110 = CCP5_out                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 01101 = CCP4_out                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 01100 = CCP3_out                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | $01011 = CCP2_out$                                                     |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | $01010 = CCP1_out$                                                     |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 01001 = SMT2_match <sup>(1)</sup><br>01000 = SMT1_match <sup>(1)</sup> |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00111 = TMR6_postscaled                                                |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00110 = TMR4 postscaled                                                |                                    |                      |              |                                                       |          |         |  |  |  |

|                       |                                                                        | 00101 = TMR2_postscaled            |                      |              |                                                       |          |         |  |  |  |

| 00100 = TMR0_overflow |                                                                        |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00011 <b>= S</b>                                                       |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00010 = MFINTOSC/16                                                    |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00001 = LF                                                             |                                    |                      |              |                                                       |          |         |  |  |  |

|                       | 00000 = SI                                                             | MTxWINPPS                          |                      |              |                                                       |          |         |  |  |  |

## REGISTER 32-5: SMTxWIN: SMT1 WINDOW INPUT SELECT REGISTER

Note 1: The SMT\_match corresponding to the SMT selected becomes reserved.

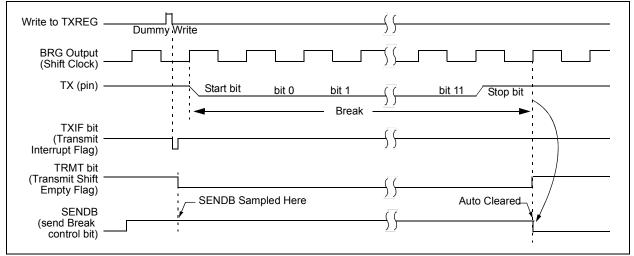

## 33.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RC1STA register and the received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when:

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 33.3.3 "Auto-Wake-up on Break"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUD1CON register before placing the EUSART in Sleep mode.

# 38.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

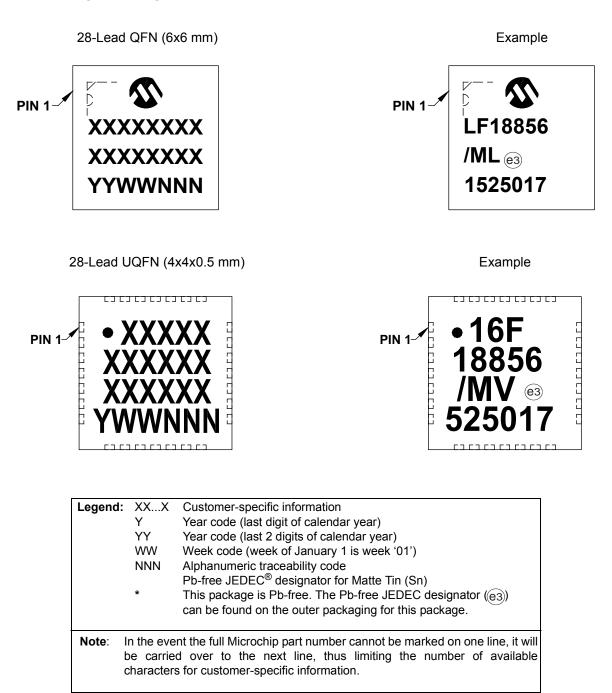

## 40.1 Package Marking Information (Continued)

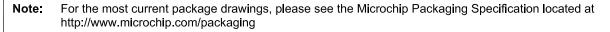

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.40 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 2.35 |

| Optional Center Pad Length | T2          |          |      | 2.35 |

| Contact Pad Spacing        | C1          |          | 4.00 |      |

| Contact Pad Spacing        | C2          |          | 4.00 |      |

| Contact Pad Width (X28)    | X1          |          |      | 0.20 |

| Contact Pad Length (X28)   | Y1          |          |      | 0.80 |

| Distance Between Pads      | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A

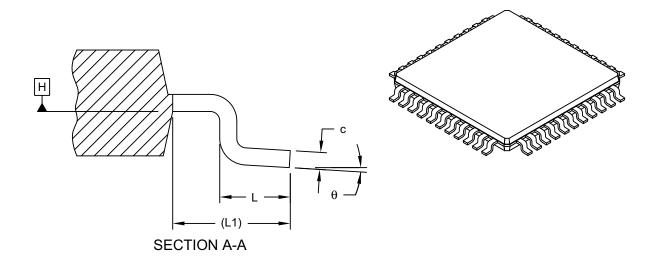

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |            |          |      |  |

|--------------------------|-------------|------------|----------|------|--|

| Dimension                | MIN         | NOM        | MAX      |      |  |

| Number of Leads          | N           |            | 44       |      |  |

| Lead Pitch               | е           |            | 0.80 BSC |      |  |

| Overall Height           | Α           | -          | -        | 1.20 |  |

| Standoff                 | A1          | 0.05       | -        | 0.15 |  |

| Molded Package Thickness | A2          | 0.95       | 1.00     | 1.05 |  |

| Overall Width            | E           | 12.00 BSC  |          |      |  |

| Molded Package Width     | E1          | 10.00 BSC  |          |      |  |

| Overall Length           | D           | 12.00 BSC  |          |      |  |

| Molded Package Length    | D1          | 10.00 BSC  |          |      |  |

| Lead Width               | b           | 0.30       | 0.37     | 0.45 |  |

| Lead Thickness           | С           | 0.09       | -        | 0.20 |  |

| Lead Length              | L           | 0.45       | 0.60     | 0.75 |  |

| Footprint                | L1          | 1.00 REF   |          |      |  |

| Foot Angle               | θ           | 0° 3.5° 7° |          |      |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2