#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18856-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-4: PIC16(L)F18876 MEMORY MAP BANK 0-7

|      | BANK 0         |              | BANK 1         |      | BANK 2         |      | BANK 3         |      | BANK 4         |      | BANK 5         |      | BANK 6         |      | BANK 7         |

|------|----------------|--------------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|------|----------------|

| 000h |                | 080h         |                | 100h |                | 180h |                | 200h |                | 280h |                | 300h |                | 380h |                |

|      | Core Registers |              | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |      | Core Registers |

|      | (Table 3-2)    |              | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |

| 00Bh |                | 08Bh         |                | 10Bh |                | 18Bh |                | 20Bh |                | 28Bh |                | 30Bh |                | 38Bh |                |

| 00Ch | PORTA          | 08Ch         | ADRESL         | 10Ch | ADCNT          | 18Ch | SSP1BUF        | 20Ch | TMR1L          | 28Ch | T2TMR          | 30Ch | CCPR1L         | 38Ch | PWM6DCL        |

| 00Dh | PORTB          | 08Dh         | ADRESH         | 10Dh | ADRPT          | 18Dh | SSP1ADD        | 20Dh | TMR1H          | 28Dh | T2PR           | 30Dh | CCPR1H         | 38Dh | PWM6DCH        |

| 00Eh | PORTC          | 08Eh         | ADPREVL        | 10Eh | ADLTHL         | 18Eh | SSP1MSK        | 20Eh | T1CON          | 28Eh | T2CON          | 30Eh | CCP1CON        | 38Eh | PWM6CON        |

| 00Fh | PORTD          | 08Fh         | ADPREVH        | 10Fh | ADLTHH         | 18Fh | SSP1STAT       | 20Fh | T1GCON         | 28Fh | T2HLT          | 30Fh | CCP1CAP        | 38Fh | —              |

| 010h | PORTE          | 090h         | ADACCL         | 110h | ADUTHL         | 190h | SSP1CON1       | 210h | T1GATE         | 290h | T2CLKCON       | 310h | CCPR2L         | 390h | PWM7DCL        |

| 011h | TRISA          | 091h         | ADACCH         | 111h | ADUTHH         | 191h | SSP1CON2       | 211h | T1CLK          | 291h | T2RST          | 311h | CCPR2H         | 391h | PWM7DCH        |

| 012h | TRISB          | 092h         | —              | 112h | ADSTPTL        | 192h | SSP1CON3       | 212h | TMR3L          | 292h | T4TMR          | 312h | CCP2CON        | 392h | PWM7CON        |

| 013h | TRISC          | 093h         | ADCON0         | 113h | ADSTPTH        | 193h | —              | 213h | TMR3H          | 293h | T4PR           | 313h | CCP2CAP        | 393h |                |

| 014h | TRISD          | 094h         | ADCON1         | 114h | ADFLTRL        | 194h | _              | 214h | T3CON          | 294h | T4CON          | 314h | CCPR3L         | 394h | _              |

| 015h | TRISE          | 095h         | ADCON2         | 115h | ADFLTRH        | 195h | _              | 215h | T3GCON         | 295h | T4HLT          | 315h | CCPR3H         | 395h | _              |

| 016h | LATA           | 096h         | ADCON3         | 116h | ADERRL         | 196h | SSP2BUF        | 216h | T3GATE         | 296h | T4CLKCON       | 316h | CCP3CON        | 396h | _              |

| 017h | LATB           | 097h         | ADSTAT         | 117h | ADERRH         | 197h | SSP2ADD        | 217h | T3CLK          | 297h | T4RST          | 317h | CCP3CAP        | 397h | —              |

| 018h | LATC           | 098h         | ADCLK          | 118h | —              | 198h | SSP2MSK        | 218h | TMR5L          | 298h | T6TMR          | 318h | CCPR4L         | 398h | —              |

| 019h | LATD           | 099h         | ADACT          | 119h | RC1REG         | 199h | SSP2STAT       | 219h | TMR5H          | 299h | T6PR           | 319h | CCPR4H         | 399h | _              |

| 01Ah | LATE           | 09Ah         | ADREF          | 11Ah | TX1REG         | 19Ah | SSP2CON1       | 21Ah | T5CON          | 29Ah | T6CON          | 31Ah | CCP4CON        | 39Ah | —              |

| 01Bh | _              | 09Bh         | ADCAP          | 11Bh | SP1BRGL        | 19Bh | SSP2CON2       | 21Bh | T5GCON         | 29Bh | T6HLT          | 31Bh | CCP4CAP        | 39Bh |                |

| 01Ch | TMR0L          | 09Ch         | ADPRE          | 11Ch | SP1BRGH        | 19Ch | SSP2CON3       | 21Ch | T5GATE         | 29Ch | T6CLKCON       | 31Ch | CCPR5L         | 39Ch | _              |

| 01Dh | TMR0H          | 09Dh         | ADACQ          | 11Dh | RC1STA         | 19Dh | —              | 21Dh | T5CLK          | 29Dh | T6RST          | 31Dh | CCPR5H         | 39Dh |                |

| 01Eh | T0CON0         | 09Eh         | ADPCH          | 11Eh | TX1STA         | 19Eh | _              | 21Eh | CCPTMRS0       | 29Eh | —              | 31Eh | CCP5CON        | 39Eh |                |

| 01Fh | T0CON1         | 09Fh<br>0A0h | —              | 11Fh | BAUD1CON       | 19Fh | —              | 21Fh | CCPTMRS1       | 29Fh | —              | 31Fh | CCP5CAP        | 39Fh | _              |

| 020h |                | UAUII        |                | 120h |                | 1A0h |                | 220h |                | 2A0h |                | 320h |                | 3A0h |                |

|      |                |              |                |      |                |      |                |      |                |      |                |      |                |      |                |

|      |                |              | General        |      | General        |      | General        |      | General        |      | General        |      | General        |      | General        |

|      | General        |              | Purpose        |      | Purpose        |      | Purpose        |      | Purpose        |      | Purpose        |      | Purpose        |      | Purpose        |

|      | Purpose        |              | Register       |      | Register       |      | Register       |      | Register       |      | Register       |      | Register       |      | Register       |

|      | Register       |              | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |

|      | 96 Bytes       |              |                |      |                |      |                |      |                |      |                |      |                |      |                |

|      |                | 0EFh         |                | 16Fh |                | 1EFh |                | 26Fh |                | 2EFh |                | 36Fh |                | 3EFh |                |

|      |                | 0F0h         | Common RAM     | 170h | Common RAM     | 1F0h | Common RAM     | 270h | Common RAM     | 2F0h | Common RAM     | 370h | Common RAM     | 3F0h | Common RAM     |

|      |                |              | (Accesses      |      | (Accesses      |      | (Accesses      |      | (Accesses      |      | (Accesses      |      | (Accesses      |      | (Accesses      |

| 07Fh |                | 0FFh         | 70h – 7Fh)     | 17Fh | 70h – 7Fh)     | 1FFh | 70h – 7Fh)     | 27Fh | 70h – 7Fh)     | 2FFh | 70h – 7Fh)     | 37Fh | 70h – 7Fh)     | 3FFh | 70h – 7Fh)     |

Legend:

= Unimplemented data memory locations, read as '0'.

| Name   | Bit 7  | Bit 6  | Bit 5     | Bit 4     | Bit 3  | Bit 2     | Bit 1     | Bit 0   | Register<br>on Page |

|--------|--------|--------|-----------|-----------|--------|-----------|-----------|---------|---------------------|

| INTCON | GIE    | PEIE   | —         | —         | _      | —         | —         | INTEDG  | 134                 |

| PIE0   | _      | _      | TMR0IE    | IOCIE     | _      | _         | _         | INTE    | 135                 |

| PIE1   | OSFIE  | CSWIE  | —         | —         | _      | —         | ADTIE     | ADIE    | 136                 |

| PIE2   | _      | ZCDIE  | —         | —         | _      | —         | C2IE      | C1IE    | 137                 |

| PIE3   | _      | _      | RCIE      | TXIE      | BCL2IE | SSP2IE    | BCL1IE    | SSP1IE  | 138                 |

| PIE4   | -      | _      | TMR6IE    | TMR5IE    | TMR4IE | TMR3IE    | TMR2IE    | TMR1IE  | 139                 |

| PIE5   | CLC4IE | CLC3IE | CLC2IE    | CLC1IE    | _      | TMR5GIE   | TMR3GIE   | TMR1GIE | 140                 |

| PIE6   | —      |        | —         | CCP5IE    | CCP4IE | CCP3IE    | CCP2IE    | CCP1IE  | 141                 |

| PIE7   | SCANIE | CRCIE  | NVMIE     | NCO1IE    | _      | CWG3IE    | CWG2IE    | CWG1IE  | 142                 |

| PIE8   | —      |        | SMT2PWAIE | SMT2PRAIE | SMT2IE | SMT1PWAIE | SMT1PRAIE | SMT1IE  | 143                 |

| PIR0   | —      | -      | TMR0IF    | IOCIF     | —      | —         | —         | INTF    | 144                 |

| PIR1   | OSFIF  | CSWIF  | —         | —         | _      | —         | ADTIF     | ADIF    | 145                 |

| PIR2   | _      | ZCDIF  | —         | —         | _      | —         | C2IF      | C1IF    | 146                 |

| PIR3   | _      | _      | RCIF      | TXIF      | BCL2IF | SSP2IF    | BCL1IF    | SSP1IF  | 147                 |

| PIR4   | _      | _      | TMR6IF    | TMR5IF    | TMR4IF | TMR3IF    | TMR2IF    | TMR1IF  | 148                 |

| PIR5   | CLC4IF | CLC3IF | CLC2IF    | CLC1IF    | _      | TMR5GIF   | TMR3GIF   | TMR1GIF | 149                 |

| PIR6   | _      |        | _         | CCP5IF    | CCP4IF | CCP3IF    | CCP2IF    | CCP1IF  | 150                 |

| PIR7   | SCANIF | CRCIF  | NVMIF     | NCO1IF    |        | CWG3IF    | CWG2IF    | CWG1IF  | 152                 |

| PIR8   | _      | _      | SMT2PWAIF | SMT2PRAIF | SMT2IF | SMT1PWAIF | SMT1PRAIF | SMT1IF  | 153                 |

## TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

## 12.0 I/O PORTS

#### TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device                           | PORTA | PORTB | PORTC | PORTD | PORTE |

|----------------------------------|-------|-------|-------|-------|-------|

| PIC16(L)F18856PIC1<br>6(L)F18856 | •     | •     | ٠     |       | ٠     |

| PIC16(L)F18876PIC1<br>6(L)F18876 | ٠     | ٠     | •     | •     | •     |

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- CCDPx registers (current control positive)

- CCDNx registers (current control negative)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

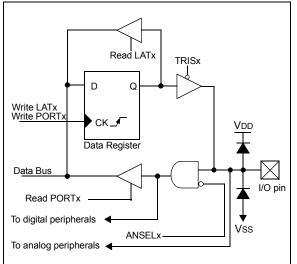

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

## 12.1 Current-Controlled Mode

Current-Controlled mode allows output currents to be regulated for both high-side and low-side drivers. All source and sink drivers for each port pin will operate at the specified current, when enabled individually by the Current-Controlled Enable registers.

Note: Current-Controlled mode is available regardless of which peripheral drives the output.

The Current-Controlled Configuration (CCDCON) register enables the Current-Controlled mode for all ports and sets the current levels.

Note: Setting CCDEN = 1 increases the device VDDIO current requirement by a fixed amount regardless of how many CCDPx[n] or CCDNx[n] bits are set.

The Current-Controlled Enable registers enable each individual port pin's positive-going (CCDPx) or negative-going (CCDNx) output driver.

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODCC7   | ODCC6   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   |

| bit 7   |         |         |         |         |         |         | bit     |

## REGISTER 12-27: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ODCC<7:0>: PORTC Open-Drain Enable bits

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

### **REGISTER 12-28: SLRCONC: PORTC SLEW RATE CONTROL REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

## REGISTER 12-29: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits

For RC<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

bit 0

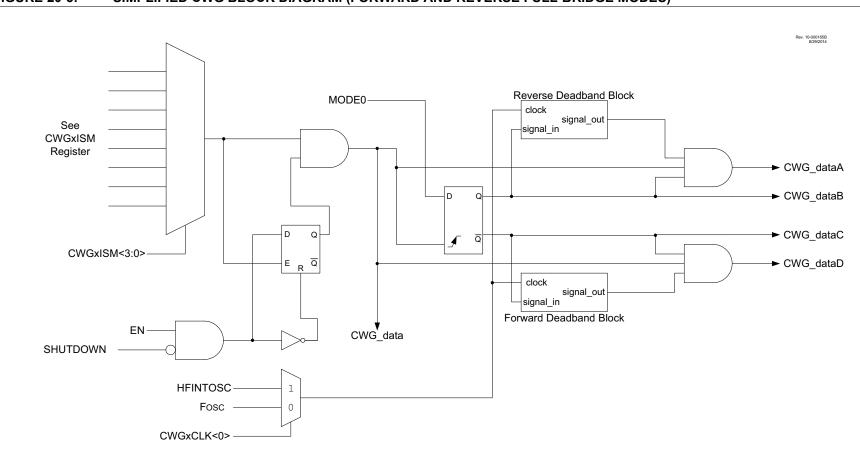

## FIGURE 20-3: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

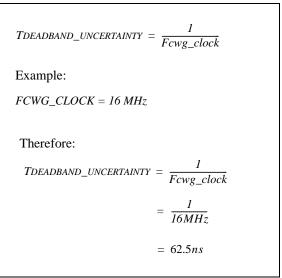

## 20.8 Dead-Band Uncertainty

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates uncertainty in the dead-band time delay. The maximum uncertainty is equal to one CWG clock period. Refer to Equation 20-1 for more details.

#### EQUATION 20-1: DEAD-BAND UNCERTAINTY

##

3: When changing directions, CWGxA and CWGxC switch at rising CWGx\_data; modulated CWGxB and CWGxD are held inactive for the dead band duration shown; dead band affects only the first pulse after the direction change.

#### FIGURE 20-9: CWG HALF-BRIDGE MODE OPERATION

| CWGx_clock                |                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------|

| CWGxA<br>CWGxC            |                                                                                               |

|                           | ← Rising Event Dead Band ← Rising Event<br>← Falling Event Dead Band ← Rising Event Dead Band |

| CWGxB<br>CWGxD            |                                                                                               |

| CWGx_data                 |                                                                                               |

| Note: CWGx_rising_src = 0 | CCP1_out, CWGx_falling_src = ~CCP1_out                                                        |

| R/W-0/0          | U-0                                                                                                                                                                                                                                                                         | R-0                                                                                                                                                                                                                | R/W-0/0                           | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|------------------|------------------|-------------|

| T0EN             |                                                                                                                                                                                                                                                                             | TOOUT                                                                                                                                                                                                              | T016BIT                           |                  | TOOUT            | PS<3:0>          |             |

| bit 7            |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                    | ·                                 | ·                |                  |                  | bit         |

| Legend:          |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                    |                                   |                  |                  |                  |             |

| R = Readable     | bit                                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                       | bit                               | U = Unimplem     | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                                       | x = Bit is unk                                                                                                                                                                                                     | nown                              | -n/n = Value a   | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                                             | '0' = Bit is cle                                                                                                                                                                                                   | ared                              |                  |                  |                  |             |

|                  |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                    |                                   |                  |                  |                  |             |

| bit 7            |                                                                                                                                                                                                                                                                             | ule is enabled                                                                                                                                                                                                     | and operating<br>I and in the low | vest power mod   | le               |                  |             |

| bit 6            | Unimplemen                                                                                                                                                                                                                                                                  | ted: Read as                                                                                                                                                                                                       | ʻ0'                               | -                |                  |                  |             |

| bit 5            | T0OUT: TMR<br>TMR0 output                                                                                                                                                                                                                                                   | 0 Output bit (r<br>bit                                                                                                                                                                                             | ead-only)                         |                  |                  |                  |             |

| bit 4            | <b>T016BIT:</b> TMI<br>1 = TMR0 is<br>0 = TMR0 is a                                                                                                                                                                                                                         | a 16-bit timer                                                                                                                                                                                                     | as 16-bit Timer                   | Select bit       |                  |                  |             |

| bit 3-0          | <b>TOOUTPS&lt;3:</b><br>1111 = 1:16 F<br>1110 = 1:15 F<br>1101 = 1:14 F<br>1000 = 1:13 F<br>1011 = 1:12 F<br>1010 = 1:11 F<br>1000 = 1:10 F<br>1000 = 1:9 P<br>0111 = 1:8 P<br>0110 = 1:7 P<br>0101 = 1:6 P<br>0100 = 1:5 P<br>0011 = 1:4 P<br>0010 = 1:3 P<br>0001 = 1:2 P | Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler<br>ostscaler | put postscaler                    | (divider) select | : bits           |                  |             |

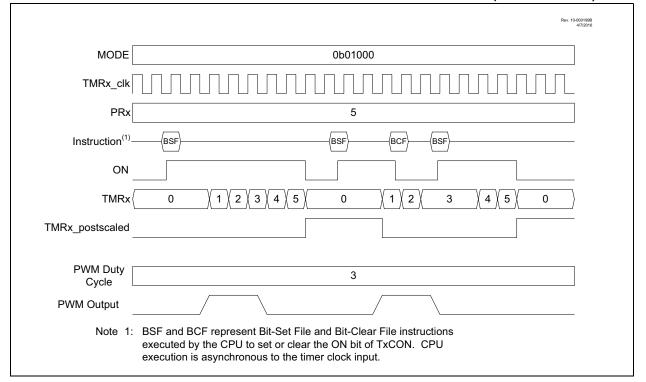

#### 29.5.5 SOFTWARE START ONE-SHOT MODE

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 29-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 29-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

## 29.7 Register Definitions: Timer2/4/6 Control

Long bit name prefixes for the Timer2/4/6 peripherals are shown in Table 29-2. Refer to **Section 1.1** "**Register and Bit naming conventions**" for more information TABLE 29-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer2     | T2              |

| Timer4     | T4              |

| Timer6     | Т6              |

## REGISTER 29-1: TxCLKCON: TIMER2/4/6 CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | —   | _   |         | CS<     | 3:0>    |         |

| bit 7 |     | •   |     |         |         |         | bit 0   |

| Legend:              |                        |                                                       |

|----------------------|------------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit       | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown     | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared   |                                                       |

|                      |                        |                                                       |

| bit 7-4 Unin         | plemented: Read as '0' |                                                       |

| bit 3-0 | CS<3:0>: Timer2/4/6 Clock Select bits |

|---------|---------------------------------------|

|         | 1111 = Reserved                       |

|         | 1110 = Reserved                       |

|         | 1101 = LC4_out                        |

|         | 1100 = LC3_out                        |

|         | 1011 = LC2_out                        |

|         | 1010 = LC1_out                        |

|         | 1001 = ZCD1_output                    |

|         | 1000 = NCO output                     |

|         | 0111 = CLKR                           |

|         | 0110 <b>= S</b> OSC                   |

|         | 0101 = MFINTOSC/16 (31.25 kHz)        |

|         | 0100 = LFINTOSC                       |

|         | 0011 = HFINTOSC (16 MHz)              |

|         | 0010 = Fosc                           |

|         | 0001 = Fosc/4                         |

0000 = TxCKIPPS

## 30.0 CAPTURE/COMPARE/PWM MODULES

The Capture/Compare/PWM module is a peripheral that allows the user to time and control different events, and to generate Pulse-Width Modulation (PWM) signals. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate Pulse-Width Modulated signals of varying frequency and duty cycle.

The Capture/Compare/PWM modules available are shown in Table 30-1.

| TABLE 30-1: AVA | ILABLE CCP | MODULES |

|-----------------|------------|---------|

|-----------------|------------|---------|

| Device            | CCP1 | CCP2 | CCP3 | CCP4 | CCP5 |

|-------------------|------|------|------|------|------|

| PIC16(L)F18856/76 | ٠    | ٠    | ٠    | ٠    | ٠    |

The Capture and Compare functions are identical for all CCP modules.

- Note 1: In devices with more than one CCP module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the CCP1CON and CCP2CON control the same operational aspects of two completely different CCP modules.

- 2: Throughout this section, generic references to a CCP module in any of its operating modes may be interpreted as being equally applicable to CCPx module. Register names, module signals, I/O pins, and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

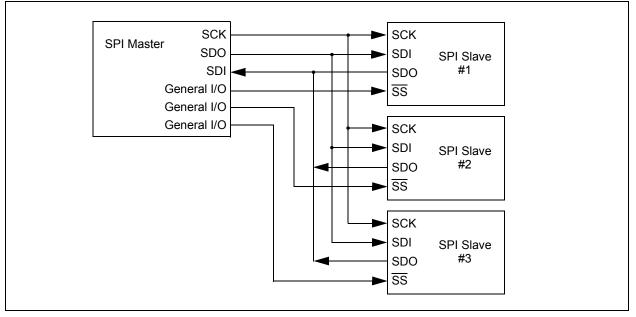

## 31.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPxSTAT)

- MSSP Control register 1 (SSPxCON1)

- MSSP Control register 3 (SSPxCON3)

- MSSP Data Buffer register (SSPxBUF)

- MSSP Address register (SSPxADD)

- MSSP Shift register (SSPxSR) (Not directly accessible)

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

In one SPI master mode, SSPxADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in **Section 31.7 "Baud Rate Generator"**.

SSPxSR is the shift register used for shifting data in and out. SSPxBUF provides indirect access to the SSPxSR register. SSPxBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPxSR and SSPxBUF together create a buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

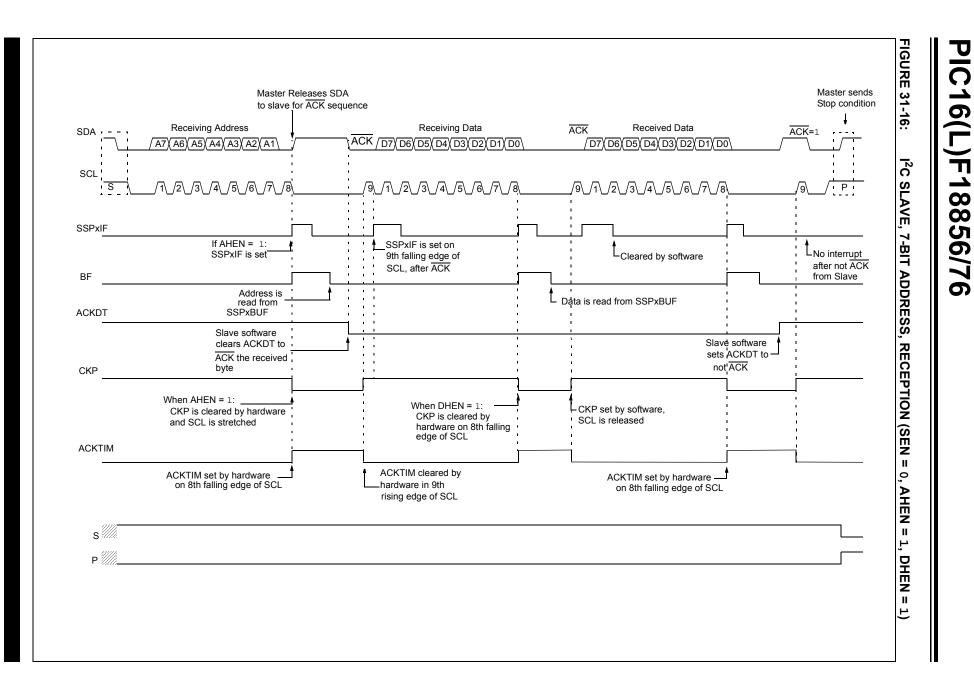

## 31.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 31.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 31.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit of the SSPxSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCL1IF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

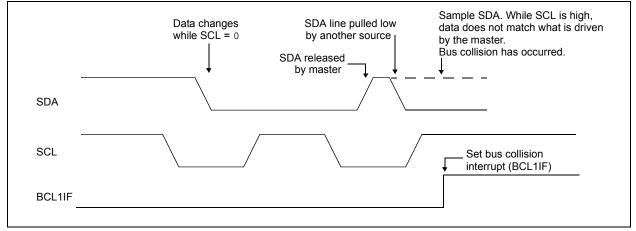

#### 31.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCL1IF and reset the I<sup>2</sup>C port to its Idle state (Figure 31-32).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPxCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPxSTAT register, or the bus is Idle and the S and P bits are cleared.

## FIGURE 31-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### 32.5.3 GO STATUS

Timer run status is determined by the TS bit of the SMTxSTAT register, and will be delayed in time by synchronizer delays in non-Counter modes.

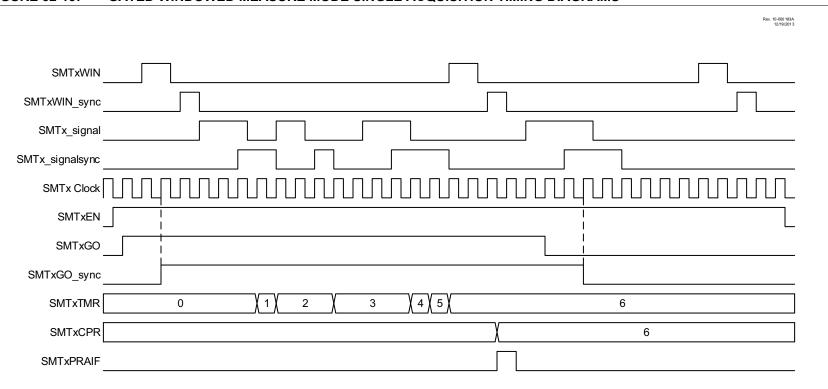

## 32.6 Modes of Operation

The modes of operation are summarized in Table 32-1. The following sections provide detailed descriptions, examples of how the modes can be used. Note that all waveforms assume WPOL/SPOL/CPOL = 0. When WPOL/SPOL/CPOL = 1, all SMTSIGx, SMTWINx and SMT clock signals will have a polarity opposite to that indicated. For all modes, the REPEAT bit controls whether the acquisition is repeated or single. When REPEAT = 0 (Single Acquisition mode), the timer will stop incrementing and the SMTxGO bit will be reset upon the completion of an acquisition. Otherwise, the timer will continue and allow for continued acquisitions to overwrite the previous ones until the timer is stopped in software.

## 32.6.1 TIMER MODE

Timer mode is the simplest mode of operation where the SMTxTMR is used as a 16/24-bit timer. No data acquisition takes place in this mode. The timer increments as long as the SMTxGO bit has been set by software. No SMT window or SMT signal events affect the SMTxGO bit. Everything is synchronized to the SMT clock source. When the timer experiences a period match (SMTxTMR = SMTxPR), SMTxTMR is reset and the period match interrupt trips. See Figure 32-3.

| MODE      | Mode of Operation                 | Synchronous<br>Operation | Reference                                    |

|-----------|-----------------------------------|--------------------------|----------------------------------------------|

| 0000      | Timer                             | Yes                      | Section 32.6.1 "Timer Mode"                  |

| 0001      | Gated Timer                       | Yes                      | Section 32.6.2 "Gated Timer Mode"            |

| 0010      | Period and Duty Cycle Acquisition | Yes                      | Section 32.6.3 "Period and Duty-Cycle Mode"  |

| 0011      | High and Low Time Measurement     | Yes                      | Section 32.6.4 "High and Low Measure Mode"   |

| 0100      | Windowed Measurement              | Yes                      | Section 32.6.5 "Windowed Measure Mode"       |

| 0101      | Gated Windowed Measurement        | Yes                      | Section 32.6.6 "Gated Window Measure Mode"   |

| 0110      | Time of Flight                    | Yes                      | Section 32.6.7 "Time of Flight Measure Mode" |

| 0111      | Capture                           | Yes                      | Section 32.6.8 "Capture Mode"                |

| 1000      | Counter                           | No                       | Section 32.6.9 "Counter Mode"                |

| 1001      | Gated Counter                     | No                       | Section 32.6.10 "Gated Counter Mode"         |

| 1010      | Windowed Counter                  | No                       | Section 32.6.11 "Windowed Counter Mode"      |

| 1011-1111 | Reserved                          | —                        | _                                            |

TABLE 32-1: MODES OF OPERATION

## FIGURE 32-13: GATED WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAMS

## 33.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 33.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RC1STA and TX1STA Control registers must be configured for Synchronous Slave Reception (see Section 33.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR3 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

#### 33.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- The RC1STA and TX1STA Control registers must be configured for synchronous slave transmission (see Section 33.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE3 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE3 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                            |

| Operands:        | None                                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT}, \\ 0 \rightarrow \text{WDT prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                    |

| Status Affected: | TO, PD                                                                                                                                                                                                                                   |

| Description:     | The power-down Status bit, $\overline{\text{PD}}$ is<br>cleared. Time-out Status bit, $\overline{\text{TO}}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>See <b>Section 8.2 "Sleep Mode"</b> for<br>more information. |

| SUBLW            | Subtract W from literal                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                 |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                |

| Status Affected: | C, DC, Z                                                                                                                 |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |

|                  |                                                                                                                          |

| <b>C</b> = 0 | W > k               |

|--------------|---------------------|

| C = 1        | $W \leq k$          |

| DC = 0       | W<3:0> > k<3:0>     |

| DC = 1       | $W<3:0> \le k<3:0>$ |

| SUBWF     | Subtract W from f |  |  |  |

|-----------|-------------------|--|--|--|

| Syntax:   | [label] SUBWF f,d |  |  |  |

| Operands: | 0 ≤ f ≤ 127       |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |

| <b>C =</b> 0 | W > f               |

|--------------|---------------------|

| <b>C =</b> 1 | $W \leq f$          |

| DC = 0       | W<3:0> > f<3:0>     |

| DC = 1       | $W<3:0> \le f<3:0>$ |

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                     |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's<br>complement method). If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] SWAPF f,d                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |  |

| TRIS             | Load TRIS Register with W                                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                       |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                      |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register 'f'                                                                                                                  |  |  |  |  |

| Status Affected: | None                                                                                                                                                 |  |  |  |  |

| Description:     | Move data from W register to TRIS<br>register.<br>When 'f' = 5, TRISA is loaded.<br>When 'f' = 6, TRISB is loaded.<br>When 'f' = 7, TRISC is loaded. |  |  |  |  |

## TABLE 37-3:POWER-DOWN CURRENT (IPD)

| PIC16LF18856/76 |                        |                                          | Standard Operating Conditions (unless otherwise stated)               |       |       |        |            |      |                       |

|-----------------|------------------------|------------------------------------------|-----------------------------------------------------------------------|-------|-------|--------|------------|------|-----------------------|

| PIC16F18856/76  |                        |                                          | Standard Operating Conditions (unless otherwise stated)<br>VREGPM = 1 |       |       |        |            |      |                       |

| Param. Symbol   | Device Characteristics | Min                                      | Turn ±                                                                | Max.  | Max.  | Unite  | Conditions |      |                       |

| No.             | Symbol                 | Device Characteristics                   | Min.                                                                  | Тур.† | +85°C | +125°C | Units      | VDD  | Note                  |

| D200            | IPD                    | IPD Base                                 |                                                                       | 0.05  | 2     | 9      | μΑ         | 3.0V |                       |

| D200 IPD IPD Ba | PD Base                | _                                        | 0.4                                                                   | 4     | 12    | μΑ     | 3.0V       |      |                       |

| D200A           |                        |                                          |                                                                       | 10    | 15    | 20     | μΑ         | 3.0V | VREGPM = 0            |

| D201            | IPD_WDT                | Low-Frequency Internal<br>Oscillator/WDT | -                                                                     | 0.4   | -     | _      | μΑ         | 3.0V |                       |

| D201            | IPD_WDT                | Low-Frequency Internal<br>Oscillator/WDT | -                                                                     | 0.6   | 5     | 13     | μΑ         | 3.0V |                       |

| D202            | IPD_SOSC               | Secondary Oscillator (SOSC)              | _                                                                     | 0.6   | 5     | 13     | μΑ         | 3.0V |                       |

| D202            | IPD_SOSC               | Secondary Oscillator (SOSC)              |                                                                       | 0.8   | 8.5   | 15     | μΑ         | 3.0V |                       |

| D203            | IPD_FVR                | FVR                                      |                                                                       | 8     | 18    |        | μΑ         | 3.0V |                       |

| D203            | IPD_FVR                | FVR                                      |                                                                       | 10    | 20    |        | μΑ         | 3.0V |                       |

| D204            | IPD_BOR                | Brown-out Reset (BOR)                    | I                                                                     | 9     | 14    | 18     | μΑ         | 3.0V |                       |

| D204            | IPD_BOR                | Brown-out Reset (BOR)                    |                                                                       | 14    | 19    | 21     | μΑ         | 3.0V |                       |

| D205            | IPD_LPBOR              | Low-Power Brown-out Reset (LPBOR)        |                                                                       | 0.5   | —     | _      | μΑ         | 3.0V |                       |

| D205            | IPD_LPBOR              | Low-Power Brown-out Reset (LPBOR)        |                                                                       | 0.7   | _     | _      | μΑ         | 3.0V |                       |

| D206            | IPD_ADCA               | ADC - Active                             | -                                                                     | 250   | -     |        | μΑ         | 3.0V | ADC is converting (4) |

| D206            | IPD_ADCA               | ADC - Active                             | _                                                                     | 280   |       | _      | μΑ         | 3.0V | ADC is converting (4) |

| D207            | IPD_CMP                | Comparator                               | -                                                                     | 25    | 38    | 40     | μΑ         | 3.0V |                       |

| D207            | IPD_CMP                | Comparator                               | _                                                                     | 28    | 40    | 50     | μΑ         | 3.0V |                       |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

3: All peripheral currents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

4: ADC clock source is FRC.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

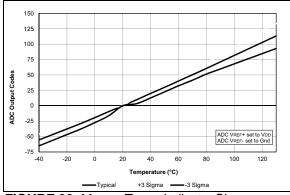

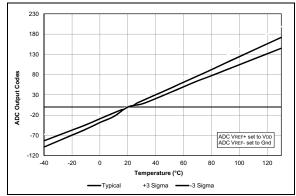

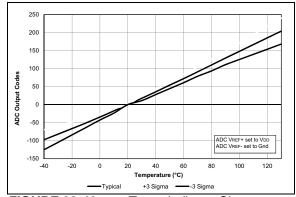

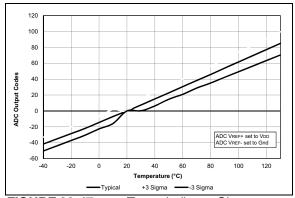

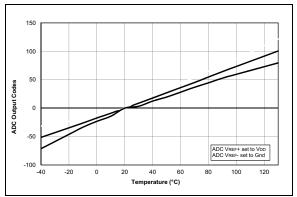

**FIGURE 38-43:** Temp. Indicator Initial Offset, Low Range, Temp. = 20°C, PIC16LF18856/76 Only.

**FIGURE 38-44:** Temp. Indicator Slope Normalized to 20°C, High Range, VDD = 5.5V, PIC16F18856/76 Only.

FIGURE 38-45: Temp. Indicator Slope Normalized to 20°C, High Range, VDD = 3.6V.

FIGURE 38-46: Temp. Indicator Slope Normalized to 20°C, High Range, VDD = 3.0V.

FIGURE 38-47: Temp. Indicator Slope Normalized to 20°C, Low Range, VDD = 3.6V.

FIGURE 38-48: Temp. Indicator Slope Normalized to 20°C, Low Range, VDD = 3.0V.