Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 28KB (16K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18856t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Rev. 10-000039J 11/20/2015 Program Flash Memory RAM PORTA CLKOUT /OSC2 Timing PORTB Generation CPU JLKIN, OSC1 ☑─► CLKIN/ PORTC INTRC Oscillator (Note 3) PORTD PORTE ADC Temp TMR0 TMR6 TMR5 TMR4 TMR3 TMR2 TMR1 CRC DSM C2 C1 DAC FVR Scanner 10-bit Indicator CWG1 CWG2 CWG3 SMT2 SMT1 NCO1 EUSART MSSP2 MSSP1 CLC4 CLC3 CLC2 CLC1 ZCD1 PWM6/7 CCPs(5)

- **Note 1:** See applicable chapters for more information on peripherals.

- 2: See Table 1-1 for peripherals available on specific devices.

PIC16(L)F18856/76 BLOCK DIAGRAM

- 3: See Figure 2-1.

- 4: PIC16(L)F18876 only.

FIGURE 1-1:

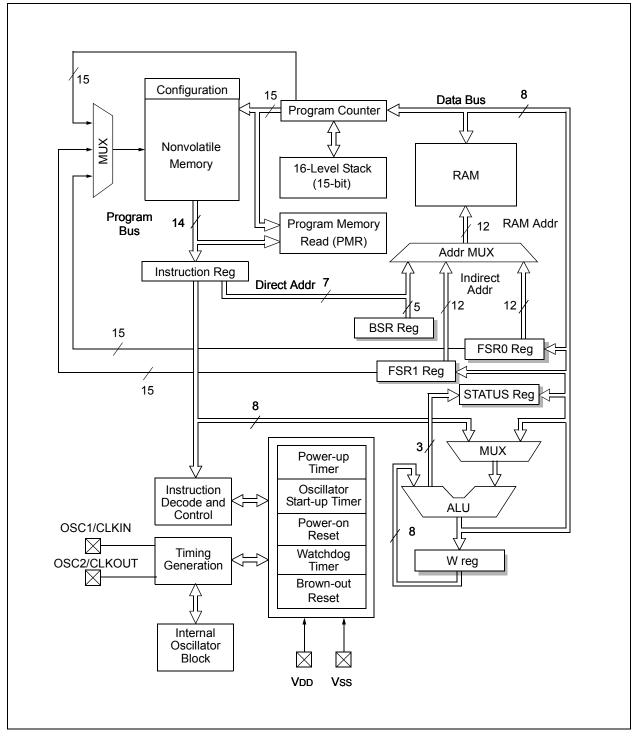

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16-levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## TABLE 3-5:PIC16F18856/76 MEMORY MAP BANK 8-15

|       | BANK 8         |       | BANK 9         |       | BANK 10        |      | BANK 11        |       | BANK 12        |      | BANK 13        |      | BANK 14        |       | BANK 15        |

|-------|----------------|-------|----------------|-------|----------------|------|----------------|-------|----------------|------|----------------|------|----------------|-------|----------------|

| 400h  |                | 480h  |                | 500h  |                | 580h |                | 600h  |                | 680h |                | 700h |                | 780h  |                |

|       | Core Registers |       | Core Registers |       | Core Registers |      | Core Registers |       | Core Registers |      | Core Registers |      | Core Registers |       | Core Registers |

|       | (Table 3-2)    |       | (Table 3-2)    |       | (Table 3-2)    |      | (Table 3-2)    |       | (Table 3-2)    |      | (Table 3-2)    |      | (Table 3-2)    |       | (Table 3-2)    |

| 40Bh  |                | 48Bh  |                | 50Bh  |                | 58Bh |                | 60Bh  |                | 68Bh |                | 70Bh |                | 78Bh  |                |

| 40Ch  | SCANLADRL      | 48Ch  | SMT1TMRL       | 50Ch  | SMT2TMRL       | 58Ch | NCO1ACCL       | 60Ch  | CWG1CLKCON     | 68Ch | CWG3CLKCON     | 70Ch | PIR0           | 78Ch  | —              |

| 40Dh  | SCANLADRH      | 48Dh  | SMT1TMRH       | 50Dh  | SMT2TMRH       | 58Dh | NCO1ACCH       | 60Dh  | CWG1ISM        | 68Dh | CWG3ISM        | 70Dh | PIR1           | 78Dh  | _              |

| 40Eh  | SCANHADRL      | 48Eh  | SMT1TMRU       | 50Eh  | SMT2TMRU       | 58Eh | NCO1ACCU       | 60Eh  | CWG1DBR        | 68Eh | CWG3DBR        | 70Eh | PIR2           | 78Eh  | —              |

| 40Fh  | SCANHADRH      | 48Fh  | SMT1CPRL       | 50Fh  | SMT2CPRL       | 58Fh | NCO1INCL       | 60Fh  | CWG1DBF        | 68Fh | CWG3DBF        | 70Fh | PIR3           | 78Fh  | —              |

| 410h  | SCANCON0       | 490h  | SMT1CPRH       | 510h  | SMT2CPRH       | 590h | NCO1INCH       | 610h  | CWG1CON0       | 690h | CWG3CON0       | 710h | PIR4           | 790h  | _              |

| 411h  | SCANTRIG       | 491h  | SMT1CPRU       | 511h  | SMT2CPRU       | 591h | NCO1INCU       | 611h  | CWG1CON1       | 691h | CWG3CON1       | 711h | PIR5           | 791h  | —              |

| 412h  | -              | 492h  | SMT1CPWL       | 512h  | SMT2CPWL       | 592h | NCO1CON        | 612h  | CWG1AS0        | 692h | CWG3AS0        | 712h | PIR6           | 792h  | —              |

| 413h  | —              | 493h  | SMT1CPWH       | 513h  | SMT2CPWH       | 593h | NCO1CLK        | 613h  | CWG1AS1        | 693h | CWG3AS1        | 713h | PIR7           | 793h  | —              |

| 414h  | -              | 494h  | SMT1CPWU       | 514h  | SMT2CPWU       | 594h | —              | 614h  | CWG1STR        | 694h | CWG3STR        | 714h | PIR8           | 794h  | —              |

| 415h  | —              | 495h  | SMT1PRL        | 515h  | SMT2PRL        | 595h | —              | 615h  | —              | 695h | —              | 715h | —              | 795h  | —              |

| 416h  | CRCDATL        | 496h  | SMT1PRH        | 516h  | SMT2PRH        | 596h | —              | 616h  | CWG2CLKCON     | 696h | —              | 716h | PIE0           | 796h  | PMD0           |

| 417h  | CRCDATH        | 497h  | SMT1PRU        | 517h  | SMT2PRU        | 597h | _              | 617h  | CWG2ISM        | 697h | _              | 717h | PIE1           | 797h  | PMD1           |

| 418h  | CRCACCL        | 498h  | SMT1CON0       | 518h  | SMT2CON0       | 598h | _              | 618h  | CWG2DBR        | 698h | -              | 718h | PIE2           | 798h  | PMD2           |

| 419h  | CRCACCH        | 499h  | SMT1CON1       | 519h  | SMT2CON1       | 599h | —              | 619h  | CWG2DBF        | 699h | -              | 719h | PIE3           | 799h  | PMD3           |

| 41Ah  | CRCSHIFTL      | 49Ah  | SMT1STAT       | 51Ah  | SMT2STAT       | 59Ah | _              | 61Ah  | CWG2CON0       | 69Ah | —              | 71Ah | PIE4           | 79Ah  | PMD4           |

| 41Bh  | CRCSHIFTH      | 49Bh  | SMT1CLK        | 51Bh  | SMT2CLK        | 59Bh | —              | 61Bh  | CWG2CON1       | 69Bh | —              | 71Bh | PIE5           | 79Bh  | PMD5           |

| 41Ch  | CRCXORL        | 49Ch  | SMT1SIG        | 51Ch  | SMT2SIG        | 59Ch | _              | 61Ch  | CWG2AS0        | 69Ch | —              | 71Ch | PIE6           | 79Ch  | —              |

| 41Dh  | CRCXORH        | 49Dh  | SMT1WIN        | 51Dh  | SMT2WIN        | 59Dh | —              | 61Dh  | CWG2AS1        | 69Dh | —              | 71Dh | PIE7           | 79Dh  | —              |

| 41Eh  | CRCCON0        | 49Eh  | —              | 51Eh  | —              | 59Eh | —              | 61Eh  | CWG2STR        | 69Eh | -              | 71Eh | PIE8           | 79Eh  | —              |

| 41Fh  | CRCCON1        | 49Fh  | —              | 51Fh  | —              | 59Fh | —              | 61Fh  | —              | 69Fh | —              | 71Fh | —              | 79Fh  | —              |

| 420h  |                | 4A0h  |                | 520h  |                | 5A0h |                | 620h  |                | 6A0h |                | 720h |                | 7A0h  |                |

|       | General        |       | General        |       | General        |      | General        |       | General        |      | General        |      | General        |       | General        |

|       | Purpose        |       | Purpose        |       | Purpose        |      | Purpose        |       | Purpose        |      | Purpose        |      | Purpose        |       | Purpose        |

|       | Register       |       | Register       |       | Register       |      | Register       |       | Register       |      | Register       |      | Register       |       | Register       |

|       | 80 Bytes       |       | 80 Bytes       |       | 80 Bytes       |      | 80 Bytes       |       | 80 Bytes       |      | 80 Bytes       |      | 80 Bytes       |       | 80 Bytes       |

| 46Fh  |                | 4EFh  |                | 56Fh  |                | 5EFh |                | 66Fh  |                | 6EFh |                | 76Fh |                | 7EFh  |                |

| 470h  | Common RAM     | 4F0h  | Common RAM     | 570h  | Common RAM     | 5F0h | Common RAM     | 670h  | Common RAM     | 6F0h | Common RAM     | 770h | Common RAM     | 7F0h  | Common RAM     |

|       | Accesses       |       | Accesses       |       | Accesses       |      | Accesses       |       | Accesses       |      | Accesses       |      | Accesses       |       | Accesses       |

| 47Fh  | 70h – 7Fh      | 4FFh  | 70h – 7Fh      | 57Fh  | 70h – 7Fh      | 5FFh | 70h – 7Fh      | 67Fh  | 70h – 7Fh      | 6FFh | 70h – 7Fh      | 77Fh | 70h – 7Fh      | 7FFh  | 70h – 7Fh      |

| 4/111 |                | +1111 |                | 5/111 |                | 5111 |                | 0/111 |                |      |                |      |                | (1111 |                |

**Legend:** = Unimplemented data memory locations, read as '0'.

## PIC16(L)F18856/76

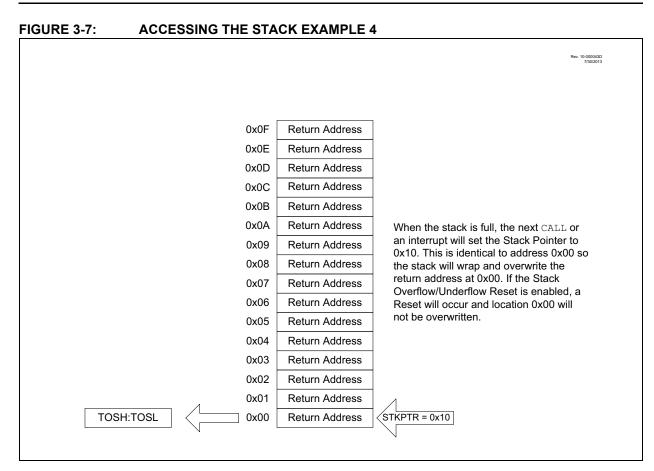

## 3.4.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

## 3.5 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional Data Memory

- · Linear Data Memory

- Data EEPROM Memory

- Program Flash Memory

## 6.2.1.4 4x PLL

The oscillator module contains a PLL that can be used with external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 37-9.

The PLL may be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to enable the EXTOSC with 4x PLL.

- 2. Write the NOSC bits in the OSCCON1 register to enable the EXTOSC with 4x PLL.

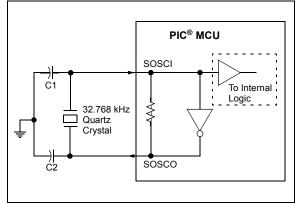

### 6.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 31 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during run-time using clock switching. Refer to **Section 6.3 "Clock Switching"** for more information.

### FIGURE 6-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

# PIC16(L)F18856/76

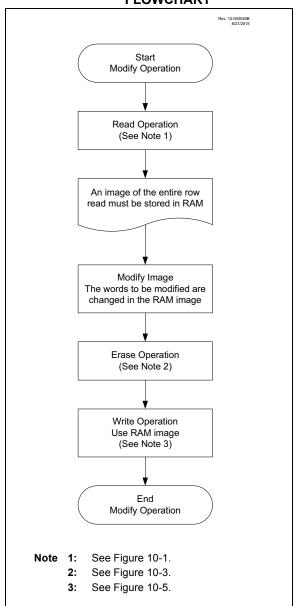

### 10.4.6 MODIFYING FLASH PROGRAM MEMORY

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

#### FIGURE 10-6:

#### FLASH PROGRAM MEMORY MODIFY FLOWCHART

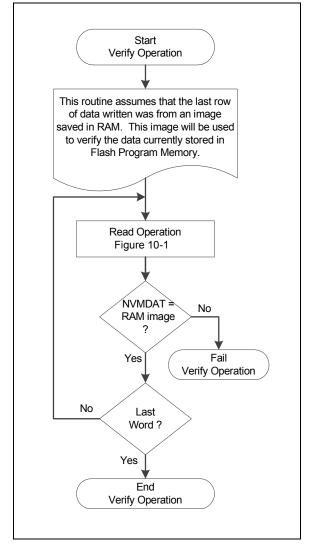

## 10.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

## 11.7 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic Program Memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 11.4 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word – 1 (refer to Example 11-1). This determines how many times the shifter will shift into the accumulator for each data word.

- Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial – 2 (refer to Example 11-1).

- Determine whether shifting in trailing zeros is desired and set the ACCM bit of CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of CRCCON0 register appropriately.

- 8. Write the CRCGO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has >8 bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically stuff words into the CRCDATH/L registers as needed, as long as the SCANGO bit is set.

- 10a. If using the Flash memory scanner, monitor the SCANIF (or the SCANGO bit) for the scanner to finish pushing information into the CRCDATA registers. After the scanner is completed, monitor the CRCIF (or the BUSY bit) to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set (or both BUSY and SCANGO bits are cleared), the completed CRC calculation can be read from the CRCACCH/L registers.

- 10b.If manual entry is used, monitor the CRCIF (or BUSY bit) to determine when the CRCACC registers will hold the check value.

## 11.8 Program Memory Scan Configuration

If desired, the Program Memory Scan module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory addresses. In order to set up the Scanner to work with the CRC you need to perform the following steps:

- Set the EN bit to enable the module. This can be performed at any point preceding the setting of the SCANGO bit, but if it gets disabled, all internal states of the Scanner are reset (registers are unaffected).

- Choose which memory access mode is to be used (see Section 11.10 "Scanning Modes") and set the MODE bits of the SCANCON0 register appropriately.

- 3. Based on the memory access mode, set the INTM bits of the SCANCON0 register to the appropriate interrupt mode (see Section 11.10.5 "Interrupt Interaction")

- 4. Set the SCANLADRL/H and SCANHADRL/H registers with the beginning and ending locations in memory that are to be scanned.

- 5. Begin the scan by setting the SCANGO bit in the SCANCON0 register. The scanner will wait (CRCGO must be set) for the signal from the CRC that it is ready for the first Flash memory location, then begin loading data into the CRC. It will continue to do so until it either hits the configured end address or an address that is unimplemented on the device, at which point the SCANGO bit will clear, Scanner functions will cease, and the SCANIF interrupt will be triggered. Alternately, the SCANGO bit can be cleared in software if desired.

## 11.9 Scanner Interrupt

The scanner will trigger an interrupt when the SCANGO bit transitions from '1' to '0'. The SCANIF interrupt flag of PIR7 is set when the last memory location is reached and the data is entered into the CRCDATA registers. The SCANIF bit can only be cleared in software. The SCAN interrupt enable is the SCANIE bit of the PIE7 register.

## 11.10 Scanning Modes

The memory scanner can scan in four modes: Burst, Peek, Concurrent, and Triggered. These modes are controlled by the MODE bits of the SCANCON0 register. The four modes are summarized in Table 11-1.

## 12.10.8 CURRENT-CONTROLLED DRIVE MODE CONTROL

The CCDPD and CCDND registers (Register 12-40 and Register 12-41) control the Current-Controlled Drive mode for both the positive-going and negative-going drivers. When a CCDPD[y] or CCDND[y] bit is set and the CCDEN bit of the CCDCON register is set, the Current-Controlled mode is enabled for the corresponding port pin. When the CCDPD[y] or CCDND[y] bit is clear, the Current-Controlled mode for the corresponding port pin is disabled. If the CCDPD[y] or CCDND[y] bit is set and the CCDEN bit is clear, operation of the port pin is undefined (see **Section 12.1.1** "**Current-Controlled Drive**" for current-controlled use precautions).

## 12.10.9 PORTD FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode. u = Bit is unchanged

| U-0            | U-0 | U-0          | U-0 | U-0          | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|----------------|-----|--------------|-----|--------------|------------------|---------|---------|

| —              | _   | _            | _   | _            | CCDPE2           | CCDPE1  | CCDPE0  |

| bit 7          |     |              |     |              | •                |         | bit 0   |

|                |     |              |     |              |                  |         |         |

| Legend:        |     |              |     |              |                  |         |         |

| R = Readable b | it  | W = Writable | bit | U = Unimpler | mented bit, read | as '0'  |         |

-n/n = Value at POR and BOR/Value at all other Resets

### **REGISTER 12-53: CCDPE: CURRENT CONTROL DRIVE NEGATIVE PORTE REGISTER**

| '1' = Bit is set      | '0' = Bit is cleared                                                           |

|-----------------------|--------------------------------------------------------------------------------|

| <b>h</b> # <b>7</b> 0 | Unimplemented: Deed on (o)                                                     |

| bit 7-3               | Unimplemented: Read as '0'                                                     |

| bit 2-0               | CCDPE<2:0>: RE<2:0> Current Control Drive Positive Control bits <sup>(1)</sup> |

|                       | 1 = Current control source enabled                                             |

0 = Current control source disabled

x = Bit is unknown

Note 1: If CCDPEy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

### **REGISTER 12-54: CCDNE: CURRENT CONTROL DRIVE NEGATIVE PORTE REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 R/W-0/0 |        | R/W-0/0 |

|-------|-----|-----|-----|-----|-----------------|--------|---------|

| _     |     |     | _   | _   | CCDNE2          | CCDNE1 | CCDNE0  |

| bit 7 |     |     |     |     |                 |        | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as | '0' |

|---------|------------------------|-----|

|---------|------------------------|-----|

CCDNE<2:0>: RE<2:0> Current Control Drive Negative Control bits<sup>(1)</sup> bit 2-0

- 1 = Current control source enabled

- 0 = Current control source disabled

Note 1: If CCDNEy is set, when CCDEN = 0 (Register 12-1), operation of the pin is undefined.

## 24.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 24-2.

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

## 24.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 24-2.

The value of the active and inactive states depends on the polarity bit, N1POL in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

### 24.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then DDS operation is undefined.

## 24.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO output signal is available to the following peripherals:

- CLC

- CWG

- Timer1/3/5

- Timer2/4/6

- SMT

- DSM

- Reference Clock Output

#### 24.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO Interrupt Flag bit, NCO1IF, of the PIR7 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- N1EN bit of the NCO1CON register

- · NCO1IE bit of the PIE7 register

- PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

## 24.6 Effects of a Reset

All of the NCO registers are cleared to zero as the result of a Reset.

## 24.7 Operation in Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

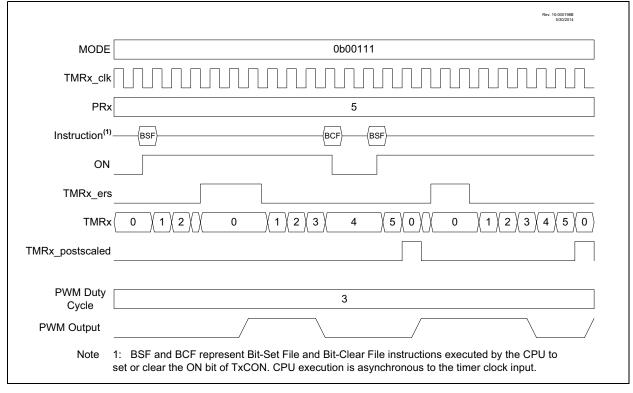

### 29.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 29-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

| R/W/HC-0/0        | R/W-0/0                                        | R/W-0/0            | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |

|-------------------|------------------------------------------------|--------------------|-----------------|-----------------|------------------|----------------|--------------|--|--|--|

| 0N <sup>(1)</sup> |                                                | CKPS<2:0>          |                 |                 | OUTP             | S<3:0>         |              |  |  |  |

| bit 7             |                                                |                    |                 |                 |                  |                | bit 0        |  |  |  |

| Legend:           |                                                |                    |                 |                 |                  |                |              |  |  |  |

| R = Readable      | bit                                            | W = Writable       | bit             | U = Unimplen    | nented bit, read | d as '0'       |              |  |  |  |

| u = Bit is unch   |                                                | x = Bit is unkr    |                 | •               |                  | R/Value at all | other Resets |  |  |  |

| '1' = Bit is set  | J                                              | '0' = Bit is clea  | ared            |                 | eared by hardw   |                |              |  |  |  |

| bit 7             | <b>ON:</b> Timerx                              | On hit             |                 |                 |                  |                |              |  |  |  |

|                   | 1 = Timerx                                     |                    |                 |                 |                  |                |              |  |  |  |

|                   |                                                | is off: all counte | rs and state m  | achines are res | set              |                |              |  |  |  |

| bit 6-4           | CKPS<2:0>                                      | : Timer2-type Cl   | ock Prescale    | Select bits     |                  |                |              |  |  |  |

|                   | 111 = 1:128                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 111 = 1.64 Prescaler                           |                    |                 |                 |                  |                |              |  |  |  |

|                   | 101 = 1:32 Prescaler                           |                    |                 |                 |                  |                |              |  |  |  |

|                   | 100 = 1:16 Prescaler                           |                    |                 |                 |                  |                |              |  |  |  |

|                   | 011 = 1:8 Prescaler                            |                    |                 |                 |                  |                |              |  |  |  |

|                   | 010 = 1:4 P                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 001 = 1:2 P                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 000 = 1:1 P                                    | rescaler           |                 |                 |                  |                |              |  |  |  |

| bit 3-0           | OUTPS<3:0                                      | >: Timerx Outpu    | it Postscaler S | Select bits     |                  |                |              |  |  |  |

|                   | 1111 <b>= 1:16</b>                             |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1110 = 1:15                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1101 = 1:14                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1100 = 1:13                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1011 = 1:12                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1010 = 1:11                                    |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1001 = 1:10  Postscaler                        |                    |                 |                 |                  |                |              |  |  |  |

|                   | 1000 = 1:9 Postscaler<br>0111 = 1:8 Postscaler |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0111 – 1.6 Postscaler                          |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0101 = 1:6 F                                   |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0100 = 1:5 F                                   |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0011 = 1:4 F                                   |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0010 = 1:3 F                                   |                    |                 |                 |                  |                |              |  |  |  |

|                   | 0001 = 1:2 F                                   | Postscaler         |                 |                 |                  |                |              |  |  |  |

|                   | 0000 = 1:1 F                                   | Postscaler         |                 |                 |                  |                |              |  |  |  |

## REGISTER 29-2: TxCON: TIMER2/4/6 CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 29.5 "Operation Examples".

## 32.6.3 PERIOD AND DUTY-CYCLE MODE

In Duty-Cycle mode, either the duty cycle or period (depending on polarity) of the SMTx\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMTxTMR resetting to 0x0001. In addition, the SMTxGO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 32-6 and Figure 32-7.

### 33.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RC1STA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

ASYNCHRONOUS RECEPTION

### 33.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RC1STA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| RX/DT pin                                      | Start<br>bit / bit 0 / bit 1 / 5 / bit 7/8 / Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rcv Shift<br>Reg →<br>Rcv Buffer Reg.<br>RCIDL | Word 1 Word 2 Streng St |

| Read Rcv<br>Buffer Reg.<br>RCREG               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RCIF<br>(Interrupt Flag)                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OERR bit                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CREN                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                | timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, sing the OERR (overrun) bit to be set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

FIGURE 33-5:

## PIC16(L)F18856/76

## TABLE 37-14: COMPARATOR SPECIFICATIONS

| Operating Conditions (unless otherwise stated)<br>/DD = 3.0V, TA = 25°C |                      |                                   |      |      |      |       |              |  |  |  |

|-------------------------------------------------------------------------|----------------------|-----------------------------------|------|------|------|-------|--------------|--|--|--|

| Param.<br>No.                                                           | Sym.                 | Characteristics                   | Min. | Тур. | Max. | Units | Comments     |  |  |  |

| CM01                                                                    | VIOFF                | Input Offset Voltage              | _    |      | ±30  | mV    | VICM = VDD/2 |  |  |  |

| CM02                                                                    | VICM                 | Input Common Mode Range           | GND  | _    | Vdd  | V     |              |  |  |  |

| CM03                                                                    | CMRR                 | Common Mode Input Rejection Ratio | _    | 50   |      | dB    |              |  |  |  |

| CM04                                                                    | VHYST                | Comparator Hysteresis             | 15   | 25   | 35   | mV    |              |  |  |  |

| CM05                                                                    | TRESP <sup>(1)</sup> | Response Time, Rising Edge        |      | 300  | 600  | ns    |              |  |  |  |

|                                                                         |                      | Response Time, Falling Edge       | —    | 220  | 500  | ns    |              |  |  |  |

These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at VDD/2, while the other input transitions from Vss to VDD.

2: A mode change includes changing any of the control register values, including module enable.

## TABLE 37-15: 5-BIT DAC SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |       |                              |      |                             |       |       |          |  |  |  |

|----------------------------------------------------------------------------------|-------|------------------------------|------|-----------------------------|-------|-------|----------|--|--|--|

| Param.<br>No.                                                                    | Sym.  | Characteristics              | Min. | Тур.                        | Max.  | Units | Comments |  |  |  |

| DSB01                                                                            | VLSB  | Step Size                    | —    | (VDACREF+ -VDACREF-)<br>/32 |       | V     |          |  |  |  |

| DSB01                                                                            | VACC  | Absolute Accuracy            |      | —                           | ± 0.5 | LSb   |          |  |  |  |

| DSB03*                                                                           | RUNIT | Unit Resistor Value          | —    | 5000                        | _     | Ω     |          |  |  |  |

| DSB04*                                                                           | Tst   | Settling Time <sup>(1)</sup> | —    | _                           | 10    | μS    |          |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Settling time measured while DACR<4:0> transitions from '00000' to '01111'.

## TABLE 37-16: FIXED VOLTAGE REFERENCE (FVR) SPECIFICATIONS

| Standard      | Standard Operating Conditions (unless otherwise stated) |                   |      |      |      |       |                                 |  |  |  |  |

|---------------|---------------------------------------------------------|-------------------|------|------|------|-------|---------------------------------|--|--|--|--|

| Param.<br>No. | Symbol                                                  | Characteristic    | Min. | Тур. | Max. | Units | Conditions                      |  |  |  |  |

| FVR01         | VFVR1                                                   | 1x Gain (1.024V)  | -4   | _    | +4   | %     | VDD $\ge$ 2.5V, -40°C to 85°C   |  |  |  |  |

| FVR02         | VFVR2                                                   | 2x Gain (2.048V)  | -4   | _    | +4   | %     | VDD $\ge$ 2.5V, -40°C to 85°C   |  |  |  |  |

| FVR03         | VFVR4                                                   | 4x Gain (4.096V)  | -5   | _    | +5   | %     | VDD $\geq$ 4.75V, -40°C to 85°C |  |  |  |  |

| FVR04         | TFVRST                                                  | FVR Start-up Time |      | 25   | _    | us    |                                 |  |  |  |  |

## TABLE 37-17: ZERO CROSS DETECT (ZCD) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>VDD = 3.0V, TA = 25°C |          |                                |     |      |     |       |          |

|----------------------------------------------------------------------------------|----------|--------------------------------|-----|------|-----|-------|----------|

| Param.<br>No.                                                                    | Sym.     | Characteristics                | Min | Тур† | Мах | Units | Comments |

| ZC01                                                                             | VPINZC   | Voltage on Zero Cross Pin      | -   | 0.75 | —   | V     |          |

| ZC02                                                                             | IZCD_MAX | Maximum source or sink current | —   | —    | 600 | μA    |          |

| ZC03                                                                             | TRESPH   | Response Time, Rising Edge     | _   | 1    | —   | μS    |          |

|                                                                                  | TRESPL   | Response Time, Falling Edge    | _   | 1    | —   | μS    |          |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

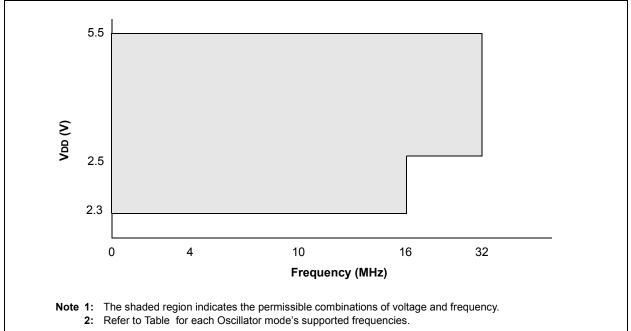

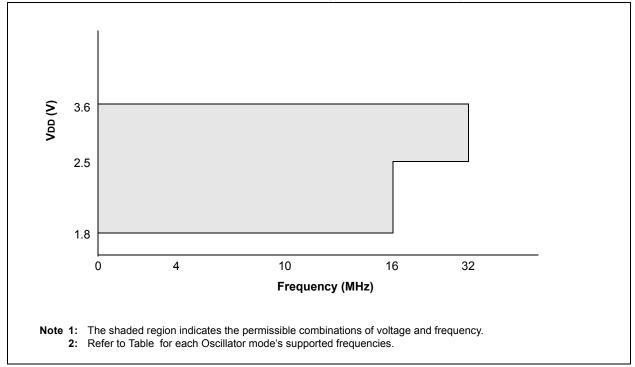

## 38.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei Tel: 886-2-2508-8600

Fax: 886-2-2508-0102 Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40 Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820