Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18876-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIN ALLOCATION TABLES**

## TABLE 2: 28-PIN ALLOCATION TABLE (PIC16(L)F18856)

| O/I | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC                           | Voltage Reference | DAC      | Comparators      | Zero-Cross Detect | MSSP (SPUI <sup>2</sup> C)                   | EUSART | WSQ                   | Timers/SMT                                   | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change         | Basic          |

|-----|------------------------|---------------|-------------------------------|-------------------|----------|------------------|-------------------|----------------------------------------------|--------|-----------------------|----------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|-----------------------------|----------------|

| RA0 | 2                      | 27            | ANA0                          | _                 | _        | C1IN0-<br>C2IN0- | -                 | —                                            | _      | —                     | —                                            | _                   | —                     | CLCIN0 <sup>(1)</sup> | -   | -                      | IOCA0                       | —              |

| RA1 | 3                      | 28            | ANA1                          | _                 | _        | C1IN1-<br>C2IN1- | _                 | —                                            | _      | _                     | —                                            | _                   | —                     | CLCIN1 <sup>(1)</sup> | —   | _                      | IOCA1                       | —              |

| RA2 | 4                      | 1             | ANA2                          | VREF-             | DAC1OUT1 | C1IN0+<br>C2IN0+ | _                 | —                                            | _      | _                     | —                                            | _                   | —                     | _                     | _   | _                      | IOCA2                       | —              |

| RA3 | 5                      | 2             | ANA3                          | VREF+             | _        | C1IN1+           | _                 | —                                            | —      | MDCARL <sup>(1)</sup> | —                                            | _                   | —                     | —                     | —   | —                      | IOCA3                       | —              |

| RA4 | 6                      | 3             | ANA4                          | _                 | _        | —                |                   | —                                            | -      | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                         | CCP5 <sup>(1)</sup> | —                     | _                     | —   | _                      | IOCA4                       | —              |

| RA5 | 7                      | 4             | ANA5                          | _                 | _        | —                |                   | SS1 <sup>(1)</sup>                           |        | MDSRC <sup>(1)</sup>  | —                                            | _                   | —                     | _                     | _   |                        | IOCA5                       | —              |

| RA6 | 10                     | 7             | ANA6                          | _                 | _        | —                |                   | _                                            | _      | _                     | —                                            | -                   | _                     | _                     | -   |                        | IOCA6                       | OSC2<br>CLKOUT |

| RA7 | 9                      | 6             | ANA7                          | _                 | _        | _                | _                 | —                                            | _      | _                     | —                                            | _                   | —                     | _                     | —   | _                      | IOCA7                       | OSC1<br>CLKIN  |

| RB0 | 21                     | 18            | ANB0                          | Ι                 | —        | C2IN1+           | ZCD               | SS2 <sup>(1)</sup>                           | _      | -                     | —                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | Ι                     |     | —                      | INT <sup>(1)</sup><br>IOCB0 | -              |

| RB1 | 22                     | 19            | ANB1                          | _                 | _        | C1IN3-<br>C2IN3- | _                 | SCL2 <sup>(3,4)</sup><br>SCK2 <sup>(1)</sup> | _      | _                     | —                                            | _                   | CWG2IN <sup>(1)</sup> | _                     | —   | _                      | IOCB1                       | —              |

| RB2 | 23                     | 20            | ANB2                          | _                 | —        | _                | _                 | SDA2 <sup>(3,4)</sup><br>SDI2 <sup>(1)</sup> | _      | _                     | —                                            | _                   | CWG3IN <sup>(1)</sup> | _                     | -   |                        | IOCB2                       | —              |

| RB3 | 24                     | 21            | ANB3                          | —                 | —        | C1IN2-<br>C2IN2- | —                 | —                                            | _      | _                     | —                                            | —                   | —                     | —                     | -   |                        | IOCB3                       | —              |

| RB4 | 25                     | 22            | ANB4<br>ADCACT <sup>(1)</sup> | _                 | _        | —                |                   | —                                            |        | —                     | T5G <sup>(1)</sup><br>SMTWIN2 <sup>(1)</sup> | _                   | —                     | —                     | -   |                        | IOCB4                       | —              |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTX pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTX pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

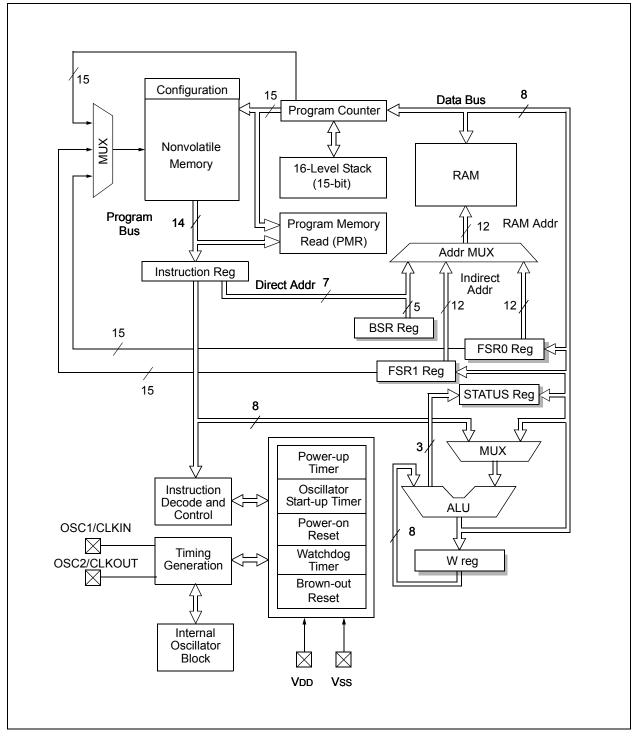

# 2.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16-levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and

FIGURE 2-1: CORE BLOCK DIAGRAM

Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

## TABLE 3-11: PIC16(L)F18876 MEMORY MAP, BANK 30

| TADLE 5-11. |         |      | , DANK 30 |      |

|-------------|---------|------|-----------|------|

|             | Bank 30 |      | Bank 30   |      |

| F0Ch        | _       | F40h | CCDNA     | F64h |

| F0Dh        |         | F41h | CCDPA     | F65h |

| F0Eh        |         | F42h | _         | F66h |

| F0Fh        | _       | F43h | ANSELB    | F67h |

| F10h        | RA0PPS  | F44h | WPUB      | F68h |

| F11h        | RA1PPS  | F45h | ODCONB    | F69h |

| F12h        | RA2PPS  | F46h | SLRCONB   | F6Ah |

| F13h        | RA3PPS  | F47h | INLVLB    | F6Bh |

| F14h        | RA4PPS  | F48h | IOCBP     | F6Ch |

| F15h        | RA5PPS  | F49h | IOCBN     | F6Dh |

| F16h        | RA6PPS  | F4Ah | IOCBF     | F6Eh |

| F17h        | RA7PPS  | F4Bh | CCDNB     | F6Fh |

| F18h        | RB0PPS  | F4Ch | CCDPB     |      |

| F19h        | RB1PPS  | F4Dh | _         |      |

| F1Ah        | RB2PPS  | F4Eh | ANSELC    |      |

| F1Bh        | RB3PPS  | F4Fh | WPUC      |      |

| F1Ch        | RB4PPS  | F50h | ODCONC    |      |

| F1Dh        | RB5PPS  | F51h | SLRCONC   |      |

| F1Eh        | RB6PPS  | F52h | INLVLC    |      |

| F1Fh        | RB7PPS  | F53h | IOCCP     |      |

| F20h        | RC0PPS  | F54h | IOCCN     |      |

| F21h        | RC1PPS  | F55h | IOCCF     |      |

| F22h        | RC2PPS  | F56h | CCDNC     |      |

| F23h        | RC3PPS  | F57h | CCDPC     |      |

| F24h        | RC4PPS  | F58h | _         |      |

| F25h        | RC5PPS  | F59h | ANSELD    |      |

| F26h        | RC6PPS  | F5Ah | WPUD      |      |

| F27h        | RC7PPS  | F5Bh | ODCOND    |      |

| F28h        |         | F5Ch | SLRCOND   |      |

|             | —       | F5Dh | INLVLD    |      |

| F37h        |         | F5Eh | _         |      |

| F38h        | ANSELA  | F5Fh | _         |      |

| F39h        | WPUA    | F60h | _         |      |

| F3Ah        | ODCONA  | F61h | CCDND     |      |

| F3Bh        | SLRCONA | F62h | CCDPD     |      |

| F3Ch        | INLVLA  | F63h | _         |      |

| F3Dh        | IOCAP   |      |           |      |

| F3Eh        | IOCAN   |      |           |      |

| F3Fh        | IOCAF   |      |           |      |

|             |         |      |           |      |

Legend:

= Unimplemented data memory locations, read as '0'.

Bank 30

ANSELE

WPUE

ODCONE

SLRCONE

INLVLE

IOCEN

IOCEN

CCDNE

CCDPE

—

| Address | Name     | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7 | Bit 6             | Bit 5 | Bit 4         | Bit 3            | Bit 2         | Bit 1 | Bit 0     | Value on:<br>POR, BOR | Value on all other Resets |

|---------|----------|----------------------------------|-------|-------------------|-------|---------------|------------------|---------------|-------|-----------|-----------------------|---------------------------|

| Bank 29 | )        |                                  |       |                   |       |               |                  |               |       |           |                       |                           |

|         |          |                                  |       |                   | CPU   |               | S; see Table 3-2 | for specifics |       |           |                       |                           |

| E8Ch    | _        | _                                |       |                   |       | U             | nimplemented     |               |       |           | —                     | —                         |

| E8Dh    | _        | —                                |       | Unimplemented — — |       |               |                  |               |       |           |                       | —                         |

| E8Eh    | —        | —                                |       | Unimplemented — — |       |               |                  |               |       |           |                       | —                         |

| E8Fh    | PPSLOCK  |                                  | _     | —                 | _     | —             | -                | _             | _     | PPSLOCKED | 0                     | 0                         |

| E90h    | INTPPS   |                                  | —     | —                 | —     | _             | - INTPPS<3:0>    |               |       |           | 1000                  | uuuu                      |

| E91h    | TOCKIPPS |                                  | _     | —                 | _     | _             | - T0CKIPPS<3:0>  |               |       |           | 0100                  | uuuu                      |

| E92h    | T1CKIPPS |                                  | _     | —                 | _     |               | T1CKIPPS<4:0>    |               |       |           | 1 0000                | u uuuu                    |

| E93h    | T1GPPS   |                                  | —     | —                 | —     |               | T1GPPS<4:0>      |               |       |           | 0 1101                | u uuuu                    |

| E94h    | T3CKIPPS |                                  | _     | —                 | —     | T3CKIPPS<4:0> |                  |               |       | 1 0000    | u uuuu                |                           |

| E95h    | T3GPPS   |                                  | _     | —                 | —     |               |                  | T3GPPS<4:0>   |       |           | 1 0000                | u uuuu                    |

| E96h    | T5CKIPPS |                                  | _     | —                 | _     |               |                  | T5CKIPPS<4:0> |       |           | 1 0000                | u uuuu                    |

| E97h    | T5GPPS   |                                  | _     | _                 | _     |               |                  | T5GPPS<4:0>   |       |           | 0 1100                | u uuuu                    |

| E98h    | —        | —                                |       |                   |       | U             | nimplemented     |               |       |           | _                     | —                         |

| E99h    | —        | —                                |       |                   |       | U             | nimplemented     |               |       |           | _                     | —                         |

| E9Ah    | —        | —                                |       |                   |       | U             | nimplemented     |               |       |           | _                     | —                         |

| E9Bh    | _        | —                                |       |                   |       | U             | nimplemented     |               |       |           | _                     | —                         |

| E9Ch    | T2AINPPS |                                  | —     | —                 | —     | T2AINPPS<4:0> |                  |               |       | 1 0011    | u uuuu                |                           |

| E9Dh    | T4AINPPS |                                  | _     | —                 | —     | T4AINPPS<4:0> |                  |               |       | 1 0101    | u uuuu                |                           |

| E9Eh    | T6AINPPS |                                  | —     | —                 |       |               |                  |               |       |           | u uuuu                |                           |

| E9Fh    | _        | -                                |       | Unimplemented — — |       |               |                  |               |       |           |                       |                           |

| EA0h    | —        | -                                |       |                   |       | U             | nimplemented     |               |       |           | _                     | —                         |

| EA1h    | CCP1PPS  |                                  | -     | -                 | —     |               |                  | CCP1PPS<4:0>  |       |           | 1 0010                | u uuuu                    |

####

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Register present on PIC16F18855/75 devices only. Legend:

Note 1:

2: Unimplemented, read as '1'.

# 5.13 Register Definitions: Power Control

## REGISTER 5-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |            | •          |            |            |            | bit 0      |

| Legend:                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                                                                                                                             |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| HC = Bit is cle                                                                                                                                                                    | ared by hardwa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | are                                                                                     | HS = Bit is set by hardware                                                                                                 |  |  |  |  |

| R = Readable                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable bit                                                                        | U = Unimplemented bit, read as '0'                                                                                          |  |  |  |  |

| u = Bit is unch                                                                                                                                                                    | anged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | x = Bit is unknown                                                                      | -m/n = Value at POR and BOR/Value at all other Resets                                                                       |  |  |  |  |

| '1' = Bit is set                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is cleared                                                                    | q = Value depends on condition                                                                                              |  |  |  |  |

| bit 7                                                                                                                                                                              | 1 = A Stack (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ack Overflow Flag bit<br>Overflow occurred<br>Overflow bas not occurred o               | r cleared by firmware                                                                                                       |  |  |  |  |

| <ul> <li>bit 6</li> <li>STKUNF: Stack Underflow Flag bit</li> <li>1 = A Stack Underflow occurred</li> <li>0 = A Stack Underflow has not occurred or cleared by firmware</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                                                                                                                             |  |  |  |  |

| bit 5                                                                                                                                                                              | 1 = A WDT W<br>0 = A WDT W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /indow Violation Reset has                                                              | not occurred or set by firmware<br>occurred (a CLRWDT instruction was executed either without<br>ndow (cleared by hardware) |  |  |  |  |

| bit 4                                                                                                                                                                              | 1 = A Watchd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ndog Timer Reset Flag bit<br>log Timer Reset has not occ<br>log Timer Reset has occurre | urred or set to '1' by firmware<br>ed (cleared by hardware)                                                                 |  |  |  |  |

| bit 3                                                                                                                                                                              | 1 = A MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IR Reset Flag bit<br>Reset has not occurred or s<br>Reset has occurred (cleared         |                                                                                                                             |  |  |  |  |

| bit 2                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                                                                                                                             |  |  |  |  |

| bit 1 <b>POR:</b> Power-on Reset Status bit<br>1 = No Power-on Reset occurred<br>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |                                                                                                                             |  |  |  |  |

| bit 0                                                                                                                                                                              | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset occurred (must be set in software after a Power-on Reset oc</li></ul> |                                                                                         |                                                                                                                             |  |  |  |  |

| TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESE | ABLE 5-5: | BLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS |

|------------------------------------------------------|-----------|------------------------------------------------------|

|------------------------------------------------------|-----------|------------------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------|------------|-------|-------|-------|--------|---------------------|

| BORCON  | SBOREN |        |       |            |       |       |       | BORRDY | 104                 |

| PCON0   | STKOVF | STKUNF | WDTWV | RWDT       | RMCLR | RI    | POR   | BOR    | 109                 |

| STATUS  | _      | _      | _     | TO         | PD    | Z     | DC    | С      | 38                  |

| WDTCON0 |        |        |       | WDTPS<4:0> |       |       |       |        | 166                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase Lock Loop (PLL) that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce a range from 1 to 32 MHz. The Low-Frequency Internal Oscillator (LFINTOSC) generates a 31 kHz frequency. The external oscillator block can also be used with the PLL. See **Section 6.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset

- Write the NOSC<2:0> and NDIV<4:0> bits in the OSCCON1 register to switch the system clock source

See **Section 6.3 "Clock Switching**" for more information.

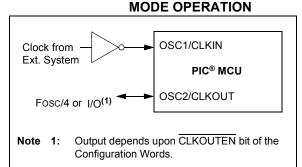

## 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.1-4 MHz

- ECL Low power, 0-0.1 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

# 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| REGISTER I       | -/. FIE3.                                            | FERIFIERA                                                |                                                                      |                  | REGISTER 5       |         |         |  |

|------------------|------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------|------------------|------------------|---------|---------|--|

| R/W-0/0          | R/W-0/0                                              | R/W-0/0                                                  | R/W-0/0                                                              | U-0              | R/W-0/0          | R/W-0/0 | R/W-0/0 |  |

| CLC4IE           | CLC3IE                                               | CLC2IE                                                   | CLC1IE                                                               | —                | TMR5GIE          | TMR3GIE | TMR1GIE |  |

| bit 7            |                                                      |                                                          |                                                                      |                  |                  |         | bit 0   |  |

|                  |                                                      |                                                          |                                                                      |                  |                  |         |         |  |

| Legend:          |                                                      |                                                          |                                                                      |                  |                  |         |         |  |

| R = Readable     |                                                      | W = Writable                                             |                                                                      |                  | mented bit, read |         |         |  |

| u = Bit is unch  | •                                                    |                                                          | Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                  |                  |         |         |  |

| '1' = Bit is set |                                                      | '0' = Bit is cle                                         | ared                                                                 | HS = Hardwa      | are set          |         |         |  |

| bit 7            | 1 = CLC4 ir                                          | C4 Interrupt Ena<br>Iterrupt enabled                     | b                                                                    |                  |                  |         |         |  |

| bit 6            | 1 = CLC3 ir                                          | C3 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b                                                                    |                  |                  |         |         |  |

| bit 5            | 1 = CLC2 ir                                          | C2 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b                                                                    |                  |                  |         |         |  |

| bit 4            | 1 = CLC1 ir                                          | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable | b                                                                    |                  |                  |         |         |  |

| bit 3            | Unimplemer                                           | ted: Read as '                                           | 0'                                                                   |                  |                  |         |         |  |

| bit 2            | 1 = Enables                                          | mer5 Gate Inte<br>s the Timer5 ga<br>s the Timer5 ga     | te acquisition                                                       | interrupt        |                  |         |         |  |

| bit 1            | 1 = Enables                                          | mer3 Gate Inte<br>the Timer3 ga<br>s the Timer3 ga       | te acquisition                                                       | interrupt        |                  |         |         |  |

| bit 0            | TMR1GIE: Ti<br>1 = Enables                           | mer1 Gate Inte<br>the Timer1 ga<br>s the Timer1 ga       | rrupt Enable te acquisition                                          | bit<br>interrupt |                  |         |         |  |

| se               | PEIE of the IN<br>t to enable a<br>ntrolled by regis | ny peripheral                                            | interrupt                                                            |                  |                  |         |         |  |

# REGISTER 7-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

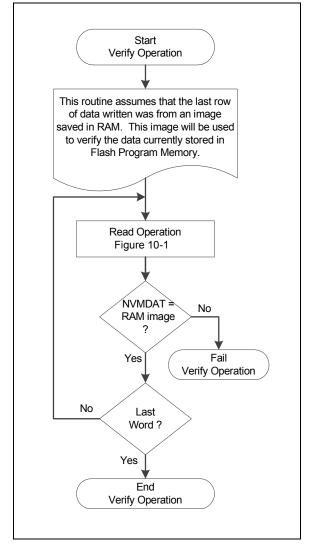

## 10.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

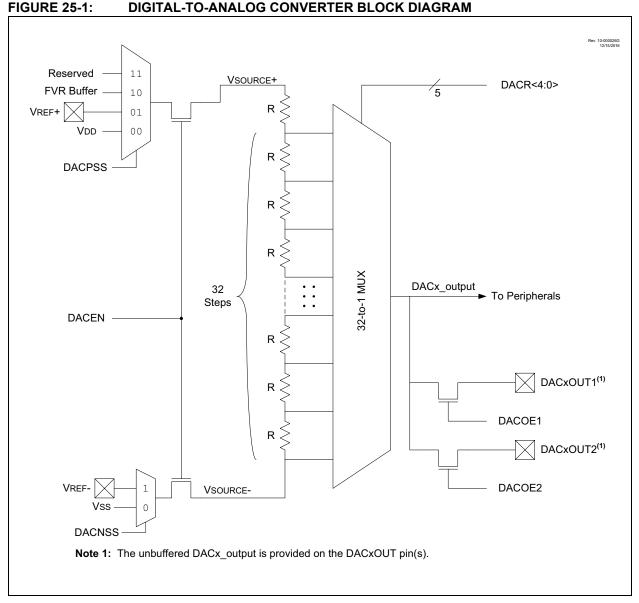

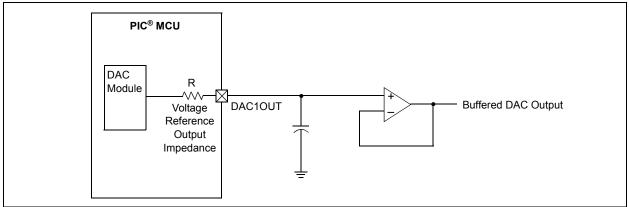

# FIGURE 25-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

# 25.6 Register Definitions: DAC Control

## REGISTER 25-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

|                  | -                                                                       |                                      | -              | -              |                  | -            |              |  |

|------------------|-------------------------------------------------------------------------|--------------------------------------|----------------|----------------|------------------|--------------|--------------|--|

| R/W-0/0          | U-0                                                                     | R/W-0/0                              | R/W-0/0        | R/W-0/0        | R/W-0/0          | U-0          | R/W-0/0      |  |

| DAC1EN           | —                                                                       | DAC10E1                              | DAC10E2        | DAC1F          | PSS<1:0>         | _            | DAC1NSS      |  |

| bit 7            |                                                                         | ·                                    |                | ·              |                  |              | bit 0        |  |

|                  |                                                                         |                                      |                |                |                  |              |              |  |

| Legend:          |                                                                         |                                      |                |                |                  |              |              |  |

| R = Readable     | bit                                                                     | W = Writable                         | bit            | U = Unimpler   | mented bit, read | as '0'       |              |  |

| u = Bit is unch  | nanged                                                                  | x = Bit is unki                      | nown           | -n/n = Value a | at POR and BOR   | Value at all | other Resets |  |

| '1' = Bit is set |                                                                         | '0' = Bit is cle                     | ared           |                |                  |              |              |  |

|                  |                                                                         |                                      |                |                |                  |              |              |  |

| bit 7            | <b>DAC1EN:</b> DA<br>1 = DAC is e                                       | C1 Enable bit                        |                |                |                  |              |              |  |

|                  | 1 = DAC is e<br>0 = DAC is d                                            |                                      |                |                |                  |              |              |  |

| bit 6            |                                                                         | ted: Read as '                       | 0'             |                |                  |              |              |  |

| bit 5            | -                                                                       | AC1 Voltage C                        |                | e bit          |                  |              |              |  |

|                  | 1 = DAC volt                                                            | age level is als                     | o an output or | n the DAC1OU   |                  |              |              |  |

|                  |                                                                         | age level is dis                     |                |                | UT1 pin          |              |              |  |

| bit 4            |                                                                         | AC1 Voltage C                        | •              |                |                  |              |              |  |

|                  |                                                                         | age level is als<br>age level is dis |                |                |                  |              |              |  |

| bit 3-2          |                                                                         | :0>: DAC1 Pos                        |                |                | • · - p          |              |              |  |

|                  | 11 = Reserv                                                             | ed, do not use                       |                |                |                  |              |              |  |

|                  | 10 = FVR ou                                                             | •                                    |                |                |                  |              |              |  |

|                  | 01 = VREF+ <br>00 = VDD                                                 | oin                                  |                |                |                  |              |              |  |

| bit 1            |                                                                         | ted: Read as '                       | 0'             |                |                  |              |              |  |

| bit 0            | Unimplemented: Read as '0'<br>DAC1NSS: DAC1 Negative Source Select bits |                                      |                |                |                  |              |              |  |

|                  | 1 = VREF- pir                                                           | •                                    |                |                |                  |              |              |  |

|                  | 0 = Vss                                                                 |                                      |                |                |                  |              |              |  |

|                  |                                                                         |                                      |                |                |                  |              |              |  |

### REGISTER 25-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | —   |         |         | DAC1R<4:0> |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                    |

|---------|-----------------------------------------------|

| bit 4-0 | DAC1R<4:0>: DAC1 Voltage Output Select bits   |

|         | Vout = (Vsrc+ - Vsrc-)*(DAC1R<4:0>/32) + Vsrc |

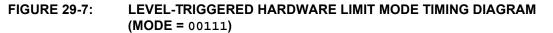

#### 29.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

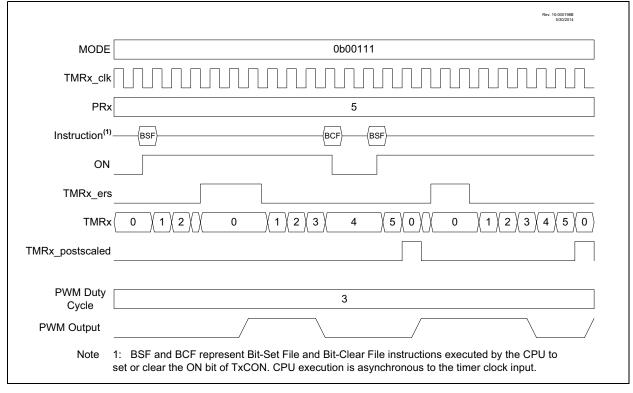

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 29-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

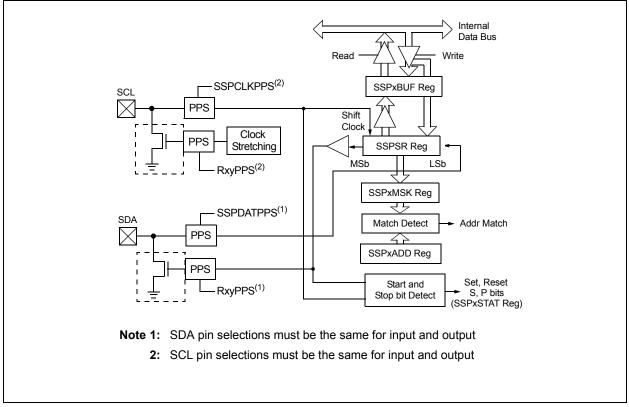

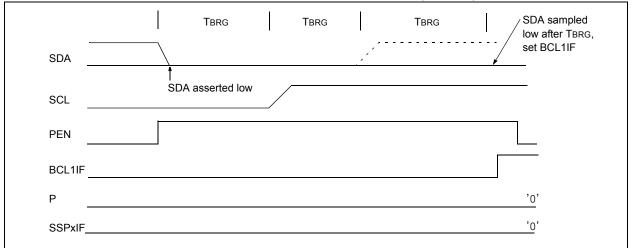

# 31.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 31-33).

- b) SCL is sampled low before SDA is asserted low (Figure 31-34).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- · the Start condition is aborted,

- the BCL1IF flag is set and

- the MSSP module is reset to its Idle state (Figure 31-33).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 31-35). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

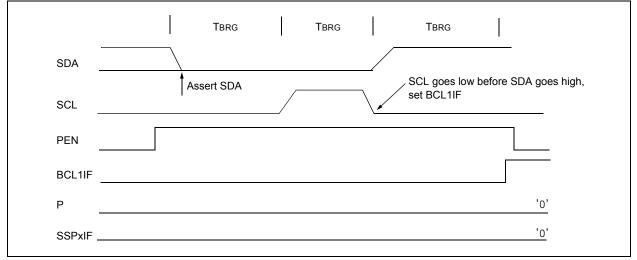

#### 31.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out (Case 1).

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high (Case 2).

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPxADD and counts down to zero. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 31-38). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 31-39).

#### FIGURE 31-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 31-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

DS40001824B-page 518

PIC16(L)F18856/76

# 37.0 ELECTRICAL SPECIFICATIONS

# 37.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias               | 40°C to +125°C       |

|----------------------------------------------|----------------------|

| Storage temperature                          | 65°C to +150°C       |

| Voltage on pins with respect to Vss          |                      |

| on VDD pin                                   |                      |

| PIC16F18856/76                               | -0.3V to +6.5V       |

| PIC16LF18856/76                              | -0.3V to +4.0V       |

| on MCLR pin                                  | -0.3V to +9.0V       |

| on all other pins                            | 0.3V to (VDD + 0.3V) |

| Maximum current                              |                      |

| on Vss pin <sup>(1)</sup>                    |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                 | 350 mA               |

| $85^{\circ}C < TA \le +125^{\circ}C$         | 120 mA               |

| on VDD pin for 28-Pin devices <sup>(1)</sup> |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                 | 250 mA               |

| $85^{\circ}C < TA \le +125^{\circ}C$         | 85 mA                |

| on VDD pin for 40-Pin devices <sup>(1)</sup> |                      |

| -40°C $\leq$ Ta $\leq$ +85°C                 | 350 mA               |

| $85^{\circ}C < TA \le +125^{\circ}C$         | 120 mA               |

| on any standard I/O pin                      | ±50 mA               |

| Clamp current, Iк (VPIN < 0 or VPIN > VDD)   | ±20 mA               |

| Total power dissipation <sup>(2)</sup>       | 800 mW               |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 37-6 to calculate device specifications.

2: Power dissipation is calculated as follows:

PDIS = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD - VOH) x IOH} +  $\Sigma$  (VOI x IOL)