Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18876-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| C          |

|------------|

| 1          |

| 6(         |

| Ľ          |

| T          |

| 18         |

| 88         |

| <b>U</b> I |

| 6/         |

| Z          |

| δ          |

| Q  | 40-Pin PDIP | 40-Pin UQFN | 44-Pin QFN | 44-Pin TQFP | ADC  | Voltage Reference | DAC | Comparators | Zero-Cross Detect | MSSP (SPI/I <sup>2</sup> C)                  | EUSART                                 | WSQ | Timers/SMT                                                                                   | CCP and PWM         | CWG | CLC | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic |

|----|-------------|-------------|------------|-------------|------|-------------------|-----|-------------|-------------------|----------------------------------------------|----------------------------------------|-----|----------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------------------------|---------------------|-------|

| RC | 0 15        | 30          | 34         | 32          | ANC0 | —                 | _   | _           | —                 | —                                            | _                                      |     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                   | _   | _   | _   |                        | IOCC0               | SOSCO |

| RC | 1 16        | 31          | 35         | 35          | ANC1 | _                 | _   |             | _                 | _                                            | _                                      | _   | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup> | _   | _   | —   |                        | IOCC1               | SOSCI |

| RC | 2 17        | 32          | 36         | 36          | ANC2 | —                 | —   | -           | —                 | —                                            | —                                      | _   | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup> | -   | —   | —   | -                      | IOCC2               | —     |

| RC | 3 18        | 33          | 37         | 37          | ANC3 | —                 | _   | -           | _                 | SCL1 <sup>(3,4)</sup><br>SCK1 <sup>(1)</sup> | Ι                                      | _   | T2IN <sup>(1)</sup>                                                                          | —                   | -   | —   | -   |                        | IOCC3               | —     |

| RC | 4 23        | 38          | 42         | 42          | ANC4 | —                 | —   | _           | —                 | SDA1 <sup>(3,4)</sup><br>SDI1 <sup>(1)</sup> | _                                      | _   | —                                                                                            | -                   | _   | —   | —   | _                      | IOCC4               | —     |

| RC | 5 24        | 39          | 43         | 43          | ANC5 | —                 | —   |             | —                 | —                                            | _                                      |     | T4IN <sup>(1)</sup>                                                                          | —                   |     | —   | —   |                        | IOCC5               | —     |

| RC | 6 25        | 40          | 44         | 44          | ANC6 |                   | —   | _           | —                 | —                                            | CK <sup>(3)</sup>                      | _   | _                                                                                            | _                   | _   | —   | —   |                        | IOCC6               | —     |

| RC | 7 26        | 1           | 1          | 1           | ANC7 | —                 | —   |             | _                 | —                                            | RX <sup>(1)</sup><br>DT <sup>(3)</sup> |     | —                                                                                            | —                   |     | —   | -   |                        | IOCC7               | —     |

| RD | 0 19        | 34          | 38         | 38          | AND0 |                   | —   | _           | —                 | —                                            | —                                      | _   | _                                                                                            | _                   | _   | —   | —   |                        | _                   | —     |

| RD | 1 20        | 35          | 39         | 39          | AND1 | —                 | —   |             | —                 | —                                            | _                                      | _   | —                                                                                            | _                   | _   | —   | —   |                        |                     | —     |

| RD | 2 21        | 36          | 40         | 40          | AND2 | —                 | —   | _           | _                 | —                                            | _                                      | _   | —                                                                                            | _                   | _   | —   | -   | _                      | _                   | _     |

| RD | 3 22        | 37          | 41         | 41          | AND3 | _                 | —   | _           | _                 | —                                            | _                                      | _   | _                                                                                            | _                   | _   | _   | _   | _                      | _                   | _     |

| RD | 4 27        | 2           | 2          | 2           | AND4 | —                 | —   | _           | _                 | —                                            | _                                      | _   | —                                                                                            | _                   | _   | —   | -   | _                      | _                   | —     |

| RD | 5 28        | 3           | 3          | 3           | AND5 | —                 | —   | 1           | —                 | —                                            | _                                      |     | _                                                                                            | _                   | 1   | —   | —   |                        |                     | _     |

| RD | 6 29        | 4           | 4          | 4           | AND6 | —                 | _   |             | —                 | —                                            | _                                      |     | _                                                                                            | _                   | 1   | —   | —   |                        | -                   | _     |

| RD | 7 30        | 5           | 5          | 5           | AND7 | _                 | _   | -           | —                 | —                                            | —                                      | -   | —                                                                                            | _                   | -   | —   | —   |                        |                     | _     |

| RE | 0 8         | 23          | 25         | 25          | ANE0 | _                 | —   |             |                   | —                                            |                                        |     | —                                                                                            | —                   |     | —   | —   | -                      | _                   | —     |

| RE | 19          | 24          | 26         | 26          | ANE1 | —                 | —   |             | -                 | —                                            |                                        |     | —                                                                                            | —                   |     | —   | —   | -                      | -                   | —     |

| RE | 2 10        | 25          | 27         | 27          | ANE2 | —                 | —   | —           | —                 | —                                            | —                                      | —   | —                                                                                            | -                   | —   | —   | —   | —                      | —                   | —     |

#### TABLE 3: 40/44-PIN ALLOCATION TABLE (PIC16(L)F18876) (CONTINUED)

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which port pins may be used for this signal.

2: All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels.; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMbus input buffer thresholds.

| <b>TABLE 1-3</b> : | PIC16F18876 PINOUT DESCRIPTION (CONTINUED) |

|--------------------|--------------------------------------------|

|--------------------|--------------------------------------------|

| Name                             | Function    | Input Type | Output Type        | Description                                          |

|----------------------------------|-------------|------------|--------------------|------------------------------------------------------|

| Vss                              | Vss         | Power      | —                  | Ground reference.                                    |

| OUT <sup>(2)</sup>               | ADGRDA      | _          | CMOS/OD            | ADC Guard Ring A output.                             |

|                                  | ADGRDB      | _          | CMOS/OD            | ADC Guard Ring B output.                             |

|                                  | C1OUT       | _          | CMOS/OD            | Comparator 1 output.                                 |

|                                  | C2OUT       | _          | CMOS/OD            | Comparator 2 output.                                 |

|                                  | SDO1        | _          | CMOS/OD            | MSSP1 SPI serial data output.                        |

|                                  | SCK1        | _          | CMOS/OD            | MSSP1 SPI serial clock output.                       |

|                                  | SDO2        | _          | CMOS/OD            | MSSP2 SPI serial data output.                        |

|                                  | SCK2        | _          | CMOS/OD            | MSSP2 SPI serial clock output.                       |

|                                  | ТХ          | _          | CMOS/OD            | EUSART Asynchronous mode transmitter data output.    |

|                                  | CK(3)       | -          | CMOS/OD            | EUSART Synchronous mode clock output.                |

|                                  | DT(3)       | -          | CMOS/OD            | EUSART Synchronous mode data output.                 |

|                                  | DSM         | -          | CMOS/OD            | Data Signal Modulator output.                        |

|                                  | TMR0        | _          | CMOS/OD            | Timer0 output.                                       |

|                                  | CCP1        | -          | CMOS/OD            | Capture/Compare/PWM1 output (compare/PWM functions). |

|                                  | CCP2        | _          | CMOS/OD            | Capture/Compare/PWM2 output (compare/PWM functions). |

| Legend: AN = Analog input or our | tput CMOS = | CMOS compa | tible input or out | put OD = Open-Drain                                  |

Legend: AN = Analog input or output TTL = TTL compatible input

ut or output CMOS = CMOS compatible input or output OD atible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C Open-Drain

Schmitt Trigger input with I<sup>2</sup>CHV=

High Voltage XTAL= Crystal levels

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Refer to Table 13-1 for details on which PORT pins may be used for this signal.

All output signals shown in this row are PPS remappable. These signals may be mapped to output onto one of several PORTx pin options as described in Table 13-3.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins are configured for I<sup>2</sup>C logic levels. The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST, as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

| Address                                         | Name    | PIC16(L)F18856<br>PIC16(L)F18876 | Bit 7 | Bit 6             | Bit 5 | Bit 4 | Bit 3        | Bit 2 | Bit 1    | Bit 0  | Value on:<br>POR, BOR | Value on all other Resets |

|-------------------------------------------------|---------|----------------------------------|-------|-------------------|-------|-------|--------------|-------|----------|--------|-----------------------|---------------------------|

| Bank 19                                         | Bank 19 |                                  |       |                   |       |       |              |       |          |        |                       |                           |

| CPU CORE REGISTERS; see Table 3-2 for specifics |         |                                  |       |                   |       |       |              |       |          |        |                       |                           |

| 98Ch                                            | —       |                                  |       |                   |       | U     | nimplemented |       |          |        | —                     | -                         |

| 98Dh                                            | —       |                                  |       |                   |       | U     | nimplemented |       |          |        | —                     | -                         |

| 98Eh                                            | —       |                                  |       |                   |       | U     | nimplemented |       |          |        | —                     | -                         |

| 98Fh                                            | CMOUT   |                                  | _     | —                 | —     | —     | —            | —     | MC2OUT   | MC1OUT | xx                    | xx                        |

| 990h                                            | CM1CON0 |                                  | ON    | OUT               | _     | POL   | —            | _     | HYS      | SYNC   | 0x-0 -100             | 0x-0 -100                 |

| 991h                                            | CM1CON1 |                                  | _     | —                 | _     | _     | _            | _     | INTP     | INTN   | 00                    | 00                        |

| 992h                                            | CM1NSEL |                                  | _     | —                 | _     | —     | —            |       | NCH<2:0> | •      | 000                   | 000                       |

| 993h                                            | CM1PSEL |                                  | _     | —                 | _     | —     | —            |       | PCH<2:0> |        | 000                   | 000                       |

| 994h                                            | CM2CON0 |                                  | ON    | OUT               | _     | POL   | —            | —     | HYS      | SYNC   | 0x-0 -100             | 0x-0 -100                 |

| 995h                                            | CM2CON1 |                                  | _     | —                 | _     | —     | —            | —     | INTP     | INTN   | 00                    | 00                        |

| 996h                                            | CM2NSEL |                                  | _     | —                 | _     | —     | —            |       | NCH<2:0> |        | 000                   | 000                       |

| 997h                                            | CM2PSEL |                                  | _     | —                 | _     | —     | —            |       | PCH<2:0> |        | 000                   | 000                       |

| 998h                                            | -       | —                                |       |                   |       | U     | nimplemented |       |          |        | -                     | -                         |

| 999h                                            | -       | -                                |       |                   |       | U     | nimplemented |       |          |        | -                     | -                         |

| 99Ah                                            | —       | —                                |       |                   |       | U     | nimplemented |       |          |        | _                     | —                         |

| 99Bh                                            | —       | —                                |       |                   |       | U     | nimplemented |       |          |        | _                     | —                         |

| 99Ch                                            | —       | —                                |       |                   |       | U     | nimplemented |       |          |        | _                     | —                         |

| 99Dh                                            | —       | —                                |       | Unimplemented — — |       |       |              |       |          |        |                       |                           |

| 99Eh                                            | —       | —                                |       |                   |       | U     | nimplemented |       |          |        | _                     | _                         |

| 99Fh                                            | —       | —                                |       |                   |       | U     | nimplemented |       |          |        | —                     | _                         |

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Register present on PIC16F18855/75 devices only. Unimplemented, read as '1'. Note 1:

2:

## 4.2 Register Definitions: Configuration Words

| REGISTER         | 4-1: CONF                     | IG1: CONFIG                                                                                                               | URATION        | WORD 1: OS                     | CILLATOR        | S                 |                |  |  |

|------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------|-----------------|-------------------|----------------|--|--|

|                  |                               | R/P-1                                                                                                                     | U-1            | R/P-1                          | U-1             | U-1               | R/P-1          |  |  |

|                  |                               | FCMEN                                                                                                                     | —              | CSWEN                          | —               | —                 | CLKOUTEN       |  |  |

|                  |                               | bit 13                                                                                                                    |                |                                |                 |                   | bit 8          |  |  |

| U-1              | R/P-1                         | R/P-1                                                                                                                     | R/P-1          | U-1                            | R/P-1           | R/P-1             | R/P-1          |  |  |

| 0-1              |                               | RSTOSC<2:0>                                                                                                               | F/F-1          | 0-1                            | N/F-1           | FEXTOSC<2:0       |                |  |  |

| <br>bit 7        |                               | K3103C<2.02                                                                                                               |                |                                |                 | FEXT030~2.0       | bit 0          |  |  |

|                  |                               |                                                                                                                           |                |                                |                 |                   | bit o          |  |  |

| Legend:          |                               |                                                                                                                           |                |                                |                 |                   |                |  |  |

| R = Readabl      | e bit                         | P = Programm                                                                                                              | nable bit      | U = Unimpler                   | mented bit, rea | ad as '1'         |                |  |  |

| '0' = Bit is cle | eared                         | '1' = Bit is                                                                                                              |                | n = Value wh                   | en blank or af  | ter Bulk Erase    |                |  |  |

|                  |                               | set                                                                                                                       |                |                                |                 |                   |                |  |  |

| bit 13           | ECMEN: Eail                   | Safe Clock Mo                                                                                                             | aitor Enabla   | hit                            |                 |                   |                |  |  |

| DIL 15           |                               | SCM timer enab                                                                                                            |                | UIL                            |                 |                   |                |  |  |

|                  | 0 = OFF <b>F</b> \$           | SCM timer disal                                                                                                           | oled           |                                |                 |                   |                |  |  |

| bit 12           | Unimplemen                    | ted: Read as '1                                                                                                           | ,              |                                |                 |                   |                |  |  |

| bit 11           |                               | ck Switch Enab                                                                                                            |                |                                |                 |                   |                |  |  |

|                  |                               | riting to NOSC<br>ne NOSC and N                                                                                           |                |                                | by user soft    | ware              |                |  |  |

| bit 10-9         | Unimplemen                    | <ul> <li>0 = OFF The NOSC and NDIV bits cannot be changed by user software</li> <li>Unimplemented: Read as '1'</li> </ul> |                |                                |                 |                   |                |  |  |

| bit 8            | CLKOUTEN:                     | Clock Out Enal                                                                                                            | ole bit        |                                |                 |                   |                |  |  |

|                  |                               | EC (high, mid                                                                                                             |                |                                | <b>.</b>        |                   |                |  |  |

|                  |                               | LKOUT functior                                                                                                            |                |                                |                 |                   |                |  |  |

|                  | <u>Otherwise</u>              |                                                                                                                           | no chabicu,    |                                | ppcars at 00    | 02                |                |  |  |

|                  | This bit is igno              | ored.                                                                                                                     |                |                                |                 |                   |                |  |  |

| bit 7            | Unimplemen                    | ted: Read as '1                                                                                                           | 3              |                                |                 |                   |                |  |  |

| bit 6-4          |                               | >: Power-up D                                                                                                             |                |                                |                 |                   | -              |  |  |

|                  | This value is t<br>111 = EXT1 |                                                                                                                           |                | OSC, and sele<br>oer FEXTOSC b |                 | tor first used by | user software  |  |  |

|                  | 110 = HFIN                    |                                                                                                                           | SC (1 MHz)     |                                | 0113            |                   |                |  |  |

|                  | 101 = LFIN                    | T LFINTO                                                                                                                  |                |                                |                 |                   |                |  |  |

|                  | 100 = SOSC                    |                                                                                                                           |                |                                |                 |                   |                |  |  |

|                  | 011 = Rese<br>010 = EXT4      |                                                                                                                           | C with 4x PI I | with EXTOS                     | Conerating of   | er FEXTOSC bit    | \$             |  |  |

|                  |                               |                                                                                                                           |                |                                |                 |                   | Fosc = 32 MHz) |  |  |

|                  | 000 = HFIN                    | T32 HFINTO                                                                                                                | SC with OS     | CFRQ= 32 MHz                   | and CDIV =      | 1:1               |                |  |  |

| bit 3            | Unimplemen                    | ted: Read as '1                                                                                                           | 3              |                                |                 |                   |                |  |  |

| bit 2-0          |                               | 0>: FEXTOSC                                                                                                               |                | cillator mode Se               | election bits   |                   |                |  |  |

|                  |                               | EC (External C<br>EC (External C                                                                                          |                |                                |                 |                   |                |  |  |

|                  |                               | EC (External C                                                                                                            |                |                                |                 |                   |                |  |  |

|                  |                               |                                                                                                                           |                | ed. RA7 is avai                | lable as a ger  | neral purpose I/C | D.             |  |  |

|                  | 011 = Reserved                |                                                                                                                           |                |                                |                 |                   |                |  |  |

|                  |                               | HS (Crystal oso<br>XT (Crystal oso                                                                                        |                |                                |                 |                   |                |  |  |

|                  |                               | LP (Crystal osc                                                                                                           |                |                                |                 |                   |                |  |  |

|                  |                               |                                                                                                                           | ,              |                                |                 |                   |                |  |  |

|                  |                               |                                                                                                                           |                |                                |                 |                   |                |  |  |

## 5.6 **RESET Instruction**

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 5-4 for default conditions after a RESET instruction has occurred.

## 5.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.4.2** "**Overflow/Underflow Reset**" for more information.

## 5.8 **Programming Mode Exit**

Upon exit of In-Circuit Serial Programming (ICSP) mode, the device will behave as if a POR had just occurred (the device does not reset upon run time self-programming/erase operations).

## 5.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of the Configuration Words.

The Power-up Timer provides a nominal 64 ms time out on POR or Brown-out Reset. The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in the Configuration Words. The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607).

## 5.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer Configuration. See Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 5-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| U-0                                                | U-0                                                          | R/W-0/0                                                                                                          | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|--|--|

|                                                    | —                                                            | TMR6IE                                                                                                           | TMR5IE          | TMR4IE         | TMR3IE           | TMR2IE           | TMR1IE      |  |  |  |

| bit 7                                              | ·                                                            | ÷                                                                                                                |                 |                |                  |                  | bit         |  |  |  |

|                                                    |                                                              |                                                                                                                  |                 |                |                  |                  |             |  |  |  |

| Legend:                                            |                                                              |                                                                                                                  |                 |                |                  |                  |             |  |  |  |

| R = Readal                                         | ble bit                                                      | W = Writable                                                                                                     | bit             | U = Unimpler   | nented bit, read | l as '0'         |             |  |  |  |

| u = Bit is ur                                      | nchanged                                                     | x = Bit is unkr                                                                                                  | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is s                                     | set                                                          | '0' = Bit is cle                                                                                                 | ared            | HS = Hardwa    | re set           |                  |             |  |  |  |

| bit 7-6                                            | Unimplomor                                                   | nted: Read as '                                                                                                  | o,'             |                |                  |                  |             |  |  |  |

| bit 5                                              | -                                                            | R6 to PR6 Mat                                                                                                    |                 | nable bit      |                  |                  |             |  |  |  |

| bit 0                                              |                                                              | s the Timer6 to                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | s the Timer6 to                                                                                                  |                 | •              |                  |                  |             |  |  |  |

| bit 4 TMR5IE: Timer5 Overflow Interrupt Enable bit |                                                              |                                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | 1 = Enables the Timer5 overflow interrupt                                                                        |                 |                |                  |                  |             |  |  |  |

|                                                    | <ul><li>0 = Disables the Timer5 overflow interrupt</li></ul> |                                                                                                                  |                 |                |                  |                  |             |  |  |  |

| bit 3                                              |                                                              | R4 to PR4 Mat                                                                                                    |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | nables the Timer4 to PR4 match interrupt<br>isables the Timer4 to PR4 match interrupt                            |                 |                |                  |                  |             |  |  |  |

| bit 2                                              |                                                              | R3 Overflow In                                                                                                   |                 | •              |                  |                  |             |  |  |  |

|                                                    |                                                              |                                                                                                                  | •               |                |                  |                  |             |  |  |  |

|                                                    |                                                              | <ul> <li>1 = Enables the Timer3 overflow interrupt</li> <li>0 = Enables the Timer3 overflow interrupt</li> </ul> |                 |                |                  |                  |             |  |  |  |

| bit 1                                              | TMR2IE: TM                                                   | R2 to PR2 Mat                                                                                                    | ch Interrupt Er | nable bit      |                  |                  |             |  |  |  |

|                                                    |                                                              | s the Timer2 to                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | s the Timer2 to                                                                                                  |                 | •              |                  |                  |             |  |  |  |

| bit 0                                              |                                                              | er1 Overflow Ir                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | s the Timer1 ov                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    |                                                              | s the Timer1 ov                                                                                                  | eniow interrup  | π              |                  |                  |             |  |  |  |

| Note:                                              | Bit PEIE of the IN                                           | ITCON register                                                                                                   | must be         |                |                  |                  |             |  |  |  |

|                                                    | set to enable a                                              |                                                                                                                  |                 |                |                  |                  |             |  |  |  |

|                                                    | controlled by regis                                          | sters PIE1-PIE8                                                                                                  |                 |                |                  |                  |             |  |  |  |

## REGISTER 7-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

## **18.2 Comparator Control**

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- Speed/Power selection

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- Interrupt on positive/negative edge enables

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 13-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

## 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-2 shows the output state versus input conditions, including polarity control.

#### TABLE 18-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

## 23.6 Register Definitions: ADC Control

## REGISTER 23-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                                                                                                                                                | U-0                             | R/W-0/0         | U-0                | R/W-0/0           | U-0            | R/W/HC-0         |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|--------------------|-------------------|----------------|------------------|--|

| ADON             | ADCONT                                                                                                                                                                 | —                               | ADCS            |                    | ADFRM0            |                | ADGO             |  |

| bit 7            |                                                                                                                                                                        |                                 |                 |                    |                   |                | bit 0            |  |

|                  |                                                                                                                                                                        |                                 |                 |                    |                   |                |                  |  |

| Legend:          |                                                                                                                                                                        |                                 |                 |                    |                   |                |                  |  |

| R = Readable b   | oit                                                                                                                                                                    | W = Writable                    | bit             | U = Unimple        | mented bit, read  | as '0'         |                  |  |

| u = Bit is uncha | anged                                                                                                                                                                  | x = Bit is unkr                 | iown            | -n/n = Value       | at POR and BOF    | R/Value at all | other Resets     |  |

| '1' = Bit is set |                                                                                                                                                                        | '0' = Bit is clea               | ared            | HC = Bit is c      | leared by hardwa  | are            |                  |  |

|                  |                                                                                                                                                                        |                                 |                 |                    |                   |                |                  |  |

| bit 7            | ADON: ADC                                                                                                                                                              |                                 |                 |                    |                   |                |                  |  |

|                  | 1 = ADC is enabled<br>0 = ADC is disabled                                                                                                                              |                                 |                 |                    |                   |                |                  |  |

| bit 6            | ADCONT: AD                                                                                                                                                             | C Continuous                    | Operation Ena   | able bit           |                   |                |                  |  |

|                  |                                                                                                                                                                        |                                 |                 |                    | ersion trigger un |                | set (if ADSOI is |  |

|                  | ,                                                                                                                                                                      | or until ADGO<br>cleared upon c |                 |                    | value of ADSOI)   |                |                  |  |

| bit 5            |                                                                                                                                                                        | ted: Read as '                  |                 |                    | n uggei           |                |                  |  |

| bit 4            | •                                                                                                                                                                      | Clock Selection                 |                 |                    |                   |                |                  |  |

|                  |                                                                                                                                                                        | plied from FR                   |                 | cillator           |                   |                |                  |  |

|                  |                                                                                                                                                                        | plied by Fosc,                  |                 |                    | < register        |                |                  |  |

| bit 3            | Unimplemen                                                                                                                                                             | ted: Read as '                  | 0'              |                    |                   |                |                  |  |

| bit 2            | ADFRM0: AD                                                                                                                                                             | C results Form                  | nat/alignment s | Selection          |                   |                |                  |  |

|                  |                                                                                                                                                                        | nd ADPREV d                     |                 |                    |                   |                |                  |  |

|                  |                                                                                                                                                                        | nd ADPREV d                     | -               | tified, zero-fille | ed                |                |                  |  |

| bit 1            | Unimplemen                                                                                                                                                             | ted: Read as '                  | 0'              |                    |                   |                |                  |  |

| bit 0            | <ul> <li>1 = ADC conversion cycle in progress. Setting this bit starts an ADC conversion cycle. The<br/>cleared by hardware as determined by the ADCONT bit</li> </ul> |                                 |                 |                    |                   |                | ycle. The bit is |  |

|                  | 0 = ADC conv                                                                                                                                                           | version comple                  | ted/not in prog | Iress              |                   |                |                  |  |

## REGISTER 24-3: NCO1ACCL: NCO1 ACCUMULATOR REGISTER – LOW BYTE

| المعممط |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         | NCO1A   | CC<7:0> |         |         |         |

| R/W-0/0 |

|         |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCO1ACC<7:0>: NCO1 Accumulator, Low Byte

#### REGISTER 24-4: NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------|---------|---------|---------|---------|---------|---------|---------|

| NCO1ACC<15:8> |         |         |         |         |         |         |         |

| bit 7         |         |         |         |         |         |         | bit 0   |

|               |         |         |         |         |         |         |         |

| Legend:       |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NOC1ACC<15:8>: NCO1 Accumulator, High Byte

#### REGISTER 24-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|----------|---------|

| —     | _   | _   | _   |         | NCO1AC  | C<19:16> |         |

| bit 7 |     |     |     |         |         | bit 0    |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

#### 29.5.5 SOFTWARE START ONE-SHOT MODE

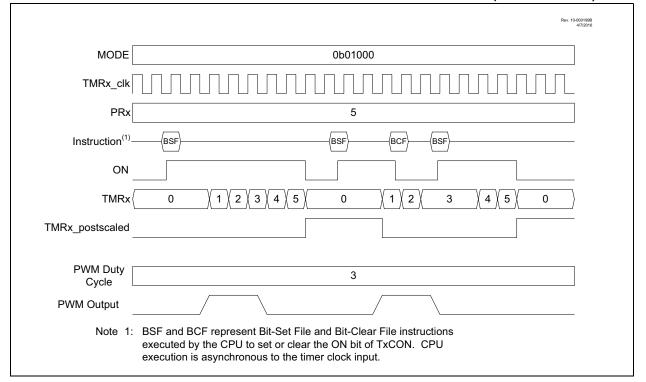

In One-Shot mode the timer resets and the ON bit is cleared when the timer value matches the PRx period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 29-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the PRx match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a PRx period count match.

FIGURE 29-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

| R/W/HC-0/0                                                                    | R/W-0/0                                          | R/W-0/0            | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|-------------------------------------------------------------------------------|--------------------------------------------------|--------------------|----------------|-----------------|------------------|----------|---------|--|

| 0N <sup>(1)</sup>                                                             |                                                  | CKPS<2:0>          |                |                 | OUTP             | S<3:0>   |         |  |

| bit 7                                                                         |                                                  |                    |                |                 |                  |          | bit 0   |  |

| Legend:                                                                       |                                                  |                    |                |                 |                  |          |         |  |

| R = Readable                                                                  | bit                                              | W = Writable       | bit            | U = Unimplen    | nented bit, read | d as '0' |         |  |

| u = Bit is unchanged $x = Bit is unknown$ $-n/n = Value at POR and BOR/Value$ |                                                  |                    |                |                 | other Resets     |          |         |  |

| '1' = Bit is set                                                              | J                                                | '0' = Bit is clea  | ared           |                 | eared by hardw   |          |         |  |

| bit 7                                                                         | <b>ON:</b> Timerx                                | On hit             |                |                 |                  |          |         |  |

|                                                                               | 1 = Timerx                                       |                    |                |                 |                  |          |         |  |

|                                                                               |                                                  | is off: all counte | rs and state m | achines are res | set              |          |         |  |

| bit 6-4                                                                       | CKPS<2:0>                                        | : Timer2-type Cl   | ock Prescale   | Select bits     |                  |          |         |  |

|                                                                               | 111 = 1:128                                      |                    |                |                 |                  |          |         |  |

|                                                                               | 111 = 1.64 Prescaler                             |                    |                |                 |                  |          |         |  |

|                                                                               | 101 = 1:32 Prescaler                             |                    |                |                 |                  |          |         |  |

|                                                                               | 100 = 1:16 Prescaler                             |                    |                |                 |                  |          |         |  |

|                                                                               | 011 = 1:8 Prescaler                              |                    |                |                 |                  |          |         |  |

|                                                                               |                                                  | = 1:4 Prescaler    |                |                 |                  |          |         |  |

|                                                                               | 001 = 1:2 P                                      |                    |                |                 |                  |          |         |  |

|                                                                               | 000 = 1:1 P                                      | rescaler           |                |                 |                  |          |         |  |

| bit 3-0                                                                       | OUTPS<3:0>: Timerx Output Postscaler Select bits |                    |                |                 |                  |          |         |  |

|                                                                               | 1111 <b>= 1:16</b>                               |                    |                |                 |                  |          |         |  |

|                                                                               | 1110 = 1:15 Postscaler                           |                    |                |                 |                  |          |         |  |

|                                                                               | 1101 = 1:14 Postscaler                           |                    |                |                 |                  |          |         |  |

|                                                                               | 1100 = 1:13                                      |                    |                |                 |                  |          |         |  |

|                                                                               | 1011 = 1:12                                      |                    |                |                 |                  |          |         |  |

|                                                                               | 1010 = 1:11 Postscaler<br>1001 = 1:10 Postscaler |                    |                |                 |                  |          |         |  |

|                                                                               |                                                  |                    |                |                 |                  |          |         |  |

|                                                                               | 1000 = 1:9 Postscaler<br>0111 = 1:8 Postscaler   |                    |                |                 |                  |          |         |  |

|                                                                               | 0111 = 1.0  Postscaler $0110 = 1.7  Postscaler$  |                    |                |                 |                  |          |         |  |

|                                                                               | 0101 = 1:6 F                                     |                    |                |                 |                  |          |         |  |

|                                                                               | 0100 = 1:5 F                                     |                    |                |                 |                  |          |         |  |

|                                                                               | 0011 = 1:4 F                                     |                    |                |                 |                  |          |         |  |

|                                                                               | 0010 = 1:3 F                                     |                    |                |                 |                  |          |         |  |

|                                                                               | 0001 = 1:2 F                                     | Postscaler         |                |                 |                  |          |         |  |

|                                                                               | 0000 = 1:1 F                                     | Postscaler         |                |                 |                  |          |         |  |

### REGISTER 29-2: TxCON: TIMER2/4/6 CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 29.5 "Operation Examples".

## 30.2.1 CCPX PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 13.0 "Peripheral Pin Select (PPS) Module"** for more details.

The CCP output can also be used as an input for other peripherals.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 30.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 28.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 30.2.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an Auto-conversion Trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to **Section 23.2.6 "Auto-Conversion Trigger"** for more information.

| Note: | Removing the match condition by            |

|-------|--------------------------------------------|

|       | changing the contents of the CCPRxH        |

|       | and CCPRxL register pair, between the      |

|       | clock edge that generates the              |

|       | Auto-conversion Trigger and the clock      |

|       | edge that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring          |

## 30.2.4 COMPARE DURING SLEEP

Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

## 30.3 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

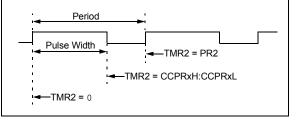

Figure 30-3 shows a typical waveform of the PWM signal.

#### 30.3.1 STANDARD PWM OPERATION

The standard PWM function described in this section is available and identical for all CCP modules.

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2 registers

- T2CON registers

- CCPRxL registers

- CCPxCON registers

Figure 30-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 30-3: CCP PWM OUTPUT SIGNAL

### **REGISTER 30-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE**

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| CCPRx<15:8> |         |         |         |         |         |         |         |

| bit 7       |         |         |         |         |         |         | bit 0   |

|             |         |         |         |         |         |         |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

bit 7-0

CCPxMODE = Capture mode

CCPRxH<7:0>: Captured value of TMR1H

CCPxMODE = Compare mode

CCPRxH<7:0>: MS Byte compared to TMR1H

CCPxMODE = PWM modes when CCPxFMT = 0:

CCPRxH<7:2>: Not used

CCPRxH<1:0>: Pulse-width Most Significant two bits

CCPxMODE = PWM modes when CCPxFMT = 1:

CCPRxH<7:0>: Pulse-width Most Significant eight bits

#### REGISTER 30-5: CCPTMRS0: CCP TIMERS CONTROL 0 REGISTER

| R/W-0/0                 | R/W-1/1 | R/W-0/0 | R/W-1/1 | R/W-0/0 | R/W-1/1     | R/W-0/0 | R/W-1/1 |

|-------------------------|---------|---------|---------|---------|-------------|---------|---------|

| C4TSEL<1:0> C3TSEL<1:03 |         | L<1:0>  | C2TSE   | EL<1:0> | C1TSEL<1:0> |         |         |

| bit 7                   |         |         |         |         |             | bit 0   |         |

| Legend:              |                      |                                                      |